# BiMOS Sequencer Driver and Segment Latch-Driver for Vacuum Fluorescent Displays

#### Features:

- Serial input, parallel output

- Total of 14 outputs

- CMOS and T<sup>2</sup>L compatible inputs

- Low-power CMOS Logic-Bipolar high-voltage output BiMOS process

- Use with vacuum fluorescent display

- Will operate in an output voltage range of 35 V to 55 V

### Sequencer Driver (CA3207E)

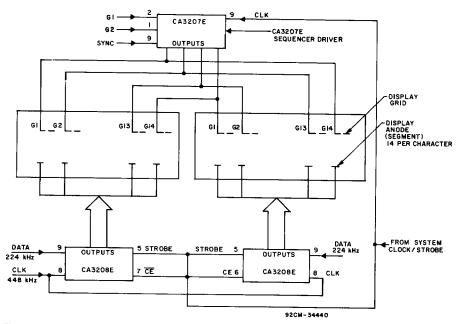

- Sequentially turns on 1 of 14 characters (or 2 of 28 when used with 2 CA3208E's)

- Signal dimming through Gates 1 or 2

### Latch Driver (CA3208E)

- Drives any combination of 14 outputs selected by DATA input

- Two or more devices may be interconnected by means of the CE and CE inputs to drive more than 14 characters

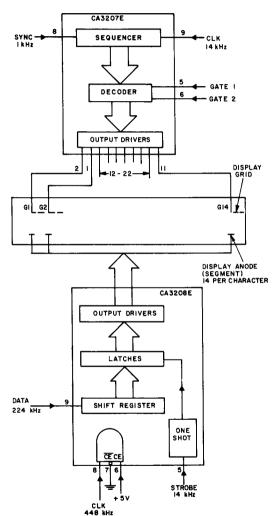

The RCA-CA3207E and CA3208E\*, sequence-driver and segment latch-driver, respectively, are used in combination to drive vacuum fluorescent display devices of up to 14 segments with up to 14 characters of display. The CA3207E selects the digit or character to be displayed in sequence and the CA3208E turns on the required number of segments of the character selected.

Each sequencer-driver will sequentially activate 14 characters. The sequencer-driver clock line may be used to drive the cross-coupled  $\overline{CE}$  and CE inputs of 2 segment-

latch drivers to provide for the display of up to 28 characters (see Fig. 12). The logic portion of both circuits use CMOS technology operating at 5 volts. The output drivers use bipolar technology and operate at supply voltages up to 55 volts. The CA3207E will source 40-mA per character and the CA3208E will source 7.5-mA per segment.

Both types are supplied in the 22-lead dual-in-line plastic package (E suffix), and they are also available in chip form (H suffix).

\*Formerly Dev. Type No. TA10563 and TA10564, respectively.

### MAXIMUM RATINGS, Absolute-Maximum Values:

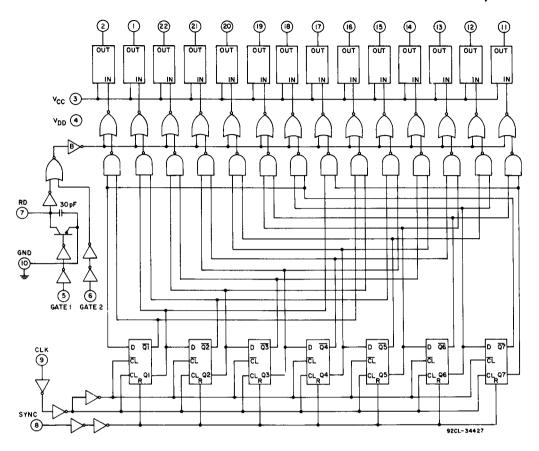

Fig. 1 - Sequencer-driver (CA3207E) logic diagram.

TERMINAL ASSIGNMENT CA3207E

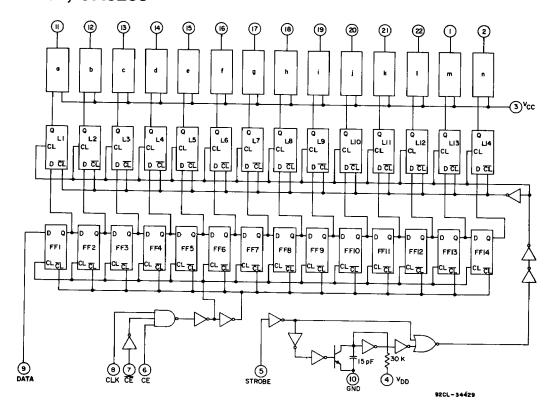

Fig. 2 - Segment-latch driver (CA3208E) logic diagram.

TERMINAL ASSIGNMENT CA3208E

164

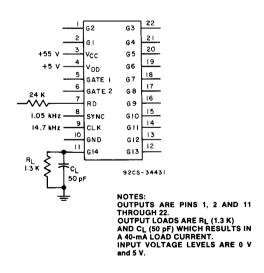

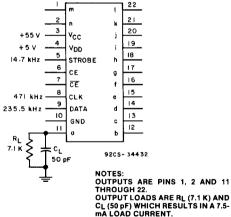

### STATIC ELECTRICAL CHARACTERISTICS at TA=25°C, Vcc=+55 V, Vnn=+5 V, Ct =50 pF, See Fig. 3 and Fig. 4.

|                                |                 |                         | LIMITS   |      |         |      |            |  |

|--------------------------------|-----------------|-------------------------|----------|------|---------|------|------------|--|

| CHARACTERISTIC                 |                 | TEST CONDITIONS         | CA3207E  |      | CA3208E |      | UNITS      |  |

|                                |                 |                         | Min.     | Max. | Min.    | Max. |            |  |

| V <sub>CC</sub> Supply Current |                 | No outputs "ON"         | _        | 10   | _       | _    | mA         |  |

|                                | ICC             | Half outputs HIGH "ON"  |          |      | _       | 65   | I IIIA     |  |

| V <sub>DD</sub> Supply Current | IDD             | All inputs HIGH         |          | 1    | _       | _    | mA         |  |

|                                |                 | All inputs LOW          | T -      | l –  | _       | 800  |            |  |

|                                |                 | All inputs HIGH         | _        | _    | _       | 1    | μΑ         |  |

| Input Current, Low-Level       | IIL             | V <sub>IN</sub> =0 V    | <b>—</b> | 1    | _       | 1    |            |  |

| Input Current, High-Level      | ΙΗ              | V <sub>IN</sub> =5 V    | l –      | 1    | _       | 1    | μA         |  |

| Output Voltage, Low-Level      | V <sub>OL</sub> | R <sub>L</sub> =1.3K    | 1 -      | 1    | _       | _    |            |  |

|                                |                 | R <sub>L</sub> =7.1K    | -        | -    | -       | 1    | v          |  |

| Output Voltage, High-Level     | Voн             | IOH=40 mA               | 53       |      | _       |      | 1          |  |

|                                |                 | I <sub>OH</sub> =7.5 mA |          | _    | 53      | _    |            |  |

| Input Low Voltage              | VIL             |                         | _        | 1.5  | _       | 1.5  | V          |  |

| Input High Voltage             | VIH             |                         | 3.5      | _    | 3.5     | Ì —  | ] <b>`</b> |  |

Fig. 3 - Sequencer-driver (CA3207E) test circuit.

THROUGH 22.

OUTPUT LOADS ARE RL (7.1 K) AND CL (50 pF) WHICH RESULTS IN A 7.5-mA LOAD CURRENT. INPUT VOLTAGE LEVELS ARE 0 V AND 5 V.

Fig. 4 - Segment-latch driver (CA3208E) test circuit.

DYNAMIC ELECTRICAL CHARACTERISTICS at TA=25°C, VCC=+55 V, VDD=+5 V, CL=50 pF, RL=1.3K

| CHARACTERISTIC               |      | LIN  | UNITS       |     |

|------------------------------|------|------|-------------|-----|

|                              |      | CAS  |             |     |

|                              | Min. | Max. |             |     |

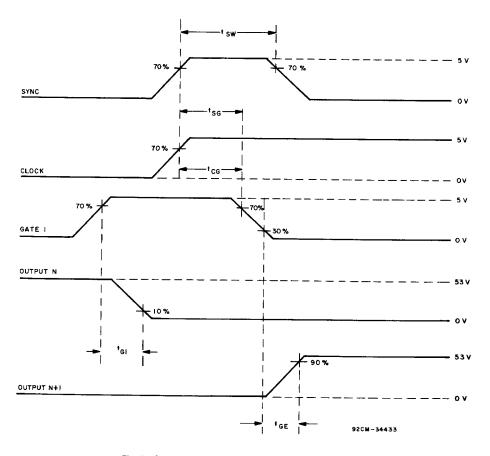

| Sequencer-Driver, See Fig. 5 |      |      |             |     |

| Sync Pulse Width             | tsw  | 2    |             | μѕ  |

| Time Delay Gate 1:           |      |      |             |     |

| Input-to-Output Inhibit      | tGI  | _    | 1.5         | μs  |

| Input-to-Output Enable       | tGE  | -    | 2.3         |     |

| Lead Time Sync to Gate       | tsg  | 0.5  |             | μs  |

| Lead Time Clock to Gate      | tcg  | 0.5  | <del></del> | ┦ ~ |

| Clock Frequency              | fCL  |      | 14          | kHz |

Fig. 5 - Sequencer-driver (CA3207E) timing waveforms.

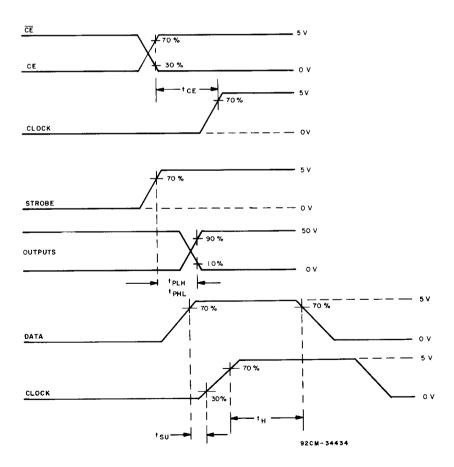

DYNAMIC ELECTRICAL CHARACTERISTICS at TA=25°C, VCC=+55 V, VDD=+5 V, CL= 50 pF, RL=7.1 K

| CHARACTERISTIC                   |                  | LIN          | UNITS |         |  |

|----------------------------------|------------------|--------------|-------|---------|--|

|                                  |                  | CA3          |       |         |  |

|                                  | Min.             | Max.         |       |         |  |

| Segment-Latch Driver, See Fig. 6 |                  |              |       |         |  |

| Time Delay:                      |                  |              |       |         |  |

| Strobe to Output                 | t <sub>PLH</sub> | 0.4          | 1.8   |         |  |

| Strobe to Output                 | t <sub>PHL</sub> | _            | 2.6   | μs      |  |

| CE or CE to Clock                | tCE              | 0.8          |       |         |  |

| Input Data Set-Up Time           | tsu              | 0.5          | _     | μs      |  |

| Input Data Hold Time             | tH               | 0.5          | _     | μς      |  |

| Clock Frequency                  | fCL              |              | 448   | kHz     |  |

| Data Frequency                   | fD               | <del>-</del> | 224   | 7 ~ ~ ~ |  |

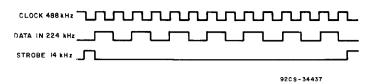

Fig. 6 - Segment-latch driver (CA3208E) timing waveforms.

### Circuit Descriptions

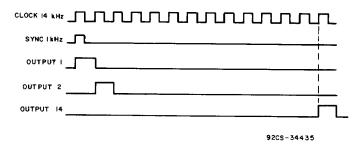

#### Sequencer-Driver (CA3207E)

The CA3207E circuit consists of a 7-stage Johnson counter, which is reset by the positive transition of the sync pulse and which is clocked on the positive transitions of the clock pulse. The outputs of the counter are decoded to turn on one output driver at a time in sequence, for the period of one clock pulse (normally 70 us). The 14 output drivers are each capable of sourcing 40 mA of current and in a typical application will be connected to the grids of a vacuum fluorescent display, thereby performing a digit select function on a display of up to 14 characters. All outputs are set to zero by the application of a positive "1" level to either of the gate terminals, 5 and 6. The action of the 7-stage counter is unaffected by the presence of inhibit levels on the gate terminals. The gate terminals can be used for a controlled power down or for chopping where display dimmer is desired. The only difference between the two terminals is that gate 1, pin 5, has a delayed falling edge, which delays the release of the output drivers for a time determined by the value of the resistor connected between pin 7 and VDD.

### Segment-Latch Driver (CA3208E)

This circuit consists of a 14-bit shift register accepting serial data at pin 9 at a typical rate of 224 kHz and being clocked on the rising edge of the 448-kHz clock signal.

The leading edge of a 14-kHz strobe signal generates an internal strobe pulse through the one shot, which shifts the data, in parallel, from the shift register to the output latches, which in turn set the output drivers to the corresponding state. There are 14 output drivers, each capable of driving 7.5-mA at 55 volts, simultaneously. The drivers are normally connected to the anodes or segments of the vacuum fluorescent display. In a multi-character display, all corresponding segments in each character would be linked together. Activation of a particular character is made by the CA3207E Sequencer-Driver turning on the appropriate output and raising the grid of the display to a positive value.

Clock Enable (CE) and Clock Enable Not  $(\overline{CE})$  pins are available for use in system applications. The first enables the chip with a logic level "1" and the second with a logic level "0".

Fig. 7 - Sequencer driver (CA3207E) timing waveforms.

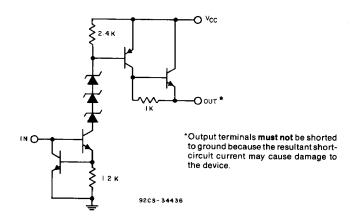

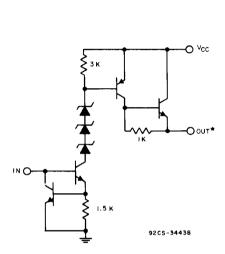

Fig. 8 - Sequencer driver (CA3207E) output circuit.

Fig. 9 - Segment-latch driver (CA3208E) timing waveforms.

\*Output terminals **must not** be shorted to ground because the resultant shortcircuit current may cause damage to the device.

Fig. 10 - Segment latch-driver (CA3208E) output circuit.

NOTE: 2 DISPLAYS CAN BE OPERATED SIMULTANEOUSLY USING ONLY I SEQUENCER AND 2 SEGMENT-LATCH-DRIVERS 92CM-34439

Fig. 11 - Typical systems application of the CA3207E and CA3206E display circuits.

Fig. 12 - Typical systems application of the CA3207E and 2 CA3208E circuits for a total 28-character display.

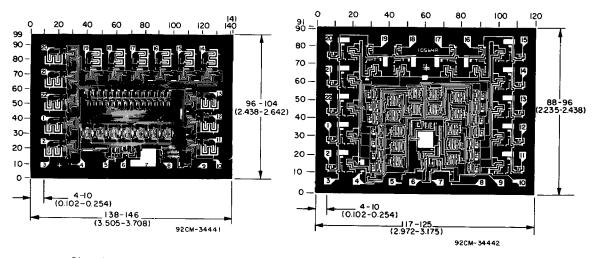

Dimensions and pad layout for the CA3207H.

Dimensions and pad layout for the CA3208H.

The photographs and dimensions represent a chip when it is part of the wafer. When the wafer is cut into chips, the cleavage angles are 57° instead of 90° with respect to the face of the chip. Therefore, the isolated chip is actually 7 mils (0.17 mm) larger in both dimensions.

Dimensions in parentheses are in millimeters and are derived from the basic inch dimensions as indicated. Grid graduations are in mils  $(10^{-3} \text{ inch})$ .