# User's Guide TPS40071 Buck Controller Evaluation Module User's Guide

# TEXAS INSTRUMENTS

#### ABSTRACT

The TPS40071EVM–001 evaluation module (EVM) is a synchronous buck converter operating from an input bus voltage ranging from 5 V to 12 V, using Predictive Gate Drive<sup>™</sup> (PGD) technology to efficiently deliver 1.8 V at up to 10 A of load current.

## **Table of Contents**

| 1 Introduction                                  | 2  |

|-------------------------------------------------|----|

| 2 Description                                   | 2  |

| 3 Schematic                                     |    |

| 3.1 Output Filter Components                    | 3  |

| 3.2 MOSFET Selection                            | 4  |

| 3.3 Frequency Feedforward Resistor Selection    | 4  |

| 3.4 Output Voltage Setpoint                     | 4  |

| 3.5 Short Circuit Protection Resistor Selection | 4  |

| 3.6 Miscellaneous Parts                         |    |

| 3.7 Control Loop Compensation                   | 5  |

| 4 Test Setup                                    |    |

| 5 Results                                       |    |

| 5.1 Control Loop Characteristics                | 9  |

| 6 Assembly Drawing and PCB Layout               | 11 |

| 7 List of Materials                             | 14 |

| 8 Reference                                     | 15 |

| 9 Revision History                              |    |

#### Trademarks

Predictive Gate Drive<sup>™</sup> and PowerPAD<sup>™</sup> are trademarks of Texas Instruments. All trademarks are the property of their respective owners.

# **1** Introduction

The TPS40071EVM-001 evaluation module (EVM) is a synchronous buck converter that uses PGD to maximize conversion efficiency by minimizing the body diode conduction loss. The use of the TPS40071 midrange input synchronous buck controller allows the EVM to deliver 10 A from a bus voltage ranging from 5 V to 14 V. The output voltage is originally set to 1.8 V, but can also be configured to provide 1.2 V to 3.3 V at a load current up to 10 A by changing one surface mount resistor.

## 2 Description

The TPS40070/TPS40071 synchronous buck controller family offers a variety of user-programmable functions including the following:

- Switching frequency

- Soft start

- High-side current limit

- UVLO

- External compensation

The controller operates with fixed frequency voltage mode control with an input voltage feedforward control input, which improves performance in applications that have a variable input source. The TPS40071 is selected in the EVM because it operates in source-sink mode over the entire operating range.

The TPS40071 incorporates internal gate drivers for external N-channel MOSFETs in the high-side switch and low-side synchronous rectifier locations. The MOSFET drivers utilize TI's proprietary Predictive Gate Drive technique, which works to minimize the body diode conduction interval to reduce undesired power loss. The PowerPAD<sup>™</sup> package allows the regulator bias power and the gate drive power to be safely dissipated without raising the junction an excessive amount. The high-side current limit/short circuit protection senses the voltage drop across the top-side MOSFET and compares it to a programmable reference to terminate output pulses on a pulse by pulse basis.

The TPS40071EVM-001 highlights the small size, highly efficient solutions that can be attained using the TPS40071 controller. This user guide provides the collateral necessary to evaluate the TPS40071 in a typical application. The collateral includes the following:

- Schematic

- List of materials

- Test setup

- Assembly drawings

- PCB layout

The TPS40071EVM-001 offers the following performance features:

- Operates continuously over a 4.75-V to 14-V input range

- Delivers 1.8-V output at 10 A; configurable for other voltages

- Excellent line/load regulation better than 0.1%

- 96% efficient with  $V_{IN}$  = 8 V,  $V_{OUT}$  = 3.3 V

- Power-good signal

- Output short circuit protection

## 3 Schematic

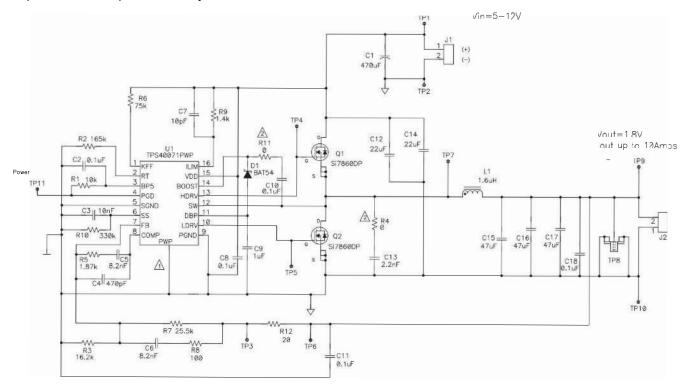

Figure 3-1 shows the TPS40071EVM-001 schematic. The switching frequency is chosen to be 300 kHz to enable the converter to operate efficiently over a wide range of input and output conditions. C1 is included on the board to represent the output capacitance of the upstream converter feeding the EVM, and no external capacitance should be required at the input. In typical applications with short input wiring (less than 1 inch to 3 inch depending on output power level), C1 might not be required. C12 and C14 are local high frequency bypass capacitors for the power circuitry.

Figure 3-1. TPS40071EVM-001 Schematic

#### 3.1 Output Filter Components

The power inductor is selected by calculating the range of peak-to-peak ripple current,  $I_{PP}$ , which is obtained with various values of inductance over the total input/output voltage range. In previous generations of buck converters, electrolytic capacitors with significant ESR were the normal, and the inductor ripple current would be selected to be 10% to 20% of  $I_{OUT}$  to minimize the output voltage ripple. Now, ceramic output capacitors with ESR in the range of 1 mW to3 mW are readily available, so the ripple current can be allowed to be 20% to 50% of the output current. The following equation was used to calculate the ripple current; and complete results are presented for the selected inductor value of 1.6  $\mu$ H.

$$\Delta I_{PP} = T_{ON} \times \frac{V_{IN} - V_{OUT}}{L} = \frac{V_{OUT}}{V_{IN} \times f_I} \times \frac{V_{IN} - V_{OUT}}{L}$$

(1)

$$\frac{V_{IN}}{12} \frac{V_{OUT}}{12} \frac{I_{RIPPLE}}{13.3} \frac{I_{RIPPLE}}{12}$$

(1)

$$\frac{12}{12} \frac{1.8}{1.2} \frac{2.25}{2.25}$$

(1)

$$\frac{8}{1.8} \frac{1.8}{2.91}$$

(1)

$$\frac{8}{1.2} \frac{1.2}{2.12}$$

(2)

$$\frac{12}{5} \frac{3.3}{3.3} \frac{2.34}{2.4}$$

(1)

Schematic

| V <sub>IN</sub> | V <sub>OUT</sub> | I <sub>RIPPLE</sub> |

|-----------------|------------------|---------------------|

| 5               | 1.2              | 1.9                 |

Ceramic capacitors are selected for the output capacitors. The minimum value is determined by output voltage ripple considerations:

$$C_{OUT(\min)} = \frac{I_{RIPPLE}}{8 \times f \times V_{RIPPLE}} = \frac{5A}{8 \times 300 \ kHz \times 0.018 \ V} = 116 \ \mu F$$

(2)

Three 47-mF ceramic capacitors are selected to handle the worst case ripple current of 5 A when V<sub>IN</sub> = 12 V and V<sub>OUT</sub> = 3.3 V. As the output voltage gets lower, the corresponding ripple current is reduced, so excessive output voltage ripple should not be an issue.

#### 3.2 MOSFET Selection

The power MOSFET selection is made with the knowledge that it is difficult to choose one set of components that are optimal over the entire operation range. From maximum V<sub>IN</sub> to minimum V<sub>IN</sub>, the switch duty cycle can vary from approximately 10% to over 66%. The Vishay Si7860DP is found to be a robust choice for both upper and lower positions with 8-mW RDS(on) and less than 30-nC gate charge to keep switching losses low. D1 is included to add to provide maximum boost voltage when V<sub>IN</sub> is a the low end of its range.

#### 3.3 Frequency Feedforward Resistor Selection

To program the switching frequency of 300 kHz, R2 is selected according to the equation from the TPS40070/1/2Midrange Input Synchronous Buck Controller data sheet:

$$R_t = R = \frac{1}{F_{SW} \times 17.82 \times 10^{-6}} - 23 = 164 \, k\Omega \tag{3}$$

A standard 1% value of 165 k $\Omega$  is selected.

After the switching frequency is selected, the value of Rkff would normally be selected to program the minimum desired start-up voltage by rearranging the equation for V<sub>UVLO ON</sub>. However, the UVLO threshold is not a tightly controlled specification, so a low value start-up voltage cannot be accurately programmed. In this case, the converter will be allowed to start at the fixed UVLO threshold of 4.5 V. This requires that the value of Rkff should be selected to be less than the minimum value on the programmable UVLO  $V_{ON}$  and  $V_{OFF}$  versus  $R_{kff}$  graph in the TPS40070/1/2Midrange Input Synchronous Buck Controller data sheet. In this converter, Rkff is selected to be 75 kΩ.

#### 3.4 Output Voltage Setpoint

The output voltage can be easily adjusted from 1.2 V to 3.3 V by changing the value of R3 from its nominal value. Equation 4 is derived from the output voltage divider R7 and R3, and the internal reference of 0.7 V.

$$R3 = \left(\frac{0.7 \, V \times R7}{V_{OUT} - 0.7}\right) \tag{4}$$

R3 VALUE (Ω) VOUT 1.2 V 35.7 k 1.8 V 16.2 k 3.3 V 6.81 k

The following table specifies the value of R3 for  $V_{OUT}$  ranging from 1.2 V to 3.3 V.

#### 3.5 Short Circuit Protection Resistor Selection

The current limit resistor, R9, is selected using Equation 5:

$$R_{LIM} = \frac{I_{LIM} \times R_{DS(on)} - V_{ILIM(offset)}}{I_{SNK}}$$

TRUMENTS

(5)

#### where

- $I_{LIM} = I_{OUT}$  (maximum) × 1.3

- $R_{DS(on)} = 0.0085 \Omega \times 1.3$  (for temperature correction)

- V<sub>LIM(offset)</sub> = -0.030 V

- I<sub>SNK</sub> = 80 mA

Using these conditions leads to selection of R9 = 1.4 k $\Omega$ . The capacitor C7 is chosen to be 10 pF to program a brief blanking interval.

#### 3.6 Miscellaneous Parts

Locations for R4 and R11 are present but shorted out in this EVM. The locations were kept to allow evaluation of other MOSFETs and snubbers. C13 is populated with a 2.2 nF to shunt some of the high frequency ringing on the switch node to ground. Since this EVM has a start-up voltage below 6.2 V, R10 is populated with 330 k $\Omega$  as required in the data sheet.

#### 3.7 Control Loop Compensation

The TPS40071 incorporates voltage mode control with feedforward compensation to minimize gain variations with a variable supply voltage. A type-3 compensation circuit is used to provide two zeroes and three poles as detailed below.

The power circuit LC double pole corner frequency,  $f_C$ , is found to be 10.6 kHz, and the output capacitor ESR zero occurs in the vicinity of 1.1 MHz. The first pole is located at placed at the origin to improve dc regulation.

The first zero is placed at 758 Hz:

$$f_{Z1} = \frac{1}{2 \times \pi \times (R_7 + R_8) \times C6}$$

(6)

The second zero is selected to be near the LC corner frequency at 10.4 kHz:

$$f_{Z1} = \frac{1}{2 \times \pi \times R_5 \times C_6} \tag{7}$$

The second and third poles are placed at 192 kHz and 194 kHz to roll off the high frequency gain:

$$f_{P2} = \frac{1}{2 \times \pi \times R_5 \times \left(\frac{C_4 - C_5}{(C_4 + C_5)}\right)}$$

(8)

$$f_{P3} = \frac{1}{2 \times \pi \times R_8 \times C_6} \tag{9}$$

# 4 Test Setup

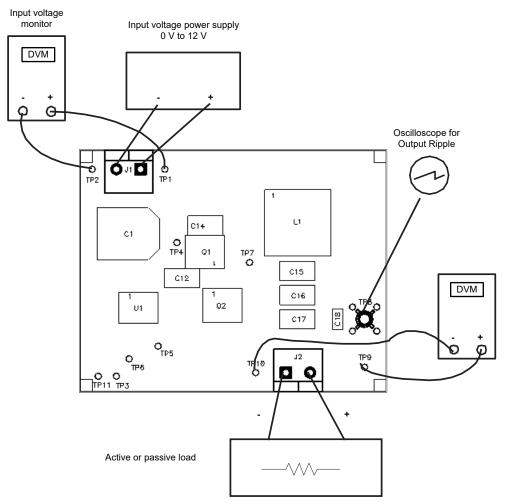

Figure 4-1 shows the basic test setup to power up the TPS40071EVM-001.. The input power source should be capable of supplying the input current to the EVM operating in the intended conditions. This input current can be estimated by Equation 10, which allows for approximately 20% headroom over the actual input current requirement:

$$I_{IN} = \frac{V_{OUT} \times I_{OUT}}{V_{IN} \times 0.7}$$

(10)

It is extremely important to monitor  $V_{IN}$  and  $V_{OUT}$  at the test jacks provided to perform accurate efficiency and regulation tests. Voltage drops through the connectors and input/output wiring can contribute significant errors in these measurements.

Some components are omitted for clarity. See Figure 6-1 for more detail.

Figure 4-1. TPS40071EVM-001 Test Setup

## 5 Results

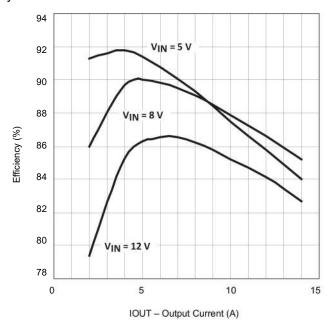

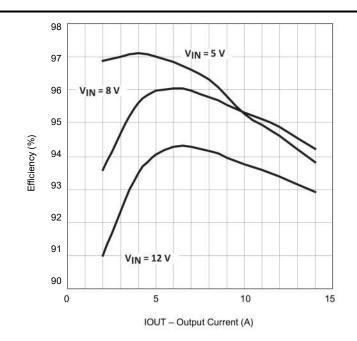

Figure 5-1 through Figure 5-3 show the efficiency of the TPS40071EVM–001 with  $V_{OUT}$  = 1.2 V, 1.8 V, and 3.3 V in Figure 5-1, Figure 5-2, and Figure 5-3, respectively. The converter is seen to perform very efficiently throughout the operating range. With  $V_{IN}$  = 5 V, the gate drive is reduced and the efficiency can be seen to decrease more rapidly as load current increases.

96 V<sub>IN</sub> = 5 V 94 V<sub>IN</sub> = 8 V 92 Efficiency (%) 90 88 86 VIN = 12 V 84 82 10 0 5 15 IOUT - Output Current (A)

Figure 5-1. Efficiency vs Output Current (V<sub>OUT</sub> = 1.2 V)

Figure 5-2. Efficiency vs Output Current (V<sub>OUT</sub> = 1.8 V)

## Figure 5-3. Efficiency vs Output Current (V<sub>OUT</sub> = 3.3 V)

The total watts loss is relatively constant as the output voltage varies from 1.2 V to 3.3 V, but the output power varies with  $V_{OUT}$ . This causes the measured efficiency to decrease markedly as the output voltage is lowered.

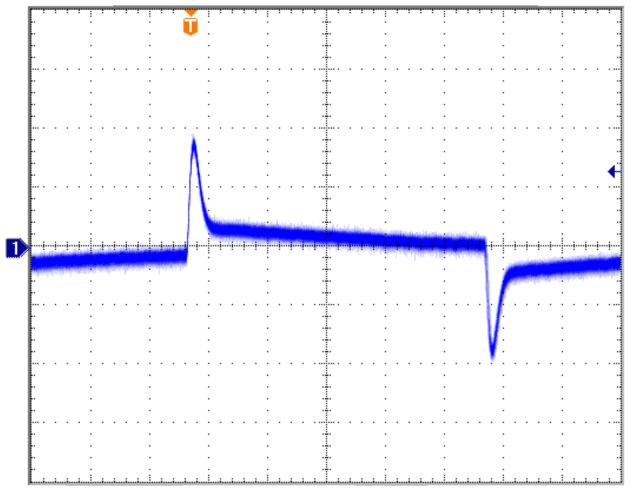

The transient response for a 50% load step (from 2.5 A to 7.5 A) is shown in Figure 5-4 for  $V_{IN}$  = 12 V, and is essentially unchanged with  $V_{IN}$  = 8 V or 5 V.

#### **5.1 Control Loop Characteristics**

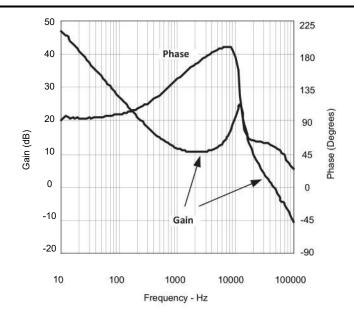

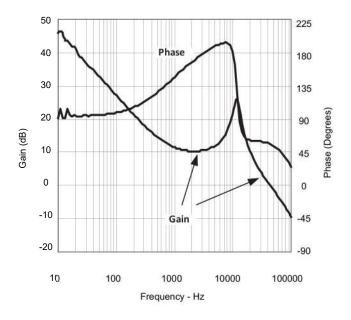

A signal can be injected across R12 at TP3 and TP6 to examine the gain and phase frequency response of this circuit with a network analyzer. Figure 5-5 and Figure 5-6 detail the loop gain and phase with  $V_{IN} = 5$  V and  $V_{IN} = 12$  V. Due to the feedforward circuitry implemented in the circuit, the gain is seen to be relatively constant as  $V_{IN}$  varies more than 2 to 1. There is approximately 50 degrees of phase margin at the loop crossover frequency near 45 kHz.

Figure 5-5. Gain/Phase vs Frequency (V<sub>IN</sub> = 5 V)

Figure 5-6. Gain/Phase vs Frequency (V<sub>IN</sub> = 12 V)

## 6 Assembly Drawing and PCB Layout

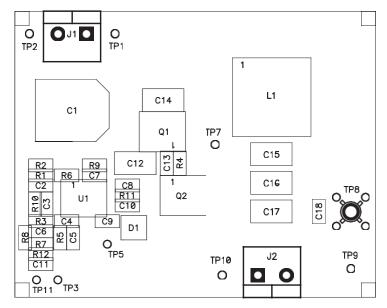

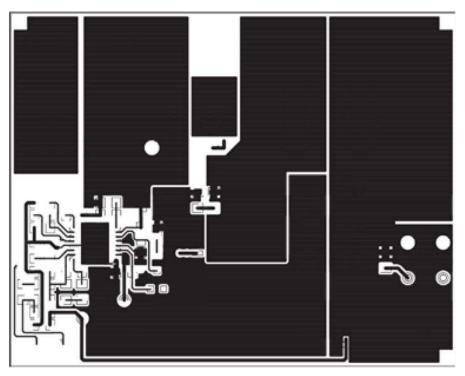

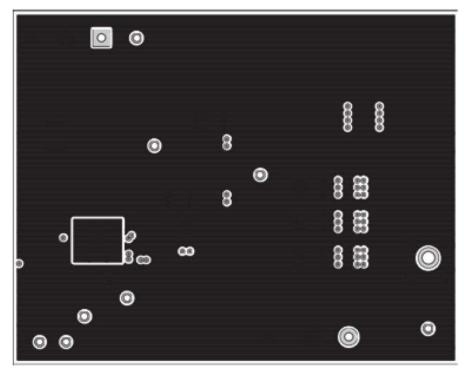

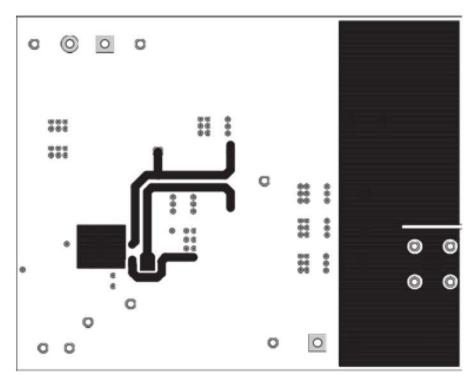

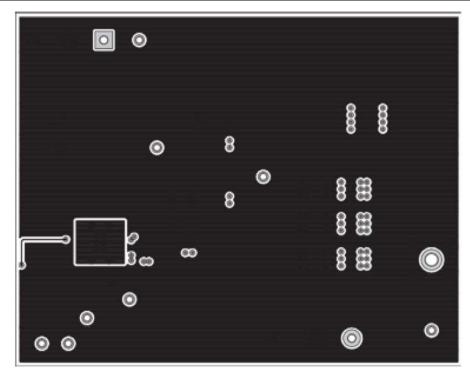

Figure 6-1 through Figure 6-5 show the assembly drawing that shows the PCB outline and the parts placement.

Figure 6-1. Assembly Drawing

Figure 6-2. Top Layer Copper

Figure 6-3. Inner Layer 1 Copper

Figure 6-4. Inner Layer 2 Copper

Figure 6-5. Bottom Layer Copper

# 7 List of Materials

#### Table 7-1. Evaluation Module List of Materials

|                       |     | 7-1. Evaluation Module List                                |                   |                 |

|-----------------------|-----|------------------------------------------------------------|-------------------|-----------------|

| REFERENCE             | QTY | DESCRIPTION                                                | MANUFACTURER      | PARTNUMBER      |

| C1                    | 1   | Capacitor,aluminum, 470<br>mF, 25 V, 20%, 0.457 ×<br>0.406 | Panasonic         | EEVFK1E471P     |

| C12, C14              | 2   | Capacitor,ceramic, 22 mF, 16 V, X5R, 20%, 1812             | TDK               | C4532X5R1C226MT |

| C13                   | 1   | Capacitor,ceramic, 2.2 nF, 50 V, X7R, 10%, 805             | Vishay            | VJ0805Y222KXAAT |

| C15, C16, C17         | 3   | Capacitor,ceramic, 47 mF,<br>6.3 V, X5R, 20%, 1812         | TDK               | C4532X5R0J47MT  |

| C2, C8, C10, C11, C18 | 5   | Capacitor,ceramic, 0.1 mF, 25 V, X7R, 10%, 805             | Vishay            | VJ0805Y104KXXAT |

| C3                    | 1   | Capacitor,ceramic, 10 nF,<br>50 V, X7R, 10%, 805           | Vishay            | VJ0805Y103KXAAT |

| C4                    | 1   | Capacitor,ceramic, 470 pF,<br>50 V, X7R, 10%, 805          | Vishay            | VJ0805Y471KXAAT |

| C5, C6                | 2   | Capacitor,ceramic, 8200<br>pF, 50 V, X7R, 10%, 805         | Vishay            | VJ0805Y822KXAAT |

| C7                    | 1   | Capacitor,ceramic, 10 pF,<br>50 V, NPO, 10%, 805           | Vishay            | VJ0805A100KXAAT |

| C9                    | 1   | Capacitor,ceramic, 1 mF, 16 V, X5R, 10%, 805               | TDK               | C2012X5R1C105KT |

| D1                    | 1   | Diode, schottky, 200 mA,<br>30 V, SOT23                    | Vishay- Liteon    | BAT54           |

| J1, J2                | 2   | Terminal block, 2 pin, 15<br>A, 5.1 mm, 0.40 × 0.35        | OST               | ED1609          |

| L1                    | 1   | Inductor, SMT, 1.6 mH,<br>14.5 A, 2.5 mW, 0.515 ×<br>0.516 | COEV              | DXM1306-1R6     |

| Q1, Q2                | 2   | MOSFET, N-channel, 30<br>V, 18 A, 8.0 mW,<br>PWRPAK S0-8   | Vishay– Siliconix | Si7860DP        |

| R1                    | 1   | Resistor,chip, 10 kΩ, 1/10<br>W, 1%, 805                   | Std               | Std             |

| R10                   | 1   | Resistor,chip, 330 kΩ,<br>1/10 W, 5%, 805                  | Std               | Std             |

| R12                   | 1   | Resistor, chip, 20 Ω, 1/10<br>W, 5%, 805                   | Std               | Std             |

| R2                    | 1   | Resistor,chip, 165 kΩ,<br>1/10 W, 1%, 805                  | Std               | Std             |

| R3                    | 1   | Resistor,chip, 16.2 kΩ,<br>1/10 W, 1%, 805                 | Std               | Std             |

| R4, R11               | 2   | Resistor,chip, 0 Ω, 1/10 W, 5%, 805                        | Std               | Std             |

| R5                    | 1   | Resistor,chip, 1.87 kΩ,<br>1/10 W, 1%, 805                 | Std               | Std             |

| R6                    | 1   | Resistor,chip, 75 kΩ, 1/10<br>W, 1%, 805                   | Std               | Std             |

| R7                    | 1   | Resistor, chip, 25.5 kΩ, 1/10 W, 1%, 805                   | Std               | Std             |

| R8                    | 1   | Resistor, chip, 100 Ω, 1/10<br>W, 1%, 805                  | Std               | Std             |

| R9                    | 1   | Resistor, chip, 1.4 kΩ, 1/10 W, 1%, 805                    | Std               | Std             |

| REFERENCE                                  | QTY | DESCRIPTION                                         | MANUFACTURER      | PARTNUMBER  |  |

|--------------------------------------------|-----|-----------------------------------------------------|-------------------|-------------|--|

| TP1, TP3, TP4, TP5, TP6,<br>TP7, TP9, TP11 | 8   | Jack, test point, red                               | Farnell           | 240-345     |  |

| TP2, TP10                                  | 2   | Jack, test point, black                             | Farnell           | 240-333     |  |

| TP8                                        | 1   | Adaptor, 3.5-mm probe<br>clip (or 131–5031–00), 0.2 | Tektronix         | 131-4244-00 |  |

| U1                                         | 1   | IC, PWP16                                           | Texas Instruments | TPS40071PWP |  |

|                                            | 1   | PCB, 2.5 inch × 2 inch ×<br>0.062 inch              | Std               | HPA038      |  |

Table 7-1. Evaluation Module List of Materials (continued)

#### 8 Reference

Texas Instruments, TPS40070/1/2Midrange Input Synchronous Buck Controller data sheet

#### **9** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision A (July 2006) to Revision B (February 2022) |                                                                                                |   |  |

|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------|---|--|

| •                                                                 | Updated the numbering format for tables, figures, and cross-references throughout the document | 2 |  |

| •                                                                 | Updated the user's guide title                                                                 | 2 |  |

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated