# High Speed, Dual, 2 A MOSFET Driver

## ADP3629/ADP3630/ADP3631

#### **FEATURES**

Industry-standard-compatible pinout

High current drive capability

Precise threshold shutdown comparator

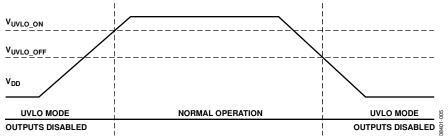

UVLO with hysteresis

Overtemperature warning signal

Overtemperature shutdown

3.3 V-compatible inputs

Rise time and fall time: 10 ns typical at 2.2 nF load

Fast propagation delay

Matched propagation delays between channels

Supply voltage: 9.5 V to 18 V

Dual outputs can be operated in parallel

(ADP3629/ADP3630)

Rated from -40°C to +85°C ambient temperature

#### **APPLICATIONS**

AC-to-DC switch mode power supplies DC-to-DC power supplies Synchronous rectification Motor drives

8-lead SOIC\_N and 8-lead MSOP

#### **GENERAL DESCRIPTION**

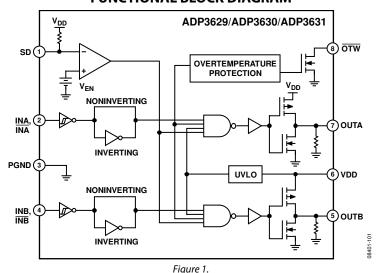

The ADP3629/ADP3630/ADP3631 are dual, high current, high speed drivers, capable of driving two independent N-channel power MOSFETs. The ADP3629/ADP3630/ADP3631 use the industry-standard footprint but add high speed switching performance and improved system reliability.

The ADP3629/ADP3630/ADP3631 have an internal temperature sensor and provide two levels of overtemperature protection: an overtemperature warning and an overtemperature shutdown at extreme junction temperatures.

The SD function, generated from a precise internal comparator, provides fast system enable or shutdown. This feature allows redundant overvoltage protection, complementing the protection inside the main controller device, or provides safe system shutdown in the event of an overtemperature warning.

The wide input voltage range allows the driver to be compatible with both analog and digital PWM controllers.

Digital power controllers are supplied from a low voltage supply, and the driver is supplied from a higher voltage supply. The ADP3629/ADP3630/ADP3631 add UVLO and hysteresis functions, allowing safe startup and shutdown of the higher voltage supply when used with low voltage digital controllers.

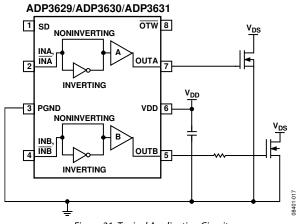

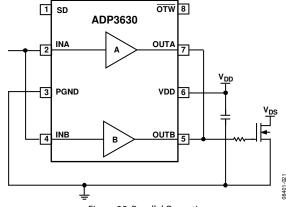

### **FUNCTIONAL BLOCK DIAGRAM**

## **TABLE OF CONTENTS**

| Features                                     | 1 |

|----------------------------------------------|---|

| Applications                                 | 1 |

| General Description                          | 1 |

| Functional Block Diagram                     | 1 |

| Revision History                             | 2 |

| Specifications                               | 3 |

| Timing Diagrams                              | 4 |

| Absolute Maximum Ratings                     | 6 |

| Thermal Resistance                           | 6 |

| ESD Caution                                  | 6 |

| Pin Configurations and Function Descriptions | 7 |

| Typical Performance Characteristics          | 8 |

| Test Circuit                                                                                       |

|----------------------------------------------------------------------------------------------------|

| Theory of Operation                                                                                |

| Input Drive Requirements (INA, $\overline{\text{INA}}$ , INB, $\overline{\text{INB}}$ , and SD) 11 |

| Low-Side Drivers (OUTA, OUTB)11                                                                    |

| Shutdown (SD) Function                                                                             |

| Overtemperature Protections                                                                        |

| Supply Capacitor Selection                                                                         |

| PCB Layout Considerations                                                                          |

| Parallel Operation                                                                                 |

| Thermal Considerations                                                                             |

| Outline Dimensions                                                                                 |

| Ordering Guide14                                                                                   |

### **REVISION HISTORY**

9/09—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{\rm DD}$  = 12 V,  $T_{\rm J}$  = -40°C to +125°C, unless otherwise noted.  $^1$

Table 1.

| Parameter                               | Symbol                 | Test Conditions/Comments                               | Min  | Тур  | Max  | Unit |

|-----------------------------------------|------------------------|--------------------------------------------------------|------|------|------|------|

| SUPPLY                                  |                        |                                                        |      |      |      |      |

| Supply Voltage Range                    | $V_{DD}$               |                                                        | 9.5  |      | 18   | V    |

| Supply Current                          | $I_{DD}$               | No switching, INA, INA, INB, and INB                   |      | 1.2  | 3    | mA   |

|                                         |                        | disabled                                               |      |      |      |      |

| Standby Current                         | I <sub>SBY</sub>       | SD = 5 V                                               |      | 1.2  | 3    | mA   |

| UVLO                                    |                        |                                                        |      |      |      |      |

| Turn-On Threshold Voltage               | $V_{UVLO\_ON}$         | $V_{DD}$ rising, $T_A = 25^{\circ}C$                   | 8.0  | 8.7  | 9.5  | V    |

| Turn-Off Threshold Voltage              | $V_{\text{UVLO\_OFF}}$ | $V_{DD}$ falling, $T_A = 25$ °C                        | 7.0  | 7.7  | 8.5  | V    |

| Hysteresis                              |                        |                                                        |      | 1.0  |      | V    |

| DIGITAL INPUTS (INA, INA, INB, INB, SD) |                        |                                                        |      |      |      |      |

| Input Voltage High                      | VIH                    |                                                        | 2.0  |      |      | V    |

| Input Voltage Low                       | VIL                    |                                                        |      |      | 8.0  | V    |

| Input Current                           | I <sub>IN</sub>        | $0 \text{ V} < V_{IN} < V_{DD}$                        | -20  |      | +20  | μΑ   |

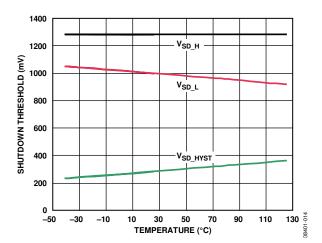

| SD Threshold High                       | $V_{\text{SD\_H}}$     |                                                        | 1.19 | 1.28 | 1.38 | V    |

|                                         |                        | T <sub>A</sub> = 25°C                                  | 1.21 | 1.28 | 1.35 | V    |

| SD Threshold Low                        | $V_{\text{SD\_L}}$     | T <sub>A</sub> = 25°C                                  | 0.95 | 1.0  | 1.05 | V    |

| SD Hysteresis                           | $V_{\text{SD\_HYST}}$  | T <sub>A</sub> = 25°C                                  | 240  | 280  | 320  | mV   |

| Internal Pull-Up/Pull-Down Current      |                        |                                                        |      | 6    |      | μΑ   |

| OUTPUTS (OUTA, OUTB)                    |                        |                                                        |      |      |      |      |

| Output Resistance, Unbiased             |                        | VDD = PGND                                             |      | 80   |      | kΩ   |

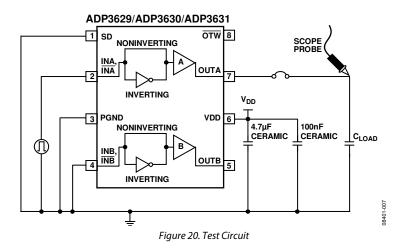

| Peak Source Current                     |                        | See Figure 20                                          |      | 2    |      | Α    |

| Peak Sink Current                       |                        | See Figure 20                                          |      | -2   |      | Α    |

| SWITCHING TIME                          |                        |                                                        |      |      |      |      |

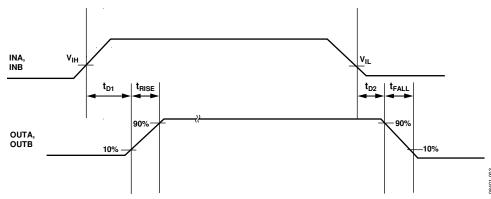

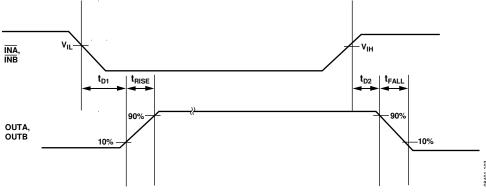

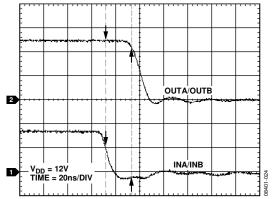

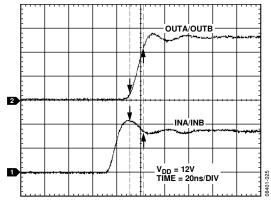

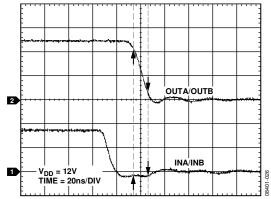

| OUTA, OUTB Rise Time                    | t <sub>RISE</sub>      | C <sub>LOAD</sub> = 2.2 nF, see Figure 3 and Figure 4  |      | 10   | 25   | ns   |

| OUTA, OUTB Fall Time                    | t <sub>FALL</sub>      | $C_{LOAD} = 2.2 \text{ nF, see Figure 3 and Figure 4}$ |      | 10   | 25   | ns   |

| OUTA, OUTB Rising Propagation Delay     | t <sub>D1</sub>        | $C_{LOAD} = 2.2 \text{ nF, see Figure 3 and Figure 4}$ |      | 14   | 30   | ns   |

| OUTA, OUTB Falling Propagation Delay    | $t_{D2}$               | $C_{LOAD} = 2.2 \text{ nF, see Figure 3 and Figure 4}$ |      | 22   | 35   | ns   |

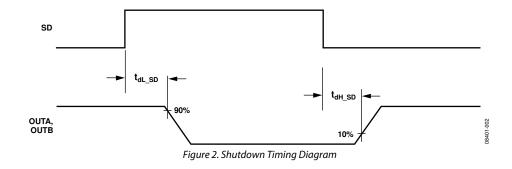

| SD Propagation Delay Low                | t <sub>dL_SD</sub>     | See Figure 2                                           |      | 32   | 45   | ns   |

| SD Propagation Delay High               | $t_{\text{dH\_SD}}$    | See Figure 2                                           |      | 48   | 75   | ns   |

| Delay Matching Between Channels         |                        |                                                        |      | 2    |      | ns   |

| OVERTEMPERATURE PROTECTION              |                        |                                                        |      |      |      |      |

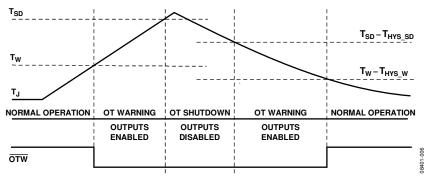

| Overtemperature Warning Threshold       | Tw                     | See Figure 6                                           | 120  | 135  | 150  | °C   |

| Overtemperature Shutdown Threshold      | T <sub>SD</sub>        | See Figure 6                                           | 150  | 165  | 180  | °C   |

| Temperature Hysteresis for Shutdown     | T <sub>HYS_SD</sub>    | See Figure 6                                           |      | 30   |      | °C   |

| Temperature Hysteresis for Warning      | T <sub>HYS_W</sub>     | See Figure 6                                           |      | 10   |      | °C   |

| Overtemperature Warning Low             | $V_{\text{OTW\_OL}}$   | Open drain, –500 μA                                    |      |      | 0.4  | V    |

$<sup>^1\,\</sup>text{All limits at temperature extremes guaranteed via correlation using standard statistical quality control (SQC) methods.}$

### **TIMING DIAGRAMS**

Figure 3. Output Timing Diagram (Noninverting)

Figure 4. Output Timing Diagram (Inverting)

Figure 5. UVLO Function

Figure 6. Overtemperature Warning and Shutdown

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Table 2.                                       |                                            |

|------------------------------------------------|--------------------------------------------|

| Parameter                                      | Rating                                     |

| VDD                                            | -0.3 V to +20 V                            |

| OUTA, OUTB                                     |                                            |

| DC                                             | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| <200 ns                                        | $-2 \text{ V to V}_{DD} + 0.3 \text{ V}$   |

| INA, <del>INA</del> , INB, <del>INB</del> , SD | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| ESD                                            |                                            |

| Human Body Model (HBM)                         | 3.5 kV                                     |

| Field Induced Charged Device<br>Model (FICDM)  |                                            |

| SOIC_N                                         | 1.5 kV                                     |

| MSOP                                           | 1.0 kV                                     |

| Junction Temperature Range                     | −40°C to +150°C                            |

| Storage Temperature Range                      | −65°C to +150°C                            |

| Lead Temperature                               |                                            |

| Soldering (10 sec)                             | 300°C                                      |

| Vapor Phase (60 sec)                           | 215°C                                      |

| Infrared (15 sec)                              | 260°C                                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for a device soldered in a 4-layer circuit board and is measured per JEDEC standards JESD51-2, JESD51-5, and JESD51-7.

**Table 3. Thermal Resistance**

| Package Type  | θιΑ   | Unit |

|---------------|-------|------|

| 8-Lead SOIC_N | 110.6 | °C/W |

| 8-Lead MSOP   | 162.2 | °C/W |

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

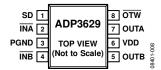

Figure 7. ADP3629 Pin Configuration

**Table 4. ADP3629 Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                |

|---------|----------|--------------------------------------------------------------------------------------------|

| 1       | SD       | Output Shutdown. When high, this pin disables normal operation, forcing OUTA and OUTB low. |

| 2       | ĪNĀ      | Inverting Input Pin for Channel A Gate Driver.                                             |

| 3       | PGND     | Ground. This pin should be closely connected to the source of the power MOSFET.            |

| 4       | ĪNB      | Inverting Input Pin for Channel B Gate Driver.                                             |

| 5       | OUTB     | Output Pin for Channel B Gate Driver.                                                      |

| 6       | VDD      | Power Supply Voltage. Bypass this pin to PGND with a 1 μF to 5 μF ceramic capacitor.       |

| 7       | OUTA     | Output Pin for Channel A Gate Driver.                                                      |

| 8       | OTW      | Overtemperature Warning Flag. Open drain, active low.                                      |

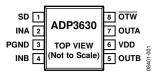

Figure 8. ADP3630 Pin Configuration

**Table 5. ADP3630 Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                |

|---------|----------|--------------------------------------------------------------------------------------------|

| 1       | SD       | Output Shutdown. When high, this pin disables normal operation, forcing OUTA and OUTB low. |

| 2       | INA      | Input Pin for Channel A Gate Driver.                                                       |

| 3       | PGND     | Ground. This pin should be closely connected to the source of the power MOSFET.            |

| 4       | INB      | Input Pin for Channel B Gate Driver.                                                       |

| 5       | OUTB     | Output Pin for Channel B Gate Driver.                                                      |

| 6       | VDD      | Power Supply Voltage. Bypass this pin to PGND with a 1 μF to 5 μF ceramic capacitor.       |

| 7       | OUTA     | Output Pin for Channel A Gate Driver.                                                      |

| 8       | OTW      | Overtemperature Warning Flag. Open drain, active low.                                      |

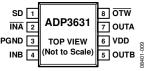

Figure 9. ADP3631 Pin Configuration

**Table 6. ADP3631 Pin Function Descriptions**

| Pin No. | Mnemonic | Description                                                                                |

|---------|----------|--------------------------------------------------------------------------------------------|

| 1       | SD       | Output Shutdown. When high, this pin disables normal operation, forcing OUTA and OUTB low. |

| 2       | ĪNĀ      | Inverting Input Pin for Channel A Gate Driver.                                             |

| 3       | PGND     | Ground. This pin should be closely connected to the source of the power MOSFET.            |

| 4       | INB      | Input Pin for Channel B Gate Driver.                                                       |

| 5       | OUTB     | Output Pin for Channel B Gate Driver.                                                      |

| 6       | VDD      | Power Supply Voltage. Bypass this pin to PGND with a 1 μF to 5 μF ceramic capacitor.       |

| 7       | OUTA     | Output Pin for Channel A Gate Driver.                                                      |

| 8       | OTW      | Overtemperature Warning Flag. Open drain, active low.                                      |

### TYPICAL PERFORMANCE CHARACTERISTICS

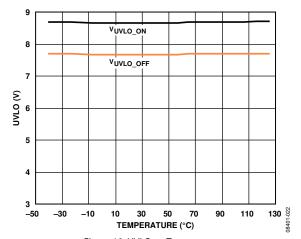

Figure 10. UVLO vs. Temperature

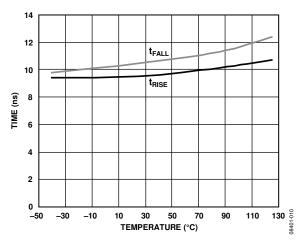

Figure 11. Rise and Fall Times vs. Temperature

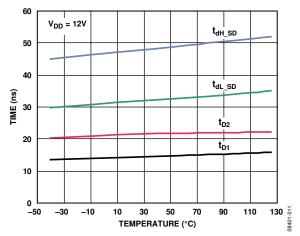

Figure 12. Propagation Delay vs. Temperature

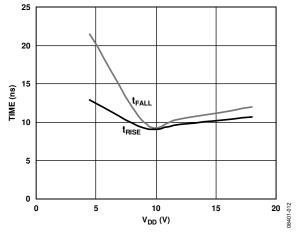

Figure 13. Rise and Fall Times vs.  $V_{DD}$

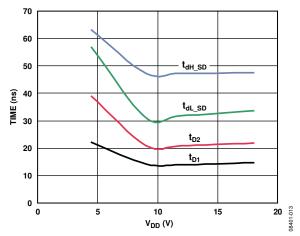

Figure 14. Propagation Delay vs. V<sub>DD</sub>

Figure 15. Shutdown Threshold vs. Temperature

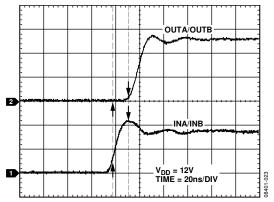

Figure 16. Typical Rising Propagation Delay (Noninverting)

Figure 17. Typical Falling Propagation Delay (Noninverting)

Figure 18. Typical Rise Time (Noninverting)

Figure 19. Typical Fall Time (Noninverting)

### **TEST CIRCUIT**

### THEORY OF OPERATION

The ADP3629/ADP3630/ADP3631 family of dual drivers is optimized for driving two independent enhancement N-channel MOSFETs or insulated gate bipolar transistors (IGBTs) in high switching frequency applications.

These applications require high speed, fast rise and fall times, and short propagation delays. The capacitive nature of MOSFETs and IGBTs requires high peak current capability, as well.

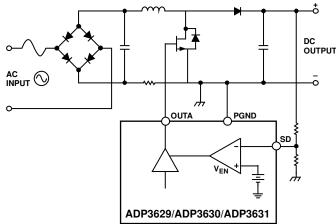

Figure 21. Typical Application Circuit

# INPUT DRIVE REQUIREMENTS (INA, INA, INB, INB, AND SD)

The inputs of the ADP3629/ADP3630/ADP3631 are designed to meet the requirements of modern digital power controllers; the signals are compatible with 3.3 V logic levels. At the same time, the input structure allows for input voltages as high as  $V_{\rm DD}$ .

The signals applied to the inputs (INA, INA, INB, and INB) should have steep and clean fronts. It is not recommended that slow changing signals be applied to drive these inputs because such signals can result in multiple switching output signals when the thresholds are crossed, causing damage to the power MOSFET or IGBT.

An internal pull-down resistor is present at the input, which guarantees that the power device is off in the event that the input is left floating.

The SD input has a precision comparator with hysteresis and is therefore suitable for slow changing signals (such as a scaled-down output voltage); see the Shutdown (SD) Function section for more information about this comparator.

### **LOW-SIDE DRIVERS (OUTA, OUTB)**

The ADP3629/ADP3630/ADP3631 family of dual drivers is designed to drive ground referenced N-channel MOSFETs. The bias is internally connected to the  $V_{\text{DD}}$  supply and to PGND.

When the ADP3629/ADP3630/ADP3631 are disabled, both low-side gates are held low. An internal impedance is present between the OUTA/OUTB pins and GND, even when  $V_{\rm DD}$  is not present; this feature ensures that the power MOSFET is normally off when bias voltage is not present.

When interfacing the ADP3629/ADP3630/ADP3631 to external MOSFETs, the designer should consider ways to create a robust design that minimizes stresses on both the driver and the MOSFETs. These stresses include exceeding the short time duration voltage ratings on the OUTA and OUTB pins, as well as on the external MOSFET.

Power MOSFETs are usually selected to have low on resistance to minimize conduction losses, which usually implies a large input gate capacitance and gate charge.

#### **SHUTDOWN (SD) FUNCTION**

The ADP3629/ADP3630/ADP3631 feature an advanced shutdown function with accurate thresholds and hysteresis.

The SD signal is an active high signal. An internal pull-up is present on this pin and, therefore, it is necessary to pull down the pin externally for the drivers to operate normally.

In some power systems, it is sometimes necessary to provide an additional overvoltage protection (OVP) or overcurrent protection (OCP) shutdown signal to turn off the power devices (MOSFETs or IGBTs) in case of failure of the main controller.

An accurate internal reference is used for the SD comparator so that it can be used to detect OVP or OCP fault conditions.

Figure 22. Shutdown Function Used for Redundant OVP

08401-018

#### **OVERTEMPERATURE PROTECTIONS**

The ADP3629/ADP3630/ADP3631 provide two levels of overtemperature protection:

- Overtemperature warning (OTW)

- Overtemperature shutdown

The overtemperature warning is an open-drain logic signal and is active low. In normal operation, when no thermal warning is present, the signal is high, whereas when the warning threshold is crossed, the signal is pulled low.

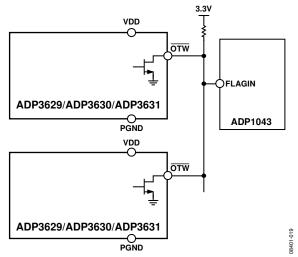

Figure 23. OTW Signaling Scheme Example

The OTW open-drain configuration allows the connection of multiple devices to the same warning bus in a wire-ORed configuration, as shown in Figure 23.

The overtemperature shutdown turns off the device to protect it in the event that the die temperature exceeds the absolute maximum limit of 150°C (see Table 2).

#### **SUPPLY CAPACITOR SELECTION**

A local bypass capacitor for the supply input (VDD) of the ADP3629/ADP3630/ADP3631 is recommended to reduce the noise and to supply some of the peak currents that are drawn.

An improper decoupling can dramatically increase the rise times, cause excessive resonance on the OUTA and OUTB pins, and, in some extreme cases, even damage the device due to inductive overvoltage on the VDD or OUTA/OUTB pins.

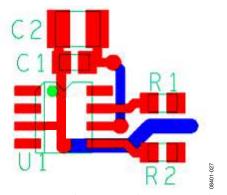

The minimum capacitance required is determined by the size of the gate capacitances being driven, but as a general rule, a 4.7  $\mu F$ , low ESR capacitor should be used. Multilayer ceramic chip (MLCC) capacitors provide the best combination of low ESR and small size. To further reduce noise, use a smaller ceramic capacitor (100 nF) with a better high frequency characteristic in parallel with the main capacitor.

Place the ceramic capacitor as close as possible to the ADP3629/ADP3630/ADP3631 device and minimize the length of the traces going from the capacitor to the power pins of the device.

#### **PCB LAYOUT CONSIDERATIONS**

Use the following general guidelines when designing printed circuit boards (PCBs) for the ADP3629/ADP3630/ADP3631:

- Trace out the high current paths and use short, wide

(>40 mil) traces to make these connections.

- Minimize trace inductance between the OUTA and OUTB outputs and the MOSFET gates.

- Connect the PGND pin as close as possible to the source of the MOSFETs.

- Place the VDD bypass capacitor as close as possible to the VDD and PGND pins.

- When possible, use vias to other layers to maximize thermal conduction away from the IC.

Figure 24 shows an example of the typical layout based on the preceding guidelines.

Figure 24. External Component Placement Example

#### **PARALLEL OPERATION**

The two driver channels in the ADP3629 and ADP3630 devices can be combined to operate in parallel to increase drive capability and minimize power dissipation in the driver.

The connection scheme for the ADP3630 is shown in Figure 25. In this configuration, INA and INB are connected together, and OUTA and OUTB are connected together.

Particular attention must be paid to the layout in this case to optimize load sharing between the two drivers.

Figure 25. Parallel Operation

#### THERMAL CONSIDERATIONS

When designing a power MOSFET gate drive, the maximum power dissipation in the driver must be considered to avoid exceeding the maximum junction temperature.

Data on package thermal resistance is provided in Table 3 to help the designer in this task.

Several equally important aspects must also be considered.

- Gate charge of the power MOSFET being driven

- Bias voltage value used to power the driver

- Maximum switching frequency of operation

- Value of external gate resistance

- Maximum ambient (and PCB) temperature

- Type of package

All of these factors influence and limit the maximum allowable power dissipated in the driver.

The gate of a power MOSFET has a nonlinear capacitance characteristic. For this reason, although the input capacitance is usually reported in the MOSFET data sheet as C<sub>ISS</sub>, it is not useful to calculate power losses.

The total gate charge necessary to turn on a power MOSFET device is usually reported on the device data sheet under  $Q_G$ . This parameter varies from a few nanocoulombs (nC) to several hundreds of nC and is specified at a specific  $V_{GS}$  value (10 V or 4.5 V).

The power necessary to charge and then discharge the gate of a power MOSFET can be calculated as follows:

$$P_{GATE} = V_{GS} \times Q_G \times f_{SW}$$

where

$V_{GS}$  is the bias voltage powering the driver (V<sub>DD</sub>).

$Q_G$  is the total gate charge.

fsw is the maximum switching frequency.

The power dissipated for each gate ( $P_{GATE}$ ) must be multiplied by the number of drivers (in this case, 1 or 2) being used in each package; this  $P_{GATE}$  value represents the total power dissipated in charging and discharging the gates of the power MOSFETs.

Not all of this power is dissipated in the gate driver because part of it is actually dissipated in the external gate resistor,  $R_{\rm G}$ . The larger the external gate resistor, the smaller the amount of power that is dissipated in the gate driver.

In modern switching power applications, the value of the gate resistor is kept at a minimum to increase switching speed and to minimize switching losses.

In all practical applications where the external resistor is in the order of a few ohms, the contribution of the external resistor can be ignored, and the extra loss is assumed to be in the driver, providing a good guard band for the power loss calculations.

In addition to the gate charge losses, there are also dc bias losses ( $P_{\rm DC}$ ) due to the bias current of the driver. This current is present regardless of the switching frequency.

$$P_{DC} = V_{DD} \times I_{DD}$$

The total estimated loss is the sum of  $P_{DC}$  and  $P_{GATE}$ .

$$P_{LOSS} = P_{DC} + (n \times P_{GATE})$$

where n is the number of gates driven.

When the total power loss is calculated, the temperature increase can be calculated as follows:

$$\Delta T_J = P_{LOSS} \times \theta_{JA}$$

### Design Example

For example, consider driving two IRFS4310Z MOSFETs with a  $V_{\rm DD}$  of 12 V at a switching frequency of 100 kHz, using an ADP3630 in the MSOP package.

The maximum PCB temperature considered for this design is 85°C.

From the MOSFET data sheet, the total gate charge is  $Q_G = 120 \text{ nC}$ .

$$P_{GATE} = 12 \text{ V} \times 120 \text{ nC} \times 100 \text{ kHz} = 144 \text{ mW}$$

$$P_{DC} = 12 \text{ V} \times 1.2 \text{ mA} = 14.4 \text{ mW}$$

$$P_{LOSS} = 14.4 \text{ mW} + (2 \times 144 \text{ mW}) = 302.4 \text{ mW}$$

The MSOP thermal resistance is 162.2°C/W (see Table 3).

$$\Delta T_I = 302.4 \text{ mW} \times 162.2 \text{°C/W} = 49.0 \text{°C}$$

$$T_I = T_A + \Delta T_I = 134.0$$

°C  $\leq T_{I MAX}$

This estimated junction temperature does not factor in the power dissipated in the external gate resistor and, therefore, provides a certain guard band.

If a lower junction temperature is required by the design, the SOIC\_N package, which provides a thermal resistance of 110.6°C/W, can be used. Using the SOIC\_N package, the maximum junction temperature is

$$\Delta T_J = 302.4 \text{ mW} \times 110.6^{\circ}\text{C/W} = 33.4^{\circ}\text{C}$$

$$T_J = T_A + \Delta T_J = 118.4$$

°C  $\leq T_{J\_MAX}$

Other options to reduce power dissipation in the driver include reducing the value of the  $V_{\rm DD}$  bias voltage, reducing the switching frequency, and choosing a power MOSFET with a smaller gate charge.

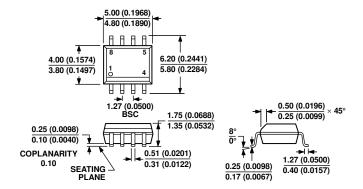

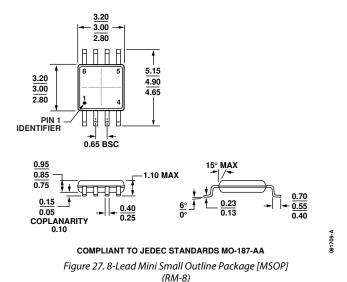

### **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-012-A A

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS

(IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR

REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN.

Figure 26. 8-Lead Standard Small Outline Package [SOIC\_N] Narrow Body (R-8) Dimensions shown in millimeters and (inches)

### **ORDERING GUIDE**

|                             | Temperature    |                                                | Package | Ordering |          |

|-----------------------------|----------------|------------------------------------------------|---------|----------|----------|

| Model                       | Range          | Package Description                            | Option  | Quantity | Branding |

| ADP3629ARZ-R7 <sup>1</sup>  | −40°C to +85°C | 8-Lead Standard Small Outline Package [SOIC_N] | R-8     | 2,500    |          |

| ADP3629ARMZ-R7 <sup>1</sup> | −40°C to +85°C | 8-Lead Mini Small Outline Package [MSOP]       | RM-8    | 3,000    | L8Q      |

| ADP3630ARZ-R7 <sup>1</sup>  | −40°C to +85°C | 8-Lead Standard Small Outline Package [SOIC_N] | R-8     | 2,500    |          |

| ADP3630ARMZ-R7 <sup>1</sup> | −40°C to +85°C | 8-Lead Mini Small Outline Package [MSOP]       | RM-8    | 3,000    | L8R      |

| ADP3631ARZ-R7 <sup>1</sup>  | −40°C to +85°C | 8-Lead Standard Small Outline Package [SOIC_N] | R-8     | 2,500    |          |

| ADP3631ARMZ-R7 <sup>1</sup> | −40°C to +85°C | 8-Lead Mini Small Outline Package [MSOP]       | RM-8    | 3,000    | L8S      |

Dimensions shown in millimeters

<sup>&</sup>lt;sup>1</sup> Z = RoHS Compliant Part.

| ADP3629/ADP3630/ADP363 | 1 |

|------------------------|---|

| ·                      |   |

## **NOTES**

| ٨ | םח | 35 | 29 | /Λ | n | DΣ | ሮን | N | /Λ  |   | DΩ  | ሮን | 1 |

|---|----|----|----|----|---|----|----|---|-----|---|-----|----|---|

| A | U٢ | 30 | ZJ | ΙH | U | rj | กภ | U | / A | Ш | ۲.5 | กภ |   |

NOTES