# STK10C68-M SMD#5962-93056 8K x 8 nvSRAM *QuantumTrap*™ CMOS Nonvolatile Static RAM Obsolete - Not Recommend for new Designs

#### FEATURES

- 25ns, 35ns, 45ns and 55ns Access Times

- STORE to Nonvolatile Elements Initiated by Hardware

- RECALL to SRAM Initiated by Hardware or Power Restore

- Automatic STORE Timing

- 10mA Typical I<sub>cc</sub> at 200ns Cycle Time

- Unlimited READ, WRITE and RECALL Cycles

- 1,000,000 STORE Cycles to Nonvolatile Elements (Industrial/Commercial)

- 100-Year Data Retention (Industrial/Commercial)

- Commercial, Industrial and Military Temperatures

- 28-Pin DIP, SOIC and LCC Packages

#### DESCRIPTION

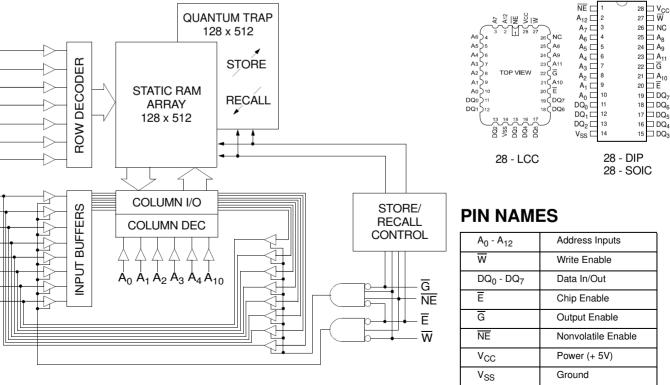

The Simtek STK10C68 is a fast static RAM with a nonvolatile element incorporated in each static memory cell. The SRAM can be read and written an unlimited number of times, while independent nonvolatile data resides in Nonvolatile Elements. Data may easily be transferred from the SRAM to the Nonvolatile Elements (the *STORE* operation), or from the Nonvolatile Elements to the SRAM (the *RECALL* operation), using the NE pin. Transfers from the Nonvolatile Elements to the SRAM (the *RECALL* operation) also take place automatically on restoration of power. The STK10C68 combines the high performance and ease of use of a fast SRAM with nonvolatile data integrity.

The STK10C68 features industry-standard pinout for nonvolatile RAMs. MIL-STD-883 and Standard Military Drawing (SMD #5962-93056) devices are available.

#### **BLOCK DIAGRAM**

$A_5$

$A_6$

$A_7$

$A_8$

Ag

A<sub>11</sub>

A<sub>12</sub>

DQ<sub>0</sub>

DQ<sub>1</sub>

$DQ_2$

$DQ_3$

$DQ_4$

DQ<sub>5</sub>

$DQ_6$

DQ<sub>7</sub>

#### **PIN CONFIGURATIONS**

March 2006

Document Control # ML0006 rev 0.2

### **ABSOLUTE MAXIMUM RATINGS**<sup>a</sup>

| Voltage on Input Relative to Ground                     |

|---------------------------------------------------------|

| Voltage on Input Relative to $V_{SS}$                   |

| Voltage on DQ <sub>0-7</sub>                            |

| Temperature under Bias                                  |

| Storage Temperature65°C to 150°C                        |

| Power Dissipation                                       |

| DC Output Current (1 output at a time, 1s duration)15mA |

## **DC CHARACTERISTICS**

| Note a: | Stresses greater than those listed under "Absolute Maximum           |

|---------|----------------------------------------------------------------------|

|         | Ratings" may cause permanent damage to the device. This is a         |

|         | stress rating only, and functional operation of the device at condi- |

|         | tions above those indicated in the operational sections of this      |

|         | specification is not implied. Exposure to absolute maximum rat-      |

|         | ing conditions for extended periods may affect reliability.          |

#### $(V_{CC} = 5.0V \pm 10\%)$

| SYMBOL             | PARAMETER                                                                         | СОММ                 | ERCIAL                |                      | STRIAL/<br>TARY      | UNITS                | NOTES                                                                                                                                                                                                           |

|--------------------|-----------------------------------------------------------------------------------|----------------------|-----------------------|----------------------|----------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    |                                                                                   | MIN                  | MAX                   | MIN                  | MAX                  |                      |                                                                                                                                                                                                                 |

| I <sub>CC1</sub> b | Average V <sub>CC</sub> Current                                                   |                      | 85<br>75<br>65<br>N/A |                      | 90<br>75<br>65<br>55 | mA<br>mA<br>mA<br>mA | $t_{AVAV} = 25ns$<br>$t_{AVAV} = 35ns$<br>$t_{AVAV} = 45ns$<br>$t_{AVAV} = 55ns$                                                                                                                                |

| I <sub>CC2</sub> c | Average V <sub>CC</sub> Current during STORE                                      |                      | 3                     |                      | 3                    | mA                   | All Inputs Don't Care, V <sub>CC</sub> = max                                                                                                                                                                    |

| I <sub>CC3</sub> b | Average V <sub>CC</sub> Current at t <sub>AVAV</sub> = 200ns<br>5V, 25°C, Typical |                      | 10                    |                      | 10                   | mA                   | $\overline{W} \ge (V_{CC} - 0.2V)$<br>All Others Cycling, CMOS Levels                                                                                                                                           |

| I <sub>SB1</sub> d | Average V <sub>CC</sub> Current<br>(Standby, Cycling TTL Input Levels)            |                      | 27<br>23<br>20<br>N/A |                      | 28<br>24<br>21<br>20 | mA<br>mA<br>mA<br>mA | $\begin{array}{l} t_{AVAV} = 25ns, \overline{E} \geq V_{IH} \\ t_{AVAV} = 35ns, \overline{E} \geq V_{IH} \\ t_{AVAV} = 45ns, \overline{E} \geq V_{IH} \\ t_{AVAV} = 55ns, \overline{E} \geq V_{IH} \end{array}$ |

| I <sub>SB2</sub> d | V <sub>CC</sub> Standby Current<br>(Standby, Stable CMOS Input Levels)            |                      | 750                   |                      | 1500                 | μΑ                   | $\label{eq:constraint} \begin{split} \overline{E} &\geq (V_{CC} - 0.2V) \\ \text{All Others } V_{IN} &\leq 0.2V \text{ or } \geq (V_{CC} - 0.2V) \end{split}$                                                   |

| I <sub>ILK</sub>   | Input Leakage Current                                                             |                      | ±1                    |                      | ±1                   | μA                   | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$                                                                                                                                                                 |

| I <sub>OLK</sub>   | Off-State Output Leakage Current                                                  |                      | ±5                    |                      | ±5                   | μA                   | $V_{CC} = max$<br>$V_{IN} = V_{SS}$ to $V_{CC}$ , $\overline{E}$ or $\overline{G} \ge V_{IH}$                                                                                                                   |

| V <sub>IH</sub>    | Input Logic "1" Voltage                                                           | 2.2                  | V <sub>CC</sub> + .5  | 2.2                  | V <sub>CC</sub> + .5 | V                    | All Inputs                                                                                                                                                                                                      |

| V <sub>IL</sub>    | Input Logic "0" Voltage                                                           | V <sub>SS</sub> – .5 | 0.8                   | V <sub>SS</sub> – .5 | 0.8                  | V                    | All Inputs                                                                                                                                                                                                      |

| V <sub>OH</sub>    | Note a: Output Logic "1" Voltage                                                  | 2.4                  |                       | 2.4                  |                      | V                    | I <sub>OUT</sub> =-4mA                                                                                                                                                                                          |

| V <sub>OL</sub>    | Output Logic "0" Voltage                                                          |                      | 0.4                   |                      | 0.4                  | V                    | I <sub>OUT</sub> = 8mA                                                                                                                                                                                          |

| T <sub>A</sub>     | Operating Temperature                                                             | 0                    | 70                    | -40/-55              | 85/125               | °C                   |                                                                                                                                                                                                                 |

Note b:  $I_{CC_1}$  and  $I_{CC_3}$  are dependent on output loading and cycle rate. The specified values are obtained with outputs unloaded. Note c:  $I_{CC_2}$  is the average current required for the duration of the *STORE* cycle (t<sub>STORE</sub>). Note d:  $E \ge V_{IH}$  will not produce standby current levels until any nonvolatile cycle in progress has timed out.

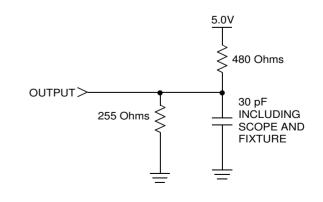

#### **AC TEST CONDITIONS**

| Input Pulse Levels                       |

|------------------------------------------|

| Input Rise and Fall Times $\leq$ 5ns     |

| Input and Output Timing Reference Levels |

| Output Load                              |

#### **CAPACITANCE**<sup>e</sup> $(T_A = 25^{\circ}C, f = 1.0MHz)$

| SYMBOL           | PARAMETER          | MAX | UNITS | CONDITIONS             |

|------------------|--------------------|-----|-------|------------------------|

| C <sub>IN</sub>  | Input Capacitance  | 8   | pF    | $\Delta V = 0$ to $3V$ |

| C <sub>OUT</sub> | Output Capacitance | 7   | pF    | $\Delta V = 0$ to 3V   |

Note e: These parameters are guaranteed but not tested.

Figure 1: AC Output Loading

#### SRAM READ CYCLES #1 & #2

$(V_{CC} = 5.0V \pm 10\%)$

|     | SYME                     |                  |                                   | STK10 | C68-35 | STK10 | STK10C68-45 |     | C68-55 |     |     |       |

|-----|--------------------------|------------------|-----------------------------------|-------|--------|-------|-------------|-----|--------|-----|-----|-------|

| NO. | #1, #2                   | Alt.             | PARAMETER                         | MIN   | MAX    | MIN   | MAX         | MIN | MAX    | MIN | MAX | UNITS |

| 1   | t <sub>ELQV</sub>        | t <sub>ACS</sub> | Chip Enable Access Time           |       | 25     |       | 35          |     | 45     |     | 55  | ns    |

| 2   | t <sub>AVAV</sub> f      | t <sub>RC</sub>  | Read Cycle Time                   | 25    |        | 35    |             | 45  |        | 55  |     | ns    |

| 3   | t <sub>AVQV</sub> g      | t <sub>AA</sub>  | Address Access Time               |       | 25     |       | 35          |     | 45     |     | 55  | ns    |

| 4   | t <sub>GLQV</sub>        | t <sub>OE</sub>  | Output Enable to Data Valid       |       | 10     |       | 15          |     | 20     |     | 25  | ns    |

| 5   | t <sub>AXQX</sub> g      | t <sub>OH</sub>  | Output Hold after Address Change  | 5     |        | 5     |             | 5   |        | 5   |     | ns    |

| 6   | t <sub>ELQX</sub>        | t <sub>LZ</sub>  | Chip Enable to Output Active      | 5     |        | 5     |             | 5   |        | 5   |     | ns    |

| 7   | t <sub>EHQZ</sub> h      | t <sub>HZ</sub>  | Chip Disable to Output Inactive   |       | 10     |       | 10          |     | 12     |     | 12  | ns    |

| 8   | t <sub>GLQX</sub>        | t <sub>OLZ</sub> | Output Enable to Output Active    | 0     |        | 0     |             | 0   |        | 0   |     | ns    |

| 9   | t <sub>GHQZ</sub> h      | t <sub>OHZ</sub> | Output Disable to Output Inactive |       | 10     |       | 10          |     | 12     |     | 12  | ns    |

| 10  | t <sub>ELICCH</sub> e    | t <sub>PA</sub>  | Chip Enable to Power Active       | 0     |        | 0     |             | 0   |        | 0   |     | ns    |

| 11  | t <sub>EHICCL</sub> d, e | t <sub>PS</sub>  | Chip Disable to Power Standby     |       | 25     |       | 35          |     | 45     |     | 55  | ns    |

Note f:  $\overline{W}$  must be high during SRAM READ cycles and low during SRAM WRITE cycles.  $\overline{NE}$  must be high during entire cycle. Note g: I/O state assumes  $\overline{E}, \overline{G} \leq V_{IL}, \overline{W} \geq V_{IH}$ , and  $\overline{NE} \geq V_{IH}$ ; device is continuously selected. Note h: Measured <u>+</u> 200mV from steady state output voltage.

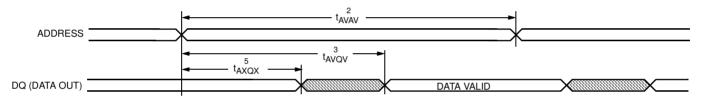

#### SRAM READ CYCLE #1: Address Controlled<sup>f, g</sup>

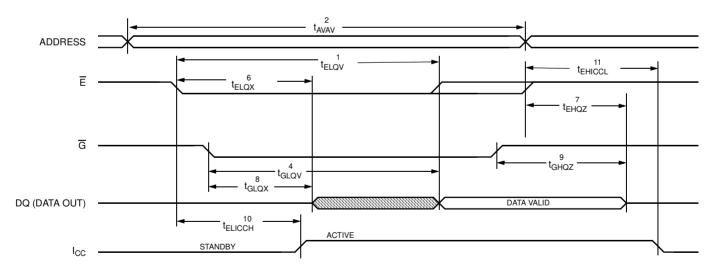

## SRAM READ CYCLE #2: E Controlled

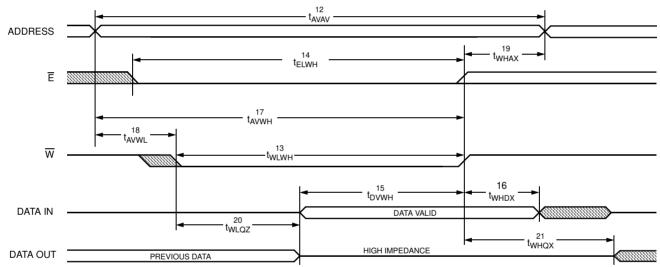

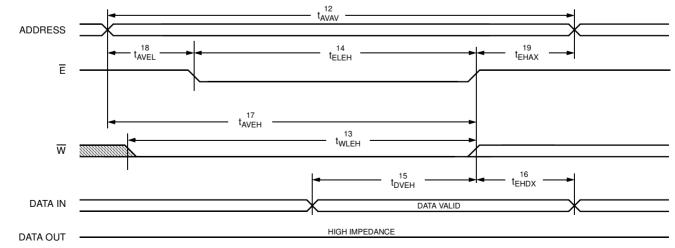

#### SRAM WRITE CYCLES #1 & #2

$(V_{CC} = 5.0V \pm 10\%)$

|     |                        | SYMBOLS           |                 |                                  | STK10 | C68-25 | STK100 | C68-35 | STK100 | C68-45 | STK10 | C68-55 |       |

|-----|------------------------|-------------------|-----------------|----------------------------------|-------|--------|--------|--------|--------|--------|-------|--------|-------|

| NO. | #1                     | #2                | Alt.            | PARAMETER                        | MIN   | MAX    | MIN    | MAX    | MIN    | MAX    | MIN   | MAX    | UNITS |

| 12  | t <sub>AVAV</sub>      | t <sub>AVAV</sub> | twc             | Write Cycle Time                 | 25    |        | 35     |        | 45     |        | 55    |        | ns    |

| 13  | t <sub>WLWH</sub>      | t <sub>WLEH</sub> | t <sub>WP</sub> | Write Pulse Width                | 20    |        | 25     |        | 30     |        | 45    |        | ns    |

| 14  | t <sub>ELWH</sub>      | t <sub>ELEH</sub> | t <sub>CW</sub> | Chip Enable to End of Write      | 20    |        | 25     |        | 30     |        | 45    |        | ns    |

| 15  | t <sub>DVWH</sub>      | t <sub>DVEH</sub> | t <sub>DW</sub> | Data Set-up to End of Write      | 10    |        | 12     |        | 15     |        | 30    |        | ns    |

| 16  | t <sub>WHDX</sub>      | t <sub>EHDX</sub> | t <sub>DH</sub> | Data Hold after End of Write     | 0     |        | 0      |        | 0      |        | 0     |        | ns    |

| 17  | t <sub>AVWH</sub>      | t <sub>AVEH</sub> | t <sub>AW</sub> | Address Set-up to End of Write   | 20    |        | 25     |        | 30     |        | 45    |        | ns    |

| 18  | t <sub>AVWL</sub>      | t <sub>AVEL</sub> | t <sub>AS</sub> | Address Set-up to Start of Write | 0     |        | 0      |        | 0      |        | 0     |        | ns    |

| 19  | t <sub>WHAX</sub>      | t <sub>EHAX</sub> | t <sub>WR</sub> | Address Hold after End of Write  | 0     |        | 0      |        | 0      |        | 0     |        | ns    |

| 20  | t <sub>WLQZ</sub> h, i |                   | t <sub>WZ</sub> | Write Enable to Output Disable   |       | 10     |        | 13     |        | 14     |       | 15     | ns    |

| 21  | t <sub>WHQX</sub>      |                   | tow             | Output Active after End of Write | 5     |        | 5      |        | 5      |        | 5     |        | ns    |

$\begin{array}{ll} \mbox{Note i:} & \mbox{If } \overline{W} \mbox{ is low when } \overline{E} \mbox{ goes low, the outputs remain in the high-impedance state.} \\ \mbox{Note j:} & \mbox{$\overline{E}$ or $\overline{W}$ must be $\geq V_{IH}$ during address transitions. $\overline{NE} \geq V_{IH}$.} \end{array}$

## SRAM WRITE CYCLE #1: W Controlled

## SRAM WRITE CYCLE #2: E Controlled

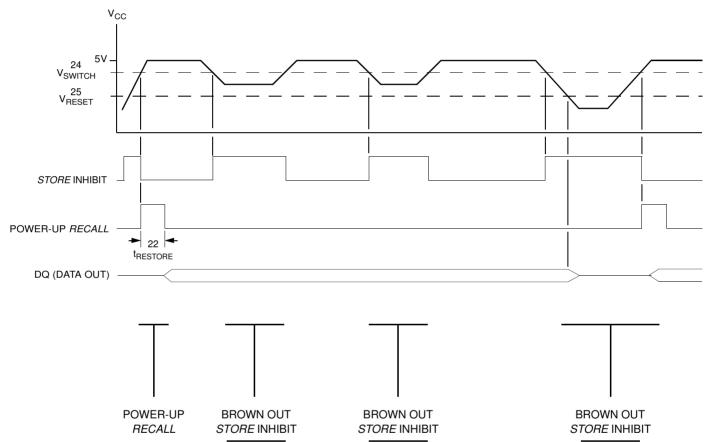

## STORE INHIBIT/POWER-UP RECALL

$(V_{CC} = 5.0V \pm 10\%)$

| NO. | SYMBOLS              | SYMBOLS PARAMETER         | STK10C68 |     |    | NOTES |

|-----|----------------------|---------------------------|----------|-----|----|-------|

| NO. | Standard             | FANAMEIEN                 | MIN      | MAX |    | NOTES |

| 22  | t <sub>RESTORE</sub> | Power-up RECALL Duration  |          | 550 | μs | k     |

| 23  | t <sub>STORE</sub>   | STORE Cycle Duration      |          | 10  | ms |       |

| 24  | V <sub>SWITCH</sub>  | Low Voltage Trigger Level | 4.0      | 4.5 | V  |       |

| 25  | V <sub>RESET</sub>   | Low Voltage Reset Level   |          | 3.6 | V  |       |

Note k: t<sub>RESTORE</sub> starts from the time V<sub>CC</sub> rises above V<sub>SWITCH</sub>.

#### STORE INHIBIT/POWER-UP RECALL

NO RECALL

$(\mathsf{V}_{\mathsf{CC}} \: \mathsf{DID} \: \mathsf{NOT} \: \mathsf{GO}$

BELOW V<sub>RESET</sub>)

NO RECALL

$(\mathsf{V}_{\mathsf{CC}} \: \mathsf{DID} \: \mathsf{NOT} \: \mathsf{GO}$

BELOW V<sub>RESET</sub>)

RECALL WHEN V<sub>CC</sub> RETURNS ABOVE V<sub>SWITCH</sub>

#### **MODE SELECTION**

| Ē | W      | G      | NE     | MODE                            | POWER            |

|---|--------|--------|--------|---------------------------------|------------------|

| Н | Х      | Х      | Х      | Not Selected                    | Standby          |

| L | Н      | L      | Н      | Read SRAM                       | Active           |

| L | L      | Х      | Н      | Write SRAM                      | Active           |

| L | Н      | L      | L      | Nonvolatile RECALL <sup>I</sup> | Active           |

| L | L      | Н      | L      | Nonvolatile STORE               | I <sub>CC2</sub> |

| L | L<br>H | L<br>H | L<br>X | No Operation                    | Active           |

Note I: An automatic *RECALL* takes place at power up, starting when V<sub>CC</sub> exceeds 4.25V and taking t<sub>RESTORE</sub>.

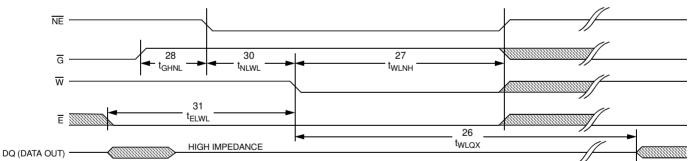

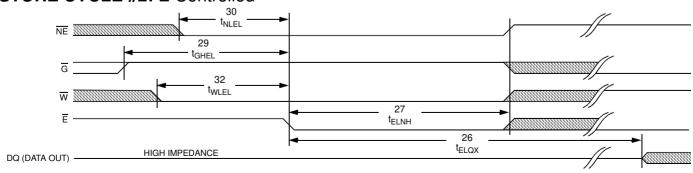

#### **STORE CYCLES #1 & #2**

#### $(V_{CC} = 5.0V \pm 10\%)$

| NO. |                     | SYMBOLS           |                    | PARAMETER                                     | MIN   | МАХ | UNITS |

|-----|---------------------|-------------------|--------------------|-----------------------------------------------|-------|-----|-------|

| NU. | #1                  | #2                | Alt.               |                                               | IVIIN | WAA | UNITS |

| 26  | t <sub>WLQX</sub> m | t <sub>ELQX</sub> | t <sub>STORE</sub> | STORE Cycle Time                              |       | 10  | ms    |

| 27  | t <sub>WLNH</sub> n | t <sub>ELNH</sub> | t <sub>WC</sub>    | STORE Initiation Cycle Time                   | 20    |     | ns    |

| 28  | t <sub>GHNL</sub>   |                   |                    | Output Disable Set-up to $\overline{NE}$ Fall | 0     |     | ns    |

| 29  |                     | t <sub>GHEL</sub> |                    | Output Disable Set-up to $\overline{E}$ Fall  | 0     |     | ns    |

| 30  | t <sub>NLWL</sub>   | t <sub>NLEL</sub> |                    | NE Set-up                                     | 0     |     | ns    |

| 31  | t <sub>ELWL</sub>   |                   |                    | Chip Enable Set-up                            | 0     |     | ns    |

| 32  |                     | <sup>t</sup> wlel |                    | Write Enable Set-up                           | 0     |     | ns    |

Note m: Measured with  $\overline{W}$  and  $\overline{NE}$  both returned high, and  $\overline{G}$  returned low. STORE cycles are inhibited below 4.0V. Note n: Once t<sub>WC</sub> has been satisfied by  $\overline{NE}$ ,  $\overline{G}$ ,  $\overline{W}$  and  $\overline{E}$ , the STORE cycle is completed automatically. Any of  $\overline{NE}$ ,  $\overline{G}$ ,  $\overline{W}$  or  $\overline{E}$  may be used to terminate the STORE initiation cycle.

Note o: If  $\overline{E}$  is low for any period of time in which  $\overline{W}$  is high while  $\overline{G}$  and  $\overline{NE}$  are low, then a *RECALL* cycle may be initiated.

#### STORE CYCLE #1: W Controlled<sup>o</sup>

## STORE CYCLE #2: E Controlled<sup>o</sup>

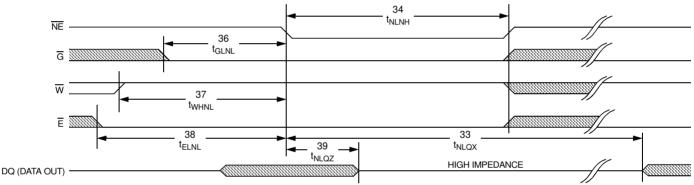

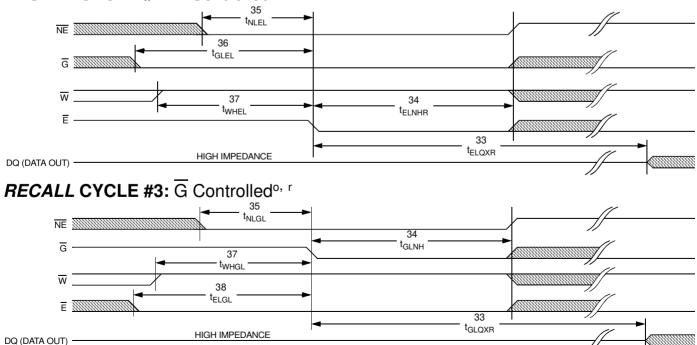

## **RECALL** CYCLES #1, #2 & #3

$(V_{CC} = 5.0V \pm 10\%)$

| NO. |                      | SYMBOLS            |                    | PARAMETER                    | MIN   | мах | UNITS |

|-----|----------------------|--------------------|--------------------|------------------------------|-------|-----|-------|

| NO. | #1                   | #2                 | #3                 |                              | IVIIN | WAA | UNITS |

| 33  | t <sub>NLQX</sub> p  | t <sub>ELQXR</sub> | t <sub>GLQXR</sub> | RECALL Cycle Time            |       | 20  | μs    |

| 34  | t <sub>NLNH</sub> q  | t <sub>ELNHR</sub> | t <sub>GLNH</sub>  | RECALL Initiation Cycle Time | 20    |     | ns    |

| 35  |                      | t <sub>NLEL</sub>  | t <sub>NLGL</sub>  | NE Set-up                    | 0     |     | ns    |

| 36  | t <sub>GLNL</sub>    | t <sub>GLEL</sub>  |                    | Output Enable Set-up         | 0     |     | ns    |

| 37  | t <sub>WHNL</sub>    | t <sub>WHEL</sub>  | twhgl              | Write Enable Set-up          | 0     |     | ns    |

| 38  | t <sub>ELNL</sub>    | t <sub>GLEL</sub>  | t <sub>ELGL</sub>  | Chip Enable Set-up           | 0     |     | ns    |

| 39  | t <sub>NLQZ</sub>    |                    |                    | NE Fall to Outputs Inactive  |       | 20  | ns    |

| 40  | t <sub>RESTORE</sub> |                    |                    | Power-up RECALL Duration     |       | 550 | μs    |

Note p: Measured with  $\overline{W}$  and  $\overline{NE}$  both high, and  $\overline{G}$  and  $\overline{E}$  low. Note q: Once t<sub>NLNH</sub> has been satisfied by  $\overline{NE}$ ,  $\overline{G}$ ,  $\overline{W}$  and  $\overline{E}$ , the *RECALL* cycle is completed automatically. Any of  $\overline{NE}$ ,  $\overline{G}$  or  $\overline{E}$  may be used to terminate the RECALL initiation cycle.

Note r: If  $\overline{W}$  is low at any point in which both  $\overline{E}$  and  $\overline{NE}$  are low and  $\overline{G}$  is high, then a STORE cycle will be initiated instead of a RECALL.

#### **RECALL CYCLE #1:** NE Controlled<sup>o</sup>

#### **RECALL CYCLE #2:** E Controlled<sup>o</sup>

## **DEVICE OPERATION**

The STK10C68 has two modes of operation: SRAM mode and <u>nonvolatile</u> mode, determined by the state of the NE pin. When in SRAM mode, the memory operates as a standard fast static RAM. While in nonvolatile mode, data is transferred in parallel from SRAM to Nonvolatile Elements or from Nonvolatile Elements to SRAM.

#### NOISE CONSIDERATIONS

Note that the STK10C68 is a high-speed memory and so must have a high-frequency bypass capacitor of approximately  $0.1\mu F$  connected between  $V_{\rm CC}$  and  $V_{\rm SS}$ , using leads and traces that are as short as possible. As with all high-speed CMOS ICs, normal careful routing of power, ground and signals will help prevent noise problems.

#### **SRAM READ**

The STK10C68 performs a READ cycle whenever  $\overline{E}$  and  $\overline{G}$  are low and NE and W are high. The address specified on pins A<sub>0-12</sub> determines which of the 8,192 data bytes will be accessed. When the READ is initiated by an address transition, the outputs will be valid after a delay of t<sub>AVQV</sub> (READ cycle #1). If the READ is initiated by  $\overline{E}$  or  $\overline{G}$ , the outputs will be valid at t<sub>ELQV</sub> or at t<sub>GLQV</sub>, whichever is later (READ cycle #2). The data outputs will repeatedly respond to address changes within the t<sub>AVQV</sub> access time without the need for transitions on any control input pins, and will remain valid until another address change or until  $\overline{E}$  or  $\overline{G}$  is brought high or  $\overline{W}$  or NE is brought low.

#### **SRAM WRITE**

A WRITE cycle is performed whenever  $\overline{E}$  and  $\overline{W}$  are low and NE is high. The address inputs must be stable prior to entering the WRITE cycle and must remain stable until either  $\overline{E}$  or  $\overline{W}$  goes high at the end of the cycle. The data on pins DQ<sub>0-7</sub> will be written into the memory if it is valid t<sub>DVWH</sub> before the end of a  $\overline{W}$  controlled WRITE or t<sub>DVEH</sub> before the end of an  $\overline{E}$  controlled WRITE.

It is recommended that  $\overline{G}$  be kept high during the entire WRITE cycle to avoid data bus contention on the common I/O lines. If  $\overline{G}$  is left low, internal circuitry will turn off the output buffers  $t_{WLOZ}$  after  $\overline{W}$  goes low.

#### NONVOLATILE STORE

A *STORE* cycle is performed when  $\overline{NE}$ ,  $\overline{E}$  and  $\overline{W}$  and low and  $\overline{G}$  is high. While any sequence that achieves this state will initiate a *STORE*, only  $\overline{W}$  initiation (*STORE* cycle #1) and  $\overline{E}$  initiation (*STORE* cycle #2) are practical without risking an unintentional SRAM WRITE that would disturb SRAM data. During a *STORE* cycle, previous nonvolatile data is erased and the SRAM contents are then programmed into nonvolatile elements. Once a *STORE* cycle is initiated, further input and output are disabled and the DQ<sub>0.7</sub> pins are tri-stated until the cycle is complete.

If  $\overline{E}$  and  $\overline{G}$  are low and  $\overline{W}$  and  $\overline{NE}$  are high at the end of the cycle, a READ will be performed and the outputs will go active, signaling the end of the *STORE*.

#### NONVOLATILE RECALL

A *RECALL* cycle is performed when  $\overline{E}$ ,  $\overline{G}$  and  $\overline{NE}$  are low and  $\overline{W}$  is high. Like the *STORE* cycle, *RECALL* is initiated when the last of the four clock signals goes to the *RECALL* state. Once initiated, the *RECALL* cycle will take  $t_{NLQX}$  to complete, during which all inputs are ignored. When the *RECALL* completes, any READ or WRITE state on the input pins will take effect.

Internally, *RECALL* is a two-step procedure. First, the SRAM data is cleared, and second, the nonvolatile information is transferred into the SRAM cells. The *RECALL* operation in no way alters the data in the nonvolatile cells. The nonvolatile data can be recalled an unlimited number of times.

As with the *STORE* cycle, a transition must occur on any one control pin to cause a *RECALL*, preventing inadvertent multi-triggering. On power up, once V<sub>CC</sub> exceeds the V<sub>CC</sub> sense voltage of 4.25V, a *RECALL* cycle is automatically initiated. Due to this automatic *RECALL*, SRAM operation cannot commence until  $t_{RESTORE}$  after V<sub>CC</sub> exceeds approximately 4.25V.

#### **POWER-UP** RECALL

During power up, or after any low-power condition ( $V_{CC}$  < 3.0V), an internal *RECALL* request will be latched. When  $V_{CC}$  once again exceeds the sense voltage of 4.25V, a *RECALL* cycle will automatically be initiated and will take t<sub>RESTORE</sub> to complete.

If the STK10C68 is in a WRITE state at the end of power-up *RECALL*, the SRAM data will be corrupted. To help avoid this situation, a 10K Ohm resistor should be connected either between W and system  $V_{cc}$  or between E and system  $V_{cc}$ .

#### HARDWARE PROTECT

The STK10C68 offers two levels of protection to suppress inadvertent *STORE* cycles. If the control signals ( $\overline{E}$ ,  $\overline{G}$ ,  $\overline{W}$  and  $\overline{NE}$ ) remain in the *STORE* condition at the end of a *STORE* cycle, a second *STORE* cycle will not be started. The *STORE* (or *RECALL*) will be initiated only after a transition on any one of these signals to the required state. In addition to multi-trigger protection, *STORE*s are inhibited when V<sub>CC</sub> is below 4.0V, protecting against inadvertent *STORE*s.

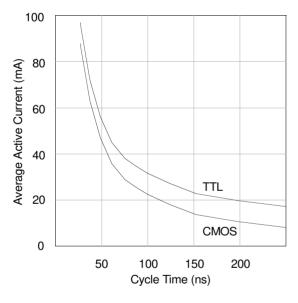

#### LOW AVERAGE ACTIVE POWER

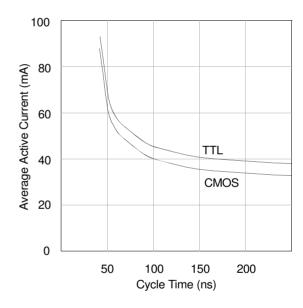

The STK10C68 draws significantly less current when it is cycled at times longer than 55ns. Figure 2 shows the relationship between  $I_{cc}$  and READ cycle time. Worst-case current consumption is shown for both CMOS and TTL input levels (commercial temperature range,  $V_{CC}$  = 5.5V, 100% duty cycle on chip enable). Figure 3 shows the same relationship for WRITE cycles. If the chip enable duty cycle is less than 100%, only standby current is drawn when the chip is disabled. The overall average current drawn by the STK10C68 depends on the following items: 1) CMOS vs. TTL input levels; 2) the duty cycle of chip enable; 3) the overall cycle rate for accesses; 4) the ratio of READs to WRITES; 5) the operating temperature; 6) the  $V_{cc}$  level; and 7) I/ O loading.

Figure 2:  $I_{CC}$  (max) Reads

Figure 3:  $I_{CC}$  (max) Writes

#### **Document Revision History**

| Revision | Date                                           | Summary                                                                           |  |  |  |  |

|----------|------------------------------------------------|-----------------------------------------------------------------------------------|--|--|--|--|

| 0.0      | December 2002                                  | Combined commercial, industrial and military data sheets. Removed 20 nsec device. |  |  |  |  |

| 0.1      | 0.1 September 2003 Added lead-free lead finish |                                                                                   |  |  |  |  |

| 0.2      | March 2006                                     | Marked as Obsolete, Not recommended for new design.                               |  |  |  |  |

|          |                                                |                                                                                   |  |  |  |  |

|          |                                                |                                                                                   |  |  |  |  |

|          |                                                |                                                                                   |  |  |  |  |

STK10C68