## 8-Bit, 20 MSPS, Flash A/D Converter

October 25, 2005

## Features

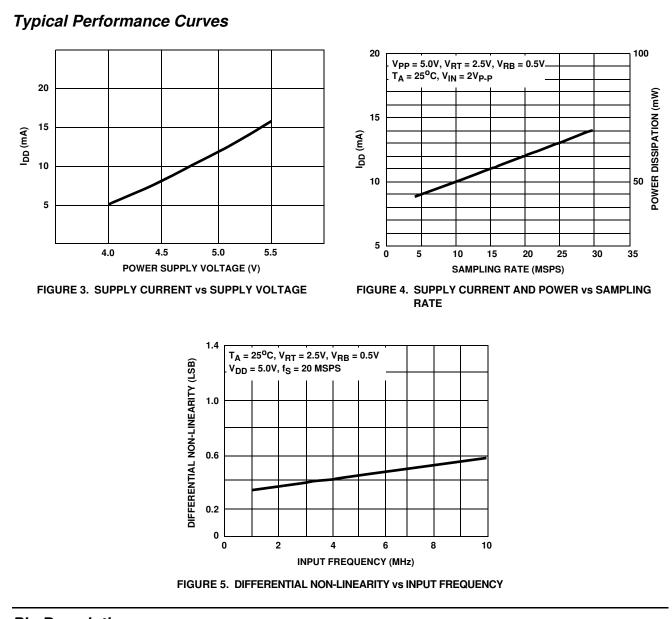

- Low Power Consumption at 20 MSPS (Typ) (Reference Current Excluded) ......60mW

- Built-In Sync Clamp Function

- · Built-In Monostable Multivibrator for Clamp Pulse Generation

- **Built-In Sync Pulse Polarity Selection Function**

- · Clamp Pulse Direct Input Possible

- Built-In Clamp ON/OFF Function

- Built-In Reference Voltage Self Bias Circuit

- Input CMOS Compatible

- Three-State TTL Compatible Output

- Single +5V Power Supply

- Low Input Capacitance (Typ) ..... 11pF

- Reference Impedance (Typ) ...... 300Ω

- Direct Replacement for the Sony CXD1176

### Description

The HI1176 is an 8-bit, CMOS analog-to-digital converter for video use that features a sync clamp function. The adoption of a 2-step parallel method realizes low power consumption and a maximum conversion speed of 20 MSPS. For higher sampling rates, refer to the pin-for-pin compatible HI1179 data sheet, document number 3666.

## Applications

- Video Digitizing

- Image Scanners

- Low Cost High Speed Data Acquisition Systems

- Multimedia

#### Ordering Information

| PART<br>NUMBER | TEMP. RANGE<br>( <sup>O</sup> C) | PACKAGE          | PKG. NO.  |

|----------------|----------------------------------|------------------|-----------|

| HI1176JCQ      | -40 to 85                        | 32 Ld MQFP       | Q32.7x7-S |

| HI1176-EV      | 25                               | Evaluation Board |           |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc. Copyright Intersil Americas Inc. 1998, 2005. All Rights Reserved 1 All other trademarks mentioned are the property of their respective owners.

#### **Absolute Maximum Ratings**

| Supply Voltage, V <sub>DD</sub> 7V                                                                         |  |

|------------------------------------------------------------------------------------------------------------|--|

| Reference Voltage, $V_{RT}$ , $V_{RB}$ $V_{DD}$ + 0.5V to $V_{SS}$ - 0.5V                                  |  |

| Analog Input Voltage, $V_{IN}$ $V_{DD}$ + 0.5V to $V_{SS}$ - 0.5V                                          |  |

| Digital Input Voltage, CLK V <sub>DD</sub> + 0.5V to V <sub>SS</sub> - 0.5V                                |  |

| Digital Output Voltage, V <sub>OH</sub> , V <sub>OL</sub> V <sub>DD</sub> + 0.5V to V <sub>SS</sub> - 0.5V |  |

#### **Operating Conditions** (Note 1)

| Temperature Range, T <sub>A</sub> 40 <sup>o</sup> C to 85 <sup>o</sup> C Supply Voltage    |

|--------------------------------------------------------------------------------------------|

| AV <sub>DD</sub> , AV <sub>SS</sub> , DV <sub>DD</sub> , DV <sub>SS</sub> +4.75V to +5.25V |

| DGND-AGND 0mV to 100mV                                                                     |

| Reference Input Voltage                                                                    |

| V <sub>RB</sub> 0V and Above                                                               |

| V <sub>RT</sub>                                                                            |

| Analog Input Voltage, VIN                                                                  |

| Clock Pulse Width                                                                          |

| t <sub>PW1</sub>                                                                           |

| t <sub>PW0</sub>                                                                           |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)     | $\theta_{JA}$ (°C/W)                 |

|------------------------------------------|--------------------------------------|

| MQFP Package                             | 122                                  |

| Maximum Junction Temperature             | 150 <sup>0</sup> C                   |

| Maximum Storage Temperature Range65      | <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering 10s) | 300 <sup>0</sup> C                   |

| (Lead Tips Only)                         |                                      |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

## $\label{eq:constraint} \textbf{Electrical Specifications} \quad \textbf{f}_{C} = 20 \; \text{MSPS}, \; \textbf{V}_{DD} = \textbf{+5V}, \; \textbf{V}_{RB} = \textbf{0.5V}, \; \textbf{V}_{RT} = \textbf{2.5V}, \; \textbf{T}_{A} = \textbf{25^{o}C} \; (\text{Note 1}) \; \textbf{V}_{CD} = \textbf{1} \; \textbf{V}_{CD} = \textbf{1$

| PARAMETER                                               | TEST CONDITIONS                                      | MIN | ТҮР  | МАХ  | UNIT   |

|---------------------------------------------------------|------------------------------------------------------|-----|------|------|--------|

| SYSTEM PERFORMANCE                                      |                                                      |     | -    | -    |        |

| Offset Voltage                                          |                                                      |     |      |      |        |

| E <sub>OT</sub>                                         |                                                      | -60 | -40  | -20  | mV     |

| E <sub>OB</sub>                                         |                                                      | +20 | +40  | +60  | mV     |

| Integral Non-Linearity, INL                             | $f_{C}$ = 20 MSPS, $V_{IN}$ = 0.5V to 2.5V           | -   | ±0.5 | ±1.3 | LSB    |

| Differential Non-Linearity, DNL                         | $f_{C}$ = 20 MSPS, $V_{IN}$ = 0.5V to 2.5V           | -   | ±0.3 | ±0.5 | LSB    |

| DYNAMIC CHARACTERISTICS                                 | ·                                                    |     |      |      |        |

| Signal to Noise Ratio, SINAD                            | f <sub>S</sub> = 20MHz, f <sub>IN</sub> = 1MHz       | -   | 46   | -    | dB     |

| RMS Signal<br>Signal-To-Noise + Distortion Ratio, SINAD | f <sub>S</sub> = 20MHz, f <sub>IN</sub> = 3.58MHz    | -   | 46   | -    | dB     |

| Maximum Conversion Speed, f <sub>C</sub>                | $V_{IN}$ = 0.5V to 2.5V, f <sub>IN</sub> = 1kHz Ramp | 20  | 35   | -    | MSPS   |

| Minimum Conversion Speed                                |                                                      | -   | -    | 0.5  | MSPS   |

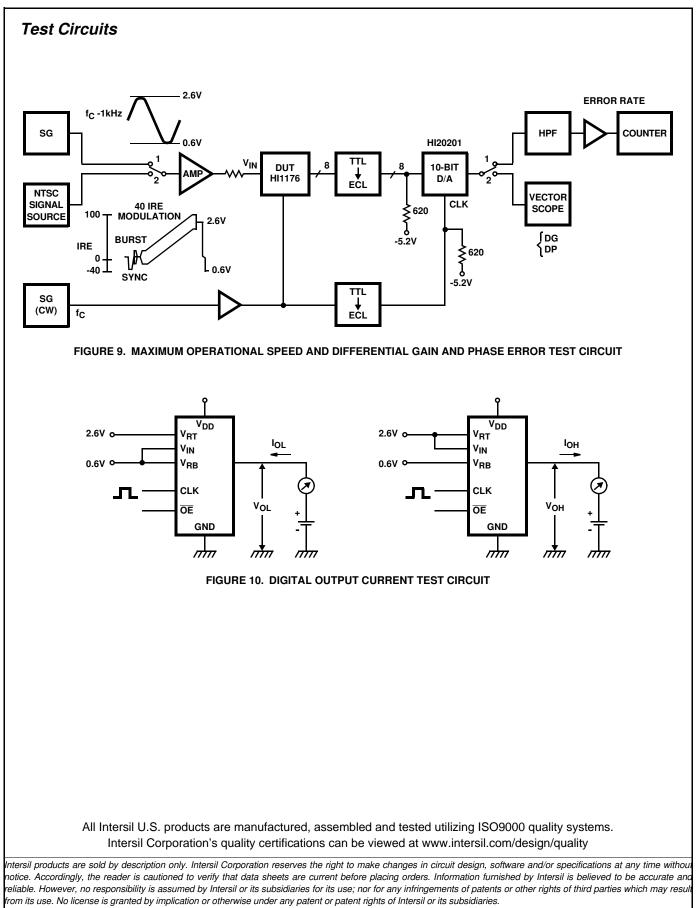

| Differential Gain Error, DG                             | NTSC 40 IRE Mod Ramp, f <sub>C</sub> = 14.3 MSPS     | -   | 1.0  | -    | %      |

| Differential Phase Error, DP                            |                                                      | -   | 0.5  | -    | Degree |

| Aperture Jitter, t <sub>AJ</sub>                        |                                                      | -   | 30   | -    | ps     |

| Sampling Delay, t <sub>DS</sub>                         |                                                      | -   | 4    | -    | ns     |

| ANALOG INPUTS                                           | •                                                    |     | •    | •    | •      |

| Analog Input Bandwidth (-1dB), BW                       |                                                      | -   | 18   | -    | MHz    |

| Analog Input Capacitance, CIN                           | V <sub>IN</sub> = 1.5V + 0.07V <sub>RMS</sub>        | -   | 11   | -    | pF     |

| PARAMETER                                                                    | TEST CONDITIONS                                            |                                   | MIN  | ТҮР  | MAX  | UNIT |

|------------------------------------------------------------------------------|------------------------------------------------------------|-----------------------------------|------|------|------|------|

| REFERENCE INPUT                                                              | -                                                          |                                   |      |      |      |      |

| Reference Pin Current, I <sub>REF</sub>                                      |                                                            |                                   | 4.5  | 6.6  | 8.7  | mA   |

| Reference Resistance (V <sub>RT</sub> to V <sub>RB</sub> ), R <sub>REF</sub> |                                                            |                                   | 230  | 300  | 450  | Ω    |

| INTERNAL VOLTAGE REFERENCES                                                  |                                                            |                                   |      |      | 1    |      |

| Self Bias                                                                    |                                                            |                                   |      |      |      |      |

| V <sub>RB</sub>                                                              | Short $V_{RB}$ and $V_{RBS},$ Short $V_{RT}$ and $V_{RTS}$ |                                   | 0.48 | 0.52 | 0.56 | V    |

| V <sub>RT</sub> - V <sub>RB</sub>                                            |                                                            |                                   | 1.96 | 2.08 | 2.22 | V    |

| DIGITAL INPUTS                                                               | •                                                          |                                   |      | •    |      |      |

| Digital Input Voltage                                                        |                                                            |                                   |      |      |      |      |

| V <sub>IH</sub>                                                              |                                                            |                                   | 4.0  | -    | -    | V    |

| V <sub>IL</sub>                                                              |                                                            |                                   | -    | -    | 1.0  | V    |

| Digital Input Current                                                        |                                                            |                                   |      |      |      |      |

| I <sub>IH</sub>                                                              | V <sub>DD</sub> = Max                                      | $V_{IH} = V_{DD}$                 | -    | -    | 5    | μΑ   |

| Ι <sub>ΙL</sub>                                                              |                                                            | $V_{IL} = 0V$                     | -    | -    | 5    | μA   |

| DIGITAL OUTPUTS                                                              |                                                            |                                   |      |      |      |      |

| Digital Output Current                                                       |                                                            |                                   |      |      |      |      |

| ЮН                                                                           | $\overline{OE} = V_{SS}, V_{DD} = Min$                     | $V_{OH} = V_{DD} - 0.5V$          | -1.1 | -    | -    | mA   |

| I <sub>OL</sub>                                                              |                                                            | $V_{OL} = 0.4V$                   | 3.7  | -    | -    | mA   |

| Digital Output Current                                                       |                                                            |                                   |      |      |      |      |

| lozh                                                                         | $\overline{OE} = V_{DD}, V_{DD} = Max$                     | V <sub>OH</sub> = V <sub>DD</sub> | -    | -    | 16   | μA   |

| I <sub>OZL</sub>                                                             |                                                            | $V_{OL} = 0V$                     | -    | -    | 16   | μA   |

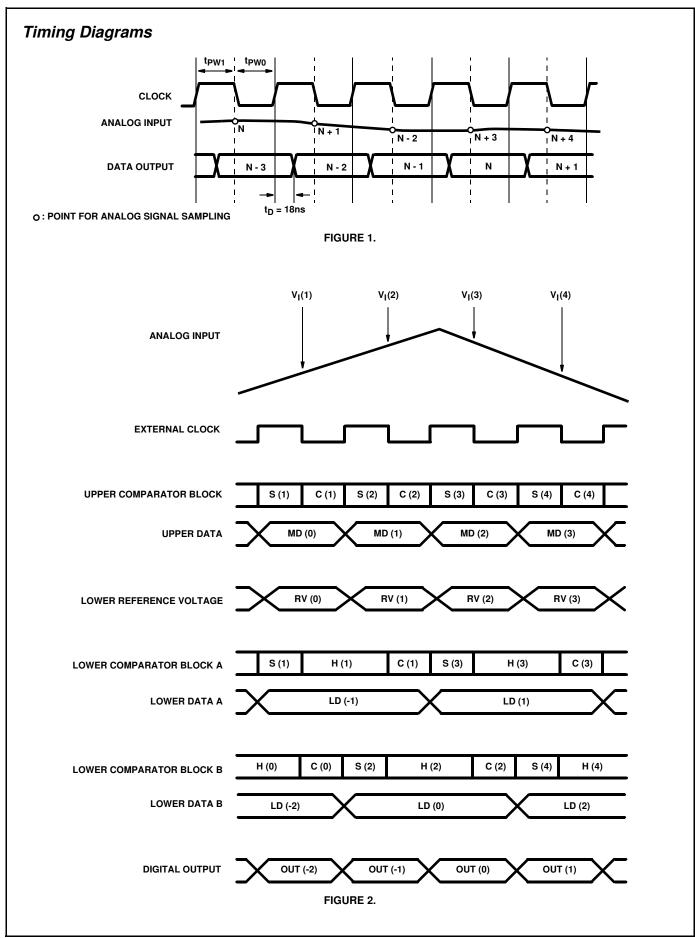

| TIMING CHARACTERISTICS                                                       |                                                            |                                   |      |      |      |      |

| Output Data Delay, t <sub>DL</sub>                                           |                                                            |                                   | -    | 18   | 30   | ns   |

| POWER SUPPLY CHARACTERISTIC                                                  |                                                            |                                   |      |      |      |      |

| Supply Current, I <sub>DD</sub>                                              | f <sub>C</sub> = 20 MSPS, NTSC Ramp                        | Wave Input                        | -    | 12   | 18   | mA   |

| CLAMP CHARACTERISTICS                                                        | •                                                          |                                   |      |      | •    |      |

| Clamp Offset Voltage, E <sub>OC</sub>                                        | $V_{IN} = DC$ , PWS = 3 $\mu$ s                            | V <sub>REF</sub> = 0.5V           | 0    | +20  | +40  | mV   |

|                                                                              |                                                            | V <sub>REF</sub> = 2.5V           | -50  | -30  | -10  | mV   |

| Clamp Pulse Width (Sync Pin Input), t <sub>CPW</sub>                         | C = 100pF, R = 130kΩ on Pi                                 | n 15                              | 1.75 | 2.75 | 3.75 | μS   |

| Clamp Pulse Delay, t <sub>CPD</sub>                                          |                                                            |                                   | -    | 25   | -    | ns   |

NOTE:

1. Electrical specifications guaranteed only under the stated operating conditions.

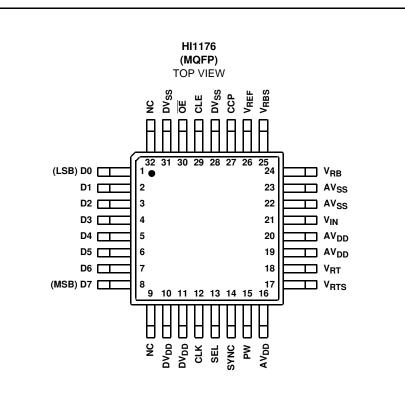

## **Pin Descriptions**

| PIN<br>NUMBER | SYMBOL           | EQUIVALENT CIRCUIT | DESCRIPTION                  |

|---------------|------------------|--------------------|------------------------------|

| 1-8           | D0 to D7         |                    | D0 (LSB) to D7 (MSB) Output. |

| 10, 11        | DV <sub>DD</sub> |                    | Digital +5V.                 |

| PIN<br>NUMBER | SYMBOL           | EQUIVALENT CIRCUIT              | DESCRIPTION                                                                                                                                                                               |

|---------------|------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12            | CLK              |                                 | Clock Input.                                                                                                                                                                              |

| 13            | SEL              |                                 | When SEL is low, the falling edge of Pin 14 (sync<br>triggers the monostable.<br>When SEL is high, the rising edge of Pin 14 (sync<br>triggers the monostable.                            |

| 14            | SYNC             |                                 | Trigger pulse input to the monostable multivibrator<br>Trigger polarity can be controlled by Pin 13 (SEL)                                                                                 |

| 15            | PW               |                                 | When a clamp pulse is generated by the<br>monostable, the pulse width is determined by the<br>external R and C.<br>When the clamp pulse is directly input, it is input to<br>Pin 15 (PW). |

| 16, 19, 20    | AV <sub>DD</sub> |                                 | Analog +5V.                                                                                                                                                                               |

| 17            | V <sub>RTS</sub> | (17) AV <sub>DD</sub>           | When shorted with V <sub>RT</sub> , generates approx. +2.6V                                                                                                                               |

| 18            | V <sub>RT</sub>  | <mark>γ</mark> AV <sub>DD</sub> | Reference Voltage (Top).                                                                                                                                                                  |

| 24            | V <sub>RB</sub>  |                                 | Reference Voltage (Bottom).                                                                                                                                                               |

| PIN<br>NUMBER | SYMBOL           | EQUIVALENT CIRCUIT     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                   |

|---------------|------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21            | VIN              |                        | Analog Input.                                                                                                                                                                                                                                                                                                                                 |

| 22, 23        | AV <sub>SS</sub> |                        | Analog Ground.                                                                                                                                                                                                                                                                                                                                |

| 25            | V <sub>RBS</sub> | ۵۷ <sub>SS</sub><br>25 | When shorted with V <sub>RB</sub> , generates approx. +0.5∖                                                                                                                                                                                                                                                                                   |

| 26            | V <sub>REF</sub> |                        | Clamp Reference Voltage Input.                                                                                                                                                                                                                                                                                                                |

| 27            | CCP              |                        | Integrates the voltage for clamp control.                                                                                                                                                                                                                                                                                                     |

| 28, 31        | DV <sub>SS</sub> |                        | Digital GND.                                                                                                                                                                                                                                                                                                                                  |

| 29            | CLE              | 29<br>CLAMP PULSI      | When $\overline{\text{CLE}}$ is low, clamp function is activated.<br>When $\overline{\text{CLE}}$ is high, clamp function is OFF and onl<br>the usual A/D converter function is active.<br>By connecting $\overline{\text{CLE}}$ pin to $\text{DV}_{\text{DD}}$ via a severa<br>hundred $\Omega$ resistance, the clamp pulse can b<br>tested. |

| 30            | ŌĒ               |                        | When $\overline{OE}$ is low, data is valid.<br>When $\overline{OE}$ is high, D0 to D7 pins are hig<br>impedance.                                                                                                                                                                                                                              |

| TABLE 1. A/D OUTPUT CODE |      |                     |   |   |   |   |   |   |  |  |

|--------------------------|------|---------------------|---|---|---|---|---|---|--|--|

| INPUT SIGNAL             |      | DIGITAL OUTPUT CODE |   |   |   |   |   |   |  |  |

| VOLTAGE                  | STEP | MSB                 |   |   |   |   |   |   |  |  |

| V <sub>RT</sub>          | 255  | 1                   | 1 | 1 | 1 | 1 | 1 | 1 |  |  |

| _                        | •    |                     |   |   |   | • |   |   |  |  |

| •                        | •    |                     |   |   |   | • |   |   |  |  |

| •                        | •    |                     |   |   |   | • |   |   |  |  |

| •                        | 128  | 1                   | 0 | 0 | 0 | 0 | 0 | 0 |  |  |

1

0

## **Detailed Description**

VRB

The HI1176 is a 2-step A/D converter featuring a 4-bit upper comparator group and two lower comparator groups of 4 bits each. The reference voltage can obtained from the onboard bias generator or be supplied externally. This IC uses an offset canceling type comparator that operates synchronously with an external clock. The operating modes of the part are input sampling/autozero (S), hold (H), and compare (C).

127

0

0

0

1

0

The operation of the part is illustrated in Figure 2. A reference voltage that is between VRT-VRB is constantly applied to the upper 4-bit comparator group.  $V_{I}(1)$  is sampled with the falling edge of the first clock by the upper comparator block. The lower block A also samples  $V_{I}(1)$  on the same edge. The upper comparator block finalizes comparison data MD(1) with the rising edge of the first clock. Simultaneously the reference supply generates a reference voltage RV(1) that corresponds to the upper results and applies it to the lower comparator block A. The lower comparator block finalizes comparison data LD(1) with the rising edge of the second clock. MD(1) and LD(1) are combined and output as OUT(1) with the rising edge of the third clock. There is a 2.5 cycle clock delay from the analog input sampling point to the corresponding digital output data. Notice how the lower comparator blocks A and B alternate generating the lower data in order to increase the overall A/D sampling rate.

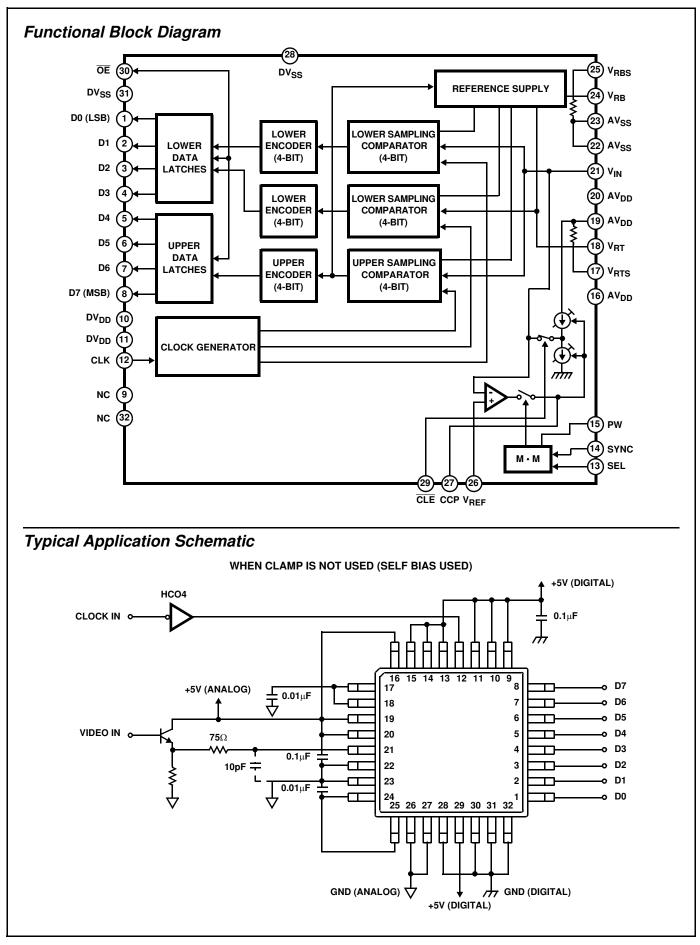

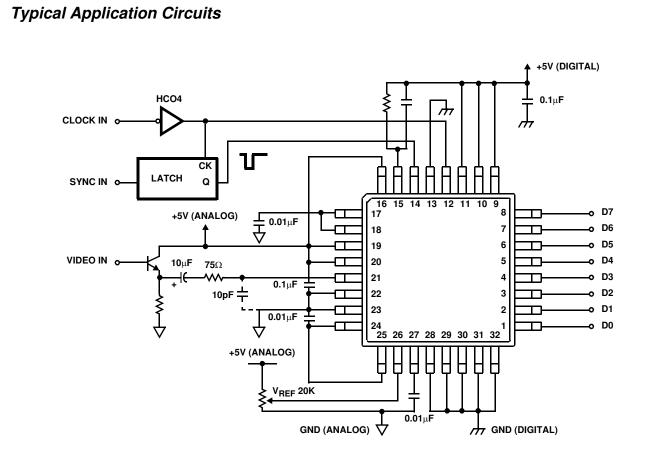

#### Power, Grounding, and Decoupling

To reduce noise effects, separate the analog and digital grounds.

Bypass both the digital and analog V<sub>DD</sub> pins to their respective grounds with a ceramic  $0.1\mu$ F capacitor close to the pin.

#### Analog Input

The input capacitance is small when compared with other flash type A/D converters. However, it is necessary to drive the input with an amplifier with sufficient bandwidth and drive capability. In order to prevent parasitic oscillation, it may be necessary to insert a resistor between the output of the amplifier and the A/D input.

#### **Reference Input**

1

0

0

The range of the A/D is set by the voltage between V<sub>RT</sub> and V<sub>RB</sub>. The internal bias generator will set V<sub>RTS</sub> to 2.5V and V<sub>RBS</sub> to 0.5V. These can be used as the part reference by shorting  $V_{RT}$  and  $V_{RTS}$  and  $V_{RB}$  to  $V_{RBS}$ . The analog input range of the A/D will now be from 0.5V to 2.5V. If a V<sub>RB</sub> below +0.5V is used the linearity of the part will be degraded.

1

0

1

0

LSB

1

0

1

0

Bypass  $V_{\text{RT}}$  and  $V_{\text{RB}}$  to analog ground with a  $0.1 \mu \text{F}$ capacitor.

#### **Clamp Operation**

The HI1176 provides a clamp option that allows the user to clamp a portion of the analog input to a voltage set by the  $V_{RFF}$  pin. The clamp function is enabled by bringing  $\overline{CLE}$ low. An internal monostable multivibrator is provided that can be used to generate the clamp pulses. The monostable pulse width is determined by the external R and C connected to the PW pin. The trigger to the monostable is applied on the SYNC pin. The edge that triggers the monostable is determined by the SEL pin. When SEL is low the falling edge will trigger the monostable and when SEL is high the rising edge will trigger the monostable. Figure 6 shows the HI1176 configured for this mode of operation. The clamp pulse is latched by the ADC sampling clock. This is not necessary to the operation of the clamp function but if this is not done then a slight beat might be generated as vertical sag according to the relation between the sampling frequency and the clamp frequency.

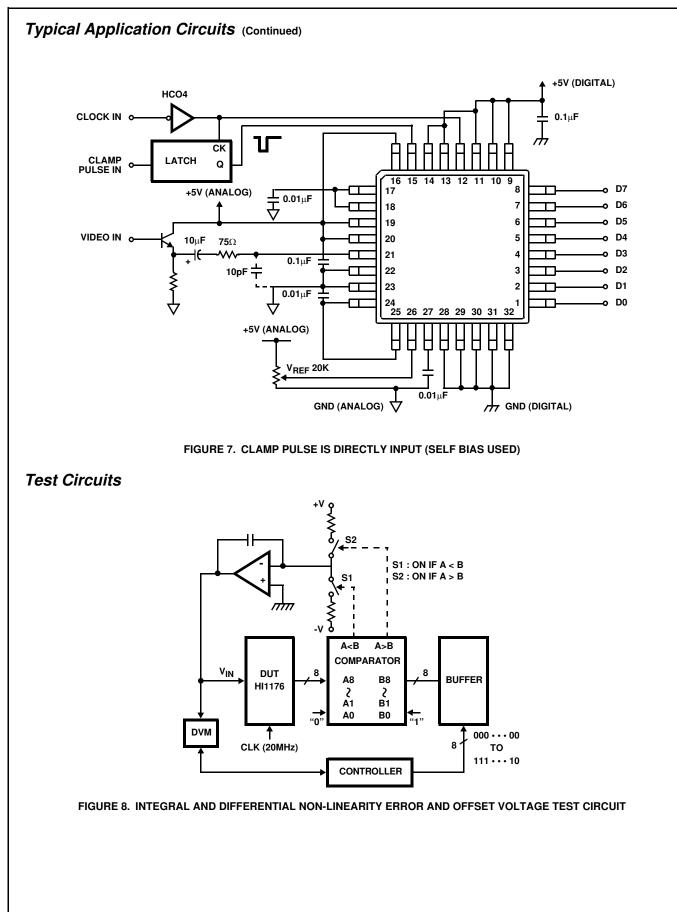

The HI1176 can also be configured to operate with an external clamp pulse. In this case a negative going pulse is input to the PW pin. VIN will now be clamped during the low period of the clamp pulse to the voltage on the V<sub>RFF</sub> pin. Figure 7 shows the HI1176 configured for this mode of operation.

Figure 1 illustrates the operation of HI1176 when the clamp function is not used.

FIGURE 6. PEDESTAL CLAMP IS EXECUTED BY SYNC PULSE (SELF BIAS USED)

For information regarding Intersil Corporation and its products, see www.intersil.com