# National Semiconductor is now part of Texas Instruments.

Search <a href="http://www.ti.com/">http://www.ti.com/</a> for the latest technical information and details on our current products and services.

# LMH1251

# YP<sub>B</sub>P<sub>B</sub> to RGBHV Converter and 2:1 Video Switch

## **General Description**

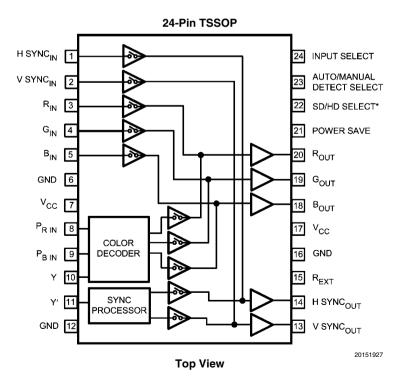

The LMH1251 is a wideband 2:1 analog video switch with an integrated  $\mathrm{YP_BP_R}$  to RGBHV converter. The device accepts one set of  $\mathrm{YP_BP_R}$  inputs and one set of RGB/HSYNC/VSYNC inputs. Based on the input selected, the output will be either a decoded TV or buffered PC video signal.

The LMH1251 has a SYNC separator and processor that is capable of extracting sync timing information from both Standard Definition Television (SDTV) and High Definition Television (HDTV) inputs. It provides bi-level sync, and tri-level sync separation.

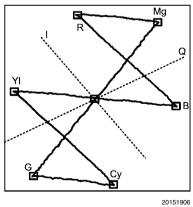

The color space conversion from YP<sub>B</sub>P<sub>R</sub> to RGB in the LMH1251 is realized with a very high precision fully analog dematrixer which provides superior chroma accuracy that is less than 2.5% of amplitude and 1.5° of phase error on a vectorscope. It is equipped with a smart video detection circuit which automatically senses SDTV and HDTV video formats and applies the appropriate color space conversion.

The LMH1251 is capable of handling SDTV, HDTV, XGA, SXGA, and UXGA video formats, which makes it an ideal solution for enhancing value in applications ranging from LCD monitors, to set-top boxes, to projectors. The LMH1251 is part of the LMH® high speed amplifier family, and is offered in a TSSOP-24 package.

## **Features**

- YP<sub>R</sub>P<sub>R</sub> to RGBHV conversion

- YP<sub>B</sub>P<sub>B</sub> path: 70 MHz, -3 dB, 700 mV<sub>PP</sub> bandwidth

- RGB path: 400 MHz, -3 dB, 700 mV<sub>PP</sub> bandwidth

- Supports PC video display resolutions up to UXGA (1600 x 1200 @ 75 Hz)

- Supports 480i, 480p, 576i, 576p, 720p, 1080i, and 1080p

- Smart video format detection for SD and HD

- Power save mode

## **Applications**

- TFT LCD monitor

- CRT monitor

- Set-top box

- Display projector

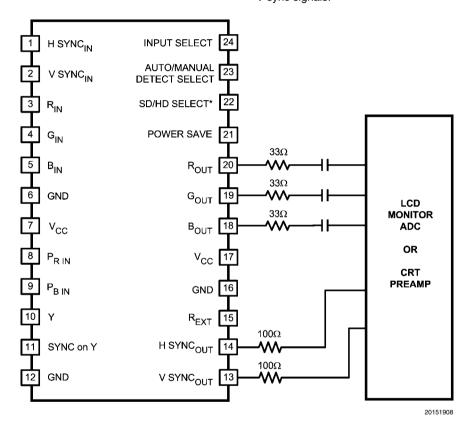

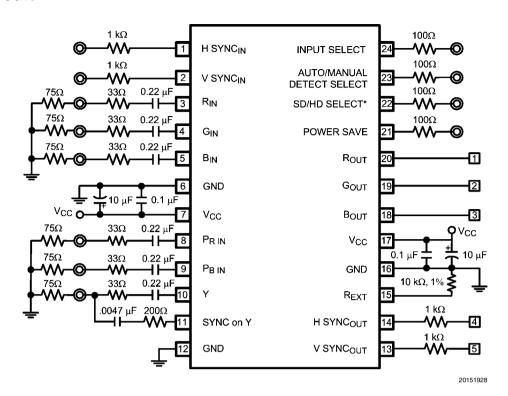

# **Connection Diagram**

$\label{eq:local_local_local} LMH^{\scriptsize \textcircled{\tiny B}} \ \ \text{is a registered trademark of National Semiconductor Corporation}.$

## **Truth Table**

# **TABLE 1. Input Select**

| Pin 24 | OUT                                     |

|--------|-----------------------------------------|

| 0      | RGBHV input Ch                          |

| 1      | YP <sub>B</sub> P <sub>R</sub> input Ch |

## **TABLE 2. Format/Conversion Select**

| Pin 23 | Pin 22     | SYNC      | Format Detection | Conversion Scheme |

|--------|------------|-----------|------------------|-------------------|

| 0      | 0          | Bi-Level  | Manual           | 480i/480p         |

| 0      | 1          | Tri-Level | Manual           | 720p/1080i        |

| 1      | *Outputs 0 | Bi-Level  | Auto             | 480i/480p         |

| 1      | *Outputs 1 | Tri-Level | Auto             | 720p/1080i        |

<sup>\*</sup> When Pin 23 is set high, the LMH1251 is in Auto Mode, in which it can detect the incoming video format (SD or HD) and apply the appropriate color conversion and sync processing. With Auto Mode, Pin 22 becomes an output pin, and will either output a logic high or low to notify the user of the format that is being detected by the LMH1251. If Pin 23 is set low, the LMH1251 is in Manual Mode, in which the user must specify the format with Pin 22. With Manual Mode, Pin 22 is an input pin. Since Pin 22 is a bi-directional pin, care must be given not to apply any voltages to it when it is in the Auto Mode, in which it functions as an output pin. The use of the Auto Mode with Pin 22 left floating is typically recommended.

## **TABLE 3. Power Save**

| Pin 21 | Low Power Mode |

|--------|----------------|

| 0      | Disable        |

| 1      | Enabled        |

# **Ordering Information**

| Package       | Package Part Number Package Marking Transport Media |           | Transport Media          | NSC Drawing |

|---------------|-----------------------------------------------------|-----------|--------------------------|-------------|

| 24-Pin TSSOP  | LMH1251MT                                           |           | 61 Units/Rail            | MTC24       |

| 24-PIII 1330P | LMH1251MTX                                          | LMH1251MT | 2.5k Units Tape and Reel | IVI I 024   |

## **Absolute Maximum Ratings** (Notes 1, 3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

ESD Tolerance

Susceptibility(Note 4) 4.0 kV Machine Model (Note 12) 400V Supply Voltage V<sub>CC</sub>, Pins 7 and 17 5.5V Voltage at any Input Pin (VIN)  $V_{CC} - 0.5 \ge V_{IN} \ge 0V$

$0.0V \le V_{\rm IN} \le 1.2V$ Video Inputs (pk-pk) Thermal Resistance to Ambient (θ<sub>1</sub>) 110°C/W

Thermal Resistance to Case  $(\theta_{1C})$ 25°C/W Junction Temperature (T<sub>1</sub>) +150°C Storage Temperature Range -65°C to +150°C Lead Temperature (soldering 10 sec.) 265°C

## **Operating Ratings** (Note 2)

Operating Temperature Range (Note 5) -20°C to +80°C Supply Voltage (V<sub>CC</sub>)  $4.75V \le V_{CC} \le 5.25V$ RGB Video Inputs (pk-pk)  $0.0V \le V_{IN} \le 0.7V$ Y Video Inputs (incl. Sync)  $-0.3V \le V_{IN} \le 0.7V$ P<sub>R</sub>P<sub>R</sub> Video Inputs  $-0.35V \le V_{IN} \le 0.35V$

# **Video Signal Electrical Characteristics**

Unless otherwise noted:  $T_A = 25$ °C,  $V_{CC} = +5.0$ V, RGB  $Video_{IN} = 0.7$   $V_{PP}$ , Y  $Video_{IN} = 0.7$   $V_{PP}$ ,  $P_BP_R$   $Video_{IN} = \pm 350$  mV,  $C_1 = 8 \text{ pF}$ , Video Outputs = 0.7  $V_{PP}$ .

| Symbol                                            | Parameter                                                         | Conditions                                                  | Min      | Тур      | Max      | Units |

|---------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------|----------|----------|----------|-------|

|                                                   |                                                                   |                                                             | (Note 8) | (Note 7) | (Note 8) |       |

| I <sub>S, RGB</sub>                               | Supply Current                                                    | No Output Loading, 80 kHz                                   | 28       | 34       | 41       | mA    |

| $I_{S, YP_BP_R}$                                  | Supply Current                                                    | No Output Loading, 480p see (Note 9)                        | 60       | 70       | 80       | mA    |

| I <sub>S-PS</sub>                                 | Supply Current, Power Save Mode                                   | Power Save Mode, No Output<br>Loading, 80 kHz, see (Note 9) | 4        | 8        | 12       | mA    |

| I <sub>OUT</sub>                                  | Output Current                                                    |                                                             |          | 3        |          | mA    |

| V <sub>O BLK</sub>                                | Typical DC Active Video Black Level<br>Output Voltage             |                                                             | 1.8      | 2.1      | 2.4      | VDC   |

| Gain <sub>RGB</sub>                               | RGB Video Unity Gain                                              | RGB Video <sub>IN</sub> = 0.7 V <sub>PP</sub>               |          | 0.07     |          | dB    |

| Ch-Ch Match <sub>RGB</sub>                        | RGB Ch to Ch Matching                                             | RGB Video <sub>IN</sub> = 0.7 V <sub>PP</sub>               |          | 0.02     |          | dB    |

| LE <sub>RGB</sub>                                 | RGB Input: Linearity Error                                        | Staircase Input Signal see (Note 10)                        |          | 0        |          | %     |

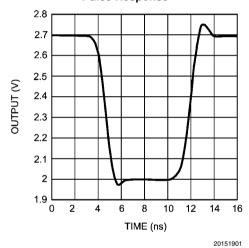

| Video Time Dom                                    | ain Response                                                      |                                                             | · · ·    |          |          |       |

| RGB t <sub>r</sub>                                | RGB Input:<br>Video Rise Time                                     | 10% to 90%, AC Input Signal (Note 6)                        |          | 1.55     |          | ns    |

| RGB OS <sub>R</sub>                               | RGB Input:<br>Rising Edge Overshoot                               | AC Input Signal (Note 6)                                    |          | 3        |          | %     |

| RGB t <sub>f</sub>                                | RGB Input:<br>Video Fall Time                                     | 90% to 10%, AC Input Signal (Note 6)                        |          | 1.55     |          | ns    |

| RGB OS <sub>F</sub>                               | RGB Input:<br>Rising Edge Overshoot                               | AC Input Signal (Note 6)                                    |          | 3        |          | %     |

| SD YP <sub>B</sub> P <sub>R</sub> t <sub>r</sub>  | SD YP <sub>B</sub> P <sub>R</sub> Input:<br>Video Rise Time       | 10% to 90%, AC Input Signal (Note 6)                        |          | 1.54     |          | ns    |

| RGB OSF                                           | RGB Input:<br>Falling Edge Overshoot                              | (Note 6), AC Input Signal                                   |          | 3        |          | %     |

| SD YP <sub>B</sub> P <sub>R</sub> t <sub>r</sub>  | SD YP <sub>B</sub> P <sub>R</sub> Input:<br>Video Rise Time       | 10% to 90%, AC Input Signal (Note 6)                        |          | 15.4     |          | ns    |

| SD YP <sub>B</sub> P <sub>R</sub> OS <sub>R</sub> | SD YP <sub>B</sub> P <sub>R</sub> Input:<br>Rising Edge Overshoot | AC Input Signal (Note 6)                                    |          | 3        |          | %     |

| SD YP <sub>B</sub> P <sub>R</sub> t <sub>f</sub>  | SD YP <sub>B</sub> P <sub>R</sub> :<br>Video Fall Time            | 90% to 10%, AC Input Signal (Note 6)                        |          | 15.4     |          | ns    |

| SD YP <sub>B</sub> P <sub>R</sub> OS <sub>F</sub> | SD YP <sub>B</sub> P <sub>R</sub> :<br>Falling Edge Overshoot     | AC Input Signal<br>(Note 6)                                 |          | 3        |          | %     |

| HD YP <sub>B</sub> P <sub>R</sub> t <sub>r</sub>  | HD YP <sub>B</sub> P <sub>R</sub> Input:<br>Video Rise Time       | 10% to 90%, AC Input Signal (Note 6)                        |          | 8.4      |          | ns    |

| Symbol                                            | Parameter                                                                             | Conditions                                       | Min<br>(Note 8) | Typ<br>(Note 7) | Max<br>(Note 8) | Units |

|---------------------------------------------------|---------------------------------------------------------------------------------------|--------------------------------------------------|-----------------|-----------------|-----------------|-------|

| HD YP <sub>B</sub> P <sub>R</sub> OS <sub>R</sub> | HD YP <sub>B</sub> P <sub>R</sub> Input:<br>Rising Edge Overshoot                     | AC Input Signal (Note 6)                         |                 | 3               |                 | %     |

| HD YP <sub>B</sub> P <sub>R</sub> t <sub>f</sub>  | HD YP <sub>B</sub> P <sub>R</sub> :<br>Video Fall Time                                | 90% to 10%, AC Input Signal (Note 6)             |                 | 8.4             |                 | ns    |

| HD YP <sub>B</sub> P <sub>R</sub> OS <sub>F</sub> | HD YP <sub>B</sub> P <sub>R</sub> :<br>Falling Edge Overshoot                         | AC Input Signal (Note 6)                         |                 | 3               |                 | %     |

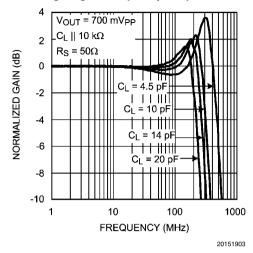

| Video Frequenc                                    | y Domain Response                                                                     |                                                  | •               | •               |                 |       |

| RGB BW                                            | RGB Input:<br>Channel Bandwidth (-3 dB)                                               | Large Signal BW                                  |                 | 400             |                 | MHz   |

| YP <sub>B</sub> P <sub>R</sub> BW                 | YP <sub>B</sub> P <sub>R</sub> Input (SD & HD):<br>Channel Bandwidth (-3 dB)          | Large Signal BW                                  |                 | 70              |                 | MHz   |

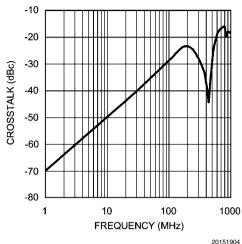

| V <sub>SEP Ch-Ch</sub><br>10 MHz                  | Video Amplifier 10 MHz Isolation<br>RGB Channel to Channel                            | (Note 13)                                        |                 | -50             |                 | dB    |

| V <sub>SEP INPUT-INPUT</sub><br>10 MHz            | Video Amplifier 10 MHz Isolation<br>RGB Input to YP <sub>B</sub> P <sub>R</sub> Input | (Note 13)                                        |                 | -55             |                 | dB    |

| SNR                                               | Signal to Noise Ratio                                                                 | AC Input Signal, C <sub>L</sub> = 8 pF (Note 13) |                 | 55              |                 | dB    |

#

| Symbol                   | Parameter                                                                   | Conditions                                                                                 | Min      | Тур      | Max      | Units |

|--------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|----------|----------|----------|-------|

|                          |                                                                             |                                                                                            | (Note 8) | (Note 7) | (Note 8) |       |

| V <sub>COLOR ERROR</sub> | IP <sub>B</sub> P <sub>R</sub> I Amplitude<br>(Calculated from RGB Outputs) | YP <sub>B</sub> P <sub>R</sub> Video Input,<br>100% Color Bar (any 3 colors),<br>(Note 14) |          | ±0.3     | ±2.5     | %     |

| θ <sub>COLOR ERROR</sub> | P <sub>B</sub> P <sub>R</sub> Phase Angle<br>(Calculated from RGB Outputs)  | YP <sub>B</sub> P <sub>R</sub> Video Input,<br>100% Color Bar (any 3 colors),<br>(Note 14) |          | ±0.2     | ±1.5     | deg   |

# **Sync Signal Electrical Characteristics**

Unless otherwise noted:  $T_A$  = 25°C,  $V_{CC}$  = +5.0V, Y Video $_{IN}$  = 0.7  $V_{PP}$ ,  $P_BP_R$  Video $_{IN}$  = ±350 mV,  $C_L$  = 8 pF, Video Outputs = 0.7  $V_{PP}$ .

| Symbol                     | Parameter                                               | Conditions                                             | Min      | Тур      | Max                  | Units |

|----------------------------|---------------------------------------------------------|--------------------------------------------------------|----------|----------|----------------------|-------|

|                            |                                                         |                                                        | (Note 8) | (Note 7) | (Note 8)             |       |

| V <sub>SYNCL</sub>         | H & V SYNC Low Input                                    | Pins 1 & 2                                             | -0.5     |          | 1.5                  | V     |

| V <sub>SYNCH</sub>         | H & V SYNC High Input                                   | Pins 1 & 2                                             | 3.0      |          | V <sub>CC</sub> +0.5 | V     |

| I <sub>O-SYNCH</sub>       | H & V SYNC Current Sink/Source<br>Capability            | 5 kΩ Load                                              |          | 3        |                      | mA    |

| t <sub>R/F-SYNC</sub>      | H & V SYNC Rise/Fall Time                               |                                                        |          | 15       |                      | ns    |

| t <sub>SYNC-WIDTH</sub>    | H & V SYNC Width Error Relative to H & V SYNC Input     | H & V SYNC Input                                       |          | 5        |                      | %     |

| t <sub>Y-SYNC-WIDTH</sub>  | H & V SYNC Width Error Relative to Composite SYNCS on Y | Composite SYNC on Y Input                              |          | 5        |                      | %     |

| t <sub>SYNC-DELAY</sub>    | 50% of H & V SYNC Input to Output                       | H & V SYNC Input                                       |          | 40       |                      | ns    |

| t <sub>Y-HSYNC-DELAY</sub> | 50% of H SYNC Input to Output                           | Composite SYNC on Y Input (Not During Vertical Period) |          | 70       |                      | ns    |

## **System Interface Signal Characteristics**

Unless otherwise noted:  $_{TA}$  = 25°C,  $V_{CC}$  = +5.0V, Y Video $_{IN}$  = 0.7  $V_{PP}$ ,  $P_BP_R$  Video $_{IN}$  = ±350 mV,  $C_L$  = 8 pF, Video Outputs = 0.7  $V_{PP}$ .

| Symbol          | Parameter                                         | Conditions            | Min      | Тур      | Max                  | Units |

|-----------------|---------------------------------------------------|-----------------------|----------|----------|----------------------|-------|

|                 |                                                   |                       | (Note 8) | (Note 7) | (Note 8)             |       |

| V <sub>IL</sub> | Logic Low Input Voltage<br>(Pins 24, 23, 22, 21)  |                       | -0.5     |          | 1.5                  | V     |

| V <sub>IH</sub> | Logic High Input Voltage<br>(Pins 24, 23, 22, 21) |                       | 3.0      |          | V <sub>CC</sub> +0.5 | V     |

| IL              | Logic Low Input Current<br>(Pins 24, 23, 22, 21)  | Input Voltage = 0.4V  |          | ±10      |                      | μΑ    |

| I <sub>H</sub>  | Logic High Input Current<br>(Pins 24, 23, 22, 21) | Input Voltage = 0.4V  |          | ±10      |                      | μΑ    |

| V <sub>OL</sub> | Logic Low Output Voltage<br>(Pins 24, 23, 22, 21) | I <sub>O</sub> = 3 mA |          | 0.5      |                      | V     |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not guaranteed. For guaranteed specifications, see the Electrical Characteristics tables.

Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. All video inputs must be properly terminated

Note 3: All voltages are measured with respect to GND, unless otherwise specified.

Note 4: Human Body Model, applicable std. MIL-STD-883, Method 3015.7. Machine Model, applicable std. JESD22-A115-A (ESD MM std. of JEDEC) Field-Induced Charge-Device Model, applicable std. JESD22-C101-C (ESD FICDM std. of JEDEC).

**Note 5:** The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $\theta_{JA}$ . The maximum allowable power dissipation at any ambient temperature is  $P_D = (T_{J(MAX)} - T_A)/\theta_{JA}$ . All numbers apply for packages soldered directly onto a PC Board.

**Note 6:** Input from RGB signal generator:  $t_r$ ,  $t_f = 1.5$  ns. Input from SDTV  $YP_BP_R$  signal generator:  $t_r$ ,  $t_f = 15$  ns. Input from HDTV  $YP_BP_R$  signal generator:  $t_r$ ,  $t_f = 8$  ns.

Note 7: Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not guaranteed on shipped production material.

**Note 8:** Datasheet min/max specification limits are guaranteed by design, test, or statistical analysis. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may change when the device is not operated under the listed test conditions.

Note 9: The supply current specified is the quiescent current for  $V_{CC}$  and 5V with  $R_L = \infty$ . Load resistors are not required and are not used in the test circuit; therefore, all the supply current is used by the device.

Note 10: Linearity Error is the maximum variation in step height of a 16 step staircase input signal waveform with a 0.7 V<sub>PP</sub> level at the input. All 16 are steps equal, with each at least 100 ns in duration.

Note 11:  $\Delta A_V$  track is a measure of the ability of any two amplifiers to track each other and quantifies the matching of the three gain stages. It is the difference in gain change between any two amplifiers with the contrast set to  $A_V$ C-50% and measured relative to the  $A_V$  max condition. For example, at  $A_V$  max the three amplifiers' gains might be 12.1 dB, 11.9 dB, and 11.8 dB and change to 2.2 dB, 1.9 dB and 1.7 dB respectively for contrast set to  $A_V$ C-50%. This yields a typical gain change of 10.0 dB with a tracking change of  $\pm$ 0.2 dB.

Note 12: The Machine Model ESD test is covered by specification EIAJ IC-121-1981. A 200 pF cap is charged to the specific voltage, then discharged directly into the IC with no external series resistor (resistance of discharge path must be under 50Ω).

Note 13: Measure output levels of the other two undriven amplifiers relative to the driven amplifier to determine channel separation. Terminate the undriven amplifier inputs to simulate generator loading. Repeat test at f<sub>IN</sub> = 10 MHz for V<sub>SEP</sub> 10 MHz.

Note 14: Any three color bar signals can be used as test signals. The RGB outputs shall be used to calculate the amplitudes and phases of the chroma results. These should fall within the limits specified.

## **Large Signal Frequency Response**

## 720p Color Bar Vectorscope

## Crosstalk vs. Frequency

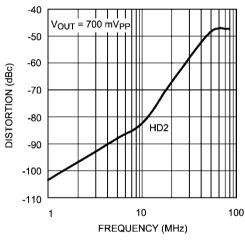

### Harmonic Distortion vs. Frequency

20151902

## **Application Information**

#### **GENERAL INFORMATION**

The LMH1251 is a high speed triple 2:1 video multiplexer with an integrated sync processor and color space converter. One input channel accepts standard RGBHV PC graphics video and the second input channel accepts  $\mathrm{YP_BP_R}$  component video. If the first input of the MUX is selected, the device will output the RGBHV video from the input with unity gain. If the second input of the MUX is selected, sync processing and color space conversion will be performed on the  $\mathrm{YP_BP_R}$  component signals to provide an equivalent RGBHV signal at the output.

## YPRPR to RGBHV PROCESSING

The LMH1251 is capable of processing 480i, 480p, 576i, 576p, 720p, 1080i, and 1080p  $YP_BP_R$  component video signals only. S-Video, composite NTSC, or composite PAL video will not be converted by the LMH1251. For High Definition, 720p and 1080i/1080p video, the LMH1251 will convert the luma and chroma signals into primary RGB signals according to the linear arithmetic formula specified in the EIA/ CEA-770.3-C Standard for High Definition Analog Component TV. For Standard Definition video, the LMH1251 will perform the conversion according to the linear arithmetic formula specified in the EIA/CEA-770.2-C Standard for Standard Definition Analog Component TV. The advanced analog architecture that is employed to perform the color space conversion is precise to within 2.5% of amplitude and 1.5° of phase error on a vectorscope with a color bar test signal. This is illustrated with a vectorscope plot of a converted color bar signal in the 720p format show in the Typical Performance Characteristics section.

Note that although 480i/576i component video is supported by the LMH1251, most PC display monitors cannot handle such line rates. Typically, only 480p, 576p, 720p, and 1080i/1080p are within the displayable line rate range of LCD and CRT monitors. Furthermore, the scaler in LCD monitor systems must include a de-interlacer for it to display interlaced video such as with 1080i.

### Component Video Formats Supported By The LMH1251

- 480i\*

- 480p

- 576i\*

- 576p

- 720p

- 1080i at 25, 29.97, and 30 Hz frame rate

- 1080p at 25, 29.97, and 30 Hz frame rate

Note: \*These formats with Macrovision are not supported. See Macrovision Compatibility section for more information.

#### **AUTO/MANUAL FORMAT DETECTION**

The LMH1251 can either automatically detect the input format of the component video source, or it can be put in a manual mode where the MCU has the flexibility to specify which  $\rm YP_BP_R$  to RGBHV processing scheme for the device to apply depending on the input format. If a logic high is applied to Pin 23, the LMH1251 will be in the AUTO detection mode, which is typically recommended. In this mode, the device will appropriately use the proper  $\rm YP_BP_R$  to RGB processing scheme based on its input format detection. If a logic low is applied to Pin 23, the LMH1251 will be in the manual detection mode. In this mode, the MCU must apply a logic low to Pin 22 if the processing scheme is for SDTV video formats, and a logic high if the processing scheme is for HDTV formats.

Note that in the AUTO mode, Pin 22 becomes an output pin, and outputs a logic low if an SD video input is detected and a logic high if an HD video input is detected, as notification to the MCII

#### **MACROVISION COMPATIBILITY**

The LMH1251 is compatible with the Macrovision Video Copy Protection System commonly used in 480p/576p progressive-scan DVD video sources. The LMH1251 does not support 480i/576i formats with Macrovision enabled. Macrovision, which is enabled by special circuitry inside many DVD players, embeds pseudo sync pulses and pseudo video pulses into the source signal during the vertical blanking interval. This system is intended to prohibit and deter analog video recording.

For 480p/576p formats with Macrovision enabled, the internal sync processor of the LMH1251 will output the true H sync pulses only and effectively ignore the pseudo sync pulses; its video processor will apply proper SDTV color space conversion, and the pseudo video pulses will pass through to comply with Macrovision.

#### **POWER SAVE MODE**

The LMH1251 is equipped with a power saving mode which is controlled by Pin 21. This pin is a logic level input. The device will enter a low power mode when the power save pin is applied with a logic high by the MCU. Under these conditions, the IC reduces its current consumption to a minimum as specified in the Electrical Characteristics section. However, the sync processor and switch will always remain active. During power save mode, the RGB video outputs are held to the blank level, while the sync signals are allowed to continue to be processed and/or passed through. Based on the absence or presence of sync signals at the output of the LMH1251, the MCU can determine whether to bring the system to a low power consumption state.

#### **INTERNAL VOLTAGE REFERENCE**

Proper operation of the LMH1251 requires a very accurate reference voltage. This voltage is generated in the  $V_{REF}$  block. The output of the  $V_{REF}$  stage goes to a number of blocks in the video sections and sets the internal bias. To insure an accurate voltage over temperature, an external resistor is used to set the current in the  $V_{REF}$  stage. The external resistor is connected to Pin 15. This resistor should be 1% and have a temperature coefficient under 100 ppm/°C.

## **H SYNC AND V SYNC CHARACTERISTICS**

When the RGBHV input is selected, the LMH1251 will produce H and V sync output signals of the same sync polarities as the H and V sync input signals. For example, VESA standard timing input signals with positive, leading edge sync pulses will produce positive, leading edge pulses in the H and V sync output signals. However when the  $\mathrm{YP_BP_R}$  input is selected, both sync outputs are always positive, leading edge syncs, set by the internal sync processor.

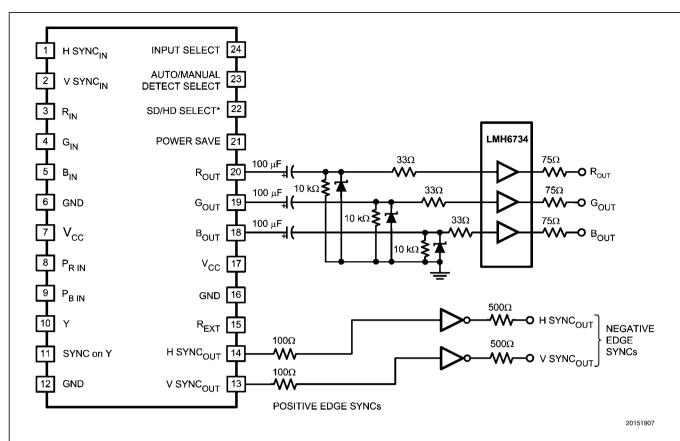

Display systems typically sync lock to negative edges of H and V sync signals, and some displays may have polarity correction to accommodate either positive or negative edges. Logic inverters can be used to invert the H and V sync output signals of the LMH1251 to satisfy the negative edge requirement.

It is worth noting that when  $YP_BP_R$  is selected with an SDTV input format, some H sync output pulses will be half the width of the normal H sync pulses due to the narrow equalization pulses in the vertical blanking interval. When the H sync signal changes from full to half width pulses, or vice versa, the H

sync period or scan rate changes with respect to the negative sync edges. These brief changes in the H sync period may cause a negative-edge triggered horizontal PLL to lose sync lock momentarily, which can cause the on-screen picture to distort or blank repeatedly. This condition can be rectified using a logic inverter to produce negative, leading edge H sync pulses. When the inverted H sync signal changes from full to half width pulses, or vice versa, the H sync period will remain constant with respect to the negative edges, which is correct H sync operation for negative-edge triggered displays.

#### **OUTPUT DRIVE CHARACTERISTICS**

The LMH1251 is designed to interface with an ADC or preamplifier through an AC coupling capacitor as shown below in Figure 1. The RGB outputs of the LMH1251 are 700 mV<sub>PP</sub> video signals with the black level at approximately 2.1V (typ), which is the chip's internal voltage reference level. The H sync and V sync output signals are CMOS logic outputs that swing rail-to-rail.

The RGBHV outputs cannot be used to drive standard  $150\Omega$  video loads and require high-bandwidth buffers for this kind of application. For example, if the LMH1251 is to be designed into a stand-alone converter box application, the configuration in Figure 2 is recommended. To drive a display monitor over a standard VGA cable, a wideband, low distortion triple video buffer, such as the LMH6739, can be used with a gain of +2 to drive the RGB video signals of the LMH1251, and logic inverters can be used to drive its H and V sync signals.

FIGURE 1. Typical LMH1251 Application

FIGURE 2. Simplified Application Diagram for Driving a VGA Cable

9

### **LAYOUT CONSIDERATIONS**

The most important point to note regarding the layout of the LMH1251 on a PCB is that the trace length between the output pins of the LMH1251 and the input AC coupling capacitors of the next stage ADC or preamplifier must be as minimal as possible. The trace lengths of the H Sync and V Sync outputs should also be minimized, as the capacitive loading on these outputs must not exceed 6 pF. For long signal paths leading up to the input of the LMH1251, controlled impedance lines

should be used, along with impedance matching elements. Bypass capacitors should be placed as close as possible to the supply pins of the device. The larger electrolytic bypass capacitor can be located farther from the device. The 10  $k\Omega$  external resistor should also be placed as close as possible to the  $R_{\rm EXT}$  pin. All video signals must be kept away from the  $R_{\rm EXT}$  pin (15). This pin has a very high input impedance and will pick up any high frequency signals routed near it.

# **Test Circuit**

FIGURE 3. Test Circuit

MTC24 (Rev E)

www.national.com

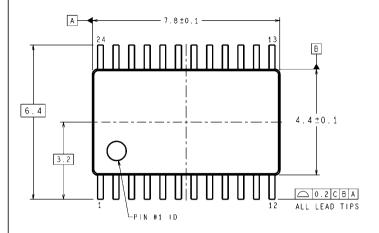

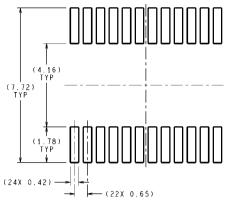

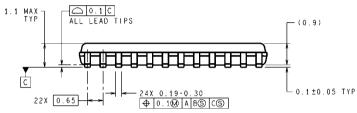

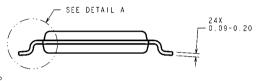

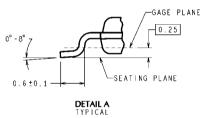

# Physical Dimensions inches (millimeters) unless otherwise noted

LAND PATTERN RECOMENDATION

**DIMENSIONS ARE IN MILLIMETERS**

24-Pin TSSOP NS Package Number MTC24

11

## **Notes**

For more National Semiconductor product information and proven design tools, visit the following Web sites at:

| Pr                             | oducts                       | Design Support          |                                |  |  |

|--------------------------------|------------------------------|-------------------------|--------------------------------|--|--|

| Amplifiers                     | www.national.com/amplifiers  | WEBENCH                 | www.national.com/webench       |  |  |

| Audio                          | www.national.com/audio       | Analog University       | www.national.com/AU            |  |  |

| Clock Conditioners             | www.national.com/timing      | App Notes               | www.national.com/appnotes      |  |  |

| Data Converters                | www.national.com/adc         | Distributors            | www.national.com/contacts      |  |  |

| Displays                       | www.national.com/displays    | Green Compliance        | www.national.com/quality/green |  |  |

| Ethernet                       | www.national.com/ethernet    | Packaging               | www.national.com/packaging     |  |  |

| Interface                      | www.national.com/interface   | Quality and Reliability | www.national.com/quality       |  |  |

| LVDS                           | www.national.com/lvds        | Reference Designs       | www.national.com/refdesigns    |  |  |

| Power Management               | www.national.com/power       | Feedback                | www.national.com/feedback      |  |  |

| Switching Regulators           | www.national.com/switchers   |                         |                                |  |  |

| LDOs                           | www.national.com/ldo         |                         |                                |  |  |

| LED Lighting                   | www.national.com/led         |                         |                                |  |  |

| PowerWise                      | www.national.com/powerwise   |                         |                                |  |  |

| Serial Digital Interface (SDI) | www.national.com/sdi         |                         |                                |  |  |

| Temperature Sensors            | www.national.com/tempsensors |                         |                                |  |  |

| Wireless (PLL/VCO)             | www.national.com/wireless    |                         |                                |  |  |

THE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION ("NATIONAL") PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COMPLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO MAKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIME WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS, IMPLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.

TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEMS NECESSARY TO SUPPORT NATIONAL'S PRODUCT WARRANTY. EXCEPT WHERE MANDATED BY GOVERNMENT REQUIREMENTS, TESTING OF ALL PARAMETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORMED. NATIONAL ASSUMES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COMPONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.

EXCEPT AS PROVIDED IN NATIONAL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE CHIEF EXECUTIVE OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.

Copyright© 2008 National Semiconductor Corporation

For the most current product information visit us at www.national.com

National Semiconductor Americas Technical Support Center Email: support@nsc.com Tel: 1-800-272-9959 National Semiconductor Europe Technical Support Center Email: europe.support@nsc.com German Tel: +49 (0) 180 5010 771 English Tel: +44 (0) 870 850 4288 National Semiconductor Asia Pacific Technical Support Center Email: ap.support@nsc.com

National Semiconductor Japan Technical Support Center Email: jpn.feedback@nsc.com