# **BMP388** Digital pressure sensor

## BMP388 – Datasheet

| Document revision           | 1.7                                                                                                                                                                                                |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Document release date       | November 2020                                                                                                                                                                                      |

| Document number             | BST-BMP388-DS001-07                                                                                                                                                                                |

| Technical reference code(s) | 0 273 300 511                                                                                                                                                                                      |

| Notes                       | Data and descriptions in this document are subject to change without notice.<br>Product photos and pictures are for illustration purposes only and may differ<br>from the real product appearance. |

## **BMP388**

### Digital pressure sensor

The BMP388 is a digital sensor with pressure and temperature measurement based on proven sensing principles. The sensor module is housed in an extremely compact 10-pin metal-lid LGA package with a footprint of only  $2.0 \times 2.0 \text{ mm}^2$  and max 0.8 mm package height. Its small dimensions and its low power consumption of  $3.4 \mu A @1Hz$  allow the implementation in battery driven devices such as mobile phones, GPS modules or watches.

Typical applications

- Vertical velocity indication (e.g. rise/sink speed)

- Internet of things

- Enhancement of GPS navigation (e.g. time-to-first-fix improvement, dead-reckoning, slope detection)

- Indoor navigation & localization (floor detection, elevator detection)

- Outdoor navigation, leisure and sports applications

- Weather forecast

- Health care applications (e.g. spirometry)

- Fitness applications like enhancement of calorie detection

- AR & VR applications

- Context awareness

#### **Target Devices**

- Flying toys

- Drones

- Handsets such as mobile phones, tablet PCs, GPS devices

- Navigation systems

- Portable health care devices

- Home weather stations

- Watches

- White goods

#### Key features

| Table 1: Key Features of BMP388                   |                                                                                                                         |  |  |  |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Package                                           | 2.0 mm x 2.0 mm x 0.75 mm metal lid LGA                                                                                 |  |  |  |

| Digital interface                                 | I <sup>2</sup> C (up to 3.4 MHz) and SPI (3 and 4 wire, up to 10 MHz)                                                   |  |  |  |

| Supply voltage                                    | V <sub>DD</sub> main supply voltage range: 1.65 V to 3.6 V<br>V <sub>DDIO</sub> interface voltage range: 1.2 V to 3.6 V |  |  |  |

| Relative accuracy                                 | typ. ± 8 Pa, equiv. to ± 0.66 m<br>(900 1100 hPa, 25 40 °C )                                                            |  |  |  |

| Absolute accuracy                                 | typ. ± 50 Pa<br>(3001100 hPa, -20+65 °C)                                                                                |  |  |  |

| Temperature coefficient offset                    | typ. ± 0.75 Pa/K<br>(0 55°C @700 -1100 hPa)                                                                             |  |  |  |

| Current consumption                               | 3.4 $\mu A$ at 1 Hz pressure and temperature 2.0 $\mu A$ in sleep mode                                                  |  |  |  |

| Operating range                                   | -40 – +85 °C, 300–1250 hPa                                                                                              |  |  |  |

| The product is RoHS compliant, halogen-free, MSL1 |                                                                                                                         |  |  |  |

BMP388 enables accurate altitude tracking and is specifically suited for drone applications. The best-in-class TCO between -20-65°C for accurate altitude measurement over a wide temperature range of the BMP388 greatly enhance the drone flying experience by making accurate steering easier. It is compatible for use with other Bosch sensors, including the new BMI088 for better performance, robustness and stability. The new BMP388 sensor offers outstanding design flexibility, providing a single package solution that can also be easily integrated into other existing and upcoming devices such as smart homes, industrial products and wearables.

The sensor is more accurate than its predecessor BMP280, covering a wide measurement range from 300 hPa to 1250 hPa.

This new barometric pressure sensor exhibits an attractive price-performance ratio coupled with low power consumption.

It is available in a compact 10-in 2.0 x 2.0 x 0.75 mm<sup>3</sup> LGA package with metal lid

Due to the built-in hardware synchronization of the pressure sensor data and its ability to synchronize data from external devices such as acceleration sensors, the BMP388 is ideally suited for fitness and navigation applications which require highly accurate, low power and low latency sensor data fusion.

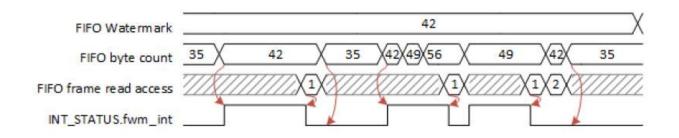

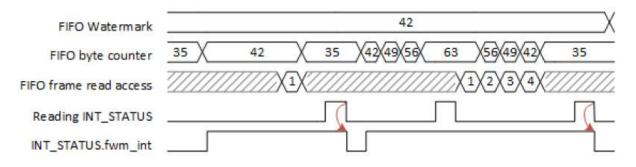

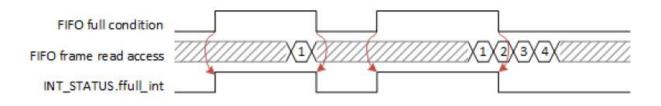

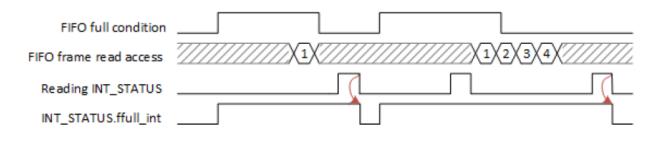

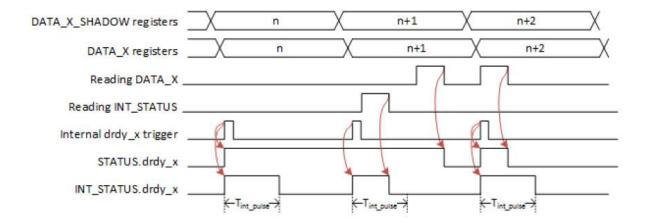

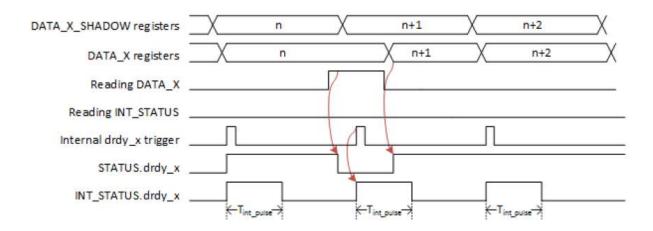

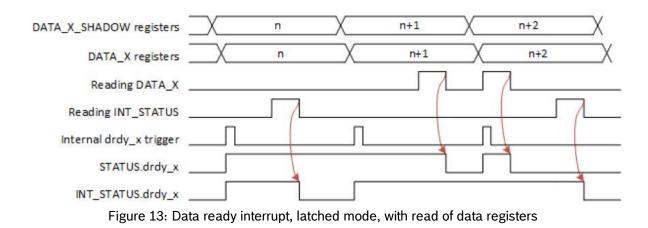

The new interrupt functionality provides simple access to data and storage. Examples of interrupts than can be used in a power efficient manner without using software algorithms include: Data ready interrupt, watermark interrupt (on byte level) or FIFO full interrupt.

BMP388 also includes a new FIFO functionality. This greatly improves ease of use while helping to reduce power consumption of the overall device system during full operation. The integrated 512 byte FIFO buffer supports low power applications and prevents data loss in non-real-time systems.

| 1. | Spe                 | ecification                             | 7  |

|----|---------------------|-----------------------------------------|----|

| 2. | Abs                 | solute maximum ratings                  | 9  |

| 3. | Fun                 | nctional description                    | 9  |

| 3  | 3.1.                | Block diagram                           | 10 |

| 3  | 3.2.                | Power management                        |    |

|    | 3.3.                | Power modes                             |    |

|    | 3.3.<br>3.3.        |                                         |    |

|    | 3.3.                |                                         |    |

|    | 3.3.                |                                         |    |

|    | 3.3.                | 4. Mode transition diagram              | 13 |

| 3  | 3.4.                | Measurement flow                        | 13 |

|    | 3.4.                | 1. Pressure measurement                 | 14 |

|    | 3.4.                | I                                       |    |

|    | 3.4.                |                                         |    |

|    | 3.4.                | 4. Oversampling                         | 15 |

| 3  | 3.5.                | Filter selection                        | 17 |

| 3  | 3.6.                | FIFO Description                        | 18 |

|    | 3.6.                |                                         |    |

|    | 3.6.                |                                         |    |

|    | 3.6.                | 3. FIFO read out                        |    |

|    | 3.6.                |                                         |    |

|    | 3.6.                |                                         |    |

|    | 3.6.                | 7. FIFO flush conditions                | 21 |

| 3  | 3.7.                | Interrupts                              |    |

|    | 3.7.                |                                         |    |

|    | 3.7.                |                                         |    |

|    | 3.7.                |                                         |    |

|    | 3.7.                |                                         |    |

|    | 3.7.                | •                                       |    |

|    | 3.8.                | Current consumption                     |    |

| 3  | 3.9.                | Measurement timings                     |    |

|    | 3.9.<br>3.9.        |                                         |    |

|    | 3.9.                |                                         |    |

| 3  | 3.10.               | Data readout from data registers        |    |

|    | 3.10                | 0.1. Data register shadowing            | 27 |

| 3  | 3.11.               | Output compensation                     |    |

|    | 3.11                | L.1. Memory Map Trimming Coefficients   | 28 |

| 4. | Glo                 | bal memory map and register description |    |

|    | 4.1.                | General remarks                         |    |

|    | 4.2.                | Datasheet Memory Map                    |    |

|    | 4.3.                | Register description                    |    |

| 2  | <b>+.3.</b><br>4.3. | •                                       |    |

|    | 4.3.                |                                         |    |

|    | 4.3.                |                                         |    |

|    | 4.3.                |                                         |    |

|    | 4.3.                | <b>v</b>                                |    |

|    | 4.3.                | 0                                       |    |

|    | 4.3.                |                                         |    |

|    | 4.3.                | 8. Register 0x11 "INT STATUS"           |    |

|                                                                                                                               | <ul><li>3.9. Register 0x12 0x13 "FIFO_LENGTH"</li><li>3.10. Register 0x14 "FIFO_DATA"</li></ul>                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                               | 3.10. Register 0x14 FIFO_DATA                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

|                                                                                                                               | 3.12. Register 0x17 "FIFO CONFIG 1"                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

|                                                                                                                               | 3.13. Register 0x18 "FIFO CONFIG 2"                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| 4.3                                                                                                                           | 3.14. Register 0x19 "INT_CTRL"                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| 4.3                                                                                                                           | 3.15. Register 0x1A "IF_CONF"                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

|                                                                                                                               | 3.16. Register 0x1B "PWR_CTRL"                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

|                                                                                                                               | 3.17. Register 0x1C "OSR"                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

|                                                                                                                               | 3.18. Register 0x1D "ODR"                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

|                                                                                                                               | 3.19. Control settings for odr_sel                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                  |

|                                                                                                                               | <ul> <li>3.20. Register 0x1F "CONFIG"</li> <li>3.21. Register 0x30 0x57 "calibration data"</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

|                                                                                                                               | 3.22. Register 0x300x37 calibration data                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

| 4.0                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

|                                                                                                                               | igital interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

| 5.1.                                                                                                                          | Interface selection                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 40                                                                                                                               |

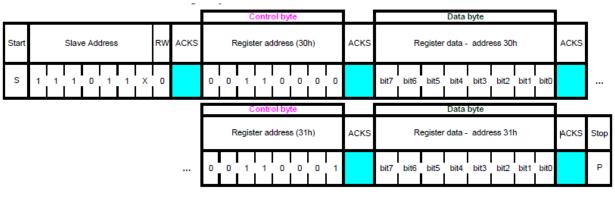

|                                                                                                                               | I <sup>2</sup> C Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| • • •                                                                                                                         | 2.1. I <sup>2</sup> C write                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                  |

| 5.2                                                                                                                           | 2.2. I <sup>2</sup> C read                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

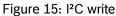

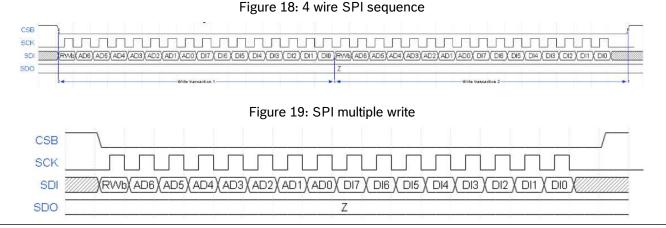

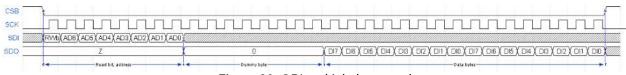

| 5.3.                                                                                                                          | SPI interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 42                                                                                                                               |

|                                                                                                                               | 3.1. SPI write                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                  |

| 5.3                                                                                                                           | 3.2. SPI read                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 43                                                                                                                               |

| 5.4.                                                                                                                          | Interface parameter specification                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

|                                                                                                                               | 4.1. General interface parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

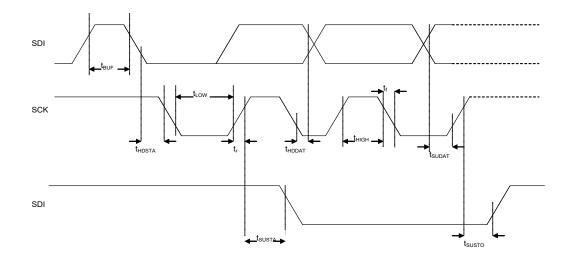

| 5.4                                                                                                                           | 4.2. I <sup>2</sup> C timings                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

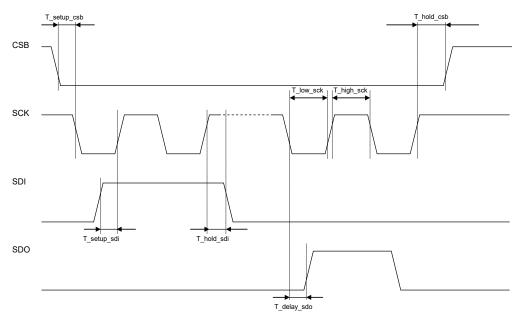

| 5.4                                                                                                                           | 4.3. SPI timings                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45                                                                                                                               |

| с D:                                                                                                                          | n-out and connection diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 16                                                                                                                               |

|                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

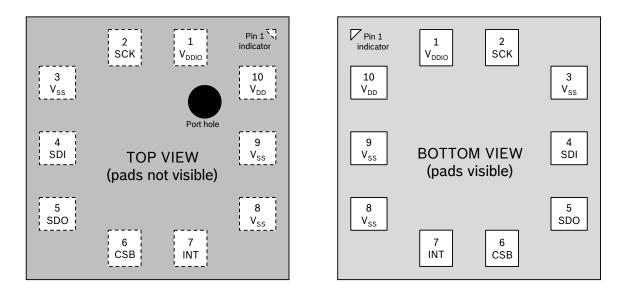

| 6.1.                                                                                                                          | Pin-out                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

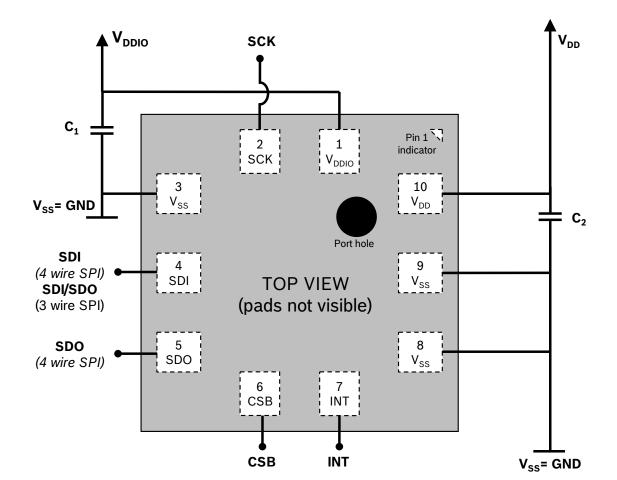

| 6.2.                                                                                                                          | Connection diagram ¾-wire SPI                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                                                                               |

|                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

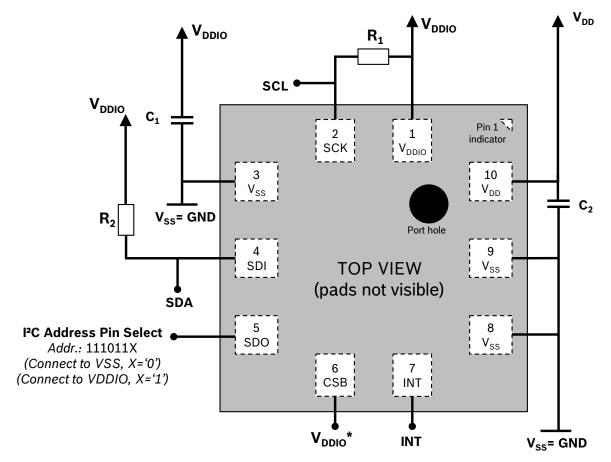

| 6.3.                                                                                                                          | Connection diagram I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| 6.3.<br>7. Pa                                                                                                                 | Connection diagram I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br><b>49</b>                                                                                                                  |

| 6.3.<br>7. Pa                                                                                                                 | Connection diagram I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br><b>49</b>                                                                                                                  |

| 6.3.<br>7. Pa                                                                                                                 | Connection diagram I <sup>2</sup> C                                                                                                                                                                                                                                                                                                                                                                                                                                              | 48<br><b>49</b><br>49                                                                                                            |

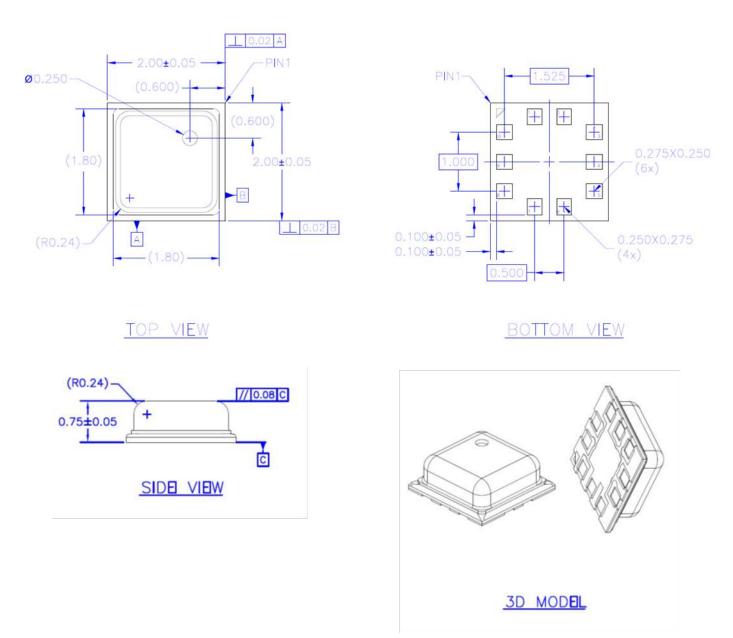

| 6.3.<br>7. Pa<br>7.1.<br>7.2.                                                                                                 | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.                                                                                         | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern<br>Marking                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3                                                                                  | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3                                                                                  | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3                                                                                  | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3                                                                                  | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

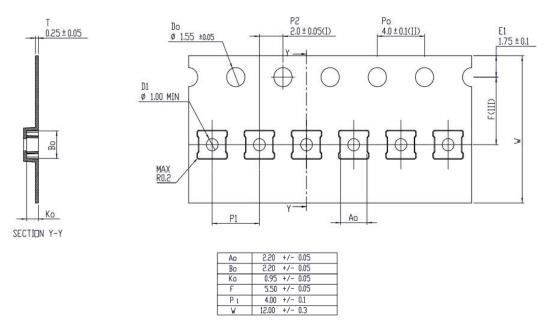

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3<br>7.3<br>7.4.<br>7.5.<br>7.5.                                                   | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern<br>Marking<br>3.1. Mass production samples<br>3.2. Engineering samples<br>Soldering guidelines<br>Tape and reel specification<br>5.1. Dimensions                                                                                                                                                                                                                    |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3<br>7.3<br>7.4.<br>7.5.<br>7.5.                                                   | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3<br>7.3<br>7.4.<br>7.5.<br>7.5.                                                   | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

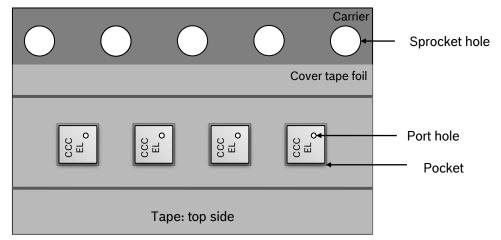

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.4.<br>7.5.<br>7.5<br>7.5                                                     | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.5<br>7.5<br>7.6.<br>7.7.                               | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern<br>Marking<br>3.1. Mass production samples<br>3.2. Engineering samples<br>Soldering guidelines<br>Tape and reel specification<br>5.1. Dimensions<br>5.2. Orientation within the reel<br>Mounting and assembly recommendations<br>Environmental safety                                                                                                               |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.5<br>7.5<br>7.6.<br>7.7.<br>7.7                        | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.5<br>7.5<br>7.6.<br>7.7<br>7.7<br>7.7                  | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern<br>Marking                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.5<br>7.5<br>7.6.<br>7.7<br>7.7<br>7.7                  | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern<br>Marking<br>3.1. Mass production samples<br>3.2. Engineering samples<br>Soldering guidelines<br>Tape and reel specification<br>5.1. Dimensions<br>5.2. Orientation within the reel<br>Mounting and assembly recommendations<br>Environmental safety<br>7.1. RoHS<br>7.2. Halogen content<br>7.3. Internal package structure                                       | 48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50                                                 |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.5<br>7.5<br>7.6.<br>7.7<br>7.7<br>7.7<br>8. Le         | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     | 48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>51<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52<br>52 |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.5<br>7.5<br>7.6.<br>7.7<br>7.7<br>7.7<br>8. Le<br>8.1. | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     | 48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50                                                 |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3.<br>7.3<br>7.4.<br>7.5.<br>7.5<br>7.6.<br>7.7.<br>7.7<br>7.7<br>8. Le<br>8.1.<br>8.2.    | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern<br>Marking<br>3.1. Mass production samples<br>3.2. Engineering samples<br>Soldering guidelines<br>Tape and reel specification<br>5.1. Dimensions<br>5.2. Orientation within the reel<br>Mounting and assembly recommendations<br>Environmental safety<br>7.1. RoHS<br>7.2. Halogen content<br>7.3. Internal package structure<br>Engineering samples<br>Product use | 48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50                                                 |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.5<br>7.5<br>7.6.<br>7.7<br>7.7<br>7.7<br>8. Le<br>8.1. | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern                                                                                                                                                                                                                                                                                                                                                                     | 48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50                                                 |

| 6.3.<br>7. Pa<br>7.1.<br>7.2.<br>7.3<br>7.3<br>7.4.<br>7.5<br>7.6.<br>7.7<br>7.7<br>7.7<br>8. Le<br>8.1.<br>8.2.<br>8.3.      | Connection diagram I <sup>2</sup> C<br>ackage, reel and environment<br>Outline dimensions<br>Landing pattern<br>Marking<br>3.1. Mass production samples<br>3.2. Engineering samples<br>Soldering guidelines<br>Tape and reel specification<br>5.1. Dimensions<br>5.2. Orientation within the reel<br>Mounting and assembly recommendations<br>Environmental safety<br>7.1. RoHS<br>7.2. Halogen content<br>7.3. Internal package structure<br>Engineering samples<br>Product use | 48<br>49<br>49<br>49<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50<br>50                                                 |

### 1. Specification

If not stated otherwise,

- All values are valid over the full voltage range

- All minimum/maximum values are given for the full accuracy temperature range

- Minimum/maximum values of drifts, offsets and temperature coefficients are  $\pm 3\sigma$  values over lifetime

- Typical values of currents and state machine timings are determined at 25 °C

- Typical values of currents and state machine timings are determined at 25°C. minimum/maximum values of currents are determined at -40°C/85°C.

- Minimum/maximum values of state machine timings are determined using corner lots over 0...+65 °C temperature range.

| Table 2: General electrical | parameter specifications |

|-----------------------------|--------------------------|

|-----------------------------|--------------------------|

| OPERATING CONDITIONS BMP388              |                                                            |                                               |      |                    |      |      |  |

|------------------------------------------|------------------------------------------------------------|-----------------------------------------------|------|--------------------|------|------|--|

| Parameter                                | Symbol                                                     | Condition                                     | Min  | Тур                | Max  | Unit |  |

| Operating                                | TA                                                         | operational                                   | -40  | 25                 | +85  | °C   |  |

| temperature range                        | TA                                                         | full accuracy                                 | 0    |                    | +65  | C    |  |

| Operating pressure<br>range              | Р                                                          | full accuracy                                 | 300  |                    | 1250 | hPa  |  |

| Sensor supply<br>voltage                 | V <sub>DD</sub>                                            | ripple max. 50mVpp                            | 1.65 | 1.8                | 3.6  | V    |  |

| Interface supply<br>voltage              | Vddio                                                      |                                               | 1.2  | 1.8                | 3.6  | V    |  |

| Sleep current                            | IDD,sleep                                                  | V <sub>DD</sub> = V <sub>DDIO</sub> 1.8-3.6 V |      | 2                  |      | μΑ   |  |

| Peak current                             | I <sub>peak</sub>                                          | during pressure<br>measurement                |      | 700                | 800  | μA   |  |

| Current at<br>temperature<br>measurement | Iddt                                                       |                                               |      | 300                | 400  | μΑ   |  |

| Relative accuracy                        | A <sub>rel</sub>                                           | 900 1100 hPa                                  |      | ±0.08 <sup>2</sup> |      | hPa  |  |

| pressure <sup>1</sup>                    | Arel                                                       | 25 40 °C                                      |      | ±66                |      | cm   |  |

| Offset temperature                       | тсо                                                        | 700-1100 hPa<br>0 55 °C                       |      | ±0.75              |      | Pa/K |  |

| coefficient                              | 100                                                        | 700-1100 hPa<br>-200 °C                       |      | ±1.0               |      | Pa/K |  |

| Absolute accuracy                        | $A^P_full$                                                 | 300 1100 hPa<br>-20 65 °C                     |      | ±0.50              |      | hPa  |  |

| pressure                                 | pressure A <sup>P</sup> <sub>ext</sub> 9001100 hPa 2540 °C |                                               |      | ±0.40              |      | hPa  |  |

<sup>2</sup> Mean value

<sup>&</sup>lt;sup>1</sup> Per 10 kPa steps

#### Bosch Sensortec | BMP388 Datasheet

|                                                                                      | AP                         | 1100 1250 hPa<br>0 65 °C                                                       | -1.5 | ±0.50  | 1.5                 | hPa |

|--------------------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------|------|--------|---------------------|-----|

| Resolution of<br>output data in<br>highest resolution<br>mode at lowest<br>bandwidth | R <sup>P</sup>             | Pressure                                                                       |      | 0.016  |                     | Pa  |

|                                                                                      | $V_{p,full}$               | Full bandwidth, highest<br>resolution<br>See chapter 3.4.4                     |      | 1.2    |                     | Ра  |

| Noise in pressure                                                                    | $V_{p,filtered}$           | Lowest bandwidth, highest<br>resolution<br>See chapter 3.4.4                   |      | 0.03   |                     | Pa  |

| Absolute accuracy                                                                    | AT                         | @ 25 °C                                                                        |      | ±0.3   |                     | °C  |

| temperature <sup>3</sup>                                                             |                            | 0 +65 °C                                                                       |      | ±0.50  |                     | °C  |

| Long term stability <sup>4</sup>                                                     | $\Delta P_{stab}$          | 12 months                                                                      |      | ±0.33  |                     | hPa |

| Solder drifts                                                                        |                            | Minimum solder height 50<br>µm                                                 |      | < ±1.0 |                     | hPa |

| Start-up time                                                                        | t <sub>startup</sub>       | Time to first communication after both $V_{DD} > 1.58V$ and $V_{DDIO} > 0.65V$ |      |        | 2                   | ms  |

| Possible sampling<br>rate                                                            | $f_{sample}$               | osrs_t = osrs_p = 1;<br>See chapter 3.9                                        |      |        | 200                 | Hz  |

| ODR accuracy                                                                         | $\Delta t_{	ext{standby}}$ | 25°C                                                                           |      | 2      | +/- 12 <sup>5</sup> | %   |

$^4$  Long term stability is specified in the full accuracy operating pressure range 0  $\dots$  65°C

<sup>&</sup>lt;sup>3</sup> Temperature measured by the internal temperature sensor. This temperature value depends on the PCB temperature, sensor element self-heating and ambient temperature and is typically above ambient temperature.

<sup>&</sup>lt;sup>5</sup> From -40 to 85°C

### 2. Absolute maximum ratings

The absolute maximum ratings are provided in Table 3 .

| Parameter                                         | Symbol              | Condition                    | Min                               | Мах                     | Unit |

|---------------------------------------------------|---------------------|------------------------------|-----------------------------------|-------------------------|------|

| Voltage at any supply pin                         |                     | $V_{DD}$ and $V_{DDIO}$ Pin  | -0.3                              | 3.8                     | V    |

| Voltage at any interface pin                      |                     |                              | Vss -0.3                          | V <sub>DDIO</sub> + 0.3 | V    |

| Storage temperature                               |                     | ≤ 65% rel. H.                | -45                               | +85                     | °C   |

| Overpressure survivability                        | Pover               |                              |                                   | 2 000 000               | Pa   |

| Mechanical shock                                  | Ms                  | MIL-STD-883H<br>2002.5       |                                   | 12000                   | g    |

| Maximum allowable dust particle<br>inside package | Dust <sub>MAX</sub> | ISO 12103-1 A2               |                                   | 300 <sup>6</sup>        | μm   |

| ESD                                               |                     | Charge device model<br>(CDM) | Class<br>C2a:<br>500V to<br><750V |                         |      |

|                                                   |                     | Human body model<br>(HBM)    | Class 2:<br>2 kV                  |                         |      |

----

Note: Stresses above these listed maximum ratings may cause permanent damage to the device. Exposure beyond specified electrical characteristics (Table 2) may affect device reliability or cause malfunction.

### 3. Functional description

The BMP388 consists of a Piezo-resistive pressure sensing element and a mixed-signal ASIC. The ASIC performs A/D conversions and provides the conversion results and sensor specific compensation data through a digital interface.

BMP388 provides highest flexibility to the designer and can be adapted to the requirements regarding accuracy, measurement time and power consumption by selecting from a high number of possible combinations of the sensor settings.

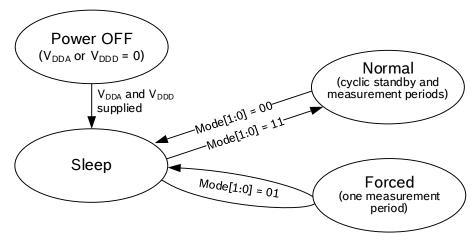

BMP388 can be operated in three power modes (see section 3.3):

sleep mode

normal mode

forced mode

1

In sleep mode, no measurements are performed. Normal mode comprises an automated perpetual cycling between an active measurement period and an inactive standby period. In forced mode, a single measurement is performed. When the measurement is finished, the sensor returns to sleep mode.

<sup>&</sup>lt;sup>6</sup> Defined by hole size

A set of oversampling settings is available ranging from ultra-low power to highest resolution setting in order to adapt the sensor to the target application. The settings are predefined combinations of pressure measurement oversampling and temperature measurement oversampling. Pressure and temperature measurement oversampling can be selected independently from 0 to 32 times oversampling (see sections 3.4.1 and 3.4.2):

- Temperature measurement

- Ultra low power

- Low power

- Standard resolution

- High resolution

- Ultra high resolution

- Highest resolution

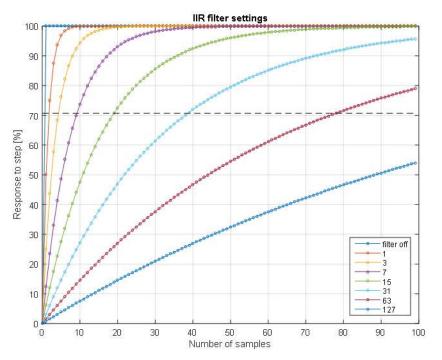

BMP388 is equipped with a built-in IIR filter in order to minimize short-term disturbances in the output data caused by the slamming of a door or window. The filter coefficient ranges from 0 (off) to 127.

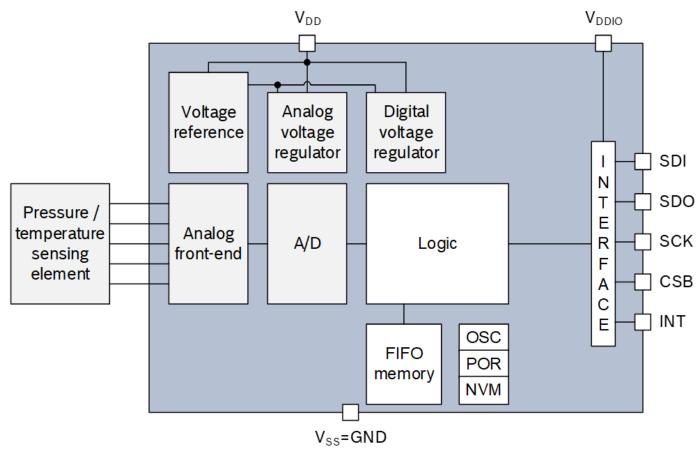

#### 3.1. Block diagram

Figure 1 shows a simplified block diagram of the BMP388:

Figure 1: Block Diagram BMP388

### 3.2. Power management

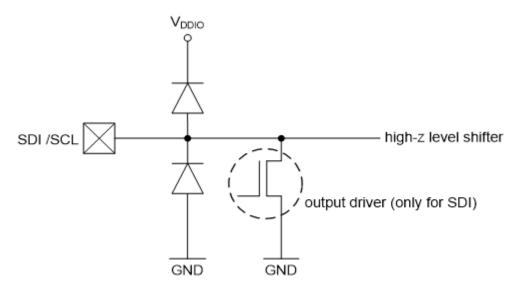

The BMP388 has two separate power supply pins

- V<sub>DD</sub> is the main power supply for all internal analog and digital regulator blocks.

- VDDIO is a separate power supply pin, used for the supply of the digital interface.

V<sub>DD</sub> and V<sub>DDIO</sub> pins can be energized in any order.

A power-on reset generator is built in which resets the logic circuitry and the register values after the power-on sequence. The slope for ramp up time must not be less than 10 ms. After powering up, the sensor settles in sleep mode (see section 3.3).

Completion of the power-on-reset or soft reset is indicated by the bit por\_detected[0]. The bit is cleared after reading.

Holding any interface pin (SDI, SDO, SCK or CSB) at a logical high level when V<sub>DDIO</sub> is switched off can permanently damage the device due caused by excessive current flow through the ESD protection diodes.

| Table 4: mode settings       |                |      |      |      |                   |  |

|------------------------------|----------------|------|------|------|-------------------|--|

| Parameter                    | Symbol         | Min. | Max. | Unit | Test <sup>7</sup> |  |

| VDDA power-on<br>rising edge | Vpor_vdda      | 1.35 | 1.6  | V    | Т                 |  |

| VDDA power-on<br>hysteresis  | Vpor_hyst_vdda | 75   |      | mV   | Т                 |  |

| VDDD power-on<br>rising edge | Vpor_vddd      | 2.7  | 1.08 | V    | Q                 |  |

| VDDD power-on<br>hysteresis  | Vpor_hyst_vddd | 200  |      | mV   | Q                 |  |

#### 3.3. Power modes

The BMP388 offers three power modes: sleep mode, forced mode and normal mode. These can be selected using the mode[1:0] bits in control register "*pwr\_ctrl*".

| Table 5: mode settings |             |  |  |  |

|------------------------|-------------|--|--|--|

| mode[1:0] Mode         |             |  |  |  |

| 00                     | Sleep mode  |  |  |  |

| 01 and 10              | Forced mode |  |  |  |

| 11                     | Normal mode |  |  |  |

#### 3.3.1. Sleep mode

Sleep mode is set by default after power on reset. In sleep mode, no measurements are performed and power consumption (I<sub>DDSL</sub>) is at a minimum. All registers are accessible; Chip-ID and compensation coefficients can be read.

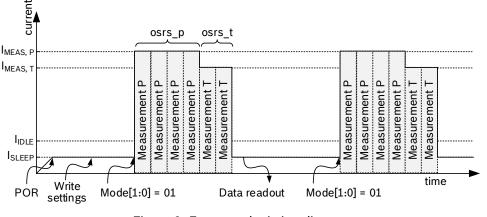

#### 3.3.2. Forced mode

In forced mode, a single measurement is performed according to selected measurement and filter options. When the measurement is finished, the sensor returns to sleep mode and the measurement results can be obtained from the data registers. For a next measurement, forced mode needs to be selected again. Forced mode is recommended for applications which require low sampling rate or host-based synchronization.

<sup>&</sup>lt;sup>7</sup> T: directly or indirectly tested at 100% at room temperature, Q: tested at the initial qualification and if necessary

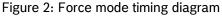

#### 3.3.3. Normal mode

Normal mode continuously cycles between an (active) measurement period and an (inactive) standby period. The measurement rate is set in the *odr\_sel* register (see 4.3.18), where various prescaler for sample frequencies  $f_{sampling}=200$ Hz can be selected. The sampling period  $\tau$  calculated by

$$\tau_{sampling} = prescaler/f_{sampling}$$

.

After setting the mode, measurement and filter options, the last measurement results can be obtained from the data registers without the need of further write accesses. Normal mode is recommended when using the IIR filter, and useful for applications in which short-term disturbances (e.g. blowing into the sensor) should be filtered.

Figure 3: Normal mode timing diagram

#### 3.3.4. Mode transition diagram

The supported mode transitions are displayed below. If the device is currently performing a measurement, execution of mode switching commands is delayed until the end of the currently running measurement period. Further mode change commands are ignored until the last mode change command is executed. Also, mode change commands that are not legal are ignored.

Figure 4: Mode transition diagram

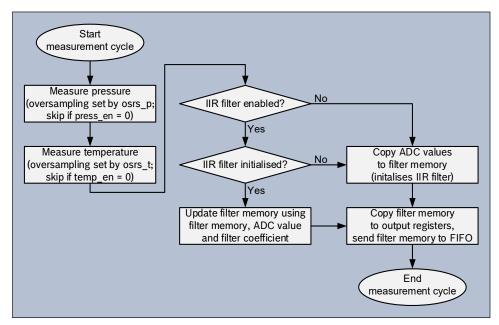

#### 3.4. Measurement flow

The BMP388 measurement period consists of a temperature and pressure measurement with selectable oversampling. After the measurement period, the data are passed through an optional IIR filter, which removes short-term fluctuations in pressure (e.g. caused by slamming a door). The flow is depicted in the diagram below.

Figure 5: BMP388 measurement cycle

The individual blocks of the diagram above will be detailed in the following subsections.

#### **3.4.1. Pressure measurement**

Pressure measurement can be enabled or skipped. Skipping the measurement could be useful if BMP388 is used as temperature sensor. When enabled, several oversampling options exist. Each oversampling step reduces noise and increases the output resolution by one bit, which is stored in the XLSB data register.

Enabling the measurement is selected by press\_en bit in "*PW\_CTRL[0]*" register (see 4.3.16). The oversampling setting *osr\_p* can be configured in "*OSR[2:0]*" register (see 4.3.17).

| Table 6: osr_p settings <sup>8</sup> |       |                          |                                |                                            |  |

|--------------------------------------|-------|--------------------------|--------------------------------|--------------------------------------------|--|

| Oversampling setting                 | osr_p | Pressure<br>oversampling | Typical pressure<br>resolution | Recommended<br>temperature<br>oversampling |  |

| Ultra low power                      | 000   | ×1                       | 16 bit / 2.64 Pa               | ×1                                         |  |

| Low power                            | 001   | ×2                       | 17 bit / 1.32 Pa               | ×1                                         |  |

| Standard resolution                  | 010   | ×4                       | 18 bit / 0.66 Pa               | ×1                                         |  |

| High resolution                      | 011   | ×8                       | 19 bit / 0.33 Pa               | ×1                                         |  |

| Ultra high resolution                | 100   | ×16                      | 20 bit / 0.17 Pa               | ×2                                         |  |

| Highest resolution                   | 101   | ×32                      | 21 bit / 0.085 Pa              | ×2                                         |  |

#### 3.4.2. Temperature measurement

Temperature measurement can be enabled or skipped. Skipping the measurement could be useful to measure pressure extremely rapidly. When enabled, several oversampling options exist. Each oversampling step reduces noise and increases the output resolution by one bit, which is stored in the XLSB data register. Noise and increases the output resolution by one bit, which is stored in the XLSB data register.

Enabling the measurement is selected by temp\_en bit in "*PW\_CTRL[1]*" register (see 4.3.16). The oversampling setting *osr\_t* can be configured in "*OSR[5:3]*" register (see 4.3.17).

| Table 7: <i>osrs_t</i> settings |                             |                                   |  |  |  |

|---------------------------------|-----------------------------|-----------------------------------|--|--|--|

| osr_t                           | Temperature<br>oversampling | Typical temperature<br>resolution |  |  |  |

| 000                             | ×1                          | 16 bit / 0.0050 °C                |  |  |  |

| 001                             | ×2                          | 17 bit / 0.0025 °C                |  |  |  |

| 010                             | ×4                          | 18 bit / 0.0012 °C                |  |  |  |

| 011                             | ×8                          | 19 bit / 0.0006 °C                |  |  |  |

| 100                             | ×16                         | 20 bit / 0.0003 °C                |  |  |  |

| 101                             | ×32                         | 21 bit / 0.00015 °C               |  |  |  |

It is recommended to base the value of *osr\_t* on the selected value of *osrs\_p* as per Table 5. Temperature oversampling above ×2 is possible, but will not significantly improve the accuracy of the pressure output any further. The reason for this is that the noise of the compensated pressure value depends more on the raw pressure than on the raw temperature noise. Following the recommended setting will result in an optimal noise-to-power ratio.

<sup>&</sup>lt;sup>8</sup> Resolution of 24 bit e.g. OSR=32x and IIR>=b011

Modifications reserved |Data subject to change without notice | Printed in Germany

#### 3.4.3. IIR filter

The environmental pressure is subject to many short-term changes, caused e.g. by slamming of a door or window, or wind blowing into the sensor. To suppress these disturbances in the output data without causing additional interface traffic and processor work load, the BMP388 features an internal IIR filter. It effectively reduces the bandwidth of the output signals<sup>9</sup>. The output of a next measurement step is filter using the following formula:

$data_{filtered} = \frac{data_{filtered\_old} * filter\_coefficient + data_{ADC}}{filter\_coefficient + 1}$

where data\_filtered\_old is the data coming from the previous acquisition, and data\_ADC is the data coming from the ADC before IIR filtering.

The IIR filter can be configured using setting *iir\_filter* in "CONFIG" register (see 4.3.20).

When writing to the register *filter*, the filter is reset. The next value will pass through the filter and be the initial memory value for the filter. IIR filter is reset if the temperature or pressure measurement is disabled (*temp\_en* or *press\_en* registers changed from '1' to '0') or when a transition from sleep mode to normal mode occurs. After enabling of pressure or temperature measurement, the filtering will start, thus the next incoming value will pass unfiltered and be the initial value of the IIR filter.

The step response (e.g. response to in sudden change in height) of different filter settings is displayed in Figure 6.

Figure 6: Step response at different IIR filter settings

#### 3.4.4. Oversampling

Noise depends on the oversampling and filter settings selected. The stated values were determined in a controlled pressure environment and are based on the average standard deviation of 32 consecutive measurement points taken at highest sampling rate (for details please refer to Table 21). This is required to exclude long term drifts from the noise measurement.

<sup>&</sup>lt;sup>9</sup> Since most pressure sensors do not sample continuously, filtering can suffer from signals with a frequency higher than the sampling rate of the sensor. E.g. environmental fluctuations caused by windows being opened and closed might have a frequency <5 Hz. Consequently, a sampling rate of ODR = 10 Hz is sufficient to obey the Nyquist theorem.

| Table 8: Noise in pressure |         |       |         |          |         |      |     |      |

|----------------------------|---------|-------|---------|----------|---------|------|-----|------|

|                            | Typical | RMS n | oise in | press    | ure [Pa | ]    |     |      |

| Oversampling               |         |       | 111     | R filter | coeffic | ient |     |      |

| setting                    | off     | 1     | 3       | 7        | 15      | 31   | 63  | 127  |

| Ultra low power            | 6.6     | 3.8   | 2.5     | 1.7      | 1.2     | 0.8  | 0.6 | 0.4  |

| Low power                  | 4.3     | 2.5   | 1.6     | 1.1      | 0.8     | 0.5  | 0.4 | 0.3  |

| Standard resolution        | 3.2     | 1.8   | 1.2     | 0.8      | 0.6     | 0.4  | 0.3 | 0.2  |

| High resolution            | 2.3     | 1.3   | 0.9     | 0.6      | 0.4     | 0.3  | 0.2 | 0.1  |

| Ultra high resolution      | 1.6     | 0.9   | 0.6     | 0.4      | 0.2     | 0.2  | 0.1 | 0.1  |

| Highest resolution         | 1.2     | 0.7   | 0.4     | 0.3      | 0.3     | 0.1  | 0.1 | <0.1 |

| Table 9: Noise in temperature         |                |  |  |  |  |

|---------------------------------------|----------------|--|--|--|--|

| Typical RMS noise in temperature [°C] |                |  |  |  |  |

| Temperature oversampling              | IIR filter off |  |  |  |  |

| Ultra low power                       | 0.005          |  |  |  |  |

| Low power                             | 0.005          |  |  |  |  |

| Standard resolution                   | 0.005          |  |  |  |  |

| High resolution                       | 0.005          |  |  |  |  |

| Ultra high resolution                 | 0.004          |  |  |  |  |

| Highest resolution                    | 0.003          |  |  |  |  |

#### 3.5. Filter selection

In order to select optimal settings, the following use cases are suggested:

Table 10: Recommended filter settings based on use cases

| Use case                                              | Mode   | Over-<br>sampling<br>setting | osrs_p | osrs_t | IIR filter<br>coeff.<br>(see<br>4.3.20) | ι <sub>DD</sub> [μΑ]<br>(see 3.8) | ODR [Hz]<br>(see 3.4.1) | RMS Noise<br>[cm]<br>(see 3.4.4) |

|-------------------------------------------------------|--------|------------------------------|--------|--------|-----------------------------------------|-----------------------------------|-------------------------|----------------------------------|

| handheld<br>device low-<br>power<br>(e.g.<br>Android) | Normal | High<br>resolution           | x8     | ×1     | 2                                       | 145                               | 12.5                    | 11                               |

| handheld<br>device<br>dynamic<br>(e.g.<br>Android)    | Normal | Standard resolution          | ×4     | ×1     | 4                                       | 310                               | 50                      | 10                               |

| Weather<br>monitoring<br>(lowest<br>power),           | Forced | Ultra low<br>power           | ×1     | ×1     | Off                                     | 4                                 | 1/60                    | 55                               |

| Drop<br>detection                                     | Normal | Low power                    | ×2     | ×1     | Off                                     | 358                               | 100                     | 36                               |

| Indoor<br>navigation                                  | Normal | Ultra high resolution        | ×16    | ×2     | 4                                       | 560                               | 25                      | 5                                |

| Drone                                                 | Normal | Standard<br>Resolution       | x8     | x1     | 2                                       | 570                               | 50                      | 11                               |

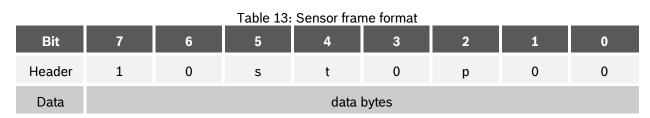

#### **3.6.** FIFO Description

The BMP388 contains a 512 Bytes FIFO (first-in-first-out) data buffer. To enable data collecting in the FIFO, *fifo\_mode* is set at '1' and data to be collected are defined through *fifo\_press\_en* and *fifo\_temp\_en*. The FIFO mode is disabled, when no writing is defined which according to the following two cases:

- fifo\_mode='0'

- *fifo\_mode='1'* and *fifo\_press\_en='0'* and *fifo\_temp\_en='0'*

If the FIFO is disabled when FIFO byte count is greater than 0, no new frame is written to the FIFO, but FIFO is operational:

- Frames already written in the FIFO remain stored and can be read out

- FIFO interrupts and their corresponding statuses are still evaluated

- after all bytes are read out, Sensortime (if enabled) and Empty frames are generated

- FIFO can be flushed

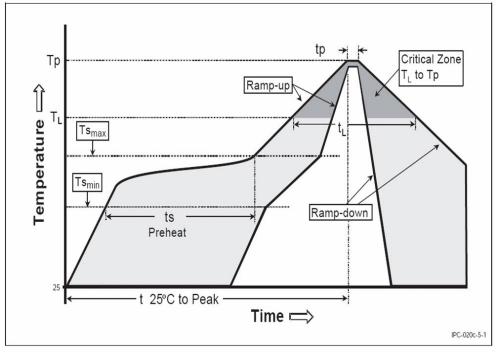

#### 3.6.1. FIFO input data