# PI7C9X7954 PCI Express<sup>®</sup> Quad UART

Datasheet Revision 2 October 2017

A Product Line of Diodes Incorporated

1545 Barber Lane Milpitas, CA 95035 Telephone: 408-232-9100 FAX: 408-435-1100 Internet: http://www.diodes.com

#### IMPORTANT NOTICE

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes Incorporated.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

A. Life support devices or systems are devices or systems which:

1. are intended to implant into the body, or

2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the

failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2016, Diodes Incorporated

www.diodes.com

### **REVISION HISTORY**

| Date       | Revision Nun | nber Description                                                                                     |

|------------|--------------|------------------------------------------------------------------------------------------------------|

| 10/31/07   | 0.1          | Preliminary Datasheet                                                                                |

|            |              | Fixed the diagrams                                                                                   |

|            |              | Corrected Section 4.2 Pin Description (RREF, GPIO[7])                                                |

|            |              | Updated Section 6 PCI Express Registers(6.2.42 [3], 6.2.36 UART Driver Setting, 6.2.41 GPIO          |

|            |              | Control Register )                                                                                   |

|            |              | Revised Section 7.1 Registers in I/O Mode                                                            |

|            |              | Updated Section 11 Ordering Info                                                                     |

| 12/20/2007 | 0.2          | Updated Section 4 Pin Assignment (description for shared pins added, MODE_SEL changed to             |

|            |              | DRIVER_SEL)                                                                                          |

|            |              | Updated Section 6 PCI Express Register Description                                                   |

|            |              | Updated Section 7 UART Register Description                                                          |

| 0.1/20/00  |              | Updated Section 8 EEPROM Interface                                                                   |

| 04/22/08   | 0.3          | Updated Section 1 Features (Clock prescaler, Data frame size, Power Dissipation)                     |

|            |              | Corrected Section 3 General Description                                                              |

|            |              | Updated Section 4 Pin Assignment (description for shared pins added, MODE_SEL changed to             |

|            |              | DRIVER_SEL, VAUX changed to VDDCAUX, WAKEUP_L, CLKINP, CLKINN)                                       |

|            |              | Added 5.2.4 Mode Selection, 5.2.5 450/550 Mode, 5.2.6 Enhanced 550 Mode, 5.2.7 Enhanced 950          |

|            |              | Mode<br>Corrected 5.2.8 Transmit and Receive FIFOs, 5.2.9 Automated Flow Control                     |

|            |              | Modified 5.2.12 Baud Rate Generation                                                                 |

|            |              | Updated Section 6 PCI Express Register Description (6.2.36, 6.2.42)                                  |

|            |              | Updated Format (6.2.20, 6.2.36, 6.2.54, 6.2.55, 6.2.57)                                              |

|            |              | Updated Section 7 UART Register Description (7.1.6 LCR Bit[5:0], 7.1.7 MCR Bit[5] and Bit[7],        |

|            |              | 7.1.9 MSR Bit[3:0], 7.2.6 LCR Bit[5:0], 7.2.7 MCR Bit[5] and Bit[7], 7.2.9 MSR Bit[3:0], 7.2.11      |

|            |              | DLL, 7.2.12 DLH, 7.2.13 EFR, 7.2.18 ACR Bit[7:2], 7.2.23 CPRM)                                       |

|            |              | Updated Chapter 8.3 EEPROM Space Address Map And Description (00h, 0Ah, 40h)                         |

|            |              | Added Section 9 Electrical Specification                                                             |

|            |              | Corrected Section 9.2 DC Specification                                                               |

|            |              | Updated Section 9.3 AC Specification                                                                 |

|            |              | Added Section 10 Clock Scheme                                                                        |

| 08/13/08   | 0.4          | Updated Section 1 Features (added Industrial Temperature Range)                                      |

|            |              | Updated 9.1 Absolute Maximum Ratings: Ambient Temperature with power applied                         |

| 11/25/08   | 1.0          | Updated 7.1.13 Sample Clock Register and 7.2.27 Sample Clock Register                                |

|            |              | Updated Chapter 12 Ordering Information                                                              |

|            |              | Removed "Preliminary" and "Confidential" references                                                  |

| 03/06/09   | 1.1          | Corrected Figure 3-1 PI7C9X7954 Block Diagram (SYN_UART_CLK removed)                                 |

|            |              | Corrected Section 4.2.1 UART Interface (SYNCLK_IN_EN and SYN_UART_CLK removed)                       |

|            |              | Corrected Figure 5-2 Internal Loopback in PI7C7954                                                   |

|            |              | Corrected Figure 5-3 Crystal Oscillator as the Clock Source (14.7456 MHz)                            |

|            |              | Corrected Section 7.1.7 Modem Control Register (Bit[5]), 7.1.10 Special Function Register (Bit[4]),  |

|            |              | 7.2.7 Modem Control Register (Bit[5]), 7.2.10 Special Function Register (Bit[4]), 7.2.29 Receive     |

|            |              | FIFO Data Registers, 7.2.30 Transmit FIFO Data Register, 7.2.31                                      |

| 04/21/09   | 1.2          | Updated Section 4 Pin Description                                                                    |

| 09/24/09   | 1.3          | Updated Figure 5-3 Crystal Oscillator as the Clock Source                                            |

|            |              | Updated Section 6.2.24 Message Signaled Interrupt (MSI) Next Item Pointer 8Ch                        |

|            |              | Added Section 6.2.25 Message Address Register – Offset 90h                                           |

|            |              | Added Section 6.2.26 Message Upper Address Register – Offset 94h                                     |

| 06/04/14   | 1.4          | Added Section 6.2.27 Message Data Register – Offset 98h                                              |

| 06/04/14   | 1.4          | Updated Section 4.1 Pin List (SR_DO and SR_DI)                                                       |

|            |              | Updated Section 4.2.5 EEPROM Interface (SR_DO and SR_DI)<br>Created for IC Revision B                |

|            |              | Updated Section 12 Ordering Information                                                              |

|            |              |                                                                                                      |

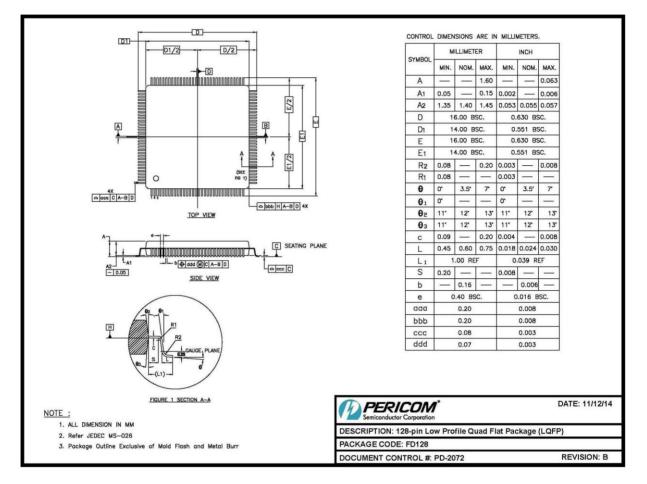

| 01/09/15   | 1.5          | Added Section 6.2.25 Message Control Register – OFFSET 8Ch<br>Updated Section 11 Package Information |

| 05/11/15   | 1.5          | Updated Table 5-2 Baud Rate Generator Setting                                                        |

| 03/11/13   | 1.0          | 1 6                                                                                                  |

| 00/20/17   | 1.7          | Updated Section 7.2.23 Clock Prescale Register – Offset 14h                                          |

| 08/30/17   | 1.7          | Updated Section 4.1.PIN LIST OF 128-PIN LQFP                                                         |

|            |              | Updated Section 4.2.1 UART Interface                                                                 |

|            |              | Updated Table 9.1 Absolute Maximum Ratings                                                           |

|            |              | Updated Table 9.2 DC Electrical Characteristics                                                      |

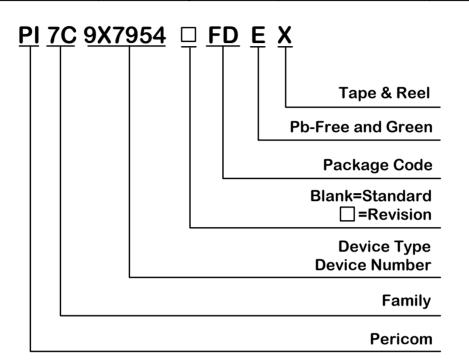

| 10/06/117  | -            | Updated Section 12 Ordering Information                                                              |

| 10/06/17   | 2            | Revision numbering system changed to whole number                                                    |

## **Table of Contents**

| 1. | FEATUI             | RES                                                                          | 9    |

|----|--------------------|------------------------------------------------------------------------------|------|

| 2. | APPLIC             | ATIONS                                                                       | 9    |

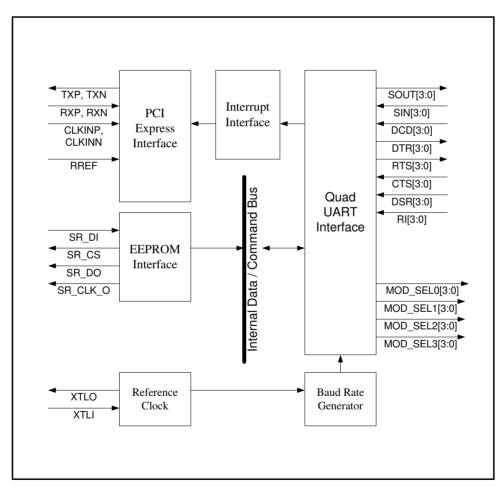

| 3. | GENER              | AL DESCRIPTION                                                               | .10  |

| 4. | PIN ASS            | IGNMENT                                                                      | .11  |

| 4  |                    | LIST OF 128-PIN LQFP                                                         |      |

|    |                    | DESCRIPTION                                                                  |      |

|    | 4.2.1.             | UART INTERFACE                                                               |      |

|    | 4.2.2.             | PCI EXPRESS INTERFACE                                                        |      |

|    | 4.2.3.             | SYSTEM INTERFACE                                                             |      |

|    | 4.2.4.             | TEST SIGNALS                                                                 |      |

|    | 4.2.5.             | EEPROM INTERFACE                                                             |      |

|    | 4.2.6.             | POWER PINS                                                                   |      |

| 5. | FUNCT              | IONAL DESCRIPTION                                                            | .16  |

| 5  | .1. COI            | NFIGURATION SPACE                                                            | .16  |

|    | 5.1.1.             | PCI Express Configuration Space                                              |      |

|    | 5.1.2.             | UART Configuration Space                                                     |      |

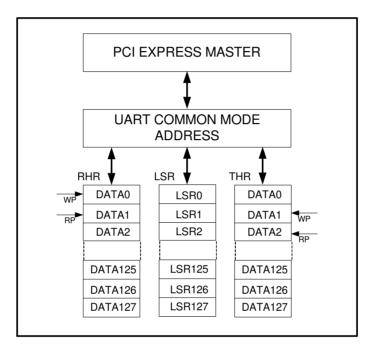

| 5  | 5.2. DEV           | VICE OPERATION                                                               |      |

|    | 5.2.1.             | Configuration Access                                                         | .17  |

|    | 5.2.2.             | I/O Reads/Writes                                                             |      |

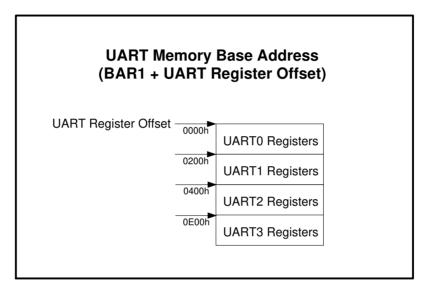

|    | 5.2.3.             | Memory Reads/Writes                                                          | .17  |

|    | 5.2.4.             | Mode Selection                                                               |      |

|    | 5.2.5.             | 450/550 Mode                                                                 | .18  |

|    | 5.2.6.             | Enhanced 550 Mode                                                            | .18  |

|    | 5.2.7.             | Enhanced 950 Mode                                                            |      |

|    | 5.2.8.             | Transmit and Receive FIFOs                                                   |      |

|    | 5.2.9.             | Automated Flow Control                                                       | 20   |

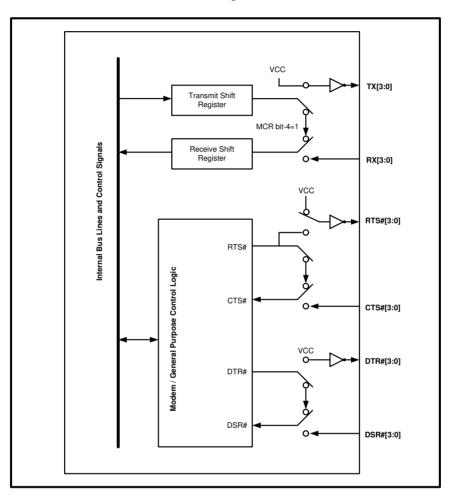

|    | 5.2.10.            | Internal Loopback                                                            |      |

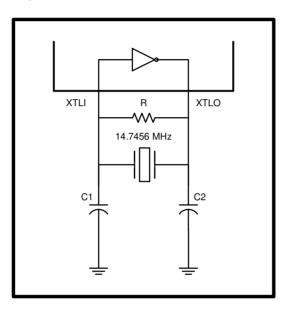

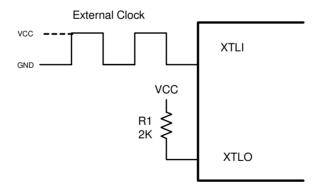

|    | 5.2.11.            | Crystal Oscillator                                                           |      |

|    | 5.2.12.            | Baud Rate Generation                                                         |      |

|    | 5.2.13.            | Power Management                                                             | .23  |

| 6. | PCI EXI            | PRESS REGISTER DESCRIPTION                                                   | .24  |

| 6  | 5.1. REC           | GISTER TYPES                                                                 | .24  |

| 6  |                    | NFIGURATION REGISTERS                                                        |      |

|    | 6.2.1.             | VENDOR ID REGISTER – OFFSET 00h                                              |      |

|    | 0.2.2.             | DEVICE ID REGISTER – OFFSET 00h                                              | . 20 |

|    | 6.2.3.             | COMMAND REGISTER – OFFSET 04h                                                |      |

|    | 6.2.4.             | STATUS REGISTER – OFFSET 04h                                                 |      |

|    | 6.2.5.             | REVISION ID REGISTER – OFFSET 08h                                            |      |

|    | 6.2.6.             | CLASS CODE REGISTER – OFFSET 08h                                             |      |

|    | 6.2.7.             | CACHE LINE REGISTER – OFFSET OCh                                             |      |

|    | 6.2.8.             | MASTER LATENCY TIMER REGISTER – OFFSET 0Ch                                   |      |

|    | 6.2.9.             | HEADER TYPE REGISTER – OFFSET OCh                                            |      |

|    | 6.2.10.            | BASE ADDRESS REGISTER 0 – OFFSET 10h                                         |      |

|    | 6.2.11.            | BASE ADDRESS REGISTER 1 – OFFSET 14h                                         |      |

|    | 6.2.12.            | SUBSYSTEM VENDOR REGISTER – OFFSET 2Ch<br>SUBSYSTEM ID REGISTER – OFFSET 2Ch |      |

|    | 6.2.13.<br>6.2.14. | CAPABILITIES POINTER REGISTER – OFFSET 2Ch                                   |      |

|    | 0.2.14.            | CAIADILITIES I UIIVIEK KEUISTEK - UTTSEI J41                                 | 20   |

| 6.2.15.                           | INTERRUPT LINE REGISTER – OFFSET 3Ch                                                                   | 28   |

|-----------------------------------|--------------------------------------------------------------------------------------------------------|------|

| 6.2.16.                           | INTERRUPT PIN REGISTER – OFFSET 3Ch                                                                    |      |

| 6.2.17.                           | POWER MANAGEMENT CAPABILITY ID REGISTER – OFFSET 80h                                                   |      |

| 6.2.18.                           | NEXT ITEM POINTER REGISTER – OFFSET 80h                                                                |      |

| 6.2.19.                           | POWER MANAGEMENT CAPABILITIES REGISTER – OFFSET 80h                                                    |      |

| 6.2.20.                           | POWER MANAGEMENT DATA REGISTER – OFFSET 84h                                                            | 29   |

| 6.2.21.                           | PPB SUPPORT EXTENSIONS – OFFSET 84h                                                                    |      |

| 6.2.22.                           | PM DATA REGISTER – OFFSET 84h                                                                          |      |

| 6.2.23.                           | MESSAGE SIGNALED INTERRUPTS (MSI) Capability ID Register 8Ch                                           |      |

| 6.2.24.                           | MESSAGE SIGNALED INTERRUPTS (MSI) NEXT ITEM POINTER 8Ch                                                |      |

| 6.2.25.                           | MESSAGE CONTROL REGISTER – OFFSET 8Ch                                                                  |      |

| 6.2.26.                           | MESSAGE ADDRESS REGISTER – OFFSET 90h                                                                  |      |

| 6.2.27.                           | MESSAGE UPPER ADDRESS REGISTER – OFFSET 94h                                                            |      |

| 6.2.28.                           | MESSAGE DATA REGISTER – OFFSET 98h                                                                     |      |

| <i>6.2.29</i> .                   | VPD CAPABILITY ID REGISTER – OFFSET 9Ch                                                                |      |

| 6.2.30.                           | NEXT ITEM POINTER REGISTER – OFFSET 9Ch                                                                |      |

| 6.2.31.                           | VPD REGISTER – OFFSET 9Ch                                                                              |      |

| 6.2.32.                           | VPD DATA REGISTER – OFFSET A0h                                                                         |      |

| 6.2.33.                           | VENDOR SPECIFIC CAPABILITY ID REGISTER – OFFSET A4h                                                    |      |

| 6.2 <i>.</i> 33.                  | NEXT ITEM POINTER REGISTER – OFFSET A4h                                                                |      |

| 6.2.3 <i>4</i> .                  | LENGTH REGISTER – OFFSET A4h                                                                           |      |

| 6.2.3 <i>6</i> .                  | XPIP CSR0 – OFFSET A8h (Test Purpose Only)                                                             |      |

| 6.2.30.                           | XPIP CSR1 – OFFSET ACh (Test Purpose Only)                                                             |      |

| 6.2. <i>3</i> 7.                  | REPLAY TIME-OUT COUNTER – OFFSET B0h                                                                   |      |

| 6.2.38.<br>6.2.39.                | ACKNOWLEDGE LATENCY TIMER – OFFSET BON                                                                 |      |

| 6.2. <i>39</i> .                  | UART DRIVER SETTING – OFFSET B4h                                                                       |      |

| <i>6.2.40</i> .                   | POWER MANAGEMENT CONTROL PARAMETER – OFFSET B8h                                                        |      |

| 6.2.41.<br>6.2.42.                | DEBUG REGISTER 1 – OFFSET BCh (Test Purpose Only)                                                      |      |

| 6.2.42.<br>6.2.43.                | DEBUG REGISTER 1 – OFFSET BCh (Test Purpose Only)<br>DEBUG REGISTER 2 – OFFSET COh (Test Purpose Only) |      |

| 6.2.43.<br>6.2.44.                | DEBUG REGISTER 2 – OFFSET Con (Test Purpose Only)<br>DEBUG REGISTER 3 – OFFSET C4h (Test Purpose Only) |      |

| 6.2.44.<br>6.2.45.                | DEBUG REGISTER 5 – OFFSET C4n (Test Purpose Only)<br>DEBUG REGISTER 4 – OFFSET C8h (Test Purpose Only) |      |

| 6.2.4 <i>5</i> .                  | GPIO CONTROL REGISTER – OFFSET Con (lest Purpose Onty)                                                 |      |

| 6.2.40.<br>6.2.47.                | EEPROM CONTROL REGISTER – OFFSET Don                                                                   |      |

| 6.2.47.<br>6.2.48.                | PCI EXPRESS CAPABILITY ID REGISTER – OFFSET DCh                                                        |      |

| 0.2.48.<br>6.2.49.                | NEXT ITEM POINTER REGISTER – OFFSET E0h                                                                |      |

| 0.2.49.<br>6.2.50.                | PCI EXPRESS CAPABILITIES REGISTER – OFFSET EUN                                                         |      |

| <i>6.2.50.</i><br><i>6.2.51</i> . | DEVICE CAPABILITIES REGISTER – OFFSET E4h                                                              |      |

| 6.2.51.<br>6.2.52.                | DEVICE CAPABILITIES REGISTER – OFFSET E4h<br>DEVICE CONTROL REGISTER – OFFSET E8h                      |      |

|                                   | DEVICE CONTROL REGISTER – OFFSET E8h                                                                   |      |

| 6.2.53.<br>6.2.54.                | LINK CAPABILITIES REGISTER – OFFSET ECh                                                                |      |

| 0.2.34.<br>6.2.55.                | LINK CAPABILITIES REGISTER – OFFSET ECH                                                                |      |

| 6.2.55.<br>6.2.56.                |                                                                                                        |      |

| 0.2.30.<br>6.2.57.                | LINK STATUS REGISTER – OFFSET F0h<br>PCI EXPRESS ADVANCED ERROR REPORTING CAPABILITY ID REGISTER – OF  |      |

| 0.2.07.                           |                                                                                                        | FSEI |

| 100h                              | 38<br>CADADU TUVEDCION OFFICET 1001                                                                    | 20   |

| 6.2.58.                           | CAPABILITY VERSION – OFFSET 100h                                                                       |      |

| 6.2.59.                           | NEXT ITEM POINTER REGISTER – OFFSET 100h                                                               |      |

| 6.2.60.                           | UNCORRECTABLE ERROR STATUS REGISTER – OFFSET 104h                                                      |      |

| 6.2.61.                           | UNCORRECTABLE ERROR MASK REGISTER – OFFSET 108h                                                        |      |

| 6.2.62.                           | UNCORRECTABLE ERROR SEVERITY REGISTER – OFFSET 10Ch                                                    |      |

| 6.2.63.                           | CORRECTABLE ERROR STATUS REGISTER – OFFSET 110h                                                        |      |

| 6.2.64.                           | CORRECTABLE ERROR MASK REGISTER – OFFSET 114h                                                          |      |

| 6.2.65.                           | ADVANCE ERROR CAPABILITIES AND CONTROL REGISTER – OFFSET 118h                                          |      |

| 6.2.66.                           | HEADER LOG REGISTER – OFFSET From 11Ch to 128h                                                         |      |

| UARTI                             | REGISTER DESCRIPTION                                                                                   |      |

7.

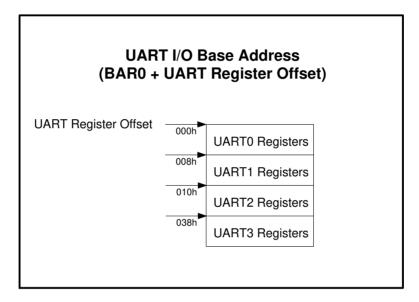

| 7.1. RE            | GISTERS IN I/O MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 7.1.1.             | RECEIVE HOLDING REGISTER – OFFSET 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 44 |

| 7.1.2.             | TRANSMIT HOLDING REGISTER – OFFSET 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7.1.3.             | INTERRUPT ENABLE REGISTER – OFFSET 01h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7.1.4.             | INTERRUPT STATUS REGISTER – OFFSET 02h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7.1.5.             | FIFO CONTROL REGISTER – OFFSET 02h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45 |

| 7.1.6.             | LINE CONTROL REGISTER – OFFSET 03h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 46 |

| 7.1.7.             | MODEM CONTROL REGISTER – OFFSET 04h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46 |

| 7.1.8.             | LINE STATUS REGISTER – OFFSET 05h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |

| 7.1.9.             | MODEM STATUS REGISTER – OFFSET 06h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 7.1.10.            | SPECIAL FUNCTION REGISTER – OFFSET 07h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7.1.11.            | DIVISOR LATCH LOW REGISTER – OFFSET 00h, LCR[7] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

| 7.1.12.            | DIVISOR LATCH HIGH REGISTER – OFFSET 01h, LCR[7] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

| 7.1.13.            | SAMPLE CLOCK REGISTER – OFFSET 02h, LCR[7] = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

|                    | GISTERS IN MEMORY-MAPPING MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |

| 7.2.1.             | RECEIVE HOLDING REGISTER – OFFSET 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

| 7.2.2.             | TRANSMIT HOLDING REGISTER – OFFSET 00h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7.2.3.             | INTERRUPT ENABLE REGISTER – OFFSET 01h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7.2.4.             | INTERRUPT STATUS REGISTER – OFFSET 02h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |

| 7.2.5.             | FIFO CONTROL REGISTER – OFFSET 02h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

| 7.2.6.             | LINE CONTROL REGISTER – OFFSET 03h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

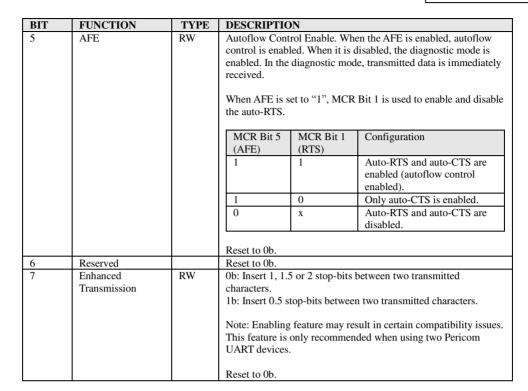

| 7.2.7.             | MODEM CONTROL REGISTER – OFFSET 04h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |