# 18-Cell Battery Stack Monitor with Daisy Chain Interface

## **FEATURES**

- Measures Up to 18 Battery Cells in Series

- 2.2mV Maximum Total Measurement Error

- Stackable Architecture for High Voltage Systems

- Built-In isoSPI™ Interface

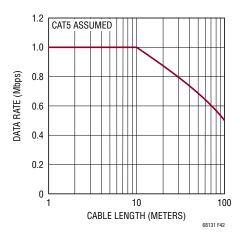

- 1Mb Isolated Serial Communications

- Uses a Single Twisted Pair, Up to 100 Meters

- Low EMI Susceptibility and Emissions

- Bidirectional for Broken Wire Protection

- 290µs to Measure All Cells in a System

- Synchronized Voltage and Current Measurement

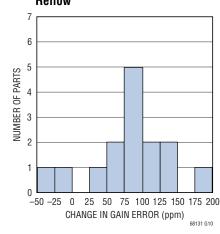

- 16-Bit Delta-Sigma ADC with Programmable Noise Filter

- Engineered for ISO 26262-Compliant Systems

- Passive Cell Balancing Up to 200mA (Max) with Programmable Pulse-Width Modulation

- 9 General Purpose Digital I/O or Analog Inputs

- Temperature or Other Sensor Inputs

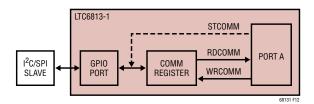

- Configurable as an I<sup>2</sup>C or SPI Master

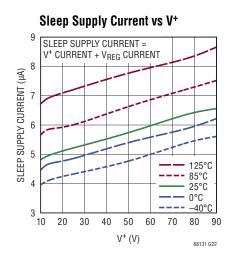

- 6µA Sleep Mode Supply Current

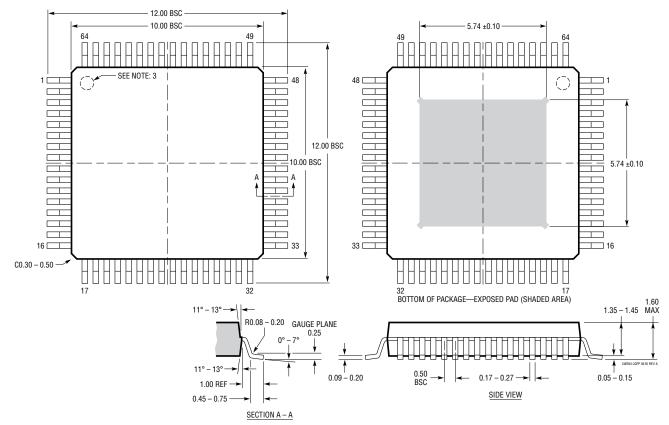

- 64-Lead eLQFP Package

- AEC-Q100 Qualified for Automotive Applications

## **APPLICATIONS**

- Electric and Hybrid Electric Vehicles

- Backup Battery Systems

- Grid Energy Storage

- High Power Portable Equipment

## DESCRIPTION

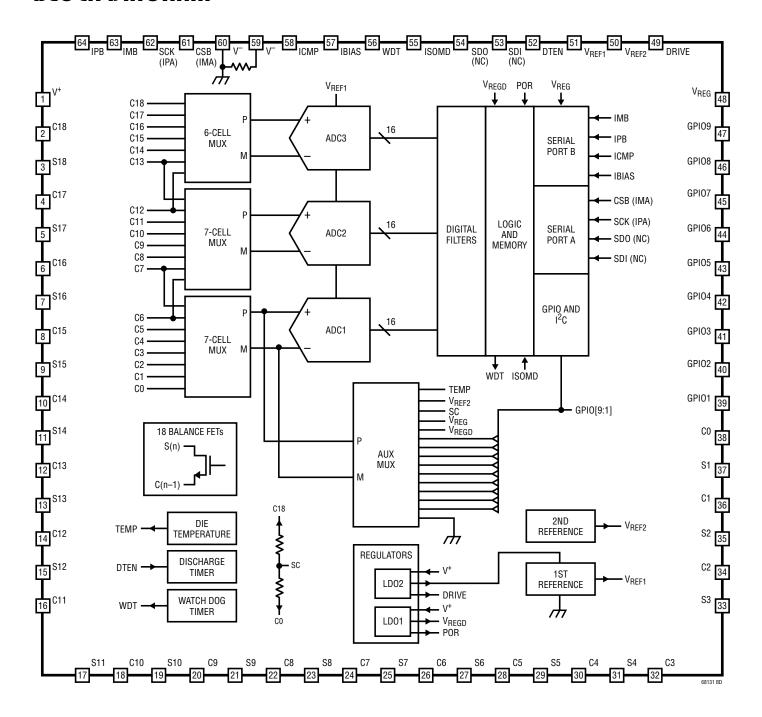

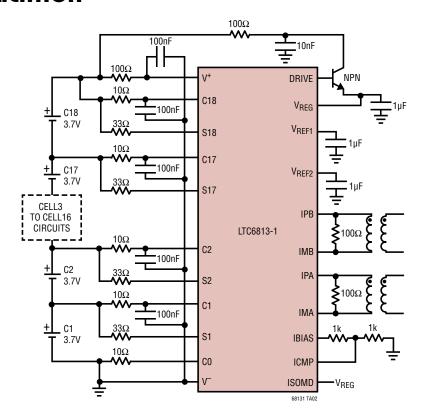

The LTC®6813-1 is a multicell battery stack monitor that measures up to 18 series connected battery cells with a total measurement error of less than 2.2mV. The cell measurement range of 0V to 5V makes the LTC6813-1 suitable for most battery chemistries. All 18 cells can be measured in 290µs, and lower data acquisition rates can be selected for high noise reduction.

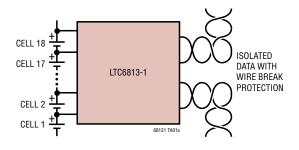

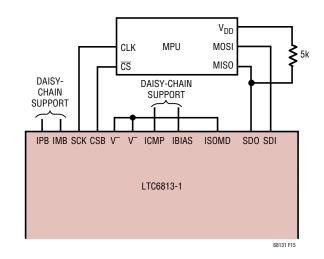

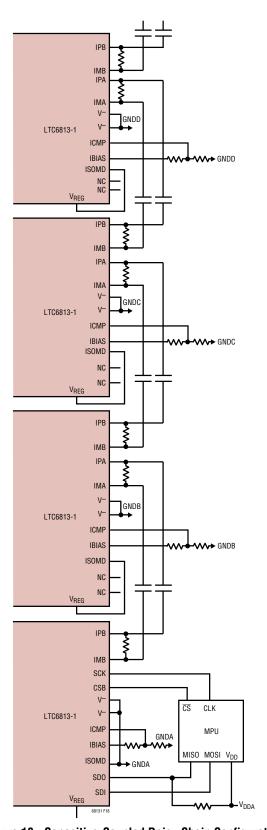

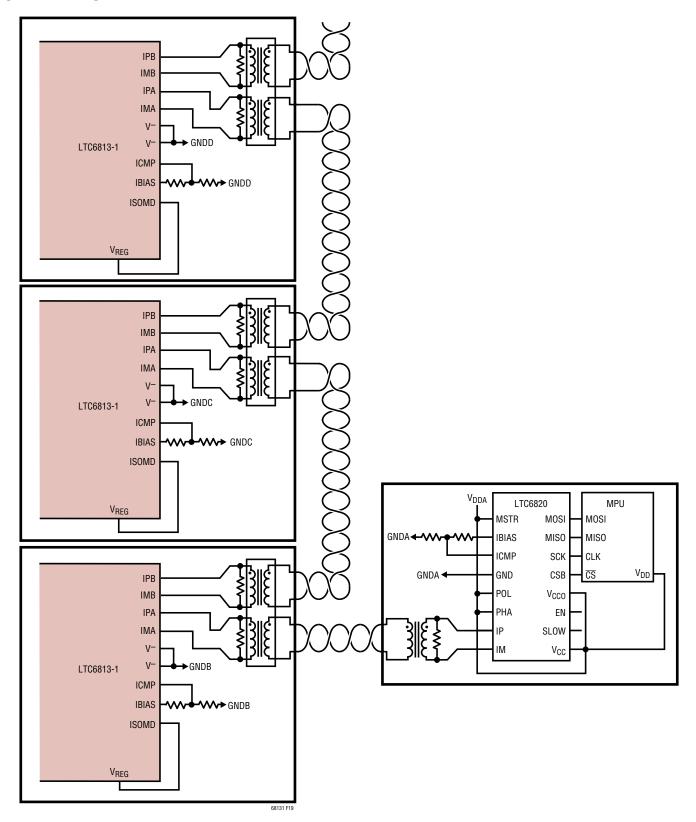

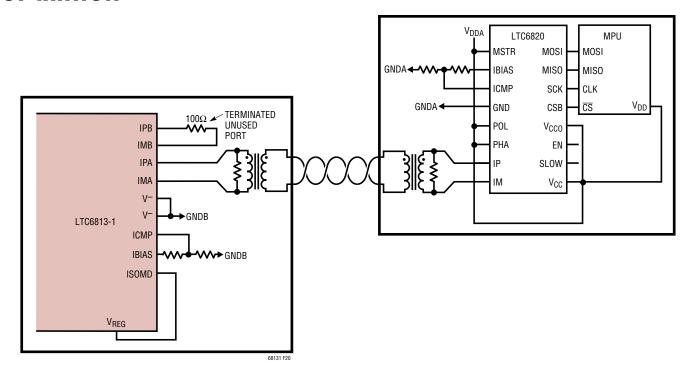

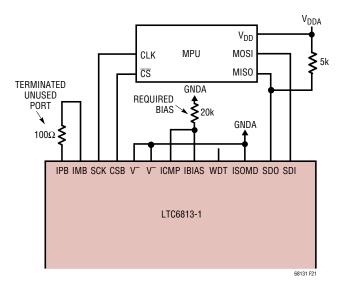

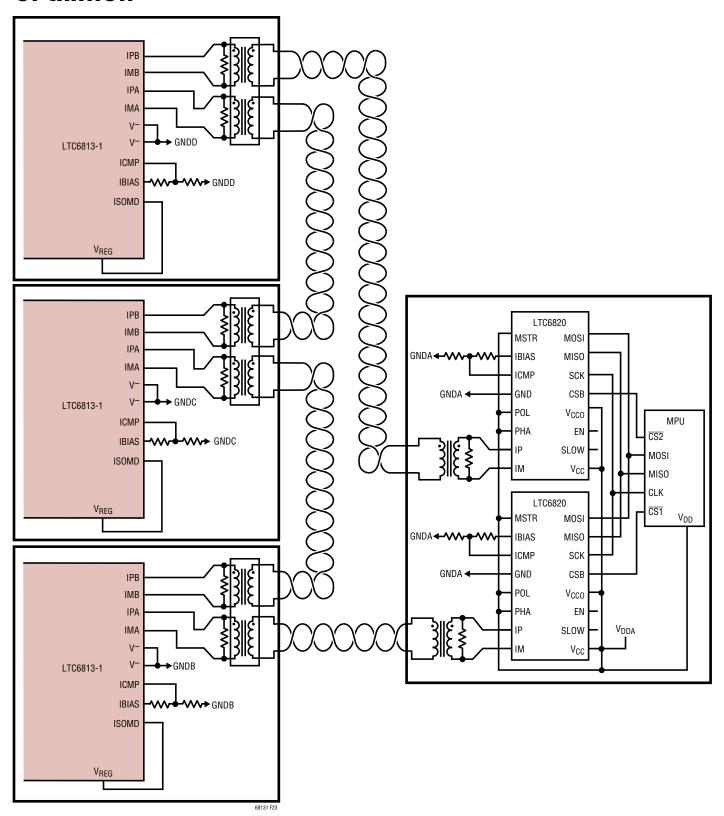

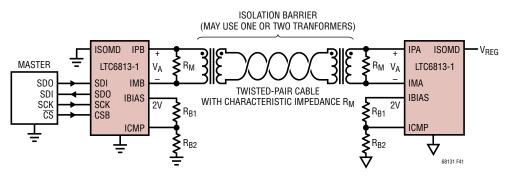

Multiple LTC6813-1 devices can be connected in series, permitting simultaneous cell monitoring of long, high voltage battery strings. Each LTC6813-1 has an isoSPI interface for high speed, RF immune, long distance communications. Multiple devices are connected in a daisy chain with one host processor connection for all devices. This daisy chain can be operated bidirectionally, ensuring communication integrity, even in the event of a fault along the communication path.

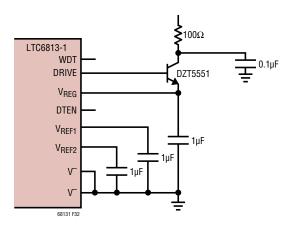

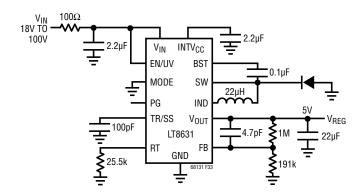

The LTC6813-1 can be powered directly from the battery stack or from an isolated supply. The LTC6813-1 includes passive balancing for each cell, with individual PWM duty cycle control for each cell. Other features include an onboard 5V regulator, nine general purpose I/O lines and a sleep mode, where current consumption is reduced to 6uA.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. patents, including 8908779, 9182428, 9270133.

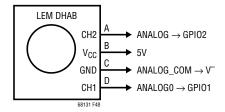

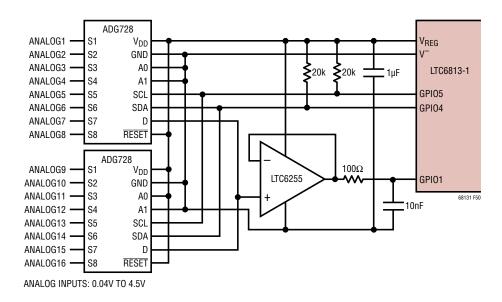

## TYPICAL APPLICATION

#### 18-Cell Monitor and Balance IC

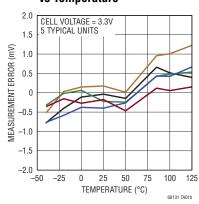

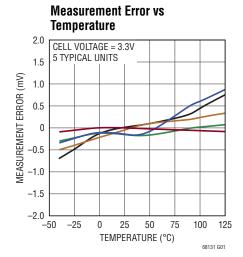

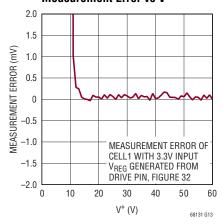

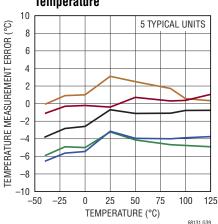

## Cell 18 Measurement Error vs Temperature

Rev. B

1

## LTC6813-1

## TABLE OF CONTENTS

| Features                                        | 1    |

|-------------------------------------------------|------|

| Applications                                    | 1    |

| Typical Application                             | 1    |

| Description                                     | 1    |

| Absolute Maximum Ratings                        | 3    |

| Order Information                               | 3    |

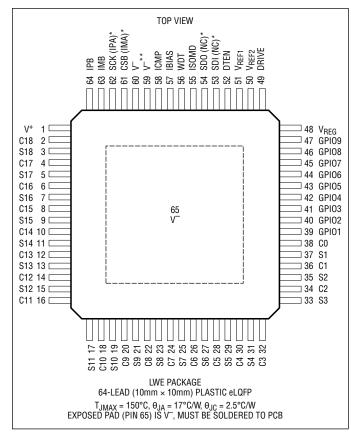

| Pin Configuration                               | 3    |

| Electrical Characteristics                      | 4    |

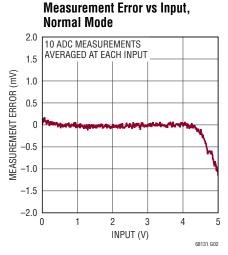

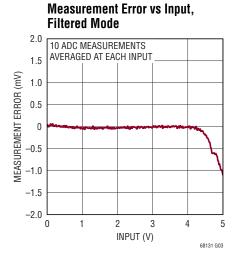

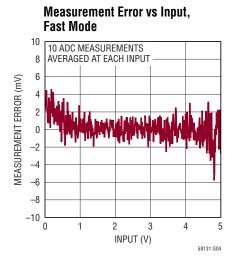

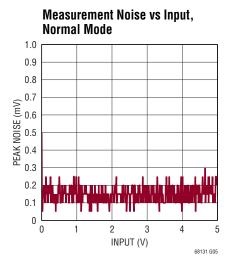

| Typical Performance Characteristics             | 9    |

| Pin Functions                                   | . 15 |

| Block Diagram                                   | . 16 |

| Improvements from the LTC6811-1                 |      |

| Operation                                       |      |

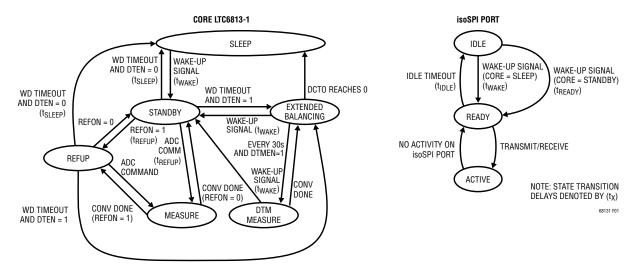

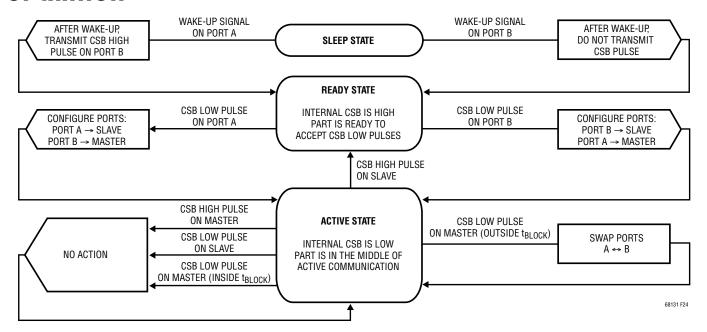

| State Diagram                                   | . 18 |

| Core LTC6813-1 State Descriptions               | . 18 |

| isoSPI State Descriptions                       | . 19 |

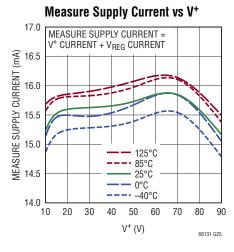

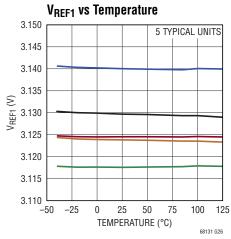

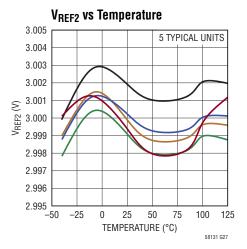

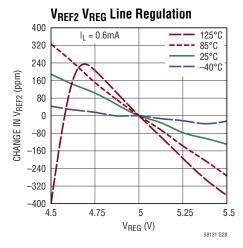

| Power Consumption                               | . 19 |

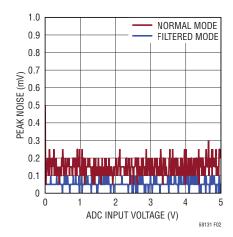

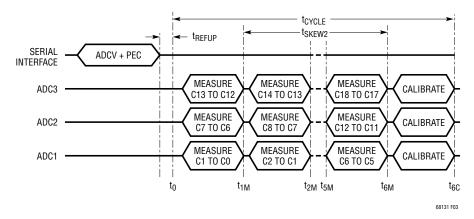

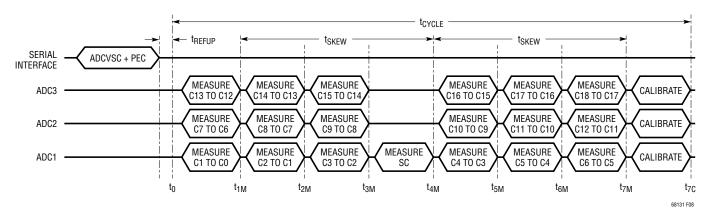

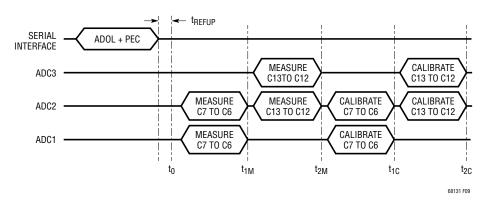

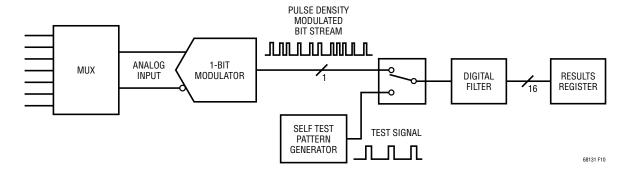

| ADC Operation                                   | .20  |

| Data Acquisition System Diagnostics             | .26  |

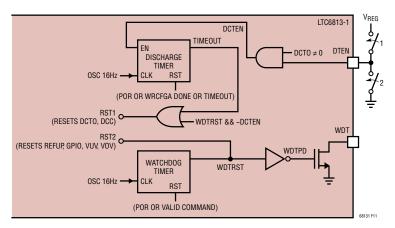

| Watchdog and Discharge Timer                    | .33  |

| Reset Behaviors                                 |      |

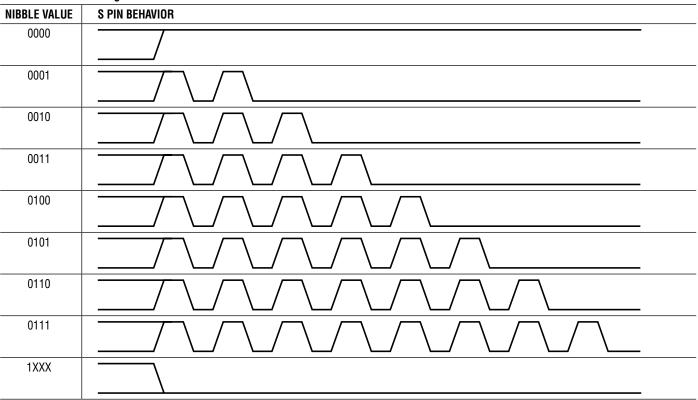

| S Pin Pulse-Width Modulation for Cell Balancing | .36  |

| Discharge Timer Monitor                              | 36 |

|------------------------------------------------------|----|

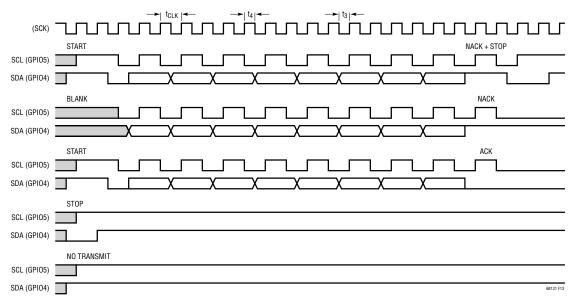

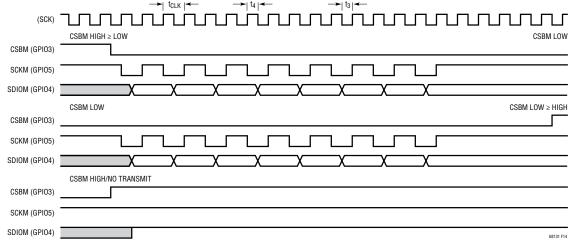

| I <sup>2</sup> C/SPI Master on LTC6813-1 Using GPIOs | 37 |

| S Pin Pulsing Using the S Pin Control Settings       | 42 |

| S Pin Muting                                         | 43 |

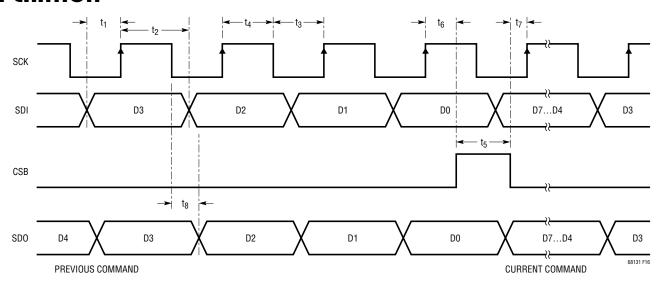

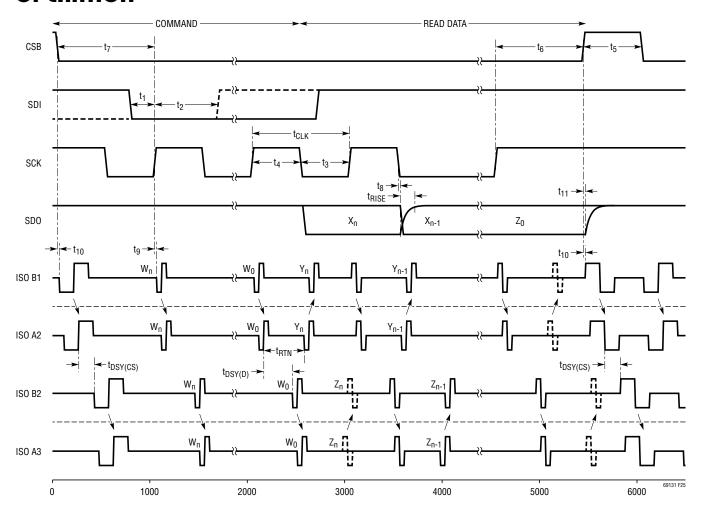

| Serial Interface Overview                            | 43 |

| 4-Wire Serial Peripheral Interface (SPI)             |    |

| Physical Layer                                       | 43 |

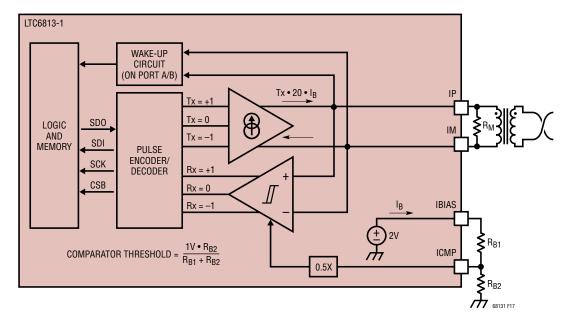

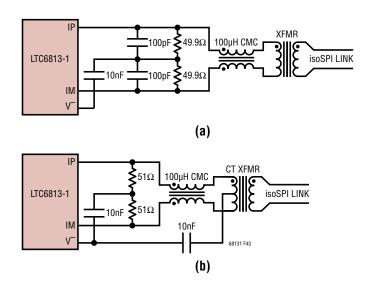

| 2-Wire Isolated Interface (isoSPI) Physical Layer.   | 43 |

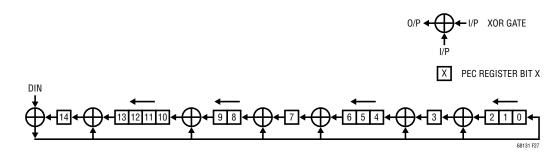

| Data Link Layer                                      |    |

| Network Layer                                        |    |

| Applications Information                             | 70 |

| Providing DC Power                                   | 70 |

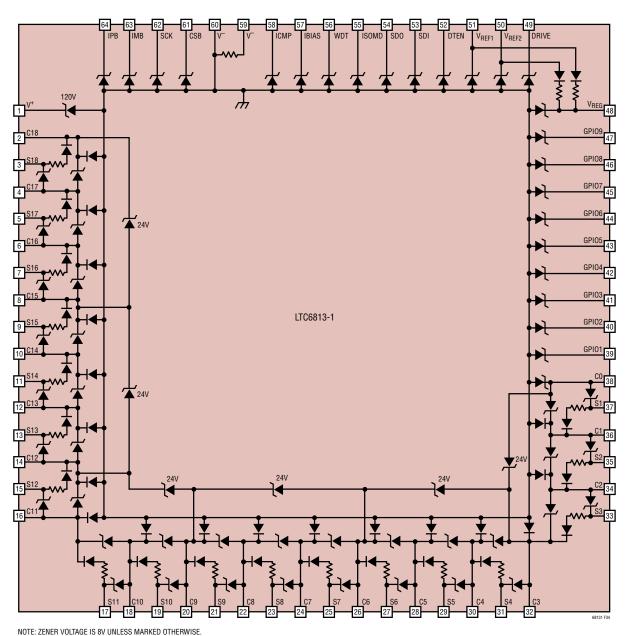

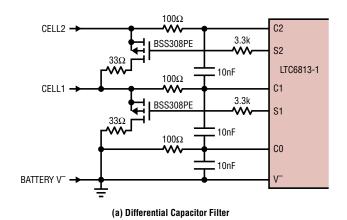

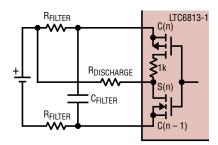

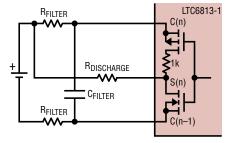

| Internal Protection and Filtering                    | 71 |

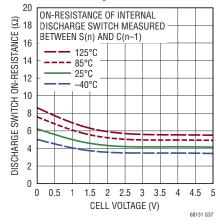

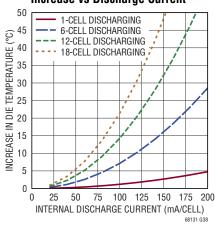

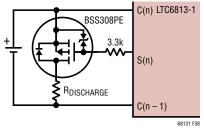

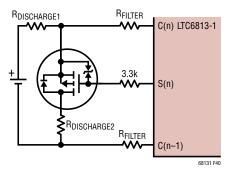

| Cell Balancing                                       | 74 |

| Discharge Control During Cell Measurements           | 75 |

| Digital Communications                               | 78 |

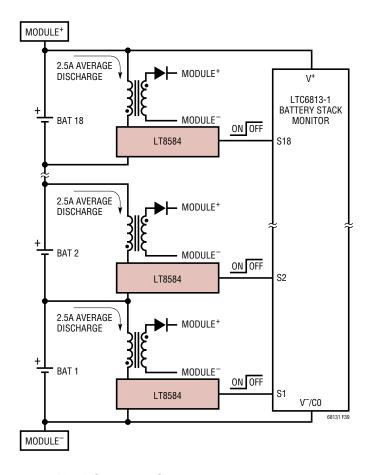

| Enhanced Applications                                | 85 |

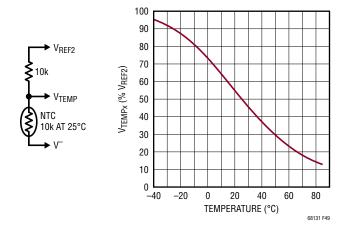

| Reading External Temperature Probes                  | 87 |

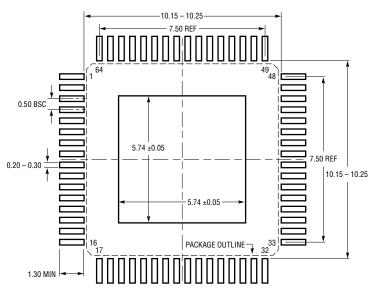

| Package Description                                  | 88 |

| Revision History                                     | 89 |

| Typical Application                                  | 90 |

| Related Parts                                        | 90 |

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Total Supply Voltage                                       |

|------------------------------------------------------------|

| V <sup>+</sup> to V <sup>-</sup> 112.5V                    |

| Supply Voltage (Relative to C12)                           |

| V <sup>+</sup> to C1250V                                   |

| Input Voltage (Relative to V <sup>-</sup> )                |

| C00.3V to 6V                                               |

| C180.3V to MIN (V+ + 5.5V, 112.5V)                         |

| C(n), S(n)0.3V to MIN (8 • n, 112.5V)                      |

| IPA, IMA, IPB, IMB $-0.3V$ to $V_{REG} + 0.3V$ , $\leq 6V$ |

| DRIVE0.3V to 7V                                            |

| All Other Pins0.3V to 6V                                   |

| Voltage Between Inputs                                     |

| C(n) to $C(n-1)$ , $S(n)$ to $C(n-1)$ 0.3V to 8V           |

| C18 to C15, C15 to C12, C12 to C9, C9 to C6, C6 to         |

| C3, C3 to C00.3V to 21V                                    |

| Current In/Out of Pins                                     |

| All Pins Except V <sub>REG</sub> , IPA, IMA, IPB, IMB,     |

| C(n), S(n)10mA                                             |

| IPA, IMA, IPB, IMB30mA                                     |

| Specified Junction Temperature Range                       |

| LTC6813I-140°C to 85°C                                     |

| LTC6813H-140°C to 125°C                                    |

| Junction Temperature 150°C                                 |

| Storage Temperature Range65°C to 150°C                     |

| Device HBM ESD Classification Level 1C                     |

| Device CDM ESD Classification Level C5                     |

## PIN CONFIGURATION

<sup>\*</sup>The Function of These Pins Depends on the Connection of ISOMD: ISOMD Tied to V $^-$ : CSB, SCK, SDI, SDO ISOMD Tied to V<sub>REG</sub>: IPA, IMA, NC, NC

## ORDER INFORMATION

#### AUTOMOTIVE PRODUCTS\*\*

| TRAY (160PC)         | TAPE AND REEL (1500PC) | PART MARKING* | PACKAGE DESCRIPTION   | MSL<br>Rating | SPECIFIED JUNCTION TEMPERATURE RANGE |

|----------------------|------------------------|---------------|-----------------------|---------------|--------------------------------------|

| LTC6813ILWE-1#3ZZPBF | LTC6813ILWE-1#3ZZTRPBF | LTC6813LWE-1  | 64-Lead Plastic eLQFP | 3             | -40°C to 85°C                        |

| LTC6813HLWE-1#3ZZPBF | LTC6813HLWE-1#3ZZTRPBF | LTC6813LWE-1  | 64-Lead Plastic eLQFP | 3             | -40°C to 125°C                       |

Contact the factory for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

Tape and reel specifications. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

<sup>\*\*</sup>This Pin Must Be Connected to V-

<sup>\*\*</sup>Versions of this part are available with controlled manufacturing to support the quality and reliability requirements of automotive applications. These models are designated with a #3ZZ suffix. Only the automotive grade products shown are available for use in automotive applications. Contact your local Analog Devices account representative for specific product ordering information and to obtain the specific Automotive Reliability reports for these models.

| ADC Offset Voltage  ADC Gain Error  (Note 2)  (Note Cin-1), GPIO(n) to V" = 0  (Note 3)  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 4.2, LTG6813I  (Note Cin-1), GPIO(n) to V = 0  (Note Cin-1), GPIO(n) to V = 0  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 4.2, LT | SYMBOL    | PARAMETER              | CONDITIONS                                               |   | MIN   | TYP   | MAX   | UNITS  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------------|----------------------------------------------------------|---|-------|-------|-------|--------|

| ADC Offset Voltage  ADC Gain Error  (Note 2)  (Note Cin-1), GPIO(n) to V" = 0  (Note 3)  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 4.2, LTG6813I  (Note Cin-1), GPIO(n) to V = 0  (Note Cin-1), GPIO(n) to V = 0  (Note Cin-1), GPIO(n) to V = 0  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 2.0, LTG6813I  (Note Cin-1), GPIO(n) to V = 3.3, LTG6813I  (Note Cin-1), GPIO(n) to V = 4.2, LTG6813I  (Not | ADC DC Sp | ecifications           |                                                          |   |       |       |       |        |

| ADC Gain Error   (Note 2)   0.01   %   %   %   %   %   %   %   %   %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           | Measurement Resolution |                                                          |   |       | 0.1   |       | mV/Bit |

| Total Measurement Error (TME) in Normal Mode    C(n) to C(n-1), GPIO(n) to V" = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | ADC Offset Voltage     | (Note 2)                                                 |   |       | 0.1   |       | mV     |

| Normal Mode   C(n) to C(n-1) = 2.0   ±1.6   m/V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | ADC Gain Error         | (Note 2)                                                 |   |       | 0.01  |       | %      |

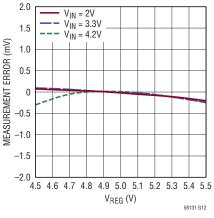

| C(n) to C(n-1), GPIO(n) to V" = 2.0, LTC6813I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 0$              |   |       | ±0.2  |       | mV     |

| C(n) to C(n-1), GPIO(n) to V" = 2.0, LTG6813H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           | Normal Mode            | C(n) to C(n-1) = 2.0                                     |   |       |       | ±1.6  | mV     |

| C(n) to C(n-1) = 3.3   ±2.2 mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 2.0$ , LTC68131 | • |       |       | ±1.8  | mV     |

| C(n) to C(n-1), GPIO(n) to V" = 3.3, LTC6813I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 2.0$ , LTC6813H | • |       |       | ±2.0  | mV     |

| C(n) to C(n-1), GPIO(n) to V⁻ = 3.3, LTC6813H       ■       ±3.3       mV         C(n) to C(n-1) = 4.2       ±2.8       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813H       ■       ±3.8       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813H       ■       ±4.2       mV         Sum of All Cells       ■       ±0.05       ±0.35       %         Internal Temperature, T = Maximum Specified Temperature       ±5       □       □         VREEP Pin       ■       −1       −0.15       0       %         VREEP Pin       ■       −0.05       0.05       0.20       %         Digital Supply Voltage, V <sub>REGD</sub> ■       −0.5       0.5       1.5       %         C(n) to C(n-1), GPIO(n) to V⁻ = 0       ±0.1       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 2.0, LTC6813I       ■       ±1.8       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 2.0, LTC6813I       ■       ±2.0       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 3.3       ±2.2       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 3.3, LTC6813I       ■       ±3.3       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813I       ■       ±3.3       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813I       ■                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |           |                        | C(n) to C(n-1) = 3.3                                     |   |       |       | ±2.2  | mV     |

| C(n) to C(n-1) = 4.2       ±2.8       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813I       ±3.8       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813H       ±4.2       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 5.0       ±1       mV         Sum of All Cells       ±0.05       ±0.35       %         Internal Temperature, T = Maximum Specified Temperature       ±5       °C       °C         VREG Pin       −1       −0.15       0       %         VREG Pin       −0.05       0.05       0.20       %         Digital Supply Voltage, V <sub>REGD</sub> −0.05       0.05       0.20       %         Total Measurement Error (TME) in Filtered Mode       C(n) to C(n-1), GPIO(n) to V⁻ = 0       ±0.1       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 0       ±0.1       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 2.0, LTC6813I       ±0.1       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 2.0, LTC6813I       ±0.1       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 3.3, LTC6813I       ±2.2       mV         C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813I       ±3.3       mV         C(n) t                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 3.3$ , LTC68131 | • |       |       | ±3.0  | mV     |

| C(n) to C(n-1), GPIO(n) to V" = 4.2, LTC6813I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 3.3$ , LTC6813H | • |       |       | ±3.3  | mV     |

| C(n) to C(n-1), GPIO(n) to V" = 4.2, LTC6813H                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |           |                        | C(n) to C(n-1) = 4.2                                     |   |       |       | ±2.8  | mV     |

| C(n) to C(n-1), GPIO(n) to V⁻ = 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 4.2$ , LTC68131 | • |       |       | ±3.8  | mV     |

| Sum of All Cells                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 4.2$ , LTC6813H | • |       |       | ±4.2  | mV     |

| Internal Temperature, T = Maximum Specified Temperature   VREG Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 5.0$            |   |       | ±1    |       | mV     |

| Temperature   VREG Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                        | Sum of All Cells                                         | • |       | ±0.05 | ±0.35 | %      |

| VREF2 Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                        |                                                          |   |       | ±5    |       | °C     |

| Digital Supply Voltage, V_REGD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                        | V <sub>REG</sub> Pin                                     | • | -1    | -0.15 | 0     | %      |

| Total Measurement Error (TME) in Filtered Mode  C(n) to C(n-1), GPIO(n) to V⁻ = 0  C(n) to C(n-1), GPIO(n) to V⁻ = 2.0, LTC6813I  C(n) to C(n-1), GPIO(n) to V⁻ = 2.0, LTC6813I  C(n) to C(n-1), GPIO(n) to V⁻ = 2.0, LTC6813H  C(n) to C(n-1) = 3.3  C(n) to C(n-1), GPIO(n) to V⁻ = 3.3, LTC6813H  C(n) to C(n-1), GPIO(n) to V⁻ = 3.3, LTC6813H  C(n) to C(n-1) = 4.2  C(n) to C(n-1) = 4.2  C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813H  C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813H  C(n) to C(n-1), GPIO(n) to V⁻ = 4.2, LTC6813H  C(n) to C(n-1), GPIO(n) to V⁻ = 5.0  Sum of All Cells  Internal Temperature, T = Maximum Specified Temperature  V <sub>REG</sub> Pin  V <sub>REF2</sub> Pin  • −1 −0.15 0 %  V <sub>REF2</sub> Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           |                        | V <sub>REF2</sub> Pin                                    | • | -0.05 | 0.05  | 0.20  | %      |

| Filtered Mode $ \begin{array}{ c c c c c c }\hline C(n) \ to \ C(n-1) = 2.0 & \pm 1.6 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 2.0, \ LTC6813I & \pm 1.8 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 2.0, \ LTC6813H & \pm 2.0 & \text{mV} \\\hline C(n) \ to \ C(n-1) = 3.3 & \pm 2.2 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 3.3, \ LTC6813I & \pm 3.0 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 3.3, \ LTC6813H & \pm 3.3 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 3.3, \ LTC6813H & \pm 3.8 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 4.2, \ LTC6813I & \pm 3.8 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 4.2, \ LTC6813H & \pm 4.2 & \text{mV} \\\hline C(n) \ to \ C(n-1), \ GPIO(n) \ to \ V^- = 5.0 & \pm 1 & \text{mV} \\\hline Sum \ of \ All \ Cells & \pm 0.05 & \pm 0.35 & \% \\\hline Internal \ Temperature & T = Maximum \ Specified \ Temperature & T = 0.15 & 0 & \% \\\hline V_{REG} \ Pin & -1 & -0.15 & 0 & \% \\\hline V_{REF2} \ Pin & -0.05 & 0.05 & 0.20 & \% \\\hline \end{array}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           |                        | Digital Supply Voltage, V <sub>REGD</sub>                | • | -0.5  | 0.5   | 1.5   | %      |

| C(n) to C(n-1), GPIO(n) to V <sup>-</sup> = 2.0, LTC6813I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 0$              |   |       | ±0.1  |       | mV     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           | Filtered Mode          | C(n) to $C(n-1) = 2.0$                                   |   |       |       | ±1.6  | mV     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 2.0$ , LTC68131 | • |       |       | ±1.8  | mV     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 2.0$ , LTC6813H | • |       |       | ±2.0  | mV     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                        | C(n) to C(n-1) = 3.3                                     |   |       |       | ±2.2  | mV     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 3.3$ , LTC68131 | • |       |       | ±3.0  | mV     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 3.3$ , LTC6813H | • |       |       | ±3.3  | mV     |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                        | C(n) to C(n-1) = 4.2                                     |   |       |       | ±2.8  | mV     |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 4.2$ , LTC68131 | • |       |       | ±3.8  | mV     |

| Sum of All Cells $\bullet$ $\pm 0.05$ $\pm 0.35$ %  Internal Temperature, T = Maximum Specified Temperature $V_{REG}$ Pin $\bullet$ -1 -0.15 0 % $V_{REF2}$ Pin $\bullet$ -0.05 0.05 0.20 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 4.2$ , LTC6813H | • |       |       | ±4.2  | mV     |

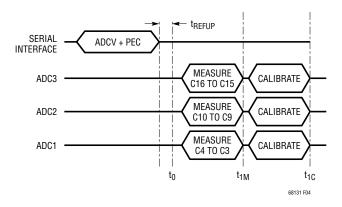

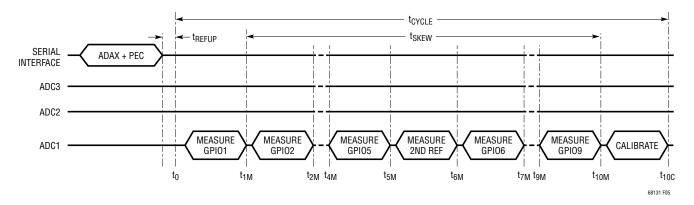

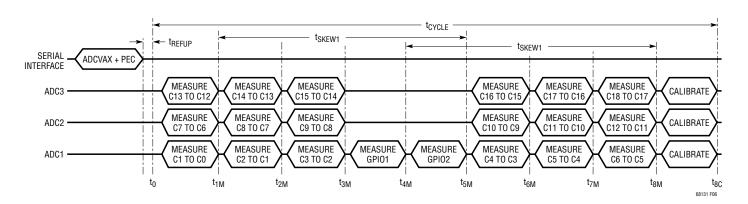

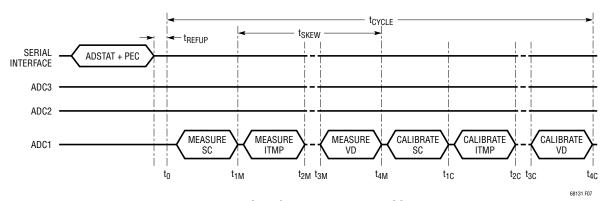

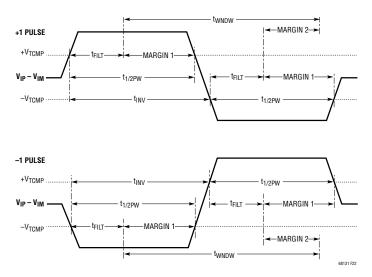

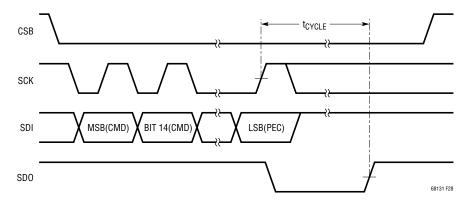

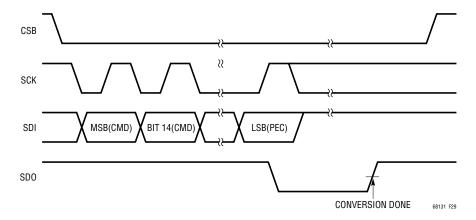

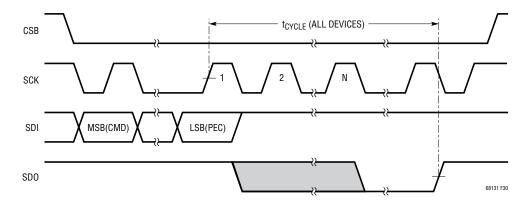

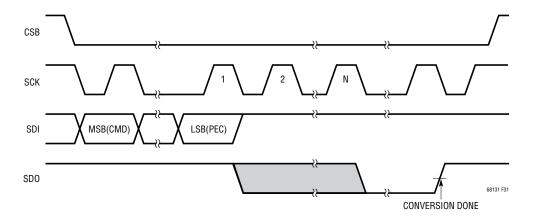

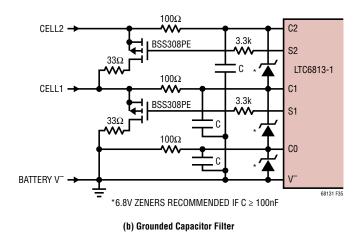

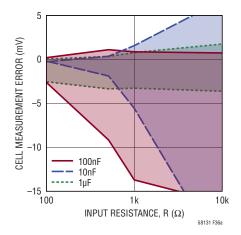

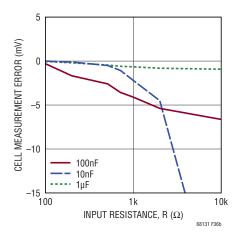

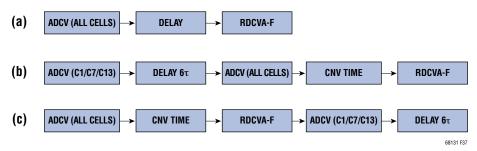

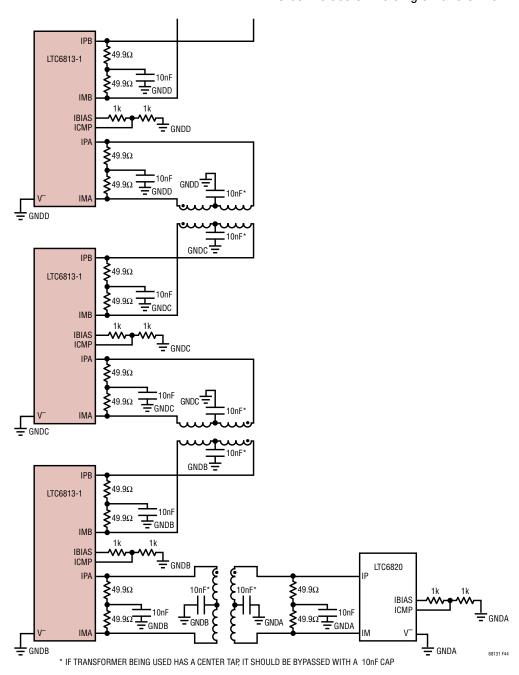

| Internal Temperature, T = Maximum Specified Temperature $V_{REG}$ Pin $\bullet$ -1 -0.15 0 % $V_{REF2}$ Pin $\bullet$ -0.05 0.05 0.20 %                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |                        | $C(n)$ to $C(n-1)$ , $GPIO(n)$ to $V^- = 5.0$            |   |       | ±1    |       | mV     |