#### **General Description**

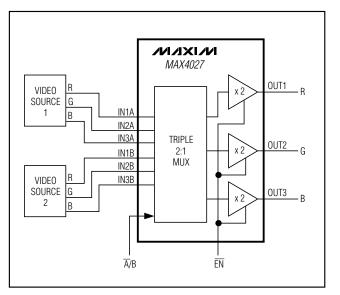

The MAX4027 is a triple, wideband, 2-channel, noninverting gain-of-two video amplifier with input multiplexing, capable of driving up to two back-terminated video loads. The MAX4027 features current-mode feedback amplifiers configured for a gain of two (+6dB) with a -3dB large-signal bandwidth of 200MHz. The device has low (0.012%/0.014°) differential gain and phase errors, and operates from ±5V supplies.

The MAX4027 is ideal for use in broadcast and graphics video systems because of the low 2pF input capacitance, channel-to-channel switching time of only 15ns, and wide 62MHz, large-signal 0.1dB bandwidth. Highimpedance output disabling allows the MAX4027 to be incorporated into large switching arrays with minimal interaction with the source. Specified over the -40°C to +85°C extended temperature range, the MAX4027 is available in 14-pin SO and TSSOP packages.

#### **Applications**

Video Source Selection (Multiplexing) Picture in Picture (PIP) Insertion Crosspoint Expansion Coaxial Cable Drivers Supports VGA to UXGA (1600 x 1200) Resolution Enterprise Class (Blade) Servers Keyboard-Video-Mouse (KVM)

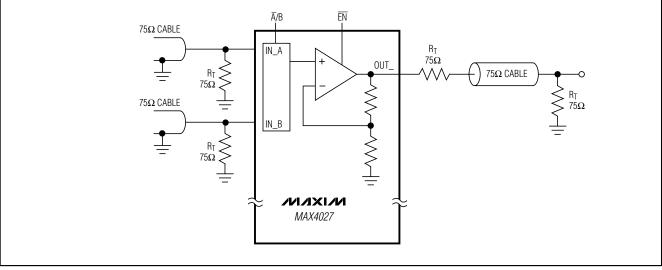

#### Typical Operating Circuit

####

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **Features**

- Excellent Video Specifications: 75MHz Small-Signal 0.1dB Gain Flatness 62MHz Large-Signal 0.1dB Gain Flatness 0.012%/0.014° Differential Gain/Phase Error

- VGA to UXGA Resolution

- High Speed: 200MHz 2VP-P -3dB Bandwidth 1100V/µs Slew Rate 15ns Settling Time to 0.1%

- Internal Gain of 2V/V Compensates for Output Back Termination

- Fast Switching: 15ns Channel-Switching Time 260mVP-P Switching Transient

- Drives Two Back-Terminated Video Loads

- ♦ High-Impedance Output Disable

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX4027ESD | -40°C to +85°C | 14 SO       |

| MAX4027EUD | -40°C to +85°C | 14 TSSOP    |

#### **Pin Configuration**

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| Positive Supply Voltage (V <sub>CC</sub> to GND)           | +6V     |

|------------------------------------------------------------|---------|

| Negative Supply Voltage (VEE to GND)                       | 6V      |

| Amplifier Input Voltage (IN)(VEE - 0.3V) to (VCC           | + 0.3V) |

| Digital Input Voltage (EN, A/B)0.3V to (V <sub>CC</sub>    | + 0.3V) |

| Output Short Circuit to GND (Note 1)Cor                    |         |

| Output Short Circuit to V <sub>CC</sub> or V <sub>EE</sub> | 5s      |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 14-Pin TSSOP (derate 9.1mW/°C above +70°C             | C)727mW        |

| 14-Pin SO (derate 8.3mW/°C above +70°C)               | 667mW          |

| Operating Temperature Range                           | -40°C to +85°C |

| Storage Temperature Range6                            | 65°C to +150°C |

| Junction Temperature                                  |                |

| Lead Temperature (soldering, 10s)                     | +300°C         |

Note 1: Continuous power-dissipation rating must also be observed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V, V_{EE} = -5V, V_{IN_{-}} = 0V, R_L = 150\Omega$  to GND,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

|                                                 | -                 |                                                                          | 51                               |       | , (   | ,    |       |

|-------------------------------------------------|-------------------|--------------------------------------------------------------------------|----------------------------------|-------|-------|------|-------|

| PARAMETER                                       | SYMBOL            | COND                                                                     | ITIONS                           | MIN   | ТҮР   | MAX  | UNITS |

| Operating Supply Voltage Pange                  | V <sub>CC</sub>   | Inferred from the PSRR test                                              |                                  | +4.5  | +5.0  | +5.5 | V     |

| Operating Supply Voltage Range                  | VEE               |                                                                          |                                  | -4.5  | -5.0  | -5.5 |       |

| Desitive Current Current                        |                   | $\overline{EN} = GND$                                                    |                                  |       | 31    | 39   | mA    |

| Positive Supply Current                         | ICC               | $\overline{EN} = 5V$                                                     |                                  |       | 17    | 24   | ШA    |

| Negetive Supply Current                         |                   | $\overline{EN} = GND$                                                    |                                  |       | 28    | 36   |       |

| Negative Supply Current                         | IEE               | $\overline{EN} = 5V$                                                     |                                  |       | 15    | 21   | mA    |

| Input Voltage Range                             | V <sub>IN_</sub>  | Inferred from voltage g                                                  | ain                              | ±1.25 | ±1.75 |      | V     |

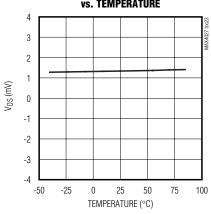

| Input Offect Veltere                            |                   | $T_A = +25^{\circ}C$                                                     |                                  |       | ±1    | ±6   | mV    |

| Input Offset Voltage                            | Vos               | $T_{A} = -40^{\circ}C \text{ to } +85^{\circ}C$                          |                                  |       |       | ±11  | mv    |

| Input Offset-Voltage Matching                   | ΔV <sub>OS</sub>  | Channel to channel                                                       |                                  |       | ±1    | ±12  | mV    |

| Voltage Gain                                    | Av                | $V_{OUT} = \pm 2.5V$                                                     |                                  | 1.9   | 2.0   | 2.1  | V/V   |

| Input Offset-Voltage Temperature<br>Coefficient | TCV <sub>OS</sub> |                                                                          |                                  |       | 1     |      | µV/°C |

|                                                 | Ι <sub>Β</sub>    | T <sub>A</sub> = +25°C                                                   |                                  |       | ±2    | ±10  |       |

| Input Bias Current                              |                   | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                            |                                  |       |       | ±18  | μA    |

|                                                 | _                 | V <sub>IN_</sub> = -1.25V to<br>+1.25V                                   | Channel on                       | 100   | 400   |      | kΩ    |

| Input Resistance                                | RIN               |                                                                          | Channel off                      | 1     | 20    |      | MΩ    |

| DC Output Resistance                            | Rout              |                                                                          |                                  |       | 10    |      | mΩ    |

| Disabled Output Resistance                      | ROUT(d)           | $\overline{\text{EN}} = 5\text{V}, \text{V}_{\text{OUT}} = -2.5\text{V}$ | √ to +2.5V (Note 3)              |       | 1.6   |      | kΩ    |

| DC Power-Supply Rejection Ratio                 | PSRR              | $V_{CC} = +4.5V \text{ to } +5.5V,$                                      | V <sub>EE</sub> = -4.5V to -5.5V | 60    | 86    |      | dB    |

| Output Voltage Swing                            | Vout_             |                                                                          |                                  | ±2.5  | ±3.5  |      | V     |

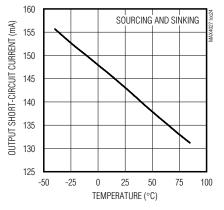

| Output Short-Circuit Current                    | Isc               |                                                                          |                                  |       | ±143  |      | mA    |

| LOGIC CHARACTERISTICS ( $\overline{EN}$ ,       | Ā/B)              |                                                                          |                                  |       |       |      |       |

| Logic-Low Threshold                             | VIL               |                                                                          |                                  |       |       | 0.8  | V     |

| Logic-High Threshold                            | VIH               |                                                                          |                                  | 2.0   |       |      | V     |

| Logic-Low Input Current                         | Ι <sub>ΙL</sub>   | V <sub>IL</sub> = 0V                                                     |                                  |       | -4    | -20  | μΑ    |

| Logic-High Input Current                        | IIН               | $V_{IH} = +5.5V, V_{CC} = +5.5V$                                         |                                  |       | 350   | 600  | μA    |

|                                                 |                   |                                                                          |                                  |       |       |      |       |

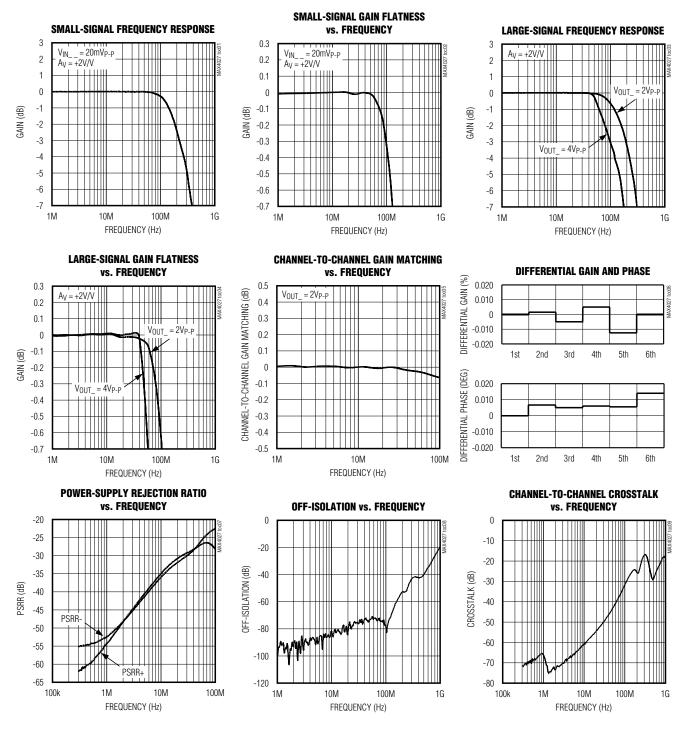

#### AC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V, V_{EE} = -5V, V_{IN_{-}} = 0V, R_{IN} = 75\Omega$  to GND,  $R_L = 150\Omega$  to GND,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

| PARAMETER                                          | SYMBOL            | CONDITIONS                                                        | MIN TYP MAX | UNITS             |

|----------------------------------------------------|-------------------|-------------------------------------------------------------------|-------------|-------------------|

| AMPLIFIER CHARACTERISTICS                          | S                 |                                                                   |             |                   |

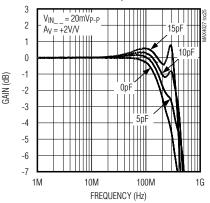

| Small-Signal -3dB Bandwidth                        | BWSS              | $V_{IN_{-}} = 20mV_{P-P}$                                         | 225         | MHz               |

| Small-Signal Bandwidth for<br>±0.1dB Gain Flatness | BWLS(0.1)         | $V_{IN\_} = 20mV_{P-P}$                                           | 75          | MHz               |

| Large-Signal -3dB Bandwidth                        | BW <sub>LS</sub>  | $V_{IN_{-}} = 1V_{P-P}$                                           | 200         | MHz               |

| Large-Signal Bandwidth for<br>±0.1dB Gain Flatness | BWLS(0.1)         | V <sub>IN_</sub> = 1V <sub>P-P</sub>                              | 62          | MHz               |

| Slew Rate                                          | SR                | $V_{IN_{-}} = 1V_{P-P}$                                           | 1100        | V/µs              |

| Settling Time to 0.1%                              | ts                | $V_{IN_{-}} = 1V_{P-P}$                                           | 15          | ns                |

| Differential Gain Error                            | DG                | 5-step modulated staircase (Note 4)                               | 0.012       | %                 |

| Differential Phase Error                           | DP                | 5-step modulated staircase (Note 4)                               | 0.014       | degrees           |

| Delay Between Channels                             | tD                | $V_{IN_{-}} = 1V_{P-P}, t_{R} = 100ps$                            | 0.1         | ns                |

| Channel-to-Channel Crosstalk                       | X <sub>TALK</sub> | $V_{IN_{P-P}} = \pm 1V_{P-P}, f = 10MHz$                          | -61         | dB                |

| Ā/B Crosstalk                                      |                   | $V_{IN_{_}} = \pm 1V_{P-P}, f = 10MHz$                            | -80         | dB                |

| Output Impedance                                   | Zout              | f = 10MHz                                                         | 1           | Ω                 |

| Total Harmonic Distortion                          | THD               | $V_{OUT} = 2V_{P-P}, f = 10MHz$                                   | 64          | dBc               |

| Off-Isolation                                      | AISO              | $V_{OUT}$ = 2 $V_{P-P}$ , f = 10MHz, R <sub>S</sub> = 75 $\Omega$ | -83         | dB                |

| Output Capacitance                                 | Соит              | Channel on or off                                                 | 3           | pF                |

| Input Capacitance                                  | CIN               | Channel on or off                                                 | 2           | pF                |

| Input-Voltage Noise Density                        | en                | f = 100 kHz                                                       | 6.5         | nV/√Hz            |

| Input-Current Noise Density                        | in                | f = 100kHz                                                        | 6.5         | pA/√Hz            |

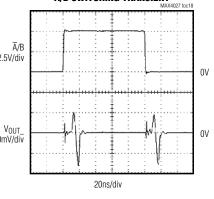

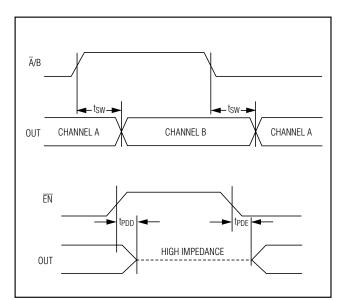

| SWITCHING CHARACTERISTIC                           | S                 |                                                                   |             |                   |

| Channel-Switching Time                             | tsw               | (Notes 5, 6)                                                      | 15          | ns                |

| Enable Delay Time                                  | <b>t</b> PDE      | (Notes 5, 7)                                                      | 20          | ns                |

| Disable Delay Time                                 | <b>t</b> PDD      | (Notes 5, 7) 25                                                   |             |                   |

| Switching Transient                                | VTRAN             | (Note 8)                                                          | 260         | mV <sub>P-P</sub> |

|                                                    |                   |                                                                   |             |                   |

**Note 2:** Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range are guaranteed by design.

Note 3: Disabled output resistance includes the internal feedback network.

Note 4: Input test signal is NTSC composite with 5-step staircase, of 40 IRE per step, modulated with 3.58MHz color subcarrier.

Note 5: See the Timing Diagram (Figure 2).

Note 6: Channel-switching time specified for switching between input channels; does not include signal rise/fall times for switching between channels with different input voltages.

Note 7: Output enable/disable delay times do not include amplifier output slewing times.

Note 8: Switching transient measured while switching between two grounded channels.

$(V_{CC} = +5V, V_{EE} = -5V, R_L = 150\Omega$  to GND,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

**Typical Operating Characteristics**

M/IXI/N

**MAX4027**

4

#### $(V_{CC} = +5V, V_{EE} = -5V, R_L = 150\Omega$ to GND, $T_A = +25^{\circ}C$ , unless otherwise noted.) **TOTAL HARMONIC DISTORTION Ā/B CROSSTALK vs. FREQUENCY OUTPUT IMPEDANCE vs. FREQUENCY** vs. FREQUENCY 0 100 -20 $V_{OUT} = 2V_{P-P}$ -30 -20 10 OUTPUT IMPEDANCE ( $\Omega$ ) -40 -40 CROSSTALK (dB) THD (dBc) -50 -60 1 -60 -80 -70 0.1 -100 -80 -120 0.01 -90 100k 1M 100M 100k 10M 100M 1G 10M 1G 1M 1M 10M 100M FREQUENCY (Hz) FREQUENCY (Hz) FREQUENCY (Hz) LARGE-SIGNAL PULSE RESPONSE LARGE-SIGNAL PULSE RESPONSE **SMALL-SIGNAL PULSE RESPONSE** $(C_{LOAD} = 20pF)$ MAX4027 toc15 V<sub>IN\_</sub> 50mV/div VIN V<sub>IN</sub>\_\_\_ 500mV/div 500mV/div 0V 0V 0V V<sub>OUT\_</sub> 1V/div V<sub>OUT\_</sub> 100mV/div Vout 1V/div 0V 0V 0V 10ns/div 10ns/div 10ns/div SMALL-SIGNAL PULSE RESPONSE **A/B SWITCHING TRANSIENT ENABLE RESPONSE TIME** $(C_{LOAD} = 20pF)$ 27 toc18 ΕN Ā/B $V_{\text{IN}}$ 2.5V/div 2.5V/div 50mV/div 0V 0V 0V VOUT VOUT Vout 0V 100mV/div 1V/div 100mV/div 0V 0V

20ns/div

# **Typical Operating Characteristics (continued)**

10ns/div

5

# **MAX4027**

# 225MHz, Triple, 2-Channel Video Multiplexer-Amplifier

2.0

1.5

1.0

0.5

0

-50 -25

#### **Typical Operating Characteristics (continued)** $(V_{CC} = +5V, V_{EE} = -5V, R_L = 150\Omega$ to GND, $T_A = +25^{\circ}C$ , unless otherwise noted.) **INPUT BIAS CURRENT POSITIVE OUTPUT SWING SUPPLY CURRENT vs. TEMPERATURE** vs. TEMPERATURE vs. TEMPERATURE 5.0 5.0 4.5 4.0 4.5 POSITIVE OUTPUT SWING (V) INPUT BIAS CURRENT (µA) 3.5 3.0 4.0 2.5

25

TEMPERATURE (°C)

50

0

75

100

TEMPERATURE (°C) **NEGATIVE OUTPUT SWING** vs. TEMPERATURE -2.5 -3.0 -3.0 -3.5 -3.5 -4.(  $R_{LOAD}=50\Omega$  $R_{LOAD} = 150\Omega$ NO LOAD -4.5 -5.0 -50 -25 0 25 50 75 100 TEMPERATURE (°C)

50

75

100

**INPUT OFFSET VOLTAGE** vs. TEMPERATURE

-25

0

25

TEMPERATURE (°C)

50

3.5

3.0

2.5

-50

#### SMALL-SIGNAL BANDWIDTH vs. FREQUENCY

100

75

M/IXI/M

35

34

33

32

31

30

29

28

27

26

25

-50

-25

0 25

SUPPLY CURRENT (mA)

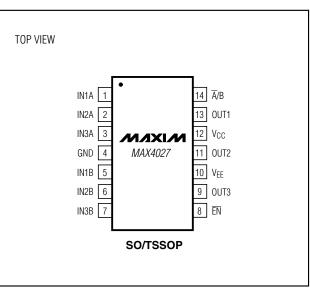

#### \_Pin Description

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                 |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | IN1A | Amplifier 1 Channel A Input                                                                                                                                                                                                                                              |

| 2   | IN2A | Amplifier 2 Channel A Input                                                                                                                                                                                                                                              |

| 3   | IN3A | Amplifier 3 Channel A Input                                                                                                                                                                                                                                              |

| 4   | GND  | Power Supply, Analog and Digital Ground. Connect GND to ground plane for best RF performance.                                                                                                                                                                            |

| 5   | IN1B | Amplifier 1 Channel B Input                                                                                                                                                                                                                                              |

| 6   | IN2B | Amplifier 2 Channel B Input                                                                                                                                                                                                                                              |

| 7   | IN3B | Amplifier 3 Channel B Input                                                                                                                                                                                                                                              |

| 8   | ĒN   | Output Enable Logic Input. Drive $\overline{EN}$ low or leave open for normal operation. Pull $\overline{EN}$ high to disconnect amplifier output (output is high impedance when disabled). $\overline{EN}$ is internally pulled to GND through a 17k $\Omega$ resistor. |

| 9   | OUT3 | Amplifier Output 3                                                                                                                                                                                                                                                       |

| 10  | VEE  | Negative Power-Supply Voltage. Bypass $V_{EE}$ to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                      |

| 11  | OUT2 | Amplifier Output 2                                                                                                                                                                                                                                                       |

| 12  | Vcc  | Positive Power-Supply Voltage. Bypass $V_{CC}$ to GND with a 0.1µF capacitor.                                                                                                                                                                                            |

| 13  | OUT1 | Amplifier Output 1                                                                                                                                                                                                                                                       |

| 14  | Ā/B  | Channel-Select Input. Drive $\overline{A}/B$ low or leave open to select channel A for all amplifiers. Pull $\overline{A}/B$ high to select channel B for all amplifiers. $\overline{A}/B$ is internally pulled to GND through a 17k $\Omega$ resistor.                  |

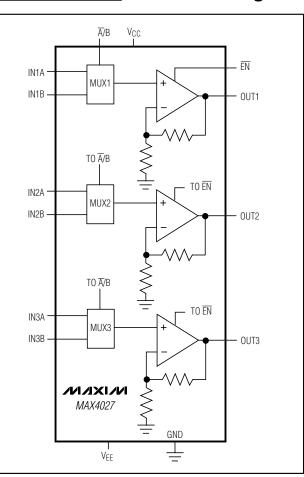

#### **Detailed Description**

# The MAX4027 combines three 2:1 multiplexers with +2V/V (+6dB) closed-loop gain (A<sub>VCL</sub>) amplifiers. This low-power, high-speed device operates from $\pm$ 5V supplies, while driving up to two back-terminated video loads with very low distortion. Differential gain and phase errors are 0.012%/0.014° for the MAX4027.

The input multiplexers feature fast 15ns channelswitching times and small switching transients. The multiplexers also feature high input resistance and constant input capacitance, so overall input impedance can be set by external input-terminating resistors.

Drive  $\overline{\text{EN}}$  high to place the amplifier outputs in a highimpedance state, and minimize the supply current. This function allows use of multiple mux/amps in parallel to form large switching arrays.

The MAX4027 features an  $\overline{A}/B$  input, which selects either channel A or B. Drive  $\overline{A}/B$  low to select channel A or drive  $\overline{A}/B$  high to select channel B. Channel A is automatically selected if  $\overline{A}/B$  is left unconnected.

#### Table 1. Input Control Logic

| Ā/B | AMPLIFIER INPUT | FUNCTION           |

|-----|-----------------|--------------------|

| 0   | IN_A            | Channel A Selected |

| 1   | IN_B            | Channel B Selected |

#### **Table 2. Output Control Logic**

| ĒN | AMPLIFIER OUTPUT | FUNCTION                  |

|----|------------------|---------------------------|

| 0  | On               | Outputs Enabled           |

| 1  | Off              | Outputs High<br>Impedance |

#### **Applications Information**

#### Disable Mode

**Truth Tables**

Drive  $\overline{\text{EN}}$  high to place the MAX4027 in disable mode. Placing the device in disable mode reduces the quiescent current to 17mA (V<sub>CC</sub>) and 15mA (V<sub>EE</sub>) and places the amplifier outputs into a high-impedance state, typi-

# **MAX4027**

cally 1.6k $\Omega$ . Parallel multiple devices to construct larger switch matrices by connecting the outputs of several devices together and disabling all but one of the paralleled amplifiers' outputs. Two internal 800 $\Omega$  thin-film resistors set the MAX4027 to a fixed gain of +2. Consider the impedance of the internal feedback resistors when operating multiple MAX4027s in large multiplexer applications.

Drive  $\overline{\text{EN}}$  low for normal operation.  $\overline{\text{EN}}$  has internal pulldown circuitry. The MAX4027 is enabled when  $\overline{\text{EN}}$  is unconnected.

#### **Video Line Driver**

The MAX4027 is well suited to drive short coaxial transmission lines when the cable is terminated at both ends (Figure 1) where the fixed gain of +2 compensates for the loss in the back termination. Cable frequency response may cause variations in the flatness of the signal.

#### **Input Voltage Range**

The guaranteed input voltage range is  $\pm 1.25V$ . Exceeding this value can cause unpredictable results, including output clipping, excessive input current, and switching delays.

#### **Multiplexer**

The input multiplexer (mux) is controlled by a 3.3V TTL/CMOS-compatible control input (see the *Truth Tables*). Input capacitance is a constant, low 2pF and input resistance is 17k $\Omega$  to GND for all input channels, regardless of whether or not the channel is selected. All logic levels ( $\overline{EN}$  and  $\overline{A}$ /B) default low if left unconnected.

#### Layout and Power-Supply Bypassing

The MAX4027 has an extremely high bandwidth and requires careful board layout. For best performance, use constant-impedance microstrip or stripline techniques.

To realize the full AC performance of these high-speed amplifiers, pay careful attention to power-supply bypassing and board layout. The PC board should have at least two layers: a signal and power layer on one side, and a large, low-impedance ground plane on the other side. The ground plane should be as free of voids as possible. With multilayer boards, locate the ground plane on an internal layer that incorporates no signal or power traces.

Observe the following guidelines when designing the board regardless of whether or not a constant-impedance board is used.

- 1) Do not use wire-wrap boards or breadboards.

- 2) Do not use IC sockets; they increase parasitic capacitance and inductance.

- Keep lines as short and as straight as possible. Do not make 90° turns; round all corners.

- 4) Observe high-frequency bypassing techniques to maintain the amplifier's accuracy and stability.

- 5) Use surface-mount components. They generally have shorter bodies and lower parasitic reactance, yielding better high-frequency performance than through-hole components.

The bypass capacitors should include a  $0.1\mu F$  ceramic surface-mount capacitor between each supply pin and the ground plane, located as close to the package as

Figure 1. Video Line Driver

**MAX4027**

possible. Optionally, place a 10 $\mu$ F tantalum capacitor at the power-supply pins' points of entry to the PC board to ensure the integrity of incoming supplies. The power-supply trace should lead directly from the tantalum capacitor to the V<sub>CC</sub> and V<sub>EE</sub> pins.

Use surface-mount resistors for input termination and output back termination. Place the termination resistors as close to the IC as possible.

Figure 2. Switching Timing Diagram

#### Functional Diagram

**MAX4027**

#### \_Chip Information

TRANSISTOR COUNT: 870 PROCESS: Bipolar

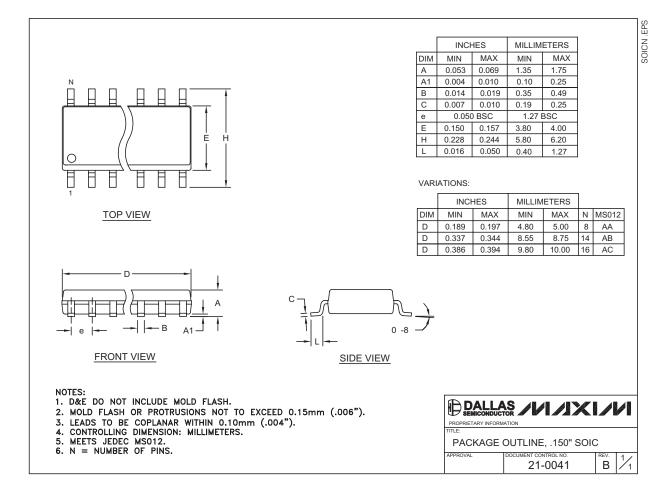

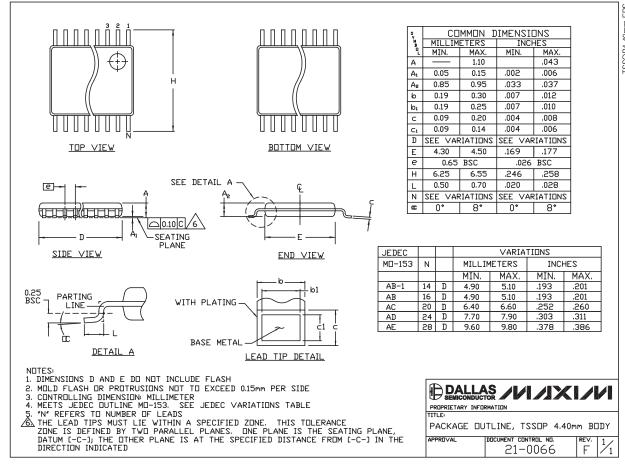

#### **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

**MAX4027**

M/XI/M

#### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to **www.maxim-ic.com/packages**.)

MAX4027

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

© 2003 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.

\_ 11