# Internal 3.5A MOSFET Switching Regulator IC for Buck Converter

### **FEATURES**

- Fast transient response at recovering from voltage drop

- External clock synchronization

- Operating voltage range 4.45V to 40V

- Switching current

- Oscillating frequency

- C ver. 450kHz J ver. 100k to 1000kHz

5A min.

- PWM control

- Maximum 100% duty cycle

- Adjustable soft start function

- Corresponds to MLCC

- UVLO function

- Over Current Protection (Hiccup type)

- Thermal shutdown protection

- Power Good function

- Standby function

- Package outline HSOP8

# **■GENERAL DESCRIPTION**

**TYPICAL APPLICATION**

The NJW4196 is a buck converter with 40V/3.5A MOSFET.

It improves transient response at recovering from voltage drop compare with conventional current mode products. Therefore the NJW4196 provides excellent stable regulation even under condition of large voltage fluctuations.

Oscillating frequency can be synchronized with an externally input clock.

Also, it has a soft start function, an over current protection and a thermal shutdown circuit.

It is suitable for power supply for Car Accessory, Office Automation Equipment, Industrial Instrument and so on.

### ■APPLICATION

### Car accessory

- Industrial equipment

- OA equipment

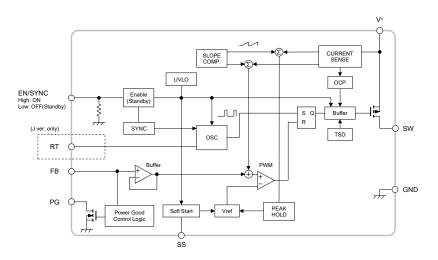

# ■BLOCK DIAGRAM

#### V<sub>out</sub> CSBD C Cour Ş R2 sw -----EN/ SYNC EN/SYNC NJW4196 0 FB High: ON I ow: OFF (St Power Good PG ss RT GND R1 ⋛⋼ ᡔᠯᡔ C1 Rτ $\rightarrow$ t the (J ver. only)

*New Japan Radio Co., Ltd.* www.njr.com

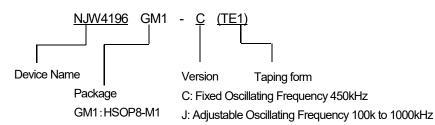

# ■PRODUCT CLASSIFICATION

|   | Part Number  | Version | Oscillating Frequency      |

|---|--------------|---------|----------------------------|

|   | NJW4196GM1-C | С       | Fixed 450kHz               |

| _ | NJW4196GM1-J | J       | Adjustable 100k to 1000kHz |

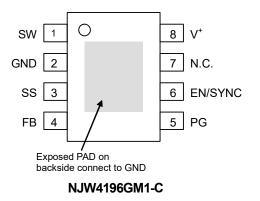

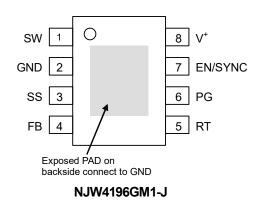

# ■PIN CONFIGURATION

| SYMBOL         | Pin    | NO.    | DESCRIPTION                                                                                   |

|----------------|--------|--------|-----------------------------------------------------------------------------------------------|

| STMDOL         | C ver. | J ver. | DESCRIFTION                                                                                   |

| SW             | 1      | 1      | Switch output pin of Power MOSFET                                                             |

| GND            | 2      | 2      | GND pin                                                                                       |

| SS             | 3      | 3      | Soft Start time setting pin.                                                                  |

|                | 5      | 5      | Soft start time is set by an external capacitor.                                              |

|                |        |        | Output voltage detecting pin                                                                  |

| FB             | 4      | 4      | Connects output voltage through the resistor divider tap to this pin in order to              |

|                |        |        | voltage of the FB pin become 1V.                                                              |

| RT             | _      | 5      | Oscillating frequency setting pin with an external timing resistor.                           |

|                | -      | 5      | Oscillating frequency should set between 100kHz and 1000kHz.(Only J version)                  |

| PG             | 5      | 6      | Power Good pin. An open drain output that goes high impedance when the FB                     |

|                | 5      | 0      | pin voltage is stable around $\pm 15\%$ .                                                     |

|                |        |        | Standby control pin                                                                           |

|                |        |        | It is internally pulled down with 500k $\Omega$ . Normal operation at the time of high level. |

| EN/SYNC        | 6      | 7      | Standby Mode at the time of low level or OPEN.                                                |

|                |        |        | Moreover, it operates by inputting clock signal at the oscillatory frequency that             |

|                |        |        | synchronized with the input signal.                                                           |

| N.C.           | 7      | -      | Non connection(Only C version)                                                                |

| V <sup>+</sup> | 8      | 8      | Power supply pin                                                                              |

| Exposed<br>PAD | -      | -      | Connect to GND                                                                                |

• *New Japan Radio Co., Ltd.* • www.njr.com

# ■MARK INFORMATION

### **■ORDERING INFORMATION**

| PART NUMBER       | PACKAGE<br>OUTLINE | Oscillating<br>Frequency | RoHS | HALOGEN-<br>FREE | TERMINAL<br>FINISH | MARKING | WEIGHT<br>(mg) | MOQ<br>(pcs) |

|-------------------|--------------------|--------------------------|------|------------------|--------------------|---------|----------------|--------------|

| NJW4196GM1-C(TE1) | HSOP8              | Fixed                    | yes  | yes              | Sn100%             | 4196C   | 81             | 3000         |

| NJW4196GM1-J(TE1) | HSOP8              | Adjustable               | yes  | yes              | Sn100%             | 4196J   | 81             | 3000         |

# ■ABSOLUTE MAXIMUM RATINGS

| PARAMETER                   | SYMBOL               | RATINGS                                  | UNIT |  |

|-----------------------------|----------------------|------------------------------------------|------|--|

| Supply Voltage              | $V^{+}$              | -0.3 to +45                              | V    |  |

| V⁺- SW pin Voltage          | V <sub>V-SW</sub>    | +45                                      | V    |  |

| FB pin Voltage              | V <sub>FB</sub>      | -0.3 to +6                               | V    |  |

| PG pin Voltage              | V <sub>PG</sub>      | -0.3 to +6                               | V    |  |

| EN/SYNC pin Voltage         | V <sub>EN/SYNC</sub> | -0.3 to +45                              | V    |  |

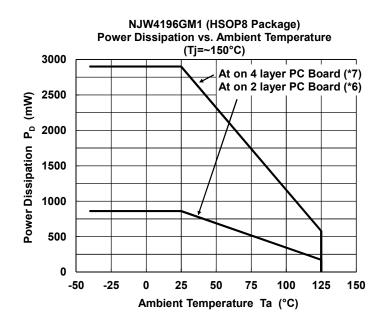

| Power Dissipation (Ta=25°C) | ſ                    | (2 Layer / 4 Layer)                      |      |  |

| HSOP8                       | PD                   | 860 <sup>(1)</sup> / 2900 <sup>(2)</sup> | mW   |  |

| Junction Temperature        | Tj                   | -40 to +150                              | °C   |  |

| Operating Temperature       | T <sub>opr</sub>     | -40 to +125                              | °C   |  |

| Storage Temperature         | T <sub>stg</sub>     | -50 to +150                              | С°   |  |

(1): Mounted on glass epoxy board. (76.2×114.3×1.6mm:based on EIA/JDEC standard, 2Layers)

(2): Mounted on glass epoxy board. (76.2×114.3×1.6mm:based on EIA/JDEC standard, 4Layers)

(For 4Layers: Applying 74.2×74.2mm inner Cu area and a thermal via hole to a board based on JEDEC standard JESD51-5)

Depending on conditions of the application, NJW4196 may not apply a max output current of it by a limit of the power consumption.

# ■RECOMMENDED OPERATING CONDITIONS

| PARAMETER                            | SYMBOL            | RATINGS                                                                                  | UNIT |

|--------------------------------------|-------------------|------------------------------------------------------------------------------------------|------|

| Supply Voltage                       | V <sup>+</sup>    | 4.45 to 40                                                                               | V    |

| PG pin Voltage                       | V <sub>PG</sub>   | 0 to 5.5                                                                                 | V    |

| Timing Resistor <sup>(3)</sup>       | R <sub>T</sub>    | 10 to 120                                                                                | kΩ   |

| Oscillating Frequency <sup>(3)</sup> | f <sub>OSC</sub>  | 100 to 1000                                                                              | kHz  |

| External Clock Input Range           | f <sub>SYNC</sub> | C ver. 440 to 600<br>J ver :f <sub>osc</sub> x 0.9(250kHz min.) to f <sub>osc</sub> x1.3 | kHz  |

(3): Apply only the J version.

New Japan Radio Co., Ltd. -www.njr.com

# ■ELECTRICAL CHARACTERISTICS

| PARAMETER                                                                                                                                              | SYMBOL                                                                                       | TEST CONDITION                               | MIN.               | TYP.                | MAX.                            | UNIT                     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------|--------------------|---------------------|---------------------------------|--------------------------|

| FARAIVIETER                                                                                                                                            | STNDOL                                                                                       | TEST CONDITION                               | IVIIIN.            | ITF.                | IVIAA.                          | UNIT                     |

| Under Voltage Lockout B                                                                                                                                | lock                                                                                         |                                              |                    |                     |                                 |                          |

| ON Threshold Voltage                                                                                                                                   | $V_{T_ON}$                                                                                   | $V^{+}=L \rightarrow H$                      | 4.05               | 4.25                | 4.45                            | V                        |

| OFF Threshold Voltage                                                                                                                                  |                                                                                              | $V^{\dagger} = H \rightarrow L$              | 4.0                | 4.15                | 4.3                             | V                        |

| Hysteresis Voltage                                                                                                                                     | V <sub>HYS</sub>                                                                             |                                              | 70                 | 100                 | -                               | mV                       |

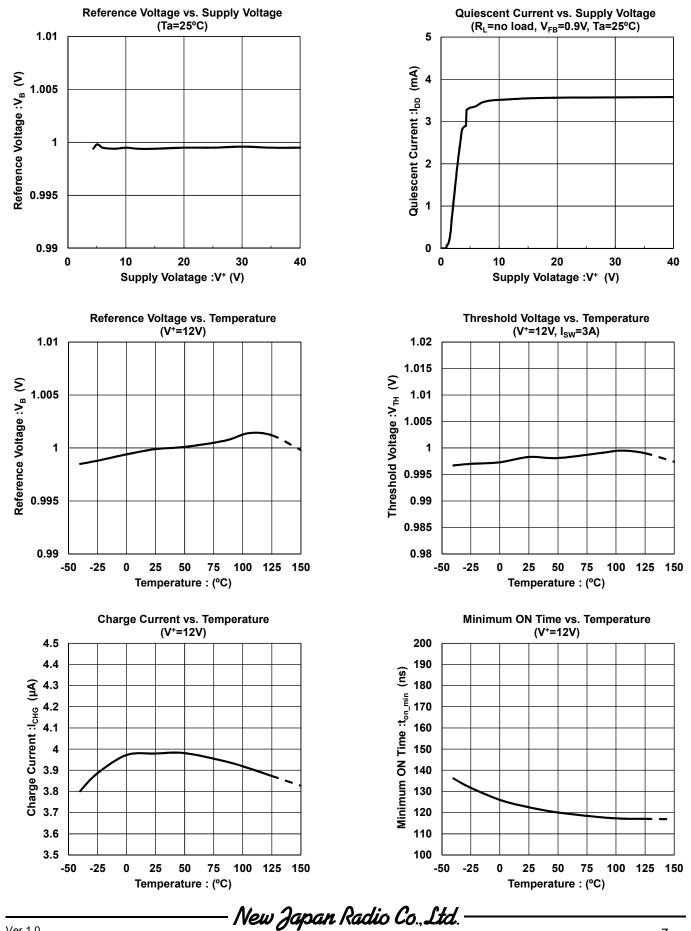

| Soft Start Block                                                                                                                                       |                                                                                              |                                              |                    |                     |                                 |                          |

| Charge Current                                                                                                                                         | I <sub>CHG</sub>                                                                             |                                              | 3.5                | 4.0                 | 4.5                             | μA                       |

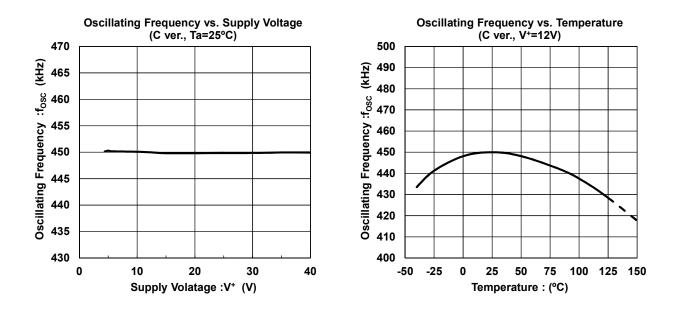

| Oscillator Block                                                                                                                                       |                                                                                              |                                              |                    |                     |                                 |                          |

|                                                                                                                                                        | f <sub>OSC_C</sub>                                                                           | C version <sup>(4)</sup>                     | 405                | 450                 | 495                             | kHz                      |

| Oscillating Frequency                                                                                                                                  | f <sub>OSC_J</sub>                                                                           | J version, $R_T$ =39k $\Omega^{(5)}$         | 270                | 300                 | 330                             | kHz                      |

| Oscillating Frequency<br>deviation (Supply voltage)                                                                                                    | f <sub>DV</sub>                                                                              | V <sup>+</sup> =4.45V to 40V                 | -                  | 1                   | -                               | %                        |

| Oscillating Frequency<br>deviation (Temperature)                                                                                                       | f <sub>DT</sub>                                                                              | Ta=-40°C to +85°C                            | -                  | 5                   | -                               | %                        |

| (4): Apply only the C ver.                                                                                                                             |                                                                                              |                                              |                    |                     |                                 |                          |

| (5): Apply only the J ver.                                                                                                                             |                                                                                              |                                              |                    |                     |                                 |                          |

| Buffer Block                                                                                                                                           |                                                                                              |                                              |                    |                     |                                 |                          |

|                                                                                                                                                        |                                                                                              |                                              |                    |                     |                                 |                          |

| Reference Voltage                                                                                                                                      | V <sub>B</sub>                                                                               |                                              | -1.0%              | 1                   | +1.0%                           | V                        |

| ų.                                                                                                                                                     | V <sub>B</sub><br>V <sub>TH</sub>                                                            | I <sub>SW</sub> =3A                          | -1.0%              | 1                   | +1.0%<br>+2.0%                  | V<br>V                   |

| Reference Voltage<br>Threshold Voltage<br>Input Bias Current                                                                                           |                                                                                              | I <sub>SW</sub> =3A                          |                    |                     |                                 |                          |

| Threshold Voltage                                                                                                                                      | V <sub>TH</sub>                                                                              | I <sub>SW</sub> =3A                          | -2.0%              | 1                   | +2.0%                           | V                        |

| Threshold Voltage<br>Input Bias Current<br>PWM Comparate Block                                                                                         | V <sub>TH</sub>                                                                              | I <sub>SW</sub> =3A<br>V <sub>FB</sub> =0.9V | -2.0%              | 1                   | +2.0%                           | V                        |

| Threshold Voltage<br>Input Bias Current<br>PWM Comparate Block<br>Maximum Duty Cycle                                                                   | V <sub>TH</sub><br>I <sub>B</sub>                                                            |                                              | -2.0%<br>-0.1      | -                   | +2.0%                           | V<br>µA                  |

| Threshold Voltage<br>Input Bias Current                                                                                                                | V <sub>TH</sub><br>I <sub>B</sub><br>M <sub>AX</sub> D <sub>UTY</sub>                        |                                              | -2.0%<br>-0.1      | -                   | +2.0%<br>0.1<br>100             | ν<br>μΑ<br>%             |

| Threshold Voltage<br>Input Bias Current<br>PWM Comparate Block<br>Maximum Duty Cycle<br>Minimum ON Time                                                | V <sub>TH</sub><br>I <sub>B</sub><br>M <sub>AX</sub> D <sub>UTY</sub>                        |                                              | -2.0%<br>-0.1      | -                   | +2.0%<br>0.1<br>100             | ν<br>μΑ<br>%             |

| Threshold Voltage<br>Input Bias Current<br>PWM Comparate Block<br>Maximum Duty Cycle<br>Minimum ON Time<br>OCP Block                                   | V <sub>TH</sub><br>I <sub>B</sub><br>M <sub>AX</sub> D <sub>UTY</sub><br>t <sub>ON-min</sub> |                                              | -2.0%<br>-0.1      | 1<br>-<br>-<br>125  | +2.0%<br>0.1<br>100<br>185      | V<br>μA<br>%<br>ns       |

| Threshold Voltage<br>Input Bias Current<br>PWM Comparate Block<br>Maximum Duty Cycle<br>Minimum ON Time<br>OCP Block<br>COOL DOWN Time<br>Output Block | V <sub>TH</sub><br>I <sub>B</sub><br>M <sub>AX</sub> D <sub>UTY</sub><br>t <sub>ON-min</sub> |                                              | -2.0%<br>-0.1      | 1<br>-<br>-<br>125  | +2.0%<br>0.1<br>100<br>185      | V<br>μA<br>%<br>ns       |

| Threshold Voltage<br>Input Bias Current<br>PWM Comparate Block<br>Maximum Duty Cycle<br>Minimum ON Time<br>OCP Block<br>COOL DOWN Time                 | V <sub>TH</sub><br>I <sub>B</sub><br>M <sub>AX</sub> D <sub>UTY</sub><br>t <sub>ON-min</sub> | V <sub>FB</sub> =0.9V                        | -2.0%<br>-0.1<br>- | 1<br>-<br>125<br>75 | +2.0%<br>0.1<br>100<br>185<br>- | V<br>μA<br>%<br>ns<br>ms |

- *New Japan Radio Co*.,*Ltd*. — www.njr.com

# ■ELECTRICAL CHARACTERISTICS

| Unless otherwise noted, $V^+=V_{EN,SYNC}=12V$ , ( $R_T=39k\Omega$ : J version only), Ta=25°C |                                 |                                          |      |      |         |      |

|----------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------|------|------|---------|------|

| PARAMETER                                                                                    | SYMBOL                          | TEST CONDITION                           | MIN. | TYP. | MAX.    | UNIT |

| Standby Control / Sync Block                                                                 |                                 |                                          |      |      |         |      |

| EN/SYNC pin<br>High Threshold Voltage                                                        | V <sub>THH_EN/SYNC</sub>        | $V_{\text{EN/SYNC}}$ = L $\rightarrow$ H | 1.6  | -    | $V^{*}$ | V    |

| EN/SYNC pin<br>Low Threshold Voltage                                                         | $V_{\text{THL}\_\text{ENSYNC}}$ | $V_{\text{EN/SYNC}}$ = H $\rightarrow$ L | 0    | -    | 0.5     | V    |

| Input Bias Current<br>(EN/SYNC pin)                                                          | I <sub>EN/SYNC</sub>            | V <sub>EN/SYNC</sub> =12V                | -    | 235  | 340     | μA   |

| Power Good Block                                                                             |                                 |                                          |      |      |         |      |

| High Level<br>Detection Voltage                                                              | $V_{\text{THH}\_\text{PG}}$     | Measured at FB pin                       | 110  | 115  | 120     | %    |

| Low Level<br>Detection Voltage                                                               | $V_{\text{THL}\_\text{PG}}$     | Measured at FB pin                       | 80   | 85   | 90      | %    |

| Hysteresis Region                                                                            | V <sub>HYS_PG</sub>             |                                          | -    | 2    | -       | %    |

| Power Good<br>ON Resistance                                                                  | $R_{ON_{PG}}$                   | I <sub>PG</sub> =10mA                    | -    | 45   | 60      | Ω    |

| Leak Current at<br>OFF State                                                                 | I <sub>LEAK_PG</sub>            | V <sub>PG</sub> =6V                      | -    | -    | 0.1     | μA   |

**General Characteristics**

| Quiescent Current | I <sub>DD</sub>     | R <sub>L</sub> =no load, V <sub>FB</sub> =0.9V | - | 3.5 | 4.2 | mA |

|-------------------|---------------------|------------------------------------------------|---|-----|-----|----|

| Standby Current   | I <sub>DD_STB</sub> | V <sub>EN/SYNC</sub> =0V                       | - | -   | 3   | μA |

- *New Japan Radio Co*.,*Ltd*. — www.njr.com

# ■THERMAL CHARACTERISTICS

| PARAMETER                                             | SYMBOL | VALUE                                   | UNIT  |

|-------------------------------------------------------|--------|-----------------------------------------|-------|

| Junction-to-ambient<br>thermal resistance             | θja    | 145 <sup>(6)</sup><br>43 <sup>(7)</sup> | °C /W |

| Junction-to-Top of package characterization parameter | ψjt    | 28 <sup>(6)</sup><br>12 <sup>(7)</sup>  | °C /W |

(6): Mounted on glass epoxy board. (76.2×114.3×1.6mm:based on EIA/JDEC standard, 2Layers)

(7): Mounted on glass epoxy board. (76.2×114.3×1.6mm:based on EIA/JDEC standard, 4Layers)

(For 4Layers: Applying 74.2×74.2mm inner Cu area and a thermal via hole to a board based on JEDEC standard JESD51-5)

# ■POWER DISSIPATION vs. AMBIENT TEMPERATURE

New Japan Radio Co., Ltd. -www.njr.com

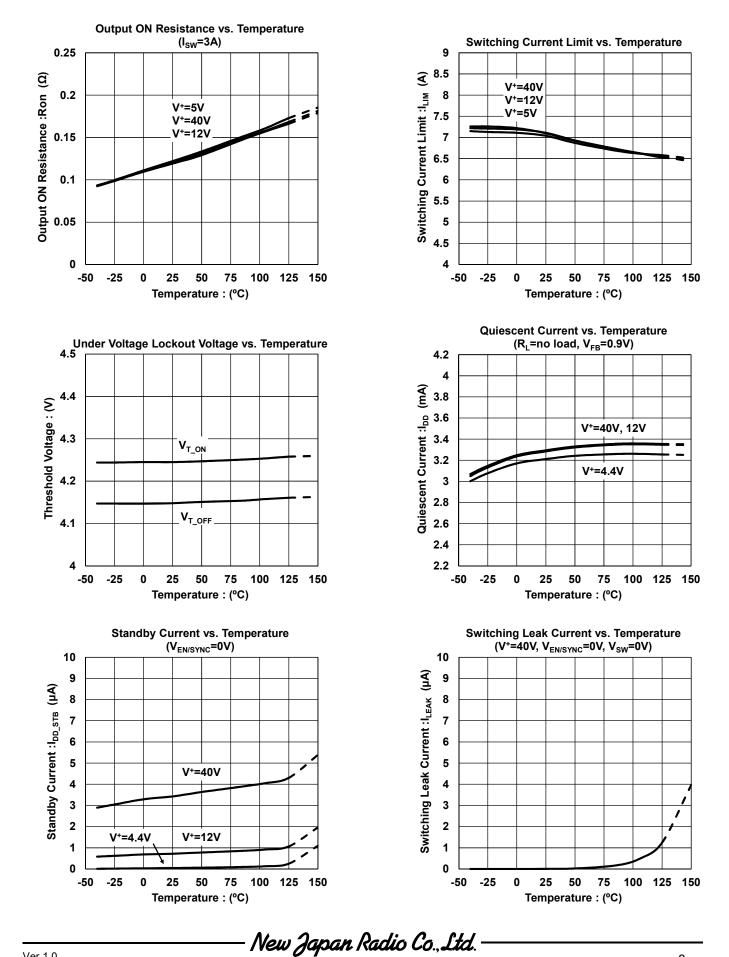

# **TYPICAL CHARACTERISTICS**

- 7 -

www.njr.com

New Japan Radio Co., Ltd. www.njr.com

# ■DESCRIPTION OF BLOCK FEATURES

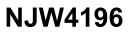

### Power MOSFET (SW Output Section)

The power is stored in the inductor by the switch operation of built-in power MOSFET. The output current is limited to 5A(min.) by overcurrent protection function. In case of buck converter, the forward direction bias voltage is generated with inductance current that flows into the external regenerative diode when MOSFET is turned off.

Although the SW pin accept a voltage between the V<sup>+</sup> pin and the SW pin up to +45V, use a Schottky diode that has low saturation voltage.

### • Power Supply, GND pin ( $V^{\dagger}$ and GND)

In line with switching element drive, current flows into the IC according to frequency. If the power supply impedance provided to the power supply circuit is high, it will not be possible to take advantage of IC performance due to input voltage fluctuation. Therefore insert a bypass capacitor close to the  $V^+$  pin – the GND pin connection in order to lower high frequency impedance.

### Under Voltage Lockout (UVLO)

The UVLO is released above ON Threshold Voltage (4.25V typ.) and IC operation starts. Then, supply voltage decrease below OFF Threshold Voltage (4.15V typ.), IC stops operate because the UVLO circuit. There is 100mV(typ.) width hysteresis voltage between detect and release.

Hysteresis prevents the malfunction near the UVLO threshold voltage.

### Soft Start Function (Soft Start)

The output voltage of the converter gradually rises to a set value by the soft start function. The soft start time is adjustable by the capacitor  $C_{SS}$  of the SS pin.

$$t_{ss} = C_{ss} \times \frac{1.0}{I_{chg}} [s]$$

I<sub>CHG</sub>: Soft Start Block Charge Current

When switching stopped by standby, UVLO, Hiccup by the OCP and TSD(Thermal Shut Down), NJW4196 discharges the capacitor of the SS pin.

When the rebooting, output voltage raises again with soft start.

New Japan Radio Co., Ltd.

www.njr.com

### DESCRIPTION OF BLOCK FEATURES (Continued)

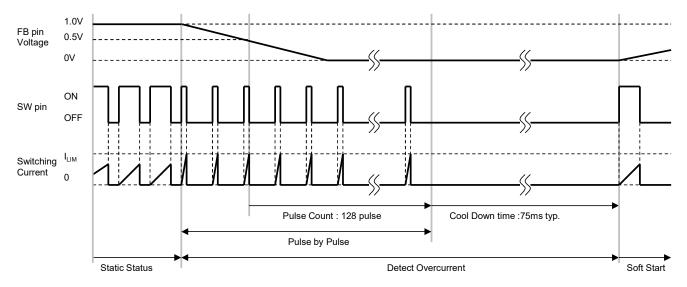

• Over Current Protection Circuit (OCP)

NJW4196 contains hiccup type over current protection(OCP). The hiccup OCP circuit is able to decrease heat generation at the overload.

If a current exceeding ILIM flows in the built-in power MOSFET, the power MOSFET is turned off by the OCP, and the switching operation is resumed at next cycle.

If the overcurrent detection continues for 128 pulses when the FB pin voltage is 0.5V or less, the switching operation stops.

When the FB pin voltage is 0.5V or lower(less), the switching operation stops after the overcurrent detection continued 128 pulses.

Then, after a cool-down time of about 75ms typ., restart with soft start.

Fig. 1. Timing Chart at Over Current Detection

### Thermal Shutdown Function (TSD)

When Junction temperature exceeds the 165°C\*, thermal shutdown(TSD) circuit function stops SW function. When junction temperature decreases to 145°C\* or less, SW operation returns with soft start operation.

The TSD circuit is preliminary function to prevent malfunctioning of IC at the high junction temperature and is not intended to compensate for improper thermal design. It is recommended to operate within the IC junction temperature range (up to +150 °C).\* Design value

# Standby Function

The NJW4196 stops the operating and becomes standby status when the EN/SYNC pin becomes less than 0.5V. The EN/SYNC pin internally pulls down with 500k $\Omega$ , therefore the NJW4196 becomes standby mode when the EN/SYNC pin is OPEN. When not using the standby function, connect the EN / SYNC pin to V<sup>+</sup>.

New Japan Radio Co., Ltd.

# DESCRIPTION OF BLOCK FEATURES (Continued)

# External Clock Synchronization

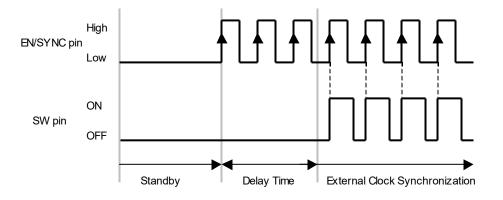

By inputting a square wave to EN/SYNC pin, can be synchronized to an external clock frequency. The square wave must meet the specifications in Table 1.

Table 1. The input square wave to an EN/SYNC pin.

|                 | C version                  | J version                              |  |  |

|-----------------|----------------------------|----------------------------------------|--|--|

|                 | (f <sub>OSC</sub> =450kHz) | (f <sub>OSC</sub> =100k to 1000kHz)    |  |  |

| Input Fraguanay | 440kHz to                  | f <sub>OSC</sub> x 0.9(250kHz min.) to |  |  |

| Input Frequency | 600kHz                     | f <sub>OSC</sub> x 1.3                 |  |  |

| Duty Cycle      | 25% to 75%                 | 40% to 60%                             |  |  |

|                 | 1.6V or more at High level |                                        |  |  |

| Voltage swing   | 0.5V or                    | less at Low level                      |  |  |

Switching operation during external synchronization is triggered by the rising edge of the input signal.

In the standby state and switching between asynchronous operation and external synchronous operation, it is set to delay time of 30µs to prevent malfunction. (Fig. 2.)

Fig. 2. Switching Operation by External Synchronized Clock

Power Good Function

It monitors the output status and outputs a signal from PG pin that internally connected to open drain MOSFET.

The PG pin goes high impedance when the FB pin voltage is stable around reference voltage  $1.0V\pm15\%$ (typ.) When the FB pin voltage is out of the range of  $1.0V\pm15\%$ , the PG pin goes low.

In order to prevent malfunction of the power good output, it is set to 2.0% typ. of hysteresis and a delay time of 20µs-30µs for the FB pin voltage changes.

New Japan Radio Co., Ltd.

Application Information

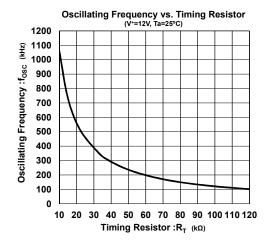

### Oscillating Frequency Setting

When the switching frequency is high, the application can use a small inductor and capacitor. However, it should be considered reducing application efficiency and limiting minimum ON time.

The J version of NJW4196 sets the oscillating frequency by connecting a resistor between the RT pin and GND.

Figure 3 shows the oscillating frequency vs. timing resistance characteristics. Set the oscillation frequency between 100kHz and 1000kHz.

In addition, since the minimum ON time ( $t_{ON-min}$ ) of NJW4196 is set to 125ns typ., It is necessary to select an oscillating frequency at which the ON time of the buck converter circuit is 125ns typ. or more.

The ON time of the buck converter circuit is determined by the following equation.

$$ton = \frac{V_{OUT}}{V_{IN} \times f_{OSC}} \left[ s \right]$$

Fig.3. Oscillating frequency vs. timing resistor

New Japan Radio Co., Ltd.

Application Information (Continued)

Inductors

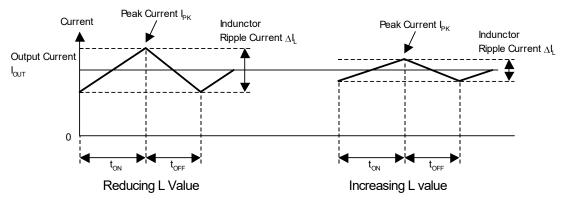

Since large current flows through the inductor, it must have a current capability that does not saturate. In case of NJW4196, optimized inductor value is determined by the input voltage and output voltage.

As the L value decreases, the peak current for the output current increases and conversion efficiency tends to decrease. (Fig. 4.) Also note that the output current is limited so that the overcurrent limit is not exceeded. The peak current is decided the following equation.

$$\Delta I_{L} = \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{L \times V_{IN} \times f_{OSC}} [A]$$

$$lpk = l_{OUT} + \frac{\Delta l_{L}}{2} [A]$$

The optimum value varies depending on the application specifications, parts, etc., so make fine adjustments with the actual machine.

Fig. 4. Inductor Current State Transition (Continuous Conduction Mode)

New Japan Radio Co., Ltd.

# Application Information (Continued)

Input Capacitor

In the input section of switching regulator, flows transient current according to oscillation frequency. If the power supply impedance is large, the input voltage will fluctuate and the NJW4196 may not deliver good performance.

Therefore, insert the input capacitor as close to the IC as possible. A ceramic capacitor is the optimal for input capacitor.

The effective input current can be calculated by the following equation.

$$I_{\text{RMS}} = I_{\text{OUT}} \times \frac{\sqrt{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}}{V_{\text{IN}}} [A]$$

In the above equation, the maximum current is obtained when  $V_{IN} = 2 \times V_{OUT}$ , and the result in this case is

$I_{\text{RMS}} = I_{\text{OUT}(\text{MAX})} \div 2.$

When selecting the input capacitor, use one with sufficient margin after evaluation.

Output Capacitor

An output capacitor stores power from the inductor, and stabilizes voltage provided to the output.

NJW4196 corresponds to a low ESR (Equivalent Series Resistance) output capacitor, so the ceramic capacitor is the optimal for compensation.

When selecting an output capacitor, it is necessary to consider the ESR characteristics, ripple current and maximum voltage. If it is a low ESR type capacitor, the ripple voltage can be lowered.

The ripple voltage can be calculated by the following equation.

$$V_{\text{ripple}(p-p)} = \Delta I_{\text{L}} \times \left( \text{ESR} + \frac{1}{8 \times f_{\text{OSC}} \times C_{\text{OUT}}} \right) [V]$$

The effective ripple current that flows in a capacitor (I<sub>rms</sub>) is calculated by the following equation.

$$I_{\rm rms} = \frac{\Delta I_{\rm L}}{2\sqrt{3}} \, [{\rm Arms}]$$

Since a ceramic capacitor capacitance decreases due to DC voltage application or temperature change, check the characteristics with a spec sheet.

New Japan Radio Co., Ltd. www.njr.com

Application Information (Continued)

Catch Diode

When the power MOSFET is in OFF cycle, the power stored in the inductor flows to output capacitor through the catch diode. Therefore, a current corresponding to the load current flows through the diode every cycle. Because diode's forward saturation voltage and current accumulation cause power loss, a Schottky Barrier Diode (SBD) which has a low forward saturation voltage is ideal.

A SBD also has a short reverse recovery time. If the reverse recovery time becomes longer, through current will flow at the power MOSFET switches to ON cycle from OFF cycle. This current may reduce efficiency and cause noise.

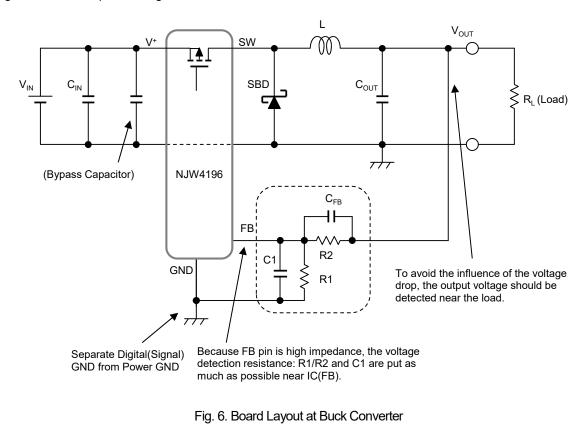

# • Setting Output Voltage, Noise Bypass Capacitor

The output voltage is determined by the relative resistances of R1 and R2. The current flowing through R1 and R2 should be large enough to ignore the bias current.

$$V_{\text{OUT}} = \left(\frac{R2}{R1} + 1\right) \times V_{\text{B}} [V]$$

Connect C1=100pF to 1,000pF to an FB pin as a noise bypass capacitor.

R2 and  $C_{FB}$  form a zero ( $f_{Z1}$ ) and compensate for the phase of the switching regulator. The pole generated by the noise bypass capacitor is compensated by R2 and  $C_{FB}$ .

$$f_{P} = \frac{1}{2 \times \pi \times R1 \times C1} [Hz]$$

$$f_{Z1} = \frac{1}{2 \times \pi \times R2 \times C_{FB}} [Hz]$$

Adjust with the actual machine so that it becomes  $0.5 < \frac{f_{Z1}}{f_{P}} < 2.5$  .

New Japan Radio Co., Ltd.

www.njr.com

# Application Information (Continued)

# Board Layout

The switching regulator supplies power to the load by charging and discharging the inductor

In the switching regulator application, because the current flow corresponds to the oscillation frequency, the substrate (PCB) layout becomes an important.

You should attempt the transition voltage decrease by making a current loop area minimize as much as possible. Therefore, you should make a current flowing line thick and short as much as possible. Fig.5. shows a current loop at buck converter. Especially, should lay out high priority the loop of  $C_{IN}$ -SW-SBD that occurs rapid current change in the switching. It is effective in reducing noise spikes caused by parasitic inductance.

Fig. 5. Current Loop at Buck Converter

Concerning the GND line, it is preferred to separate the power system and the signal system, and use single ground point.

The voltage sensing feedback line should be as far away as possible from the inductance. Because this line has high impedance, it is laid out to avoid the influence noise caused by flux leaked from the inductance.

Fig. 6. shows example of wiring at buck converter.

# Calculation of Package Power

A lot of the power consumption of buck converter occurs from the internal switching element (Power MOSFET). Power consumption of NJW4196 is roughly estimated as follows.

| Input Power:               | $P_{IN} = V_{IN} \times I_{IN}  [W]$                       |

|----------------------------|------------------------------------------------------------|

| Output Power:              | $P_{OUT} = V_{OUT} \times I_{OUT}$ [W]                     |

| Diode Loss:                | $P_{DIODE} = V_F \times I_{L(avg)} \times OFF \ duty  [W]$ |

| NJW4196 Power Consumption: | $P_{LOSS} = P_{IN} - P_{OUT} - P_{DIODE}  [W]$             |

Where:

| V <sub>IN</sub>  | : Input Voltage for Converter        | I <sub>IN</sub>     | : Input Current for Converter |

|------------------|--------------------------------------|---------------------|-------------------------------|

| V <sub>OUT</sub> | : Output Voltage of Converter        | I <sub>OUT</sub>    | : Output Current of Converter |

| V <sub>F</sub>   | : Diode's Forward Saturation Voltage | I <sub>L(avg)</sub> | : Inductor Average Current    |

| OFF duty         | : Switch OFF Duty                    |                     |                               |

Efficiency  $(\eta)$  is calculated as follows.

$\eta = (P_{\text{OUT}} \div P_{\text{IN}}) \times 100 \text{ [\%]}$

You should consider temperature derating to the calculated power consumption: P<sub>D</sub>.

You should design power consumption in rated range referring to the power dissipation vs. ambient temperature characteristics.

New Japan Radio Co., Ltd. -www.njr.com

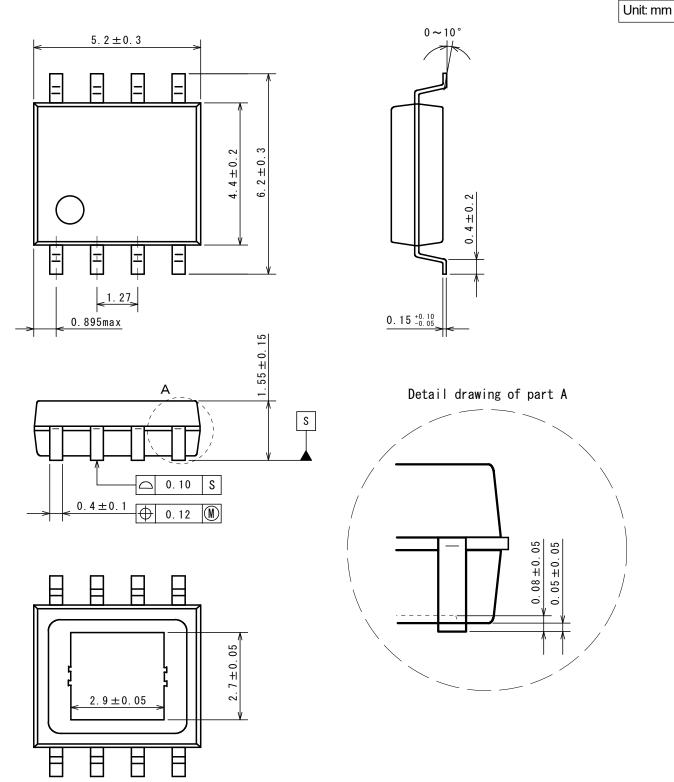

# NJW4196

# HSOP8

# ■PACKAGE OUTLINE

New Japan Radio Co., Ltd.

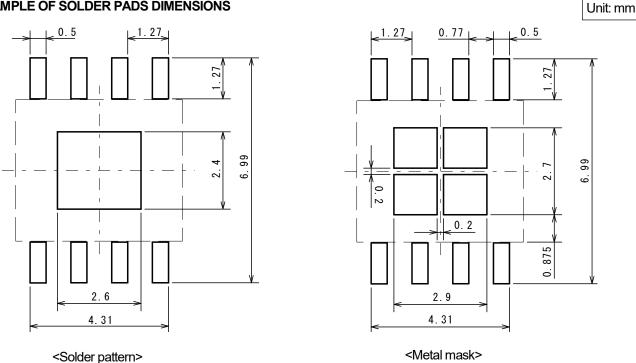

# NJW4196

**HSOP8**

# ■EXAMPLE OF SOLDER PADS DIMENSIONS

#### <Instructions for mounting>

Please note the following points when you mount HSOP-8 package IC because there is a standoff on the backside electrode.

(1) Temperature profile of lead and backside electrode.

It is necessary that both re-flow temperature profile of lead and backside electrode are higher than preset temperature. When solder wet temperature is lower than lead/backside electrode temperature, there is possibility of defect mounting.

(2) Design of foot pattern / metal mask

Metal mask thickness of solder pattern print is more than 0.13mm.

(3) Solder paste

The mounting was evaluated with following solder paste, foot pattern and metal mask.

Because mounting might be greatly different according to the manufacturer and the product number even if the solder composition is the same.

We will strongly recommend to evaluate mounting previously with using foot pattern, metal mask and solder paste.

| Solder paste composition | Sn37Pb (Senju Metal Industry Co., Ltd: OZ7053-340F-C)         |

|--------------------------|---------------------------------------------------------------|

|                          | Sn3Ag0.5Cu (Senju Metal Industry Co., Ltd: M705-GRN350-32-11) |

New Japan Radio Co., Ltd. www.njr.com

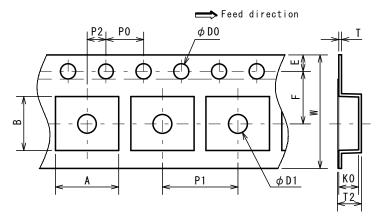

# NJW4196

# **HSOP8**

Unit: mm

■PACKING SPEC

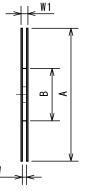

### TAPING DIMENSIONS

**REEL DIMENSIONS**

| SYMBOL | DIMENSION | REMARKS |

|--------|-----------|---------|

| A      | 6.7±0.1   |         |

| В      | 5.55±0.1  |         |

| DO     | 1.55±0.05 |         |

| D1     | 2.05±0.05 |         |

| E      | 1.75±0.1  |         |

| F      | 5.5±0.05  |         |

| PO     | 4.0±0.1   |         |

| P1     | 8.0±0.1   |         |

| P2     | 2.0±0.05  |         |

| Т      | 0.3±0.05  |         |

| T2     | 2. 47     |         |

| К0     | 2.1±0.1   |         |

| W      | 12.0±0.2  |         |

| SYMBOL | DIMENSION |

|--------|-----------|

| Α      | φ330±2    |

| В      | φ 80±1    |

| С      | φ 13±0.2  |

| D      | φ 21±0.8  |

| E      | 2±0.5     |

| W      | 13.5±0.5  |

| W1     | 17.5±1    |

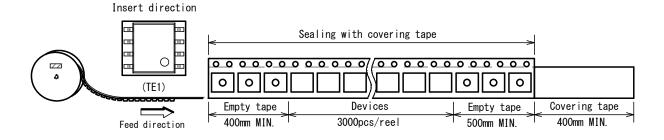

**TAPING STATE**

**PACKING STATE**

Label

EAE-D1006-000-02

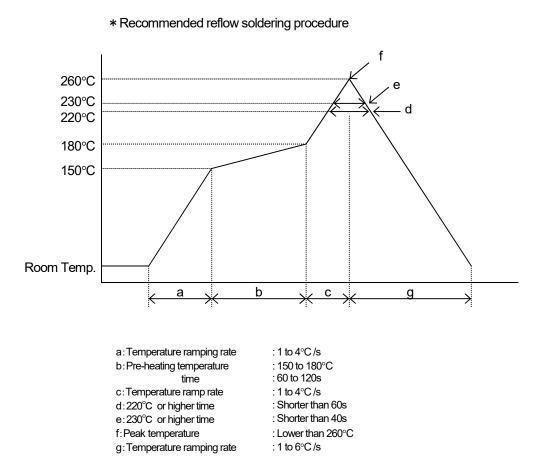

# ■RECOMMENDED MOUNTING METHOD

INFRARED REFLOW SOLDERING METHOD

The temperature indicates at the surface of mold package.

New Japan Radio Co., Ltd. -www.njr.com

# **REVISION HISTORY**

| Date          | Revision | Changes                             |

|---------------|----------|-------------------------------------|

| 29. Nov.2019. | Ver.1.0  | New Release C version and J version |

|               |          |                                     |

·New Japan Radio Co.,Ltd.—

# [CAUTION]

- NJR strives to produce reliable and high quality semiconductors. NJR's semiconductors are intended for specific applications 1. and require proper maintenance and handling. To enhance the performance and service of NJR's semiconductors, the devices, machinery or equipment into which they are integrated should undergo preventative maintenance and inspection at regularly scheduled intervals. Failure to properly maintain equipment and machinery incorporating these products can result in catastrophic system failures

- The specifications on this datasheet are only given for information without any guarantee as regards either mistakes or 2. omissions. The application circuits in this datasheet are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial property rights. All other trademarks mentioned herein are the property of their respective companies.

- To ensure the highest levels of reliability, NJR products must always be properly handled. 3. The introduction of external contaminants (e.g. dust, oil or cosmetics) can result in failures of semiconductor products.

- NJR offers a variety of semiconductor products intended for particular applications. It is important that you select the proper 4. component for your intended application. You may contact NJR's Sale's Office if you are uncertain about the products listed in this datasheet.

- 5. Special care is required in designing devices, machinery or equipment which demand high levels of reliability. This is particularly important when designing critical components or systems whose failure can foreseeably result in situations that could adversely affect health or safety. In designing such critical devices, equipment or machinery, careful consideration should be given to amongst other things, their safety design, fail-safe design, back-up and redundancy systems, and diffusion design.

- The products listed in this datasheet may not be appropriate for use in certain equipment where reliability is critical or where 6 the products may be subjected to extreme conditions. You should consult our sales office before using the products in any of the following types of equipment.

- · Aerospace Equipment

- · Equipment Used in the Deep Sea

- · Power Generator Control Equipment (Nuclear, steam, hydraulic, etc.)

- · Life Maintenance Medical Equipment

- · Fire Alarms / Intruder Detectors

- · Vehicle Control Equipment (Airplane, railroad, ship, etc.)

- · Various Safety Devices

- NJR's products have been designed and tested to function within controlled environmental conditions. Do not use products 7. under conditions that deviate from methods or applications specified in this datasheet. Failure to employ the products in the proper applications can lead to deterioration, destruction or failure of the products. NJR shall not be responsible for any bodily injury, fires or accident, property damage or any consequential damages resulting from misuse or misapplication of the products. The products are sold without warranty of any kind, either express or implied, including but not limited to any implied warranty of merchantability or fitness for a particular purpose.

- 8. Warning for handling Gallium and Arsenic (GaAs) Products (Applying to GaAs MMIC, Photo Reflector). These products use Gallium (Ga) and Arsenic (As) which are specified as poisonous chemicals by law. For the prevention of a hazard, do not burn, destroy, or process chemically to make them as gas or power. When the product is disposed of, please follow the related regulation and do not mix this with general industrial waste or household waste.

- The product specifications and descriptions listed in this datasheet are subject to change at any time, without notice. 9

New Japan Radio Co., Ltd. www.njr.com