## μPD48288209AF1 μPD48288218AF1 μPD48288236AF1

# 288M-BIT Low Latency DRAM Common I/O

R10DS0254EJ0101 Rev. 1.01 Jan. 15, 2016

## Description

The  $\mu$ PD48288209AF1 is a 33,554,432-word by 9 bit, the  $\mu$ PD48288218AF1 is a 16,777,216-word by 18 bit and the  $\mu$ PD48288236AF1 is a 8,388,608-word by 36 bit synchronous double data rate Low Latency RAM fabricated with advanced CMOS technology using one-transistor memory cell.

The  $\mu$ PD48288209AF1,  $\mu$ PD48288218AF1 and  $\mu$ PD48288236AF1 integrate unique synchronous peripheral circuitry and a burst counter. All input registers controlled by an input clock pair (CK and CK#) are latched on the positive edge of CK and CK#. These products are suitable for application which require synchronous operation, high speed, low voltage, high density and wide bit configuration.

#### **Specification**

• Density: 288M bit

• Organization

- Common I/O: 4M words x 9 bits x 8 banks

2M words x 18 bits x 8 banks

1M words x 36 bits x 8 banks

• Operating frequency: 533 / 400 / 300 MHz

• Interface: HSTL I/O

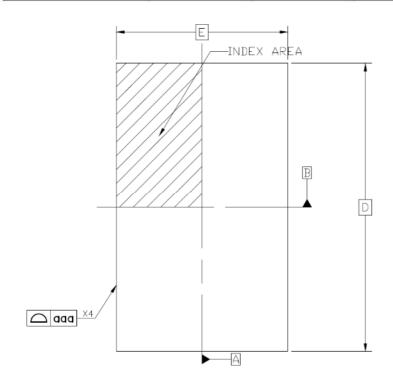

• Package: 144-pin FBGA

Package size: 18.5 x 11

- Lead free

Power supply

- 2.5 V VEXT

- 1.8 V V<sub>DD</sub>

- 1.5 V or 1.8 V VDDQ

• Refresh command

Auto Refresh

- 8192 cycle / 32 ms for each bank

- 64K cycle / 32 ms for total

$\bullet$  Operating case temperature : Tc=0 to  $95^{\circ}C$

#### **Features**

- SRAM-type interface

- Double-data-rate architecture

- PLL circuitry

• Cycle time: 1.875 ns @ trc = 15 ns

2.5 ns @  $t_{RC} = 15$  ns 2.5 ns @  $t_{RC} = 20$  ns 3.3 ns @  $t_{RC} = 20$  ns

- Non-multiplexed addresses

- Multiplexing option is available.

- Data mask for WRITE commands

- Differential input clocks (CK and CK#)

- Differential input data clocks (DK and DK#)

- Data valid signal (QVLD)

- Programmable burst length: 2 / 4 / 8 (x9 / x18 / x36)

- User programmable impedance output (25  $\Omega$  60  $\Omega$ )

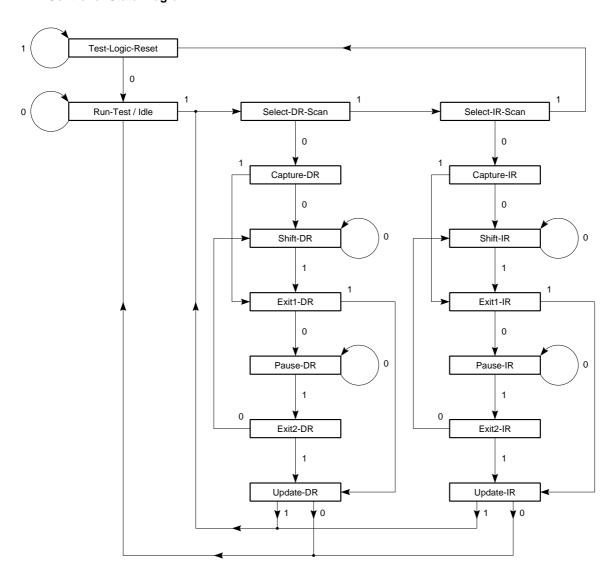

- JTAG boundary scan

## **Ordering Information**

| Part number              | Cycle<br>Time | Clock<br>Frequency |    | Organization<br>(word x bit) | Core Supply<br>Voltage<br>(V <sub>EXT</sub> ) | Core Supply<br>Voltage<br>(V <sub>DD</sub> ) | Output Supply<br>Voltage<br>(VDDQ) | Package     |

|--------------------------|---------------|--------------------|----|------------------------------|-----------------------------------------------|----------------------------------------------|------------------------------------|-------------|

|                          | ns            | MHz                | Ns |                              | V                                             | V                                            | V                                  |             |

| μPD48288209AF1-E24-DW1-A | 2.5           | 400                | 15 | 32 M x 9                     | 2.5 + 0.13                                    | 1.8 ± 0.1                                    | 1.5 ± 0.1                          | 144-pin     |

| μPD48288218AF1-E18-DW1-A | 1.875         | 533                | 15 | 16 M x 18                    | 2.5 – 0.12                                    |                                              | or                                 | FBGA        |

| μPD48288218AF1-E24-DW1-A | 2.5           | 400                | 15 |                              |                                               |                                              | 1.8 ± 0.1                          | (18.5 x 11) |

| μPD48288236AF1-E18-DW1-A | 1.875         | 533                | 15 | 8 M x 36                     |                                               |                                              |                                    | Lead-free   |

| μPD48288236AF1-E24-DW1-A | 2.5           | 400                | 15 |                              |                                               |                                              |                                    |             |

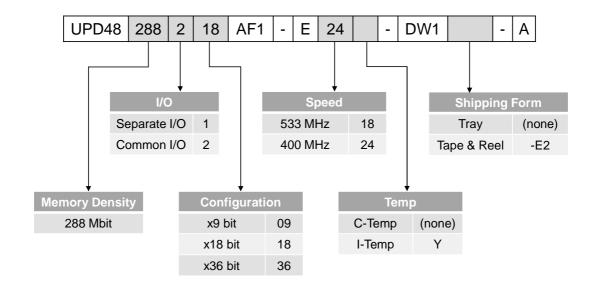

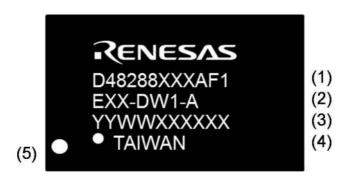

## **Part Number Definition**

Example) UPD48288218AF1-E24-DW1-A

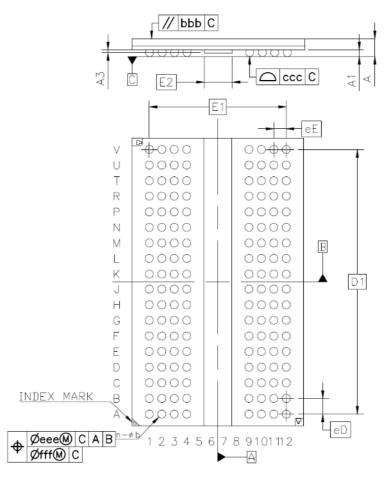

## **Pin Arrangement**

## 144-pin FBGA (18.5 x 11) (Top View) [Common I/O x9]

|   | 1               | 2                   | 3             | 4                      | 5 | 6 | 7 | 8 | 9                 | 10              | 11            | 12          |

|---|-----------------|---------------------|---------------|------------------------|---|---|---|---|-------------------|-----------------|---------------|-------------|

| Α | VREF            | Vss                 | VEXT          | Vss                    |   |   |   |   | Vss               | <b>V</b> EXT    | TMS           | тск         |

| В | V <sub>DD</sub> | Note 3<br>DNU       | Note 3<br>DNU | VssQ                   |   |   |   |   | VssQ              | DQ0             | Note 3<br>DNU | <b>V</b> DD |

| С | <b>V</b> TT     | Note 3<br>DNU       | Note 3<br>DNU | V <sub>DD</sub> Q      |   |   |   |   | V <sub>DD</sub> Q | DQ1             | Note 3<br>DNU | <b>V</b> TT |

| D | Note 1<br>(A22) | Note 3<br>DNU       | Note 3<br>DNU | VssQ                   |   |   |   |   | VssQ              | QK0#            | QK0           | Vss         |

| Ε | Note 1<br>(A21) | Note 3<br>DNU       | Note 3<br>DNU | $V_{DD}Q$              |   |   |   |   | V <sub>DD</sub> Q | DQ2             | Note 3<br>DNU | A20         |

| F | A5              | Note 3<br>DNU       | Note 3<br>DNU | VssQ                   |   |   |   |   | VssQ              | DQ3             | Note 3<br>DNU | QVLD        |

| G | A8              | <b>A6</b>           | A7            | <b>V</b> DD            |   |   |   |   | <b>V</b> DD       | A2              | <b>A</b> 1    | A0          |

| Н | BA2             | A9                  | Vss           | Vss                    |   |   |   |   | Vss               | Vss             | A4            | А3          |

| J | Note 2<br>NF    | Note 2<br><b>NF</b> | <b>V</b> DD   | <b>V</b> <sub>DD</sub> |   |   |   |   | <b>V</b> DD       | <b>V</b> DD     | BA0           | СК          |

| K | DK              | DK#                 | <b>V</b> DD   | <b>V</b> DD            |   |   |   |   | <b>V</b> DD       | V <sub>DD</sub> | BA1           | CK#         |

| L | REF#            | CS#                 | Vss           | Vss                    |   |   |   |   | Vss               | Vss             | A14           | A13         |

| M | WE#             | A16                 | A17           | <b>V</b> DD            |   |   |   |   | <b>V</b> DD       | A12             | A11           | A10         |

| N | A18             | Note 3<br>DNU       | Note 3<br>DNU | VssQ                   |   |   |   |   | VssQ              | DQ4             | Note 3<br>DNU | A19         |

| P | A15             | Note 3<br>DNU       | Note 3<br>DNU | V <sub>DD</sub> Q      |   |   |   |   | V <sub>DD</sub> Q | DQ5             | Note 3<br>DNU | DM          |

| R | Vss             | Note 3<br>DNU       | Note 3<br>DNU | VssQ                   |   |   |   |   | VssQ              | DQ6             | Note 3<br>DNU | Vss         |

| Т | <b>V</b> TT     | Note 3<br>DNU       | Note 3<br>DNU | V <sub>DD</sub> Q      |   |   |   |   | V <sub>DD</sub> Q | DQ7             | Note 3<br>DNU | VTT         |

| U | <b>V</b> DD     | Note 3<br>DNU       | Note 3<br>DNU | VssQ                   |   |   |   |   | VssQ              | DQ8             | Note 3<br>DNU | <b>V</b> DD |

| ٧ | VREF            | ZQ                  | <b>V</b> EXT  | Vss                    |   |   |   |   | Vss               | <b>V</b> EXT    | TDO           | TDI         |

- **Notes 1.** Reserved for future use. This signal is internally connected and has parasitic characteristics of an address input signal. This may optionally be connected to Vss, or left open.

- **2.** No function. This signal is internally connected and has parasitic characteristics of a clock input signal. This may optionally be connected to Vss, or left open.

- **3.** Do not use. This signal is internally connected and has parasitic characteristics of a I/O. This may optionally be connected to Vss, or left open.

| CK, CK#   | : Input clock             | TMS                | : IEEE 1149.1 Test input     |

|-----------|---------------------------|--------------------|------------------------------|

| CS#       | : Chip select             | TDI                | : IEEE 1149.1 Test input     |

| WE#       | : WRITE command           | TCK                | : IEEE 1149.1 Clock input    |

| REF#      | : Refresh command         | TDO                | : IEEE 1149.1 Test output    |

| A0-A20    | : Address inputs          | $V_{\text{REF}}$   | : HSTL input reference input |

| A21-A22   | : Reserved for the future | $V_{\text{EXT}}$   | : Power Supply               |

| BA0-BA2   | : Bank address input      | $V_{\text{DD}}$    | : Power Supply               |

| DQ0-DQ8   | : Data input/output       | $V_{\mathrm{DD}}Q$ | : DQ Power Supply            |

| DK, DK#   | : Input data clock        | $V_{ss}$           | : Ground                     |

| DM        | : Input data Mask         | VssQ               | : DQ Ground                  |

| QK0, QK0# | : Output data clock       | $V_{TT}$           | : Power Supply               |

| QVLD      | : Data Valid              | NF                 | : No function                |

|           |                           |                    |                              |

: Output impedance matching

# indicates active LOW signal.

: Do not use

ZQ

DNU

## **Pin Arrangement**

## 144-pin FBGA (18.5 x 11) (Top View) [Common I/O x18]

|   | 1               | 2                   | 3            | 4                    | 5 | 6 | 7 | 8 | 9                 | 10              | 11            | 12           |

|---|-----------------|---------------------|--------------|----------------------|---|---|---|---|-------------------|-----------------|---------------|--------------|

| Α | VREF            | Vss                 | <b>V</b> EXT | Vss                  |   |   |   |   | Vss               | <b>V</b> EXT    | TMS           | тск          |

| В | V <sub>DD</sub> | Note 3<br>DNU       | DQ4          | VssQ                 |   |   |   |   | VssQ              | DQ0             | Note 3<br>DNU | <b>V</b> DD  |

| С | VTT             | Note 3<br>DNU       | DQ5          | V <sub>DD</sub> Q    |   |   |   |   | $V_{DD}Q$         | DQ1             | Note 3<br>DNU | <b>V</b> TT  |

| D | Note 1<br>(A22) | Note 3<br>DNU       | DQ6          | VssQ                 |   |   |   |   | VssQ              | QK0#            | QK0           | Vss          |

| E | Note 1<br>(A21) | Note 3<br>DNU       | DQ7          | <b>V</b> DD <b>Q</b> |   |   |   |   | $V_{DD}Q$         | DQ2             | Note 3<br>DNU | Note 1 (A20) |

| F | A5              | Note 3<br>DNU       | DQ8          | VssQ                 |   |   |   |   | VssQ              | DQ3             | Note 3<br>DNU | QVLD         |

| G | A8              | A6                  | A7           | V <sub>DD</sub>      |   |   |   |   | <b>V</b> DD       | A2              | <b>A</b> 1    | A0           |

| Н | BA2             | Α9                  | Vss          | Vss                  |   |   |   |   | Vss               | Vss             | A4            | А3           |

| J | Note 2<br>NF    | Note 2<br><b>NF</b> | <b>V</b> DD  | V <sub>DD</sub>      |   |   |   |   | <b>V</b> DD       | V <sub>DD</sub> | BA0           | СК           |

| K | DK              | DK#                 | <b>V</b> DD  | V <sub>DD</sub>      |   |   |   |   | <b>V</b> DD       | V <sub>DD</sub> | BA1           | CK#          |

| L | REF#            | CS#                 | Vss          | Vss                  |   |   |   |   | Vss               | Vss             | A14           | A13          |

| M | WE#             | A16                 | A17          | V <sub>DD</sub>      |   |   |   |   | <b>V</b> DD       | A12             | A11           | A10          |

| N | A18             | Note 3<br>DNU       | DQ14         | VssQ                 |   |   |   |   | VssQ              | DQ9             | Note 3<br>DNU | A19          |

| Р | A15             | Note 3<br>DNU       | DQ15         | V <sub>DD</sub> Q    |   |   |   |   | V <sub>DD</sub> Q | DQ10            | Note 3<br>DNU | DM           |

| R | Vss             | QK1                 | QK1#         | VssQ                 |   |   |   |   | VssQ              | DQ11            | Note 3<br>DNU | Vss          |

| Т | <b>V</b> TT     | Note 3<br>DNU       | DQ16         | V <sub>DD</sub> Q    | - |   | _ |   | V <sub>DD</sub> Q | DQ12            | Note 3<br>DNU | <b>V</b> TT  |

| U | <b>V</b> DD     | Note 3<br>DNU       | DQ17         | VssQ                 |   |   |   |   | VssQ              | DQ13            | Note 3<br>DNU | <b>V</b> DD  |

| ٧ | VREF            | ZQ                  | <b>V</b> EXT | Vss                  |   |   |   |   | Vss               | <b>V</b> EXT    | TDO           | TDI          |

- **Notes 1.** Reserved for future use. This signal is internally connected and has parasitic characteristics of an address input signal. This may optionally be connected to Vss, or left open.

- **2.** No function. This signal is internally connected and has parasitic characteristics of a clock input signal. This may optionally be connected to Vss, or left open.

- **3.** Do not use. This signal is internally connected and has parasitic characteristics of a I/O. This may optionally be connected to Vss, or left open.

| CK, CK#            | : Input clock               | TMS                        | : IEEE 1149.1 Test input     |

|--------------------|-----------------------------|----------------------------|------------------------------|

| CS#                | : Chip select               | TDI                        | : IEEE 1149.1 Test input     |

| WE#                | : WRITE command             | TCK                        | : IEEE 1149.1 Clock input    |

| REF#               | : Refresh command           | TDO                        | : IEEE 1149.1 Test output    |

| A0-A19             | : Address inputs            | $V_{\text{REF}}$           | : HSTL input reference input |

| A20-A22            | : Reserved for the future   | $V_{\text{EXT}}$           | : Power Supply               |

| BA0-BA2            | : Bank address input        | $V_{\rm DD}$               | : Power Supply               |

| DQ0-DQ17           | : Data input/output         | $V_{\mathrm{DD}}Q$         | : DQ Power Supply            |

| DK, DK#            | : Input data clock          | $\mathbf{V}_{\mathbf{SS}}$ | : Ground                     |

| DM                 | : Input data Mask           | VssQ                       | : DQ Ground                  |

| QK0-QK1, QK0#-QK1# | : Output data clock         | $V_{\text{TT}}$            | : Power Supply               |

| QVLD               | : Data Valid                | NF                         | : No function                |

| ZQ                 | : Output impedance matching | DNU                        | : Do not use                 |

# indicates active LOW signal.

## **Pin Arrangement**

## 144-pin FBGA (18.5 x 11) (Top View) [Common I/O x36]

|   | 1               | 2         | 3               | 4                 | 5 | 6 | 7 | 8 | 9                               | 10              | 11         | 12              |

|---|-----------------|-----------|-----------------|-------------------|---|---|---|---|---------------------------------|-----------------|------------|-----------------|

| Α | VREF            | Vss       | <b>V</b> EXT    | Vss               |   |   |   |   | Vss                             | <b>V</b> EXT    | TMS        | TCK             |

| В | V <sub>DD</sub> | DQ8       | DQ9             | VssQ              |   |   |   |   | VssQ                            | DQ1             | DQ0        | <b>V</b> DD     |

| С | <b>V</b> TT     | DQ10      | DQ11            | V <sub>DD</sub> Q |   |   |   |   | <b>V</b> <sub>DD</sub> <b>Q</b> | DQ3             | DQ2        | <b>V</b> TT     |

| D | Note<br>(A22)   | DQ12      | DQ13            | VssQ              |   |   |   |   | VssQ                            | QK0#            | QK0        | Vss             |

| E | Note<br>(A21)   | DQ14      | DQ15            | V <sub>DD</sub> Q |   |   |   |   | V <sub>DD</sub> Q               | DQ5             | DQ4        | Note<br>(A20)   |

| F | A5              | DQ16      | DQ17            | VssQ              |   |   |   |   | VssQ                            | DQ7             | DQ6        | QVLD            |

| G | A8              | <b>A6</b> | A7              | V <sub>DD</sub>   |   |   |   |   | <b>V</b> DD                     | A2              | <b>A</b> 1 | Α0              |

| Н | BA2             | <b>A9</b> | Vss             | Vss               |   |   |   |   | Vss                             | Vss             | A4         | А3              |

| J | DK0             | DK0#      | V <sub>DD</sub> | V <sub>DD</sub>   |   |   |   |   | <b>V</b> DD                     | V <sub>DD</sub> | BA0        | СК              |

| K | DK1             | DK1#      | <b>V</b> DD     | V <sub>DD</sub>   |   |   |   |   | <b>V</b> DD                     | <b>V</b> DD     | BA1        | CK#             |

| L | REF#            | CS#       | Vss             | Vss               |   |   |   |   | Vss                             | Vss             | A14        | A13             |

| M | WE#             | A16       | A17             | V <sub>DD</sub>   |   |   |   |   | <b>V</b> DD                     | A12             | A11        | A10             |

| N | A18             | DQ24      | DQ25            | VssQ              |   |   |   |   | VssQ                            | DQ35            | DQ34       | Note<br>(A19)   |

| Р | A15             | DQ22      | DQ23            | V <sub>DD</sub> Q |   |   |   |   | V <sub>DD</sub> Q               | DQ33            | DQ32       | DM              |

| R | Vss             | QK1       | QK1#            | VssQ              |   |   |   |   | VssQ                            | DQ31            | DQ30       | Vss             |

| Т | VTT             | DQ20      | DQ21            | V <sub>DD</sub> Q |   |   |   |   | VDDQ                            | DQ29            | DQ28       | VTT             |

| U | V <sub>DD</sub> | DQ18      | DQ19            | VssQ              |   |   |   |   | VssQ                            | DQ27            | DQ26       | V <sub>DD</sub> |

| ٧ | <b>V</b> REF    | ZQ        | <b>V</b> EXT    | Vss               |   |   |   |   | Vss                             | <b>V</b> EXT    | TDO        | TDI             |

**Note** Reserved for future use. This signal is internally connected and has parasitic characteristics of an address input signal. This may optionally be connected to Vss, or left open.

| CK, CK# | : Input clock     | TMS          | : IEEE 1149.1 Test input     |

|---------|-------------------|--------------|------------------------------|

| CS#     | : Chip select     | TDI          | : IEEE 1149.1 Test input     |

| WE#     | : WRITE command   | TCK          | : IEEE 1149.1 Clock input    |

| REF#    | : Refresh command | TDO          | : IEEE 1149.1 Test output    |

| A0-A18  | : Address inputs  | $V_{ m REF}$ | : HSTL input reference input |

|         |                   |              |                              |

QVLD : Data Valid

ZQ : Output impedance matching

# indicates active LOW signal.

## **Pin Description**

(1/2)

| Symbol     | Туре    | Description                                                                                                                                                                                                                                                       |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK, CK#    | Input   | Clock inputs:                                                                                                                                                                                                                                                     |

|            |         | CK and CK# are differential clock inputs. This input clock pair registers address and control inputs on the rising edge of CK. CK# is ideally 180 degrees out of phase with CK.                                                                                   |

| CS#        | Input   | Chip select                                                                                                                                                                                                                                                       |

|            |         | CS# enables the commands when CS# is LOW and disables them when CS# is HIGH. When the command is disabled, new commands are ignored, but internal operations continue.                                                                                            |

| WE#, REF#  | Input   | WRITE command pin, Refresh command pin:                                                                                                                                                                                                                           |

|            |         | WE#, REF# are sampled at the positive edge of CK, WE#, and REF# define (together with CS#) the command to be executed.                                                                                                                                            |

| A0-A20     | Input   | Address inputs:                                                                                                                                                                                                                                                   |

|            |         | A0–A20 define the row and column addresses for READ and WRITE operations. During a MODE REGISTER SET, the address inputs define the register settings. They are sampled at the rising edge of CK.                                                                 |

|            |         | In the x36 configuration, A19–A20 are reserved for address expansion; in the x18 configuration, A20 is reserved for address expansion. These expansion addresses can be treated as address inputs, but they do not affect the operation of the device.            |

| A21-A22    | Input   | Reserved for future use:                                                                                                                                                                                                                                          |

|            |         | These signals should be tied to Vss or leave open.                                                                                                                                                                                                                |

| BA0-BA2    | Input   | Bank address inputs;                                                                                                                                                                                                                                              |

|            |         | Select to which internal bank a command is being applied.                                                                                                                                                                                                         |

| DQ0-DQxx   | Input   | Data input/output:                                                                                                                                                                                                                                                |

|            | /Output | The DQ signals form the 9/18/36 bit data bus. During READ commands, the data is referenced to both edges of QKx. During WRITE commands, the data is sampled at both edges of DKx.                                                                                 |

|            |         | x 9 device uses DQ0 to DQ8.                                                                                                                                                                                                                                       |

|            |         | x18 device uses DQ0 to DQ17.                                                                                                                                                                                                                                      |

| 014 014 11 | 0       | x36 device uses DQ0 to DQ35.                                                                                                                                                                                                                                      |

| QKx, QKx#  | Output  | Output data clocks: QKx and QKx# are opposite polarity, output data clocks. They are always free running and edge-aligned with data output from the $\mu$ PD48288209/18/36AF1. QKx# is ideally 180 degrees out of phase with QKx.                                 |

|            |         | For the x36 device, QK0 and QK0# are aligned with DQ0–DQ17. QK1 and QK1# are aligned with DQ18–DQ35. For the x18 device, QK0 and QK0# are aligned with DQ0–DQ8. QK1 and QK1# are aligned with DQ9–DQ17. For the x9 device, QK0 and QK0# are aligned with DQ0–DQ8. |

| DKx, DKx#  | Input   | Input data clock;                                                                                                                                                                                                                                                 |

|            |         | DKx and DKx# are the differential input data clocks. All input data is referenced to both edges of DK. DK# is ideally 180 degrees out of phase with DK.                                                                                                           |

|            |         | For the x36 device, DQ0–DQ17 are referenced to DK0 and DK0#, and DQ18–DQ35 are referenced to DK1 and DK1#. For the x9 and x18 devices, all DQs are referenced to DK and DK#.                                                                                      |

| DM         | Input   | Input data mask;                                                                                                                                                                                                                                                  |

|            |         | The DM signal is the input mask signal for WRITE data. Input data is masked when DM is sampled HIGH along with the WRITE input data. DM is sampled on both edges of DK (DK1 for the x36 configuration). The signal should be Vss if not used.                     |

| QVLD       | Output  | Data valid; The QVLD indicates valid output data. QVLD is edge-aligned with QKx and QKx#.                                                                                                                                                                         |

(2/2)

| Symbol            | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ZQ                | Input<br>/Output | External impedance [ $25 \Omega - 60 \Omega$ ]; This signal is used to tune the device outputs to the system data bus impedance. DQ output impedance is set to $0.2 \times RQ$ , where RQ is a resistor from this signal to Vss. Connecting ZQ to Vss invokes the minimum impedance mode. Connecting ZQ to VpQ invokes the maximum impedance mode. Refer to <b>Figure 2-5. Mode Register Bit Map</b> to activate this function. |

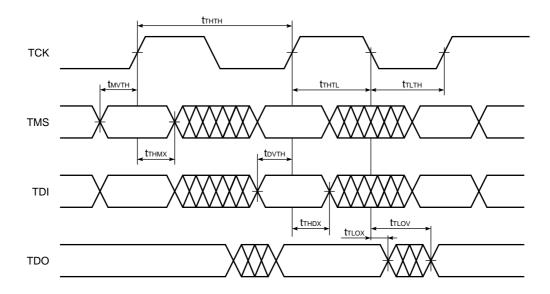

| TMS, TDI          | Input            | JTAG function pins:  IEEE 1149.1 test inputs: These balls may be left as no connects if the JTAG function is not used in the circuit                                                                                                                                                                                                                                                                                            |

| тск               | Input            | JTAG function pin; IEEE 1149.1 clock input: This ball must be tied to Vss if the JTAG function is not used in the circuit.                                                                                                                                                                                                                                                                                                      |

| TDO               | Output           | JTAG function pin; IEEE 1149.1 test output: JTAG output. This ball may be left as no connect if JTAG function is not used.                                                                                                                                                                                                                                                                                                      |

| VREF              | Input            | Input reference voltage; Nominally VDDQ/2. Provides a reference voltage for the input buffers.                                                                                                                                                                                                                                                                                                                                  |

| Vext              | Supply           | Power supply; 2.5 V nominal. See Recommended DC Operating Conditions for range.                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>DD</sub>   | Supply           | Power supply;  1.8 V nominal. See Recommended DC Operating Conditions for range.                                                                                                                                                                                                                                                                                                                                                |

| V <sub>DD</sub> Q | Supply           | DQ power supply; Nominally, 1.5 V or 1.8 V. Isolated on the device for improved noise immunity. See Recommended DC Operating Conditions for range.                                                                                                                                                                                                                                                                              |

| Vss               | Supply           | Ground                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VssQ              | Supply           | DQ ground; Isolated on the device for improved noise immunity.                                                                                                                                                                                                                                                                                                                                                                  |

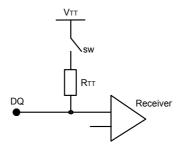

| Vπ                | Supply           | Power supply; Isolated termination supply. Nominally, VDDQ/2. See Recommended DC Operating Conditions for range.                                                                                                                                                                                                                                                                                                                |

| NF                |                  | No function; These balls may be connected to Vss.                                                                                                                                                                                                                                                                                                                                                                               |

| DNU               |                  | Do not use; These balls may be connected to Vss.                                                                                                                                                                                                                                                                                                                                                                                |

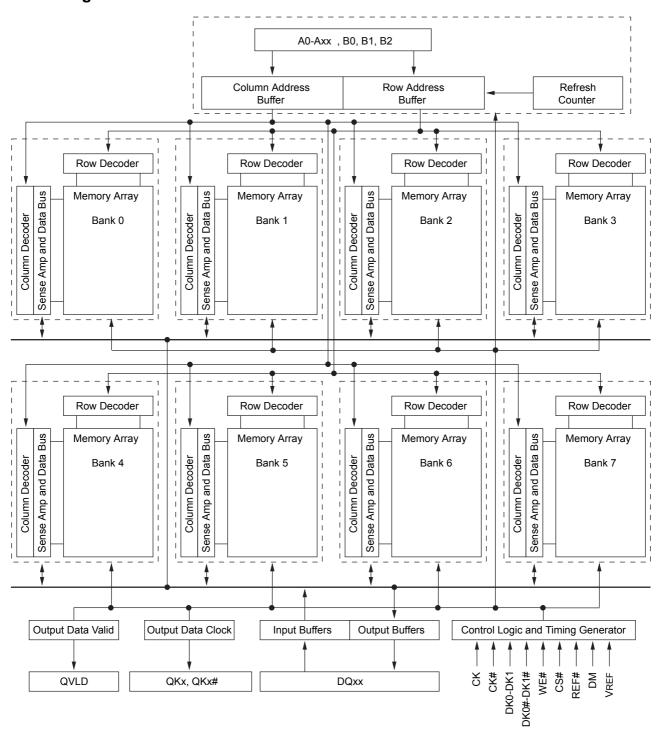

## **Block Diagram**

## $\mu$ PD48288209AF1, $\mu$ PD48288218AF1, $\mu$ PD48288236AF1

## **Contents**

| 1. | Electric   | cal Characteristics                                       | 10 |

|----|------------|-----------------------------------------------------------|----|

| 2. | Oner       | ation                                                     | 17 |

| ۷. | 2.1        | Command Operation                                         |    |

|    | 2.1        | Description of Commands                                   |    |

|    | 2.2        | •                                                         |    |

|    | 2.3<br>2.4 | Initialization Power-On Sequence                          |    |

|    | 2.4<br>2.5 | <u> </u>                                                  |    |

|    | 2.5<br>2.6 | Programmable Impedance Output Buffer                      |    |

|    |            | PLL Reset                                                 |    |

|    | 2.7        | Clock Input                                               |    |

|    | 2.8        | Mode Register Set Command (MRS)                           |    |

|    | 2.9        | Read & Write configuration (Non Multiplexed Address Mode) |    |

|    | 2.10       | Write Operation (WRITE)                                   |    |

|    | 2.11       | Read Operation (READ)                                     |    |

|    | 2.12       | Refresh Operation: AUTO REFRESH Command (AREF)            | 30 |

|    | 2.13       | On-Die Termination                                        |    |

|    | 2.14       | Operation with Multiplexed Address                        | 34 |

|    | 2.15       | Address Mapping in Multiplexed Mode                       | 36 |

|    | 2.16       | Read & Write configuration in Multiplexed Address Mode    | 37 |

|    | 2.17       | Refresh Command in Multiplexed Address Mode               |    |

|    | 2.18       | Input Slew Rate Derating                                  |    |

| 3. | JTAG       | Specification                                             | 43 |

| 4. | Packa      | age Dimensions                                            | 50 |

| 5. | Reco       | mmended Soldering Condition                               | 52 |

#### 1. Electrical Characteristics

#### **Absolute Maximum Ratings**

| Parameter                             | Symbol              | Conditions | Rating       | Unit |

|---------------------------------------|---------------------|------------|--------------|------|

| Supply voltage                        | V <sub>EXT</sub>    |            | -0.3 to +2.8 | V    |

| Supply voltage                        | $V_{DD}$            |            | -0.3 to +2.1 | V    |

| Output supply voltage,                | $V_{DD}Q$           |            | -0.3 to +2.1 | V    |

| Input voltage, Input / Output voltage |                     |            |              |      |

| Input / Output voltage                | VIH / VIL           |            | -0.3 to +2.1 | V    |

| Junction temperature                  | T <sub>j</sub> MAX. |            | 110          | °C   |

| Storage temperature                   | T <sub>stg</sub>    |            | -55 to +125  | °C   |

Caution Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

## **Recommended DC Operating Conditions**

$0^{\circ}C \le T_C \le 95^{\circ}C$ ;  $1.7 \text{ V} \le V_{DD} \le 1.9 \text{ V}$ , unless otherwise noted.

| Parameter             | Symbol            | Conditions | MIN.                     | TYP.       | MAX.                   | Unit | Note    |

|-----------------------|-------------------|------------|--------------------------|------------|------------------------|------|---------|

| Supply voltage        | VEXT              |            | 2.38                     | 2.5        | 2.63                   | V    | 1       |

| Supply voltage        | V <sub>DD</sub>   |            | 1.7                      | 1.8        | 1.9                    | V    | 1       |

| Output supply voltage | V <sub>DD</sub> Q |            | 1.4                      |            | V <sub>DD</sub>        | V    | 1, 2, 3 |

| Reference Voltage     | VREF              |            | 0.49 x V <sub>DD</sub> Q | 0.5 x VddQ | 0.51 x VddQ            | V    | 1, 4, 5 |

| Termination voltage   | Vπ                |            | 0.95 x Vref              | VREF       | 1.05 x Vref            | V    | 1, 6    |

| Input HIGH voltage    | VIH (DC)          |            | V <sub>REF</sub> + 0.1   |            |                        | V    | 1       |

| Input LOW voltage     | VIL (DC)          |            |                          |            | V <sub>REF</sub> – 0.1 | V    | 1       |

**Notes 1.** All voltage referenced to Vss (GND).

- 2. During normal operation, VDDQ must not exceed VDD.

- **3.** V<sub>DD</sub>Q can be set to a nominal 1.5 V  $\pm$  0.1 V or 1.8 V  $\pm$  0.1 V supply.

- **4.** Typically the value of V<sub>REF</sub> is expect to be 0.5 x V<sub>DD</sub>Q of the transmitting device. V<sub>REF</sub> is expected to track variations in V<sub>DD</sub>Q.

- **5.** Peak-to-peak AC noise on V<sub>REF</sub> must not exceed  $\pm 2\%$  V<sub>REF</sub>(DC).

- 6.  $V_{\text{TT}}$  is expected to be set equal to  $V_{\text{REF}}$  and must track variations in the DC level of  $V_{\text{REF}}$ .

#### **DC Characteristics**

$0^{\circ}C \le T_C \le 95^{\circ}C$ ; 1.7 V  $\le V_{DD} \le 1.9$  V, unless otherwise noted

| Parameter                 | Symbol | Test condition       | MIN.                                  | MAX.                                  | Unit | Note |

|---------------------------|--------|----------------------|---------------------------------------|---------------------------------------|------|------|

| Input leakage current     | lu     |                      | <b>-</b> 5                            | +5                                    | μΑ   | 1,2  |

| Output leakage current    | Іьо    |                      | -5                                    | +5                                    | μΑ   | 1,2  |

| Reference voltage current | IREF   |                      | -5                                    | +5                                    | μΑ   | 1,2  |

| Output high current       | Іон    | $V_{OH} = V_{DD}Q/2$ | (V <sub>DD</sub> Q/2) / (1.15 x RQ/5) | (V <sub>DD</sub> Q/2) / (0.85 x RQ/5) | mA   | 3,4  |

| Output low current        | Іоь    | Vol = VddQ/2         | (V <sub>DD</sub> Q/2) / (1.15 x RQ/5) | (V <sub>DD</sub> Q/2) / (0.85 x RQ/5) | mA   | 3,4  |

- **Notes 1.** Outputs are impedance-controlled.  $| \text{Ioh } | = (V_{DD}Q/2)/(RQ/5)$  for values of  $125 \Omega \le RQ \le 300 \Omega$ .

- 2. Outputs are impedance-controlled. IoL =  $(V_{DD}Q/2)/(RQ/5)$  for values of 125  $\Omega \le RQ \le 300 \Omega$ .

- **3.** IoH and IoL are defined as absolute values and are measured at VDDQ/2. IoH flows from the device, IoL flows into the device.

- **4.** If MRS bit A8 is 0, use  $RQ = 250 \Omega$  in the equation in lieu of presence of an external impedance matched resistor.

#### Capacitance (TA = 25 °C, f = 1MHz)

| Parameter                           | Symbol           | Test conditions      | MIN. | MAX. | Unit |

|-------------------------------------|------------------|----------------------|------|------|------|

| Address / Control Input capacitance | Cin              | Vin = 0 V            | 1.5  | 2.5  | pF   |

| I/O, Output, Other capacitance      | C <sub>I/O</sub> | V//O = 0 V           | 3.5  | 5.0  | pF   |

| (DQ, DM, QK, QVLD)                  |                  |                      |      |      |      |

| Clock Input capacitance             | Cclk             | Vclk = 0 V           | 2.0  | 3.0  | pF   |

| JTAG pins                           | Cı               | V <sub>J</sub> = 0 V | 2.0  | 5.0  | pF   |

Remark These parameters are periodically sampled and not 100% tested. Capacitance is not tested on ZQ pin.

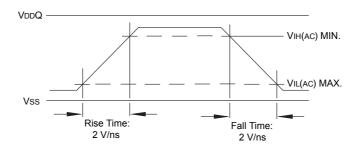

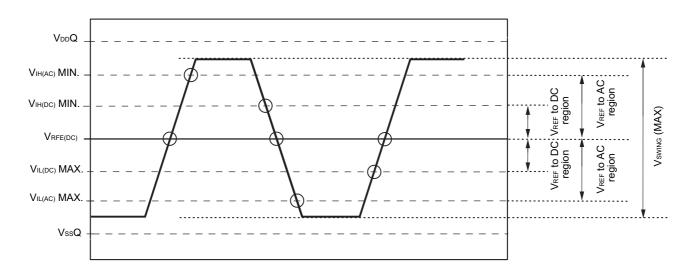

#### **Recommended AC Operating Conditions**

$0^{\circ}C \le TC \le 95^{\circ}C$ ; 1.7  $V \le V_{DD} \le 1.9 V$ , unless otherwise noted

| Parameter          | Symbol   | Conditions | MIN.                   | MAX.                   | Unit | Note |

|--------------------|----------|------------|------------------------|------------------------|------|------|

| Input HIGH voltage | VIH (AC) |            | V <sub>REF</sub> + 0.2 |                        | V    | 1    |

| Input LOW voltage  | VIL (AC) |            |                        | V <sub>REF</sub> – 0.2 | V    | 1    |

**Note** Overshoot:  $V_{IH (AC)} \le V_{DD}Q + 0.7 \text{ V for } t \le t_{CK}/2$

Undershoot:  $V_{\text{IL (AC)}} \ge -0.5 \text{ V for } t \le t_{\text{CK}}/2$

Control input signals may not have pulse widths less than tckh (MIN.) or operate at cycle rates less than tck

(MIN.).

## **DC Characteristics**

I<sub>DD</sub> / I<sub>SB</sub> Operating Conditions

| Parameter         | Symbol            | Test condition                                           |                 |        |      | MA   | ٩X.  |          | Unit     |

|-------------------|-------------------|----------------------------------------------------------|-----------------|--------|------|------|------|----------|----------|

|                   |                   |                                                          |                 |        | -E18 |      | -E24 |          |          |

|                   |                   |                                                          |                 |        | tRC= | 15ns | tRC= | 20ns     |          |

|                   |                   |                                                          |                 |        |      |      |      | 300MHz   |          |

| Standby current   | I <sub>SB1</sub>  | tck = Idle                                               | V <sub>DD</sub> | x9/x18 |      | 55   | 55   | 55       | mA       |

| Standby current   | 1561              | All banks idle, no inputs toggling                       | V DD            | x36    | 55   | 55   | 55   | 55       | 111/     |

|                   |                   | All banks fule, no inputs togging                        | VEXT            | X30    | 5    | 5    | 5    | 5        |          |

| Active standby    | I <sub>SB2</sub>  | CS# = HIGH, No commands, half bank / address /           | VEXI            | x9/x18 |      | 215  | 215  | 190      | mA       |

| •                 | 1582              | ,                                                        | V DD            |        | 250  | 215  | 215  |          | IIIA     |

| current           |                   | data change once every four clock cycles                 | VEXT            | x36    | 5    | 5    | 5    | 190<br>5 |          |

| Operating aurrent | l                 | DI 2 cognestial bank cooper bank transitions             |                 | x9/x18 |      | _    |      |          | A        |

| Operating current | DD1               | BL=2, sequential bank access, bank transitions           | V <sub>DD</sub> |        |      | 302  | 266  | 239      | mA       |

|                   |                   | once every tRc, half address transitions once            |                 | x36    | 375  | 344  | 302  | 283      |          |

|                   |                   | every t <sub>RC</sub> , read followed by write sequence, | VEXT            |        | 10   | 10   | 10   | 10       |          |

| •                 |                   | continuous data during WRITE commands.                   |                 | 0/ 40  |      |      |      |          |          |

| Operating current | I <sub>DD2</sub>  | BL=4, sequential bank access, bank transitions           | V <sub>DD</sub> | x9/x18 |      | 345  | 288  | 262      | mA       |

|                   |                   | once every tRC, half address transitions once            |                 | x36    | 433  | 418  | 348  | 339      |          |

|                   |                   | every tRC, read followed by write sequence,              | VEXT            |        | 10   | 10   | 10   | 10       |          |

|                   | _                 | continuous data during WRITE commands.                   |                 |        |      |      |      |          | _        |

| Operating current | I <sub>DD3</sub>  | BL=8, sequential bank access, bank transitions           | V <sub>DD</sub> | x9/x18 | 377  | 357  | 299  | 276      | mA       |

|                   |                   | once every tRc, half address transitions once            |                 |        |      |      |      |          |          |

|                   |                   | every tRC, read followed by write sequence,              | VEXT            |        | 15   | 15   | 15   | 15       |          |

|                   |                   | continuous data during WRITE commands.                   |                 |        |      |      |      |          |          |

| Burst refresh     | REF1              | Eight bank cyclic refresh, continuous                    | V <sub>DD</sub> | x9/x18 |      | 464  | 464  | 362      | mA       |

| current           |                   | address/data, command bus remains in refresh             |                 | x36    | 563  | 432  | 432  | 338      |          |

|                   |                   | for all banks                                            | VEXT            | 1      | 45   | 30   | 30   | 25       |          |

| Disturbed         | I <sub>REF2</sub> | Single bank refresh, sequential bank access,             | V <sub>DD</sub> | x9/x18 | 260  | 219  | 205  | 173      | mA       |

| refresh current   |                   | half address transitions once every tRC,                 |                 | x36    | 258  | 216  | 203  | 171      |          |

|                   |                   | continuous data                                          | VEXT            | •      | 10   | 10   | 10   | 10       |          |

| Operating burst   | I <sub>DD2W</sub> | BL=2, cyclic bank access, half of address bits           | V <sub>DD</sub> | x9/x18 | 890  | 691  | 691  | 542      | mA       |

| write current     |                   | change every clock cycle, continuous data,               |                 | x36    | 998  | 792  | 792  | 641      |          |

|                   |                   | measurement is taken during continuous WRITE             | VEXT            |        | 40   | 35   | 35   | 30       |          |

| Operating burst   | IDD4W             | BL=4, cyclic bank access, half of address bits           | V <sub>DD</sub> | x9/x18 | 609  | 478  | 478  | 380      | mA       |

| write current     |                   | change every two clocks, continuous data,                |                 | x36    | 753  | 608  | 608  | 498      |          |

|                   |                   | measurement is taken during continuous WRITE             | VEXT            |        | 25   | 20   | 20   | 20       |          |

| Operating burst   | IDD8W             | BL=8, cyclic bank access, half of address bits           | V <sub>DD</sub> | x9/x18 | 478  | 378  | 378  | 303      | mA       |

| write current     |                   | change every four clocks, continuous data,               |                 |        |      |      |      |          |          |

|                   |                   | measurement is taken during continuous WRITE             | VEXT            | •      | 25   | 20   | 20   | 20       |          |

| Operating burst   | I <sub>DD2R</sub> | BL=2, cyclic bank access, half of address bits           | V <sub>DD</sub> | x9/x18 | 927  | 712  | 712  | 551      | mA       |

| read current      |                   | change every clock cycle, measurement is taken           |                 | x36    | 925  | 710  | 710  | 549      |          |

|                   |                   | during continuous READ                                   | VEXT            | ı      | 40   | 35   | 35   | 30       |          |

| Operating burst   | I <sub>DD4R</sub> | BL=4, cyclic bank access, half of address bits           | V <sub>DD</sub> | x9/x18 | 619  | 477  | 477  | 377      | mA       |

| read current      |                   | change every two clocks, measurement is taken            |                 | x36    | 643  | 494  | 494  | 390      |          |

|                   |                   | during continuous READ                                   | VEXT            |        | 25   | 20   | 20   | 20       |          |

| Operating burst   | I <sub>DD8R</sub> | BL=8, cyclic bank access, half of address bits           | VDD             | x9/x18 |      | 368  | 368  | 292      | mA       |

| read current      | .DDGK             | change every four clocks, measurement is taken           | • 55            |        | 710  | 300  | 300  | 202      | , \      |

| TOUG OUTTOIN      |                   |                                                          | \/              | 1      | 25   |      |      |          |          |

|                   |                   | during continuous READ                                   | VEXT            |        | 25   | 20   | 20   | 20       | <u> </u> |

- **Remarks 1.** Idd specifications are tested after the device is properly initialized.  $0^{\circ}\text{C} \le \text{Tc} \le 95^{\circ}\text{C}$ ;  $1.7 \text{ V} \le \text{V}_{DD} \le 1.9 \text{ V}$ ,  $2.38 \text{ V} \le \text{V}_{EXT} \le 2.63 \text{ V}$ ,  $1.4 \text{ V} \le \text{V}_{DD}Q \le \text{V}_{DD}$ ,  $\text{V}_{REF} = \text{V}_{DD}Q/2$

- 2.  $t_{CK} = t_{DK} = MIN.$ ,  $t_{RC} = MIN.$

- 3. Input slew rate is specified in **Recommended DC Operating Conditions** and **Recommended AC Operating Conditions**.

- **4.** IDD parameters are specified with ODT disabled.

- 5. Continuous data is defined as half the DQ signals changing between HIGH and LOW every half clock cycles (twice per clock).

- **6.** Continuous address is defined as half the address signals between HIGH and LOW every clock cycles (once per clock).

- 7. Sequential bank access is defined as the bank address incrementing by one ever trc.

- **8.** Cyclic bank access is defined as the bank address incrementing by one for each command access. For BL=4 this is every other clock.

- **9.** CS# is HIGH unless a READ, WRITE, AREF, or MRS command is registered. CS# never transitions more than per clock cycle.

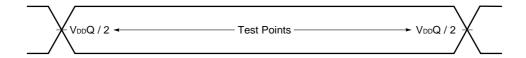

## **AC Characteristics**

## **AC Test Conditions**

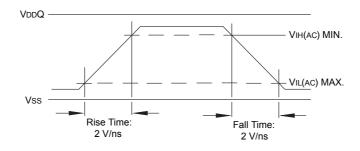

## Input waveform

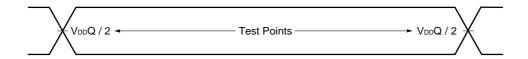

## **Output waveform**

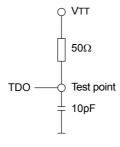

## **Output load condition**

## AC Characteristics <Read and Write Cycle>

| Parameter                        | Symbol                       | -Е    | 18   |       | -Е   | 24    |      | Unit         | Note |

|----------------------------------|------------------------------|-------|------|-------|------|-------|------|--------------|------|

|                                  |                              | (533  | MHz) | (400  | MHz) | (300  | MHz) |              |      |

|                                  |                              | MIN.  | MAX. | MIN.  | MAX. | MIN.  | MAX. |              |      |

| Clock                            |                              |       |      |       |      |       |      |              |      |

| Clock cycle time (CK,CK#,DK,DK#) | tck, tok                     | 1.875 | 5.7  | 2.5   | 5.7  | 3.3   | 5.7  | ns           |      |

| Clock frequency (CK,CK#,DK,DK#)  | tck, tok                     | 175   | 533  | 175   | 400  | 175   | 300  | MHz          |      |

| Random Cycle time                | <b>t</b> RC                  | 15    |      | 15    |      | 20    |      | ns           |      |

| Clock Jitter: period             | <b>t</b> JIT PER             | -100  | 100  | -150  | 150  | -200  | 200  | ps           | 1, 2 |

| Clock Jitter: cycle-to-cycle     | <b>t</b> лт сс               |       | 200  |       | 300  |       | 400  | ps           |      |

| Clock HIGH time (CK,CK#,DK,DK#)  | <b>t</b> скн, <b>t</b> дкн   | 0.45  | 0.55 | 0.45  | 0.55 | 0.45  | 0.55 | Cycle        |      |

| Clock LOW time (CK,CK#,DK,DK#)   | tckl, tdkl                   | 0.45  | 0.55 | 0.45  | 0.55 | 0.45  | 0.55 | Cycle        |      |

| Clock to input data clock        | tckdk                        | -0.3  | 0.3  | -0.45 | 0.5  | -0.45 | 1.0  | ns           |      |

| Mode register set cycle time     | tmrsc                        | 6     |      | 6     |      | 6     |      | Cycle        |      |

| to any command                   |                              |       |      |       |      |       |      |              |      |

| PLL Lock time                    | <b>t</b> CK Lock             | 15    |      | 15    |      | 15    |      | μs           |      |

| Clock static to PLL reset        | tCK Reset                    | 30    |      | 30    |      | 30    |      | ns           |      |

| Output Times                     |                              |       |      |       |      |       |      |              |      |

| Output data clock HIGH time      | tqкн                         | 0.9   | 1.1  | 0.9   | 1.1  | 0.9   | 1.1  | <b>t</b> cкн |      |

| Output data clock LOW time       | <b>t</b> QKL                 | 0.9   | 1.1  | 0.9   | 1.1  | 0.9   | 1.1  | <b>t</b> ckl |      |

| QK edge to clock edge skew       | tскак                        | -0.2  | 0.2  | -0.25 | 0.25 | -0.3  | 0.3  | ns           |      |

| QK edge to output data edge      | <b>t</b> QKQ0, <b>t</b> QKQ1 | -0.12 | 0.12 | -0.2  | 0.2  | -0.25 | 0.25 | ns           | 3, 5 |

| QK edge to any output data       | tака                         | -0.22 | 0.22 | -0.3  | 0.3  | -0.35 | 0.35 | ns           | 4, 5 |

| QK edge to QVLD                  | takvld                       | -0.22 | 0.22 | -0.3  | 0.3  | -0.35 | 0.35 | ns           |      |

| Setup Times                      |                              |       |      |       |      |       |      |              |      |

| Address/command and input        | tas/tcs                      | 0.3   |      | 0.4   |      | 0.5   |      | ns           |      |

| Data-in and data mask to DK      | tos                          | 0.17  |      | 0.225 |      | 0.3   |      | ns           |      |

| Hold Times                       |                              |       |      |       |      |       |      |              |      |

| Address/command and input        | taн/tcн                      | 0.3   |      | 0.4   |      | 0.5   |      | ns           |      |

| Data-in and data mask to DK      | tон                          | 0.17  |      | 0.225 |      | 0.3   |      | ns           |      |

**Notes 1.** Clock phase jitter is the variance from clock rising edge to the next expected clock rising edge.

- 2. Frequency drift is not allowed.

- 3.  $t_{QKQ0}$  is referenced to DQ0–DQ17 in x36 and DQ0–DQ8 in x18.  $t_{QKQ1}$  is referenced to DQ18–DQ35 in x36 and DQ9–DQ17 in x18.

- 4. toko takes into account the skew between any QKx and any DQ.

- 5. tqkq, tqkqx are guaranteed by design.

**Remark** All timing parameters are measured relative to the crossing point of CK/CK#, DK/DK# and to the crossing point with  $V_{\text{REF}}$  of the command, address, and data signals.

CK# CK COMMAND, VALID VALID **ADDRESS** tas tан tckpk tckpk DKx# DKx tok tokh **t**DKL Don't care

Figure 1-1. Clock / Input Data Clock Command / Address Timings

## **Temperature and Thermal Impedance**

## **Temperature Limits**

| Parameter                        | Symbol | MIN. | MAX. | Unit | Note |

|----------------------------------|--------|------|------|------|------|

| Reliability junction temperature | TJ     | 0    | +110 | °C   | 1    |

| Operating junction temperature   | TJ     | 0    | +100 | °C   | 2    |

| Operating case temperature       | Tc     | 0    | +95  | °C   | 3    |

- **Notes 1.** Temperatures greater than 110°C may cause permanent damage to the device. This is a stress rating only and functional operation of the device at or above this is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability of the part.

- 2. Junction temperature depends upon cycle time, loading, ambient temperature, and airflow.

- **3.** MAX operating case temperature; Tc is measured in the center of the package. Device functionality is not guaranteed if the device exceeds maximum Tc during operation.

## **Thermal Impedance**

| Substrate | Ball      |                  | θja (°C/W)       |                  | θjb    | θјс    |

|-----------|-----------|------------------|------------------|------------------|--------|--------|

|           |           | Air Flow = 0 m/s | Air Flow = 1 m/s | Air Flow = 2 m/s | (°C/W) | (°C/W) |

| 4 - Layer | Lead free | 18.9             | 15.2             | 14.4             | 9.1    | 3.0    |

#### 2. Operation

#### 2.1 Command Operation

According to the functional signal description, the following command sequences are possible. All input states or sequences not shown are illegal or reserved. All command and address inputs must meet setup and hold times around the rising edge of CK.

Table 2-1. Address Widths at Different Burst Lengths

| Burst Length | Configuration |        |        |  |  |  |

|--------------|---------------|--------|--------|--|--|--|

|              | х9            | x18    | x36    |  |  |  |

| BL=2         | A0-A20        | A0-A19 | A0–A18 |  |  |  |

| BL=4         | A0-A19        | A0-A18 | A0–A17 |  |  |  |

| BL=8         | A0–A18        | A0-A17 | N/A    |  |  |  |

Table 2-2. Command Table

| Operation                      | Code        | CS# | WE# | REF# | A0-An <sup>Note1</sup> | BA0-BA2 | Note |

|--------------------------------|-------------|-----|-----|------|------------------------|---------|------|

| Device DESELECT / No Operation | DESEL / NOP | Н   | Х   | Х    | Х                      | Х       |      |

| MRS: Mode Register Set         | MRS         | L   | L   | L    | OPCODE                 | Х       | 2    |

| READ                           | READ        | L   | Н   | Н    | А                      | ВА      | 3    |

| WRITE                          | WRITE       | L   | L   | Н    | А                      | ВА      | 3    |

| AUTO REFRESH                   | AREF        | L   | Н   | L    | Х                      | ВА      |      |

**Notes** 1. n = 20.

- 2. Only A0-A17 are used for the MRS command.

- 3. See Table 2-1.

Remark X = "Don't Care", H = logic HIGH, L = logic LOW, A = valid address, BA = valid bank address

#### 2.2 Description of Commands

## DESEL / NOP Note1

The NOP command is used to perform a no operation to the  $\mu$ PD48288209/18/36AF1, which essentially deselects the chip. Use the NOP command to prevent unwanted commands from being registered during idle or wait states. Operations already in progress are not affected. Output values depend on command history.

#### MRS

The mode register is set via the address inputs A0–A17. See **Figure 2-5. Mode Register Bit Map** for further information. The MRS command can only be issued when all banks are idle and no bursts are in progress.

### **READ**

The READ command is used to initiate a burst read access to a bank. The value on the BA0–BA2 inputs selects the bank, and the address provided on inputs A0–A20 selects the data location within the bank.

#### **WRITE**

The WRITE command is used to initiate a burst write access to a bank. The value on the BA0–BA2 inputs selects the bank, and the address provided on inputs A0–A20 selects the data location within the bank. Input data appearing on the DQ is written to the memory array subject to the DM input logic level appearing coincident with the data. If the DM signal is registered LOW, the corresponding data will be written to memory. If the DM signal is registered HIGH, the corresponding data inputs will be ignored (i.e., this part of the data word will not be written).

#### **AREF**

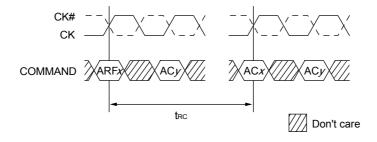

The AREF is used during normal operation of the  $\mu$ PD48288209/18/36AF1 to refresh the memory content of a bank. The command is non-persistent, so it must be issued each time a refresh is required. The value on the BA0–BA2 inputs selects the bank. The refresh address is generated by an internal refresh controller, effectively making each address bit a "Don't Care" during the AREF command. The  $\mu$ PD48288209/18/36AF1 requires 64K cycles at an average periodic interval of 0.49 $\mu$ s Note2 (MAX.). To improve efficiency, eight AREF commands (one for each bank) can be posted to  $\mu$ PD48288209/18/36AF1 at periodic intervals of 3.9  $\mu$ s Note3.

Within a period of 32 ms, the entire memory must be refreshed. The delay between the AREF command and a subsequent command to same bank must be at least trace as continuous refresh. Other refresh strategies, such as burst refresh, are also possible.

Notes 1. When the chip is deselected, internal NOP commands are generated and no commands are accepted.

- **2.** Actual refresh is 32 ms / 8k / 8 = 0.488  $\mu$ s.

- 3. Actual refresh is 32 ms / 8k = 3.90  $\mu$ s.

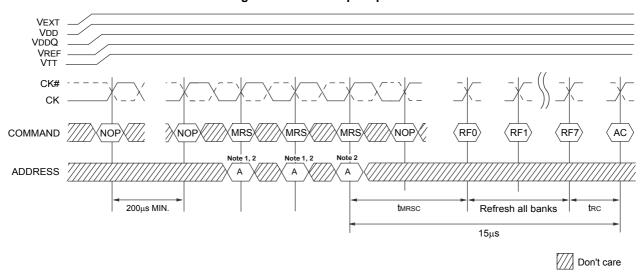

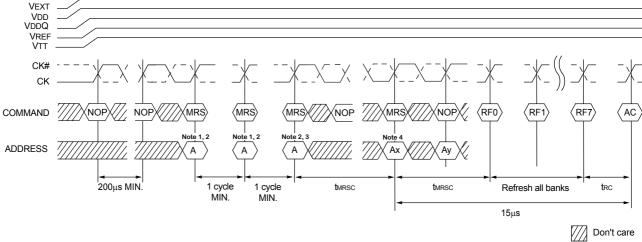

#### 2.3 Initialization

The  $\mu$ PD48288209/18/36AF1 must be powered up and initialized in a predefined manner. Operational procedures other than those specified may result in undefined operations or permanent damage to the device. The following sequence is used for Power-Up:

1. Apply power (Vext, Vdd, Vdd, Vref, Vtt) and start clock as soon as the supply voltages are stable. Apply Vdd and Vext before or at the same time as Vdd. Apply Vdd before or at the same time as Vref and Vtt. Although there is no timing relation between Vext and Vdd, the chip starts the power-up sequence only after both voltages are at their nominal levels. Vdd supply must not be applied before Vdd supply. CK/CK# must meet Vdd(DC) prior to being applied. Maintain all remaining balls in NOP conditions.

**Note** No rule of apply power sequence is the design target.

- 2. Maintain stable conditions for 200  $\mu$ s (MIN.).

- **3.** Issue at least three or more consecutive MRS commands: two dummies or more plus one valid MRS. It is recommended that all address pins are held LOW during the dummy MRS commands.

- **4.** t<sub>MRSC</sub> after valid MRS, an AUTO REFRESH command to all 8 banks must be issued and wait for 15 μs with CK/CK# toggling in order to lock the PLL prior to normal operation.

- **5.** After tRC, the chip is ready for normal operation.

#### 2.4 Power-On Sequence

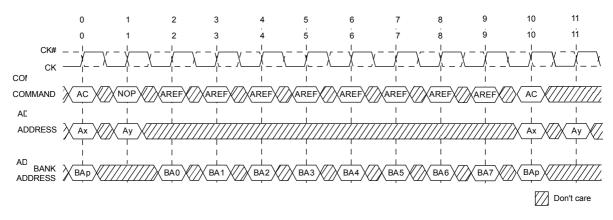

Figure 2-1. Power-Up Sequence

Notes 1. Recommended all address pins held LOW during dummy MRS commands.

2. A10-A17 must be LOW.

**Remark** MRS: MRS command

RFp: REFRESH bank p

AC: Any command

#### 2.5 Programmable Impedance Output Buffer

The  $\mu$ PD48288209/18/36AF1 is equipped with programmable impedance output buffers. This allows a user to match the driver impedance to the system. To adjust the impedance, an external precision resistor (RQ) is connected between the ZQ ball and Vss. The value of the resistor must be five times the desired impedance. For example, a 300  $\Omega$  resistor is required for an output impedance of 60  $\Omega$ . To ensure that output impedance is one fifth the value of RQ (within 15 percent), the range of RQ is 125  $\Omega$  to 300  $\Omega$ . Output impedance updates may be required because, over time, variations may occur in supply voltage and temperature. The device samples the value of RQ. An impedance update is transparent to the system and does not affect device operation. All data sheet timing and current specifications are met during an update.

#### 2.6 PLL Reset

The  $\mu$ PD48288209/18/36AF1 utilizes internal Phase-locked loops for maximum output, data valid windows. It can be placed into a stopped-clock state to minimize power with a modest restart time of 15  $\mu$ s. The clock (CK/CK#) must be toggled for 15  $\mu$ s in order to stabilize PLL circuits for next READ operation.

## 2.7 Clock Input

**Table 2-3. Clock Input Operation Conditions**

| Parameter                                | Symbol   | Conditions | MIN.                       | MAX.                       | Unit | Note |

|------------------------------------------|----------|------------|----------------------------|----------------------------|------|------|

| Clock Input Voltage Level                | VIN (DC) | CK and CK# | -0.3                       | V <sub>DD</sub> Q + 0.3    | ٧    |      |

| Clock Input Differential Voltage Level   | VID (DC) | CK and CK# | 0.2                        | V <sub>DD</sub> Q + 0.6    | ٧    | 8    |

| Clock Input Differential Voltage Level   | VID (AC) | CK and CK# | 0.4                        | V <sub>DD</sub> Q + 0.6    | ٧    | 8    |

| Clock Input Crossing Point Voltage Level | VIX (AC) | CK and CK# | V <sub>DD</sub> Q/2 - 0.15 | V <sub>DD</sub> Q/2 + 0.15 | V    | 9    |

VIN(DC) MAX.

CK#

VDDQ/2 + 0.15

VDDQ/2 - 0.15

VIX(AC) MAX.

VID(DC)

VID(DC)

VID(DC)

VID(DC)

VIX(AC) MIN.

Minimum Clock Level

Figure 2-2. Clock Input

Notes 1. DKx and DKx# have the same requirements as CK and CK#.

- 2. All voltages referenced to Vss.

- **3.** Tests for AC timing, IDD and electrical AC and DC characteristics may be conducted at normal reference/supply voltage levels; but the related specifications and device operations are tested for the full voltage range specified.

- **4.** AC timing and IDD tests may use a V<sub>IL</sub> to V<sub>IH</sub> swing of up to 1.5 V in the test environment, but input timing is still referenced to V<sub>REF</sub> (or the crossing point for CK/CK#), and parameters specifications are tested for the specified AC input levels under normal use conditions. The minimum slew rate for the input signals used to test the device is 2V/ns in the range between V<sub>IL(AC)</sub> and V<sub>IH(AC)</sub>.

- 5. The AC and DC input level specifications are as defined in the HSTL Standard (i.e. the receiver will effectively switch as a result of the signal crossing the AC input level, and will remain in that state as long as the signal does not ring back above[below] the DC input LOW[HIGH] level).

- **6.** The CK/CK# input reference level (for timing referenced to CK/CK#) is the point at which CK and CK# cross. The input reference level for signal other than CK/CK# is V<sub>REF</sub>.

- 7. CK and CK# input slew rate must be  $\geq 2V/ns$  ( $\geq 4V/ns$  if measured differentially).

- 8. V<sub>ID</sub> is the magnitude of the difference between the input level on CK and input level on CK#.

- 9. The value of V<sub>IX</sub> is expected to equal V<sub>DD</sub>Q/2 of the transmitting device and must track variations in the DC level of the same.

10.CK and CK# must cross within the region.

- 11.CK and CK# must meet at least VID(DC) (MIN.) when static and centered around VDDQ/2.

- 12. Minimum peak-to-peak swing.

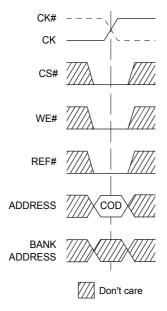

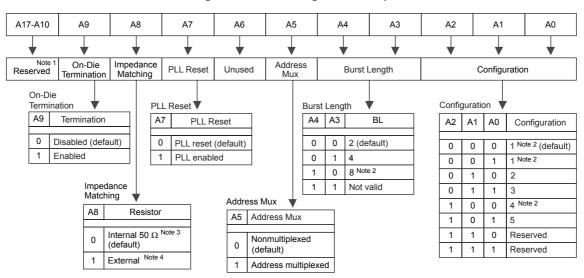

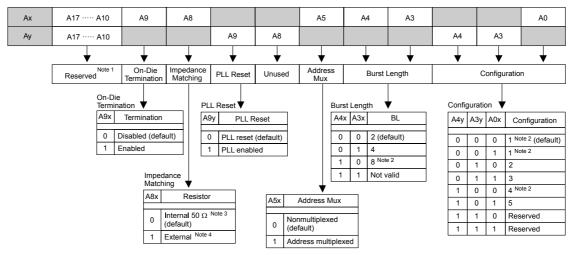

#### 2.8 Mode Register Set Command (MRS)

The mode register stores the data for controlling the operating modes of the memory. It programs the  $\mu$ PD48288209/18/36AF1 configuration, burst length, and I/O options. During a MRS command, the address inputs A0–A17 are sampled and stored in the mode register. tmrsc must be met before any command can be issued to the  $\mu$ PD48288209/18/36AF1. The mode register may be set at any time during device operation. However, any pending operations are not guaranteed to successfully complete, and all memory cell data are not guaranteed.

Since MRS is used for internal test mode entry, bits A10-A17 must be set to all "0" at the MRS setting.

CK# - KMRSC COMMAND CO

Figure 2-3. Mode Register Set Timing

Remark MRS: MRS command

AC: any command

Figure 2-4. Mode Register Set

Remark COD: code to be loaded into the register.

Figure 2-5. Mode Register Bit Map

**Notes** 1. Bits A10–A17 must be set to all '0'. A18-An are "Don't Care".

- **2.** BL=8 is not available for configuration 1 and 4.

- 3.  $\pm 30\%$  temperature variation.

- 4. Within 15%.

#### 2.9 Read & Write configuration (Non Multiplexed Address Mode)

**Table 2-4** shows, for different operating frequencies, the different  $\mu$ PD48288209/18/36AF1 configurations that can be programmed into the mode register. The READ and WRITE latency (trl and twl) values along with the row cycle times (trl) are shown in clock cycles as well as in nanoseconds.

| Parameter             |         | Configuration |         |            |         |             |  |  |

|-----------------------|---------|---------------|---------|------------|---------|-------------|--|--|

|                       | 1 Note1 | 2             | 3       | 4 Note1, 2 | 5       |             |  |  |

| trc                   | 4       | 6             | 8       | 3          | 5       | tск         |  |  |

| <b>t</b> RL           | 4       | 6             | 8       | 3          | 5       | <b>t</b> cĸ |  |  |

| twL                   | 5       | 7             | 9       | 4          | 6       | <b>t</b> cĸ |  |  |

| Valid frequency range | 266-175 | 400-175       | 533-175 | 200-175    | 333-175 | MHz         |  |  |

Table 2-4. Configuration Table

## **Notes 1.** BL= 8 is not available.

2. The minimum trc is typically 3 cycles, except in the case of a WRITE followed by a READ to the same bank. In this instance the minimum trc is 4 cycles.

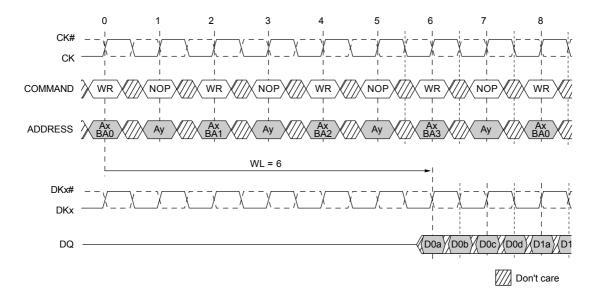

#### 2.10 Write Operation (WRITE)

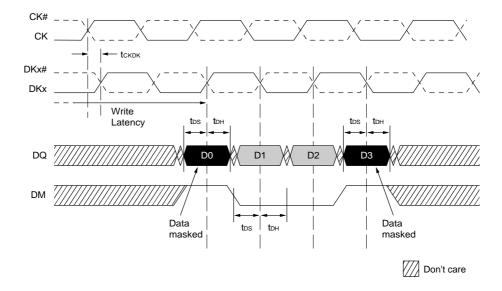

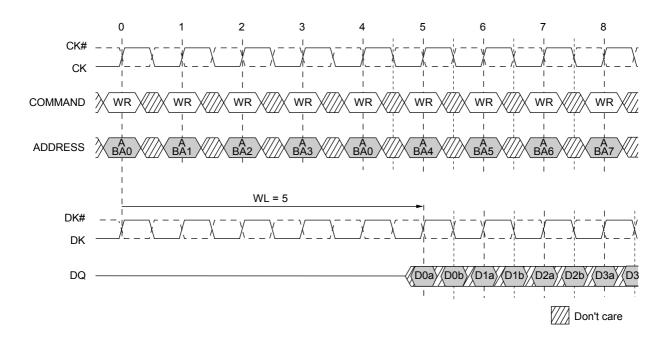

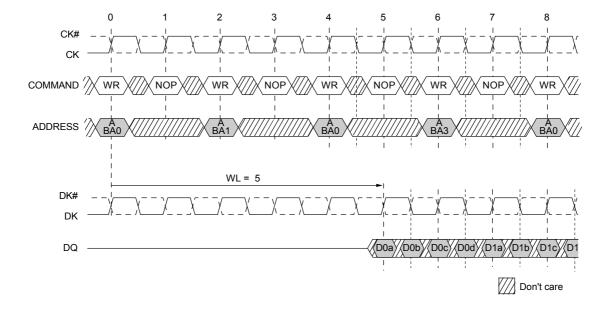

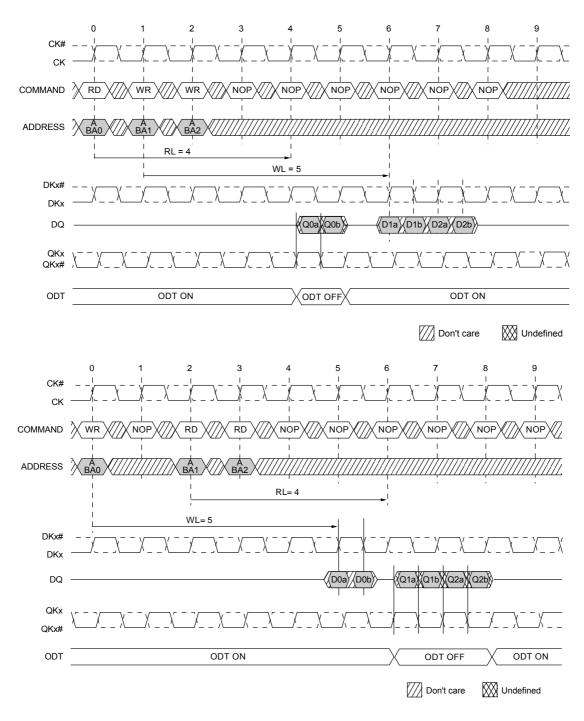

Write accesses are initiated with a WRITE command, as shown in **Figure 2-6**. Row and bank addresses are provided together with the WRITE command. During WRITE commands, data will be registered at both edges of DK according to the programmed burst length (BL). A WRITE latency (WL) one cycle longer than the programmed READ latency (RL + 1) is present, with the first valid data registered at the first rising DK edge WL cycles after the WRITE command.

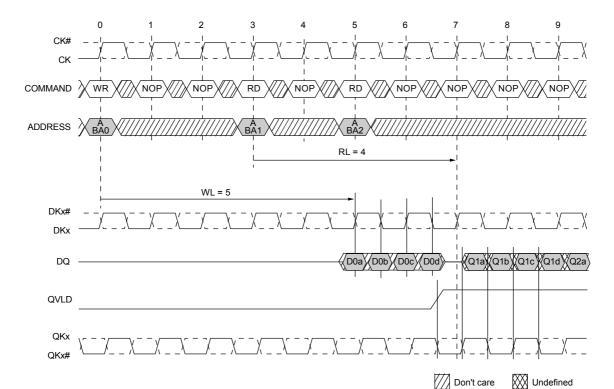

Any WRITE burst may be followed by a subsequent READ command. Figure 2-10. WRITE Followed By READ: BL=2, RL=4, WL=5, Configuration 1 and Figure 2-11. WRITE Followed By READ: BL=4, RL=4, WL=5, Configuration 1 illustrate the timing requirements for a WRITE followed by a READ for bursts of two and four, respectively.

Setup and hold times for incoming input data relative to the DK edges are specified as t<sub>DS</sub> and t<sub>DH</sub>. The input data is masked if the corresponding DM signal is HIGH. The setup and hold times for data mask are also t<sub>DS</sub> and t<sub>DH</sub>.

Figure 2-6. WRITE Command

Remark A: Address

BA: Bank address

Figure 2-7. Basic WRITE Burst / DM Timing

Figure 2-8. WRITE Burst Basic Sequence: BL=2, RL=4, WL=5, Configuration 1

Figure 2-9. WRITE Burst Basic Sequence: BL=4, RL=4, WL=5, Configuration 1

Remarks 1. WR : WRITE command A/Bap : Address A of bank p WL : WRITE latency

: Data q to bank p

Dpq

**2.** Any free bank may be used in any given command. The sequence shown is only one example of a bank sequence.

COMMAND ADDRESS X A RL = 4 (D0a)(D0b) DQ QVLD QKx ₩ Undefined Don't care

Figure 2-10. WRITE Followed By READ: BL=2, RL=4, WL=5, Configuration 1

Figure 2-11. WRITE Followed By READ: BL=4, RL=4, WL=5, Configuration 1

Remark

WR

WL RL

Dpq

: WRITE command : READ command A/BAp: Address A of bank p : WRITE latency

: READ latency

: Data q to bank p Qpq : Data q from bank p

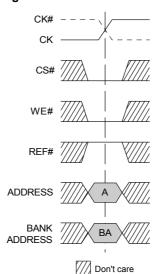

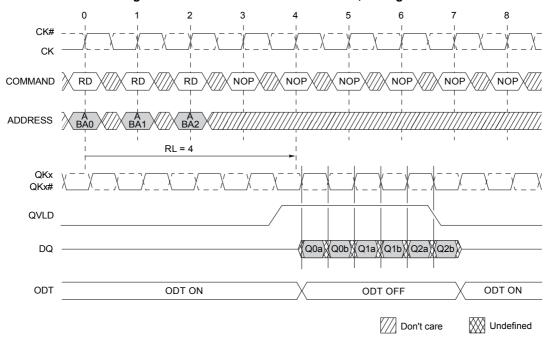

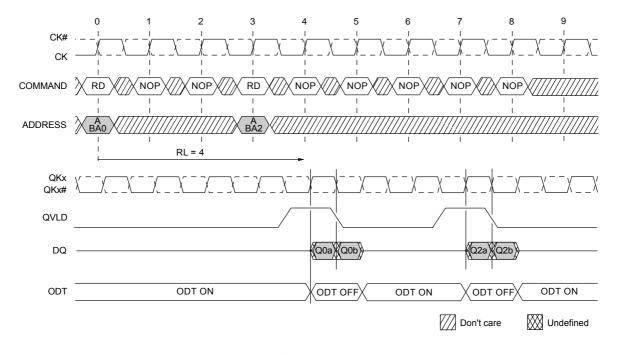

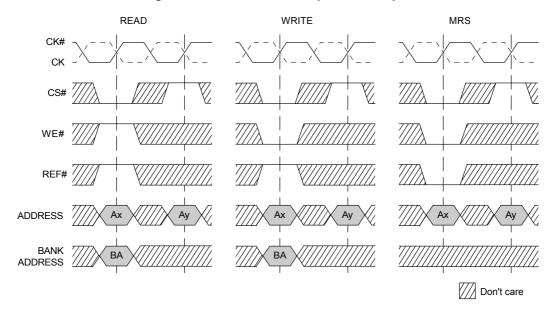

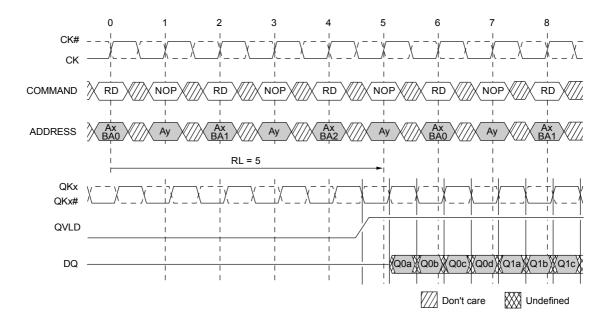

#### 2.11 Read Operation (READ)

Read accesses are initiated with a READ command, as shown in **Figure 2-12**. Row and bank addresses are provided with the READ command.

During READ bursts, the memory device drives the read data edge-aligned with the QK signal. After a programmable READ latency, data is available at the outputs. The data valid signal indicates that valid data will be present in the next half clock cycle.

The skew between QK and the crossing point of CK is specified as tCKQK. tQKQO is the skew between QKO and the last valid data edge considered the data generated at the DQ0–DQ17 in x36 and DQ0–DQ8 in x18 data signals. tQKQI is the skew between QK1 and the last valid data edge considered the data generated at the DQ18–DQ35 in x36 and DQ9–DQ17 in x18 data signals. tQKQx is derived at each QKx clock edge and is not cumulative over time.

After completion of a burst, assuming no other commands have been initiated, DQ will go High-Z. Back-to-back READ commands are possible, producing a continuous flow of output data.

Minimum READ data valid window can be expressed as MIN.(tokh, tokh) – 2 x MAX.(tokox)

Any READ burst may be followed by a subsequent WRITE command. Figure 2-16. READ followed by WRITE, BL=2, RL=4, WL=5, Configuration 1 and Figure 2-17. READ followed by WRITE, BL=4, RL=4, WL=5, Configuration 1 illustrate the timing requirements for a READ followed by a WRITE.

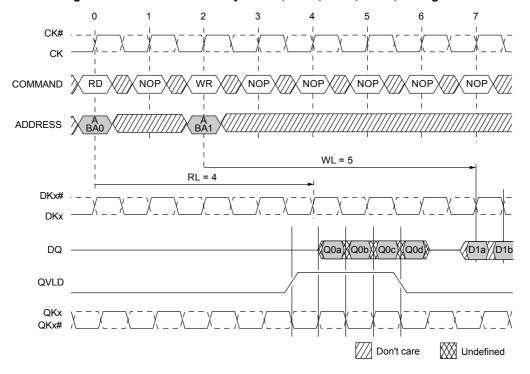

CK# ---CK

CS#

WE#

ADDRESS

BANK

ADDRESS

Don't care

Figure 2-12. READ Command

Remark A : Address

BA: Bank address

R10DS0254EJ0101 Rev. 1.01 Jan. 15, 2016

Figure 2-13. Basic READ Burst Timing

Note Minimum READ data valid window can be expressed as MIN.( $t_{QKH}$ ,  $t_{QKL}$ ) – 2 x MAX.( $t_{QKQx}$ ) tckh and tckl are recommended to have 50% / 50% duty.

- **Remarks** 1.  $t_{QKQ0}$  is referenced to DQ0–DQ17 in x36 and DQ0–DQ8 in x18.  $t_{QKQ1}$  is referenced to DQ18–DQ35 in x36 and DQ9–DQ17 in x18.

- 2. toko takes into account the skew between any QKx and any DQ.

- 3. tckqk is specified as CK rising edge to QK rising edge.

Undefined

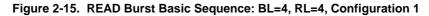

CK# CK COMMAND RD RD RD RD RD RD RD RD RD **RL = 4** QKx QKx# QVLD DQ Don't care Undefined

Figure 2-14. READ Burst Basic Sequence: BL=2, RL=4, Configuration 1

**Remark** RD : READ command

A/BAp : Address A of bank p

RL : READ latency

Qpq : Data q from bank p

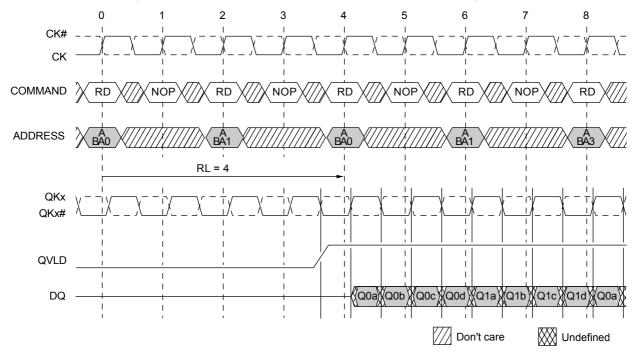

COMMAND > WR NOP NOP NOP NOP ADDRESS X A WL = 5 DKx# DKx D1a D1b D2a D2b DQ QVLD QKx QKx# Don't care Undefined

Figure 2-16. READ followed by WRITE, BL=2, RL=4, WL=5, Configuration 1

Figure 2-17. READ followed by WRITE, BL=4, RL=4, WL=5, Configuration 1

Remark WR : WRITE command

RD : READ command

A/BAp : Address A of bank p

WL : WRITE latency

RL : READ latency

Dpq : Data q to bank p

Qpq : Data q from bank p

#### 2.12 Refresh Operation: AUTO REFRESH Command (AREF)