## **Enhanced Product**

## FEATURES

#### 12-bit SAR ADC

8 single-ended analog input channels Analog input range: 0 V to 2.5 V 12-bit temperature to digital converter Temperature sensor accuracy of ±1°C typical Channel sequencer operation Specified for V<sub>DD</sub> of 2.8 V to 3.6 V Logic voltage V<sub>DRIVE</sub> = 1.65 V to 3.6 V Internal 2.5 V reference I<sup>2</sup>C-compatible serial interface supports standard and fast speed modes Out of range indicator/alert function Autocycle mode Power-down current: 13 μA maximum 20-lead LFCSP package

#### **ENHANCED PRODUCT FEATURES**

Supports defense and aerospace applications (AQEC standard) Extended industrial temperature range: -55°C to +125°C Controlled manufacturing baseline 1 assembly/test site 1 fabrication site Product change notification Qualification data available upon request

## **GENERAL DESCRIPTION**

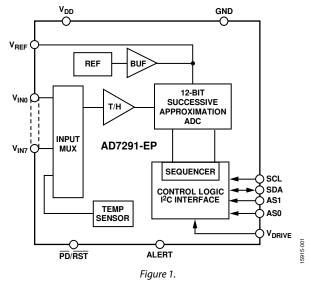

The AD7291-EP is a 12-bit, low power, 8-channel, successive approximation analog-to-digital converter (ADC) with an internal temperature sensor.

The device operates from a single 3.3 V power supply and features an  $I^2C$ -compatible interface. The device contains a 9-channel multiplexer and a track-and-hold amplifier with an input bandwidth of 30 MHz. The device has an on-chip 2.5 V reference that can be disabled to allow the use of an external reference.

The AD7291-EP provides a 2-wire serial interface compatible with I<sup>2</sup>C interfaces. The I<sup>2</sup>C interface supports standard and fast I<sup>2</sup>C interface modes. The AD7291-EP normally remains in a partial power-down state while not converting and powers up for conversions. The conversion process can be controlled by a command mode where conversions occur across I<sup>2</sup>C write operations or an autocycle mode selected through software control.

# 8-Channel, I<sup>2</sup>C, 12-Bit SAR ADC with Temperature Sensor

## AD7291-EP

#### FUNCTIONAL BLOCK DIAGRAM

The AD7291-EP includes a high accuracy band gap temperature sensor, which is monitored and digitized by the 12-bit ADC to give a resolution of 0.25°C.

The AD7291-EP offers a programmable sequencer, which enables the selection of a preprogrammable sequence of channels for conversion.

On-chip limit registers can be programmed with high and low limits for the conversion results; an out-of-range indicator output (ALERT) becomes active when the programmed high or low limits are violated by the conversion result. This output can be used as an interrupt.

Additional application and technical information can be found in the AD7291 data sheet.

Rev. 0

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2017 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## TABLE OF CONTENTS

| Features                  | 1 |

|---------------------------|---|

| Enhanced Product Features | 1 |

| Functional Block Diagram  | 1 |

| General Description       | 1 |

| Revision History          | 2 |

| Specifications            | 3 |

| Absolute Maximum Ratings  | 5 |

| Thermal Resistance5                          |

|----------------------------------------------|

| ESD Caution5                                 |

| Pin Configuration and Function Descriptions6 |

| Typical Performance Characteristics7         |

| Outline Dimensions                           |

| Ordering Guide8                              |

## **REVISION HISTORY**

7/2017—Revision 0: Initial Version

## **SPECIFICATIONS**

$V_{DD}$  = 2.8 V to 3.6 V;  $V_{DRIVE}$  = 1.65 V to 3.6 V;  $f_{SCL}$  = 400 kHz, fast SCLK mode;  $V_{REF}$  = 2.5 V internal/external;  $T_A$  = -55°C to +125°C, unless otherwise noted.

| Parameter                                       | Min                           | Тур   | Max                           | Unit <sup>1</sup> | Test Conditions/Comments                       |

|-------------------------------------------------|-------------------------------|-------|-------------------------------|-------------------|------------------------------------------------|

| DYNAMIC PERFORMANCE                             |                               |       |                               |                   | $f_{IN} = 1 \text{ kHz}$ sine wave             |

| Signal-to-Noise Ratio (SNR)                     | 70                            | 71    |                               | dB                |                                                |

| Signal-to-Noise + Distortion Ratio (SINAD)      | 70                            | 71    |                               | dB                |                                                |

| Total Harmonic Distortion (THD)                 |                               | -84   | -78                           | dB                |                                                |

| Spurious-Free Dynamic Range (SFDR)              |                               | -85   | -80                           | dB                |                                                |

| Intermodulation Distortion (IMD)                |                               |       |                               |                   | $f_A = 5.4 \text{ kHz}, f_B = 4.6 \text{ kHz}$ |

| Second-Order Terms                              |                               | -88   |                               | dB                |                                                |

| Third-Order Terms                               |                               | -88   |                               | dB                |                                                |

| Channel-to-Channel Isolation                    |                               | -100  |                               | dB                | $f_{IN} = 10 \text{ kHz}$                      |

| Full Power Bandwidth <sup>2</sup>               |                               | 30    |                               | MHz               | At 3 dB                                        |

|                                                 |                               | 10    |                               | MHz               | At 0.1 dB                                      |

| DC ACCURACY                                     |                               |       |                               |                   |                                                |

| Resolution                                      | 12                            |       |                               | Bits              |                                                |

| Integral Nonlinearity (INL)                     |                               | ±0.5  | ±1                            | LSB               |                                                |

| Differential Nonlinearity (DNL)                 |                               | ±0.5  | ±0.99                         | LSB               | Guaranteed no missing codes to 12 bits         |

| Offset Error                                    |                               | ±2    | ±4.5                          | LSB               |                                                |

| Offset Error Matching                           |                               | ±2.5  | ±4.5                          | LSB               |                                                |

| Offset Temperature Drift                        |                               | 4     |                               | ppm/°C            |                                                |

| Gain Error                                      |                               | ±1    | ±4                            | LSB               |                                                |

| Gain Error Matching                             |                               | ±1    | ±2.5                          | LSB               |                                                |

| Gain Temperature Drift                          |                               | 0.5   |                               | ppm/°C            |                                                |

| ANALOG INPUT                                    |                               |       |                               |                   |                                                |

| Input Voltage Ranges                            | 0                             |       | V <sub>REF</sub>              | V                 |                                                |

| DC Leakage Current                              |                               | ±0.01 | ±1                            | μΑ                |                                                |

| Input Capacitance <sup>2</sup>                  |                               | 34    |                               | pF                | When in track                                  |

|                                                 |                               | 8     |                               | pF                | When in hold                                   |

| REFERENCE INPUT/OUTPUT                          |                               |       |                               |                   |                                                |

| Reference Output Voltage <sup>3</sup>           | 2.4925                        | 2.5   | 2.5075                        | V                 | ±0.3% maximum at 25°C                          |

| Long-Term Stability                             |                               | 150   |                               | ppm               | For 1000 hours                                 |

| Output Voltage Hysteresis                       |                               | 50    |                               | ppm               |                                                |

| Reference Input Voltage Range <sup>4</sup>      | 1                             |       | 2.5                           | V                 |                                                |

| DC Leakage Current                              |                               | ±0.01 | ±1                            | μΑ                | External reference applied to $Pin V_{REF}$    |

| V <sub>REF</sub> Output Impedance               |                               | 1     |                               | Ω                 |                                                |

| Reference Temperature Coefficient               |                               | 12    | 35                            | ppm/°C            |                                                |

| V <sub>REF</sub> Noise <sup>2</sup>             |                               | 60    |                               | μV rms            | Bandwidth = 10 MHz                             |

| LOGIC INPUTS (SDA, SCL)                         |                               |       |                               |                   |                                                |

| Input High Voltage, V <sub>INH</sub>            | $0.7 	imes V_{\text{DRIVE}}$  |       |                               | V                 |                                                |

| Input Low Voltage, VINL                         |                               |       | $0.3 \times V_{\text{DRIVE}}$ | V                 |                                                |

| Input Current, I <sub>IN</sub>                  |                               | ±0.01 | ±1                            | μΑ                | $V_{IN} = 0 V \text{ or } V_{DRIVE}$           |

| Input Capacitance, C <sub>IN</sub> <sup>2</sup> |                               | 6     |                               | pF                |                                                |

| Input Hysteresis, V <sub>HYST</sub>             | $0.1 \times V_{\text{DRIVE}}$ |       |                               | V                 |                                                |

## AD7291-EP

| Parameter                                      | Min                      | Тур   | Max   | Unit <sup>1</sup> | <b>Test Conditions/Comments</b>               |

|------------------------------------------------|--------------------------|-------|-------|-------------------|-----------------------------------------------|

| LOGIC OUTPUTS                                  |                          |       |       |                   |                                               |

| Output High Voltage, V <sub>он</sub>           | $V_{\text{DRIVE}} - 0.3$ |       |       | V                 | V <sub>DRIVE</sub> < 1.8                      |

|                                                | $V_{\text{DRIVE}} - 0.2$ |       |       | V                 | $V_{\text{DRIVE}} \ge 1.8$                    |

| Output Low Voltage, Vol                        |                          |       | 0.4   | V                 | I <sub>SINK</sub> = 3 mA                      |

|                                                |                          |       | 0.6   | V                 | I <sub>SINK</sub> = 6 mA                      |

| Floating State Leakage Current                 |                          | ±0.01 | ±1    | μΑ                |                                               |

| Floating State Output Capacitance <sup>2</sup> |                          | 8     |       | pF                |                                               |

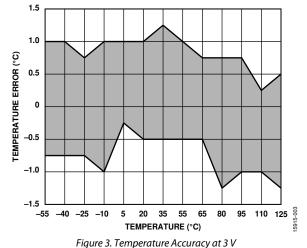

| INTERNAL TEMPERATURE SENSOR                    |                          |       |       |                   |                                               |

| Operating Range                                | -55                      |       | +125  | °C                |                                               |

| Accuracy                                       |                          | ±1    | ±2    | °C                | $T_A = -55^{\circ}C \text{ to } +85^{\circ}C$ |

|                                                |                          | ±1    | ±3    | °C                | $T_A = 85^{\circ}C \text{ to } 125^{\circ}C$  |

| Resolution                                     |                          | 0.25  |       | °C                | LSB size                                      |

| CONVERSION RATE                                |                          |       |       |                   |                                               |

| Conversion Time                                |                          | 3.2   |       | μs                |                                               |

| Autocycle Update Rate <sup>5</sup>             |                          | 50    |       | μs                |                                               |

| Throughput Rate                                |                          |       | 22.22 | kSPS              | $f_{SCL} = 400 \text{ kHz}$                   |

| POWER REQUIREMENTS                             |                          |       |       |                   | Digital inputs = $0 V \text{ or } V_{DRIVE}$  |

| V <sub>DD</sub>                                | 2.8                      | 3     | 3.6   | V                 |                                               |

| V <sub>DRIVE</sub>                             | 1.65                     | 3     | 3.6   | V                 |                                               |

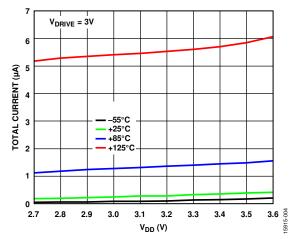

| ITOTAL <sup>6, 7</sup>                         |                          |       |       |                   |                                               |

| Normal Mode (Operational)                      |                          | 2.9   | 3.5   | mA                |                                               |

| Normal Mode (Static)                           |                          | 2.9   | 3.4   | mA                |                                               |

| Full Power-Down Mode                           |                          | 0.3   | 1.6   | μA                | $T_A = -55^{\circ}C$ to $+25^{\circ}C$        |

|                                                |                          | 1.6   | 4.5   | μΑ                | $T_A = >25^{\circ}C$ to $85^{\circ}C$         |

|                                                |                          | 4.9   | 13    | μΑ                | $T_A = >85^{\circ}C$ to 125°C                 |

| Power Dissipation <sup>7</sup>                 |                          |       |       |                   |                                               |

| Normal Mode (Operational)                      |                          | 8.7   | 10.5  | mW                | $V_{DD} = 3 V$ , $V_{DRIVE} = 3 V$            |

|                                                |                          | 10.4  | 12.6  | mW                |                                               |

| Normal Mode (Static)                           |                          | 10.4  | 12.2  | mW                |                                               |

| Full Power-Down Mode                           |                          | 1.1   | 5.8   | μW                | $T_A = -55^{\circ}C$ to $+25^{\circ}C$        |

|                                                |                          | 5.8   | 16.2  | μW                | $T_A = >25^{\circ}C$ to $85^{\circ}C$         |

|                                                |                          | 17.6  | 46.8  | μW                | $T_A = >85^{\circ}C$ to 125°C                 |

<sup>1</sup> All specifications expressed in decibels are referred to full-scale range (FSR) and tested with an input signal at 0.5 dB below full scale, unless otherwise specified. <sup>2</sup> Sample tested during initial product release to ensure compliance. <sup>3</sup> Refers to Pin V<sub>REF</sub> specified for 25°C.

<sup>4</sup> A correction factor can be required on the temperature sensor results when using an external V<sub>REF</sub> (see the AD7291 data sheet).

<sup>5</sup> Sampled during initial product release to ensure compliance; not subject to production testing.

$^{6}$  I<sub>TOTAL</sub> is the total current flowing in V<sub>DD</sub> and V<sub>DRIVE</sub>.  $^{7}$  I<sub>TOTAL</sub> and power dissipation are specified with V<sub>DD</sub> = V<sub>DRIVE</sub> = 3.6 V, unless otherwise noted.

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| Parameter                                             | Rating                                  |

|-------------------------------------------------------|-----------------------------------------|

| V <sub>DD</sub> to GND1, GND                          | –0.3 V to +5 V                          |

| V <sub>DRIVE</sub> to GND1, GND                       | –0.3 V to +5 V                          |

| Analog Input Voltage to GND1                          | –0.3 V to +3 V                          |

| Digital Input Voltage to GND1                         | $-0.3V$ to $V_{\text{DRIVE}}$ + 0.3 $V$ |

| Digital Output Voltage to GND1                        | $-0.3V$ to $V_{\text{DRIVE}}+0.3V$      |

| V <sub>REF</sub> to GND1                              | –0.3 V to +3 V                          |

| GND to GND1                                           | –0.3 V to +0.3 V                        |

| Input Current to Any Pin Except Supplies <sup>1</sup> | ±10 mA                                  |

| Operating Temperature Range                           | –55°C to +125°C                         |

| Storage Temperature Range                             | –65°C to +150°C                         |

| Junction Temperature                                  | 150°C                                   |

| Pb-free Temperature, Soldering                        |                                         |

| Reflow                                                | 260(+0)°C                               |

| ESD                                                   | 2 kV                                    |

<sup>1</sup> Transient currents of up to 100 mA do not cause latch-up.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## THERMAL RESISTANCE

Thermal performance is directly linked to printed circuit board (PCB) design and operating environment. Close attention to PCB thermal design is required.

#### Table 3. Thermal Resistance

| Package Type         | θ <sub>JA</sub> | θ」  | Unit |

|----------------------|-----------------|-----|------|

| CP-20-8 <sup>1</sup> | 52              | 6.5 | °C/W |

<sup>1</sup> Thermal impedance simulated values are based on JEDEC 2S2P thermal test board with 9 thermal vias. See JEDEC JESD51.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

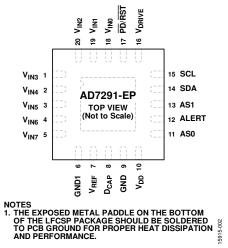

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

Figure 2. Pin Configuration

#### **Table 4. Pin Function Descriptions**

| Pin No.             | Mnemonic                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 5,<br>18 to 20 | V1N3, V1N4,<br>V1N5, V1N6,<br>V1N7, V1N0,<br>V1N1, V1N2 | Analog Inputs. The AD7291-EP has eight single-ended analog inputs that are multiplexed into the on-chip track-<br>and-hold amplifier. Each input channel can accept analog inputs from 0 V to 2.5 V. Any unused input channels<br>must be connected to GND1 to avoid noise pickup.                                                                                                                                                                                                                                                                                                                                                  |

| 6                   | GND1                                                    | Ground. Ground reference point for the internal reference circuitry on the AD7291-EP. All analog input signals and the external reference signals must be referred to this GND1 voltage. The GND1 pin must be connected to the ground plane of a system. All ground pins must ideally be at the same potential and must not be more than 0.3 V apart, even on a transient basis. The V <sub>REF</sub> pin must be decoupled to this ground pin via a 10 µF decoupling capacitor.                                                                                                                                                    |

| 7                   | Vref                                                    | Internal Reference/External Reference Supply. The nominal internal reference voltage of 2.5 V appears at this pin.<br>Provided the output is buffered, the on-chip reference can be taken from this pin and applied externally to the rest<br>of a system. Decoupling capacitors must be connected to this pin to decouple the reference buffer. For best<br>performance, it is recommended to use a 10 µF decoupling capacitor on this pin to GND1. The internal reference<br>can be disabled and an external reference supplied to this pin if required. The input voltage range for the external<br>reference is 2.0 V to 2.5 V. |

| 8                   | Dcap                                                    | Decoupling Capacitor Pin. Decoupling capacitors (1 μF recommended) are connected to this pin to decouple the internal low dropout regulator (LDO).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9                   | GND                                                     | Ground. Ground reference point for all analog and digital circuitry on the AD7291-EP. The GND pin must be con-<br>nected to the ground plane of the system. All ground pins must ideally be at the same potential and must not be<br>more than 0.3 V apart, even on a transient basis. Both D <sub>CAP</sub> and V <sub>DD</sub> pins must be decoupled to this GND pin.                                                                                                                                                                                                                                                            |

| 10                  | V <sub>DD</sub>                                         | Supply Voltage, 2.8 V to 3.6 V. This supply must be decoupled to GND with 10 μF and 100 nF decoupling capacitors.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 11, 13              | AS0, AS1                                                | Logic Inputs. Together, the logic state of these two inputs selects a unique I <sup>2</sup> C address for the AD7291-EP. See the AD7291 data sheet for details. The device address depends on the voltage applied to these pins.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12                  | ALERT                                                   | Digital Output. This pin acts as an out-of-range indicator and, if enabled, becomes active when the conversion result violates the DATA <sub>HIGH</sub> or DATA <sub>LOW</sub> register values. See the AD7291 data sheet for further details.                                                                                                                                                                                                                                                                                                                                                                                      |

| 14                  | SDA                                                     | Digital Input/Output. Serial bus bidirectional data. This open-drain output requires a pull-up resistor. The output coding is straight binary for the voltage channels and twos complement for the temperature sensor result.                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15                  | SCL                                                     | Digital Inputs. Serial I <sup>2</sup> C Bus Clock. This input requires a pull-up resistor. The data transfer rate in I <sup>2</sup> C mode is compatible with both 100 kHz and 400 kHz operating modes.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 16                  | V <sub>DRIVE</sub>                                      | Logic Power Supply Input. The voltage supplied at this pin determines the voltage at which the interface operates. This pin must be decoupled to GND. The voltage range on this pin is 1.65 V to 3.6 V and can be less than the voltage at V <sub>DD</sub> but must never exceed it by more than 0.3 V.                                                                                                                                                                                                                                                                                                                             |

| 17                  | PD/RST                                                  | Power-Down Pin. This pin places the device into a full power-down mode and enables power conservation when operation is not required. This pin can be used to reset the device by toggling the pin low for a minimum of 1 ns and a maximum of 100 ns. If the maximum time is exceeded, the device enters power-down mode. When placing the device in full power-down mode, the analog inputs must be returned to 0 V.                                                                                                                                                                                                               |

| EPAD                | EPAD                                                    | Exposed Pad. The exposed metal paddle on the bottom of the LFCSP package must be soldered to PCB ground for proper functionality and heat dissipation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Figure 4. Full Shutdown Current vs. Supply Voltage for Various Temperatures

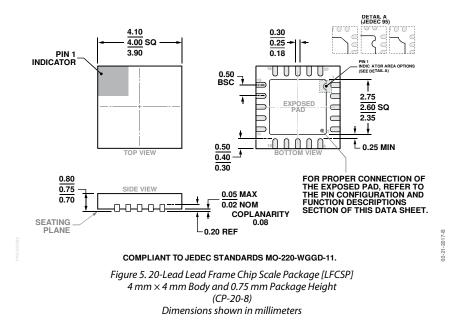

## **OUTLINE DIMENSIONS**

## **ORDERING GUIDE**

| Model <sup>1</sup> Temperature Range Package Desc |                 | Package Description                           | Package Option |

|---------------------------------------------------|-----------------|-----------------------------------------------|----------------|

| AD7291TCPZ-EP                                     | –55°C to +125°C | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-8        |

| AD7291TCPZ-EP-RL7                                 | –55°C to +125°C | 20-Lead Lead Frame Chip Scale Package [LFCSP] | CP-20-8        |

<sup>1</sup> Z = RoHS Compliant Part.

I<sup>2</sup>C refers to a communications protocol originally developed by Philips Semiconductors (now NXP Semiconductors).

©2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D15915-0-7/17(0)

www.analog.com

Rev. 0 | Page 8 of 8