### Intel<sup>®</sup> 975X Express Chipset

Datasheet

For the Intel<sup>®</sup> 82975X Memory Controller Hub (MCH)

November 2005

Document Number: 310158-001

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 82975X Memory Controller Hub (MCH) may contain design defects or errors known as errata, which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

<sup>1</sup>Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a Hyper-Threading Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/info/hyperthreading/ for more information including details on which processors support HT Technology.

Intel and Pentium are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright<sup>©</sup> 2005, Intel Corporation

### **Contents**

| 1 | Introd | luction                                                                                                                        | 15 |

|---|--------|--------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1    | Terminology                                                                                                                    | 17 |

|   | 1.2    | Reference Documents                                                                                                            | 18 |

|   | 1.3    | MCH Overview                                                                                                                   | 19 |

|   |        | 1.3.1 Host Interface                                                                                                           | 19 |

|   |        | 1.3.2 System Memory Interface                                                                                                  |    |

|   |        | 1.3.3 PCI Express* Graphics Interface                                                                                          |    |

|   |        | 1.3.4 Bifurcated PCI Express* Graphics Supported Features                                                                      |    |

|   |        | 1.3.5 Direct Media Interface (DMI)                                                                                             |    |

|   |        | 1.3.6 System Interrupts<br>1.3.7 MCH Clocking                                                                                  |    |

|   |        | <ul><li>1.3.7 MCH Clocking</li><li>1.3.8 Power Management</li></ul>                                                            |    |

| 0 | Ciana  |                                                                                                                                |    |

| Ζ | •      | al Description                                                                                                                 |    |

|   | 2.1    | Host Interface Signals                                                                                                         |    |

|   | 2.2    | DDR2 DRAM Channel A Interface                                                                                                  |    |

|   | 2.3    | DDR2 DRAM Channel B Interface                                                                                                  |    |

|   | 2.4    | DDR2 DRAM Reference and Compensation                                                                                           |    |

|   | 2.5    | PCI Express* Interface Signals                                                                                                 |    |

|   | 2.6    | Clocks, Reset, and Miscellaneous                                                                                               | 33 |

|   | 2.7    | Direct Media Interface (DMI)                                                                                                   |    |

|   | 2.8    | Power, Ground                                                                                                                  |    |

|   | 2.9    | Reset States and Pull-up/Pull-down Values                                                                                      | 34 |

| 3 | MCH    | Register Description                                                                                                           |    |

|   | 3.1    | Register Terminology                                                                                                           | 40 |

|   | 3.2    | Platform Configuration                                                                                                         |    |

|   | 3.3    | Configuration Mechanisms                                                                                                       |    |

|   |        | 3.3.1 Standard PCI Configuration Mechanism                                                                                     |    |

|   |        | 3.3.2 PCI Express* Enhanced Configuration Mechanism                                                                            |    |

|   | 3.4    | Routing Configuration Accesses                                                                                                 | 45 |

|   |        | 3.4.1 Internal Device Configuration Accesses                                                                                   | 46 |

|   |        | 3.4.2 Bridge Related Configuration Accesses                                                                                    |    |

|   |        | 3.4.2.1 PCI Express* Configuration Accesses                                                                                    |    |

|   |        | 3.4.2.2 DMI Configuration Accesses                                                                                             |    |

|   | 3.5    | I/O Mapped Registers                                                                                                           |    |

|   |        | <ul> <li>3.5.1 CONFIG_ADDRESS—Configuration Address Register</li> <li>3.5.2 CONFIG_DATA—Configuration Data Register</li> </ul> |    |

| 4 | 110-41 |                                                                                                                                |    |

| 4 |        | Bridge Registers (D0:F0)                                                                                                       |    |

|   | 4.1    | Configuration Register Details (D1:F0)                                                                                         |    |

|   |        | 4.1.1 VID—Vendor Identification (D0:F0)                                                                                        | 53 |

|   |        |                                                                                                                                |    |

| 4.1.2            | DID—Device Identification (D0:F0)                                    | 53 |

|------------------|----------------------------------------------------------------------|----|

| 4.1.2            |                                                                      |    |

| -                | PCICMD—PCI Command (D0:F0)                                           |    |

| 4.1.4            | PCISTS—PCI Status (D0:F0)                                            | 55 |

| 4.1.5            | RID—Revision Identification (D0:F0)                                  |    |

| 4.1.6            | CC—Class Code (D0:F0)                                                | 56 |

| 4.1.7            | MLT—Master Latency Timer (D0:F0)                                     |    |

| 4.1.8            | HDR—Header Type (D0:F0)                                              | 57 |

| 4.1.9            | SVID—Subsystem Vendor Identification (D0:F0)                         |    |

| 4.1.10           | SID—Subsystem Identification (D0:F0)                                 | 58 |

| 4.1.11           | CAPPTR—Capabilities Pointer (D0:F0)                                  |    |

| 4.1.12           | EPBAR—Egress Port Base Address (D0:F0)                               | 59 |

| 4.1.13           | MCHBAR—MCH Memory Mapped Register Range Base Address (D0:F0)         | 60 |

| 4.1.14           | PCIEXBAR—PCI Express* Register Range Base Address (D0:F0)            |    |

| 4.1.15           | DMIBAR—Root Complex Register Range Base Address (D0:F0)              |    |

| 4.1.16           | DEVEN—Device Enable (D0:F0)                                          |    |

| 4.1.17           | DEAP—DRAM Error Address Pointer (D0:F0)                              |    |

| 4.1.18           | DERRSYN— DRAM Error Syndrome (D0:F0)                                 |    |

| 4.1.19           | DERRDST—DRAM Error Destination (D0:F0)                               |    |

| 4.1.20           | PAM0—Programmable Attribute Map 0 (D0:F0)                            |    |

| 4.1.21           | PAM1—Programmable Attribute Map 0 (D0:F0)                            |    |

| 4.1.22           | PAM2—Programmable Attribute Map 1 (D0:F0)                            |    |

| 4.1.23           | PAM3—Programmable Attribute Map 2 (D0:F0)                            |    |

| 4.1.24           | PAM4—Programmable Attribute Map 3 (D0:F0)                            |    |

| 4.1.24           | PAM4—Programmable Attribute Map 4 (D0.P0)                            |    |

| 4.1.26           | PAM6—Programmable Attribute Map 6 (D0:F0)                            |    |

| 4.1.20           | LAC—Legacy Access Control (D0:F0)                                    |    |

| 4.1.27           | REMAPBASE—Remap Base Address (D0:F0)                                 |    |

| 4.1.20           | REMAPLIMIT—Remap Limit Address (D0:F0)                               |    |

| 4.1.29           | TOLUD—Top of Low Usable DRAM (D0:F0)                                 |    |

| 4.1.30           | SMRAM—System Management RAM Control (D0:F0)                          |    |

| 4.1.31           | ESMRAM—System Management RAM Control (D0.F0)                         |    |

| 4.1.32           | TOM—Top of Memory (D0:F0).                                           |    |

| 4.1.33           |                                                                      |    |

| -                | ERRSTS—Error Status (D0:F0)                                          |    |

| 4.1.35<br>4.1.36 | ERRCMD—Error Command (D0:F0)                                         |    |

|                  | SMICMD—SMI Command (D0:F0)                                           |    |

| 4.1.37           | SCICMD—SCI Command (D0:F0)                                           |    |

| 4.1.38<br>4.1.39 | SKPD—Scratchpad Data (D0:F0)<br>CAPID0—Capability Identifier (D0:F0) |    |

| 4.1.39           |                                                                      |    |

|                  | EDEAP—Extended DRAM Error Address Pointer (D0:F0)                    |    |

|                  | Register                                                             |    |

| 4.2.1            | C0DRB0—Channel A DRAM Rank Boundary Address 0                        |    |

| 4.2.2            | C0DRB1—Channel A DRAM Rank Boundary Address 1                        |    |

| 4.2.3            | C0DRB2—Channel A DRAM Rank Boundary Address 2                        |    |

| 4.2.4            | C0DRB3—Channel A DRAM Rank Boundary Address 3                        |    |

| 4.2.5            | C0DRA0—Channel A DRAM Rank 0,1 Attribute                             |    |

| 4.2.6            | C0DRA2—Channel A DRAM Rank 2, 3 Attribute                            |    |

| 4.2.7            | CODCLKDIS—Channel A DRAM Clock Disable                               |    |

| 4.2.8            | C0BNKARC—Channel A DRAM Bank Architecture                            |    |

| 4.2.9            | C0DRT1—Channel 0 DRAM Timing Register                                |    |

| 4.2.10           | C0DRC0—Channel 0 DRAM Controller Mode 0                              |    |

| 4.2.11           | C0DRC1—Channel 0 DRAM Controller Mode 1                              |    |

| 4.2.12           | C1DRB0—Channel B DRAM Rank Boundary Address 0                        | 93 |

|                  |                                                                      |    |

4.2

|        | 4.2.13     | C1DRB1—Channel B DRAM Rank Boundary Address 1               | 93  |

|--------|------------|-------------------------------------------------------------|-----|

|        | 4.2.14     | C1DRB2—Channel B DRAM Rank Boundary Address 2               | 93  |

|        | 4.2.15     | C1DRB3—Channel B DRAM Rank Boundary Address 3               | 94  |

|        | 4.2.16     | C1DRA0—Channel B DRAM Rank 0,1 Attribute                    | 94  |

|        | 4.2.17     | C1DRA2—Channel B DRAM Rank 2,3 Attribute                    | 94  |

|        | 4.2.18     | C1DCLKDIS—Channel B DRAM Clock Disable                      |     |

|        | 4.2.19     | C1BNKARC—Channel B Bank Architecture                        | 94  |

|        | 4.2.20     | C1DRT1—Channel 1 DRAM Timing Register 1                     | 95  |

|        | 4.2.21     | C1DRC0—Channel 1 DRAM Controller Mode 0                     |     |

|        | 4.2.22     | C1DRC1—Channel 1 DRAM Controller Mode 1                     |     |

|        | 4.2.23     | PMCFG—Power Management Configuration                        |     |

|        | 4.2.24     | PMSTS—Power Management Status                               |     |

| 4.3    | EPBAR      | Registers—Egress Port Register Summary                      |     |

| -      | 4.3.1      | EPESD—EP Element Self Description                           |     |

|        | 4.3.2      | EPLE1D—EP Link Entry 1 Description                          |     |

|        | 4.3.3      | EPLE1A—EP Link Entry 1 Address                              |     |

|        | 4.3.4      | EPLE2D—EP Link Entry 2 Description                          |     |

|        | 4.3.5      | EPLE2A—EP Link Entry 2 Address                              |     |

|        | 4.3.6      | EPLE3D—EP Link Entry 3 Description                          | 102 |

|        | 4.3.7      | EPLE2A—EP Link Entry 3 Address                              | 103 |

|        |            |                                                             |     |

| Host-I | Primary PC | CI Express* Bridge Registers (D1:F0)                        | 105 |

| 5.1    | Configur   | ation Register Details (D1:F0)                              | 109 |

|        | 5.1.1      | VID1—Vendor Identification (D1:F0)                          | 109 |

|        | 5.1.2      | DID1—Device Identification (D1:F0)                          | 109 |

|        | 5.1.3      | PCICMD1—PCI Command (D1:F0)                                 |     |

|        | 5.1.4      | PCISTS1—PCI Status (D1:F0)                                  |     |

|        | 5.1.5      | RID1—Revision Identification (D1:F0)                        |     |

|        | 5.1.6      | CC1—Class Code (D1:F0)                                      |     |

|        | 5.1.7      | CL1—Cache Line Size (D1:F0)                                 |     |

|        | 5.1.8      | HDR1—Header Type (D1:F0)                                    |     |

|        | 5.1.9      | PBUSN1—Primary Bus Number (D1:F0)                           |     |

|        | 5.1.10     | SBUSN1—Secondary Bus Number (D1:F0)                         |     |

|        | 5.1.11     | SUBUSN1—Subordinate Bus Number (D1:F0)                      |     |

|        | 5.1.12     | IOBASE1—I/O Base Address (D1:F0)                            |     |

|        | 5.1.13     | IOLIMIT1—I/O Limit Address (D1:F0)                          |     |

|        | 5.1.14     | SSTS1—Secondary Status (D1:F0)                              |     |

|        | 5.1.15     | MBASE1—Memory Base Address (D1:F0)                          |     |

|        | 5.1.16     | MLIMIT1—Memory Limit Address (D1:F0)                        |     |

|        | 5.1.17     | PMBASE1—Prefetchable Memory Base Address (D1:F0)            |     |

|        | 5.1.18     | PMLIMIT1—Prefetchable Memory Limit Address (D1:F0)          |     |

|        | 5.1.19     | PMBASEU1—Prefetchable Memory Base Address                   |     |

|        | 5.1.20     | PMLIMITU1— Prefetchable Memory Limit Address                |     |

|        | 5.1.21     | CAPPTR1—Capabilities Pointer (D1:F0)                        |     |

|        | 5.1.22     | INTRLINE1—Interrupt Line (D1:F0)                            | 124 |

|        | 5.1.23     | INTRPIN1—Interrupt Pin (D1:F0)                              |     |

|        | 5.1.24     | BCTRL1—Bridge Control (D1:F0)                               |     |

|        | 5.1.25     | PM_CAPID1—Power Management Capabilities (D1:F0)             |     |

|        | 5.1.26     | PM CS1—Power Management Control/Status (D1:F0)              |     |

|        | 5.1.27     | SS_CAPID—Subsystem ID and Vendor ID Capabilities (D1:F0)    |     |

|        | 5.1.28     | SS—Subsystem ID and Subsystem Vendor ID (D1:F0)             |     |

|        | 5.1.29     | MSI CAPID—Message Signaled Interrupts Capability ID (D1:F0) |     |

|        | 5.1.30     | MC—Message Control (D1:F0)                                  |     |

|        |            |                                                             |     |

|         | 5.1.31    | MA—Message Address (D1:F0)                                | 132 |

|---------|-----------|-----------------------------------------------------------|-----|

|         | 5.1.32    | MD—Message Data (D1:F0)                                   |     |

|         | 5.1.33    | PEGCAPL—PCI Express* Capability List (D1:F0)              | 133 |

|         | 5.1.34    | PCI_EXPRESS _CAP—PCI Express* Capabilities (D1:F0)        |     |

|         | 5.1.35    | DCAP—Device Capabilities (D1:F0)                          |     |

|         | 5.1.36    | DCTL—Device Control (D1:F0)                               |     |

|         | 5.1.37    | DSTS—Device Status (D1:F0)                                |     |

|         | 5.1.38    | LCAP—Link Capabilities (D1:F0)                            | 137 |

|         | 5.1.39    | LCTL—Link Control (D1:F0)                                 | 138 |

|         | 5.1.40    | LSTS—Link Status (D1:F0)                                  | 139 |

|         | 5.1.41    | SLOTCAP—Slot Capabilities (D1:F0)                         | 140 |

|         | 5.1.42    | SLOTCTL—Slot Control (D1:F0)                              |     |

|         | 5.1.43    | SLOTSTS—Slot Status (D1:F0)                               |     |

|         | 5.1.44    | RCTL—Root Control (D1:F0)                                 | 143 |

|         | 5.1.45    | RSTS—Root Status (D1:F0)                                  |     |

|         | 5.1.46    | PEGLC—PCI Express* Legacy Control (D1:F0)                 |     |

|         | 5.1.47    | VCECH—Virtual Channel Enhanced Capability Header (D1:F0)  |     |

|         | 5.1.48    | PVCCAP1—Port VC Capability Register 1 (D1:F0)             |     |

|         | 5.1.49    | PVCCAP2—Port VC Capability Register 2 (D1:F0)             |     |

|         | 5.1.50    | PVCCTL—Port VC Control (D1:F0)                            |     |

|         | 5.1.51    | VC0RCAP—VC0 Resource Capability (D1:F0)                   |     |

|         | 5.1.52    | VC0RCTL—VC0 Resource Control (D1:F0)                      |     |

|         | 5.1.53    | VC0RSTS—VC0 Resource Status (D1:F0)                       | 150 |

|         | 5.1.54    | VC1RCAP—VC1 Resource Capability (D1:F0)                   | 150 |

|         | 5.1.55    | VC1RCTL—VC1 Resource Control (D1:F0)                      | 151 |

|         | 5.1.56    | VC1RSTS—VC1 Resource Status (D1:F0)                       | 152 |

|         | 5.1.57    | RCLDECH—Root Complex Link Declaration Enhanced Capability | 102 |

|         | 0.1.07    | Header (D1:F0)                                            | 152 |

|         | 5.1.58    | ESD—Element Self Description (D1:F0)                      |     |

|         | 5.1.59    | LE1D—Link Entry 1 Description (D1:F0)                     | 154 |

|         | 5.1.60    | LE1A—Link Entry 1 Address (D1:F0)                         | 154 |

|         | 5.1.61    | LE2D—Link Entry 2 Description (D1:F0)                     | 155 |

|         | 5.1.62    | LE2A— Link Entry 2 Address                                |     |

|         | 5.1.63    | UESTS—Uncorrectable Error Status (D1:F0)                  |     |

|         | 5.1.64    | UEMSK—Uncorrectable Error Mask (D1:F0)                    | 158 |

|         | 5.1.65    | CESTS—Correctable Error Status (D1:F0)                    |     |

|         | 5.1.66    | CEMSK—Correctable Error Mask (D1:F0)                      |     |

|         | 5.1.67    | PEGSSTS—PCI Express* Sequence Status (D1:F0)              |     |

|         |           |                                                           |     |

| Host-Se | econdary  | PCI Express* Bridge Registers (D3:F0)                     | 163 |

| 6.1     | Configura | ation Register Details (D3:F0)                            | 166 |

|         | 6.1.1     | VID3—Vendor Identification (D3:F0)                        |     |

|         | 6.1.2     | DID3—Device Identification (D3:F0)                        |     |

|         | 6.1.3     | PCICMD3—PCI Command (D3:F0)                               |     |

|         | 6.1.4     | PCISTS3—PCI Status (D3:F0)                                |     |

|         | 6.1.5     | RID3—Revision Identification (D3:F0)                      |     |

|         | 6.1.6     | CC3—Class Code (D3:F0)                                    |     |

|         | 6.1.7     | CL3—Cache Line Size (D3:F0)                               |     |

|         | 6.1.8     | HDR3—Header Type (D3:F0)                                  |     |

|         | 6.1.9     | PBUSN3—Primary Bus Number (D3:F0)                         |     |

|         | 6.1.10    | SBUSN3—Secondary Bus Number (D3:F0)                       | 168 |

|         | 6.1.10    | SUBUSN3—Subordinate Bus Number (D3:F0)                    | 168 |

|         | 6.1.12    | IOBASE3—I/O Base Address (D3:F0)                          |     |

|         | 0.1.12    | 10070LJ-10 Dase Audiess (DJ.FU)                           | 109 |

|                                                                     | 400   |

|---------------------------------------------------------------------|-------|

| 6.1.13 IOLIMIT3—I/O Limit Address (D3:F0)                           |       |

| 6.1.14 SSTS3—Secondary Status (D3:F0)                               |       |

| 6.1.15 MBASE3—Memory Base Address (D3:F0)                           |       |

| 6.1.16 MLIMIT3—Memory Limit Address (D3:F0)                         |       |

| 6.1.17 PMBASE3—Prefetchable Memory Base Address (D3:F0)             |       |

| 6.1.18 PMLIMIT3—Prefetchable Memory Limit Address (D3:F0)           |       |

| 6.1.19 PMBASEU3—Prefetchable Memory Base Address                    | 170   |

| 6.1.20 PMLIMITU3— Prefetchable Memory Limit Address                 | 171   |

| 6.1.21 CAPPTR3—Capabilities Pointer (D3:F0)                         |       |

| 6.1.22 INTRLINE3—Interrupt Line (D3:F0)                             |       |

| 6.1.23 INTRPIN3—Interrupt Pin (D3:F0)                               |       |

| 6.1.24 BCTRL3—Bridge Control (D3:F0)                                |       |

| 6.1.25 PM_CAPID3—Power Management Capabilities (D3:F0)              |       |

| 6.1.26 PM_CS3—Power Management Control/Status (D3:F0)               |       |

| 6.1.27 SS_CAPID3—Subsystem ID and Vendor ID Capabilities (D3:F0).   |       |

|                                                                     |       |

| 6.1.28 SS3—Subsystem ID and Subsystem Vendor ID (D3:F0)             |       |

| 6.1.29 MSI_CAPID3—Message Signaled Interrupts Capability ID (D3:F0) | ) 173 |

| 6.1.30 MC3—Message Control (D3:F0)                                  |       |

| 6.1.31 MA3—Message Address (D3:F0)                                  |       |

| 6.1.32 MD3—Message Data (D3:F0)                                     |       |

| 6.1.33 PEGCAPL3—PCI Express* Capability List (D3:F0)                |       |

| 6.1.34 PCI_EXPRESS _CAP3—PCI Express* Capabilities (D3:F0)          | 174   |

| 6.1.35 DCAP3—Device Capabilities (D3:F0)                            | 174   |

| 6.1.36 DCTL3—Device Control (D3:F0)                                 | 175   |

| 6.1.37 DSTS3—Device Status (D3:F0)                                  | 175   |

| 6.1.38 LCAP3—Link Capabilities (D3:F0)                              |       |

| 6.1.39 LCTL3—Link Control (D3:F0)                                   |       |

| 6.1.40 LSTS3—Link Status (D3:F0)                                    |       |

| 6.1.41 SLOTCAP3—Slot Capabilities (D3:F0)                           | 177   |

| 6.1.42 SLOTCTL3—Slot Control (D3:F0)                                | 177   |

| 6.1.43 SLOTSTS3—Slot Status (D3:F0)                                 |       |

|                                                                     |       |

|                                                                     |       |

| 6.1.45 RSTS3—Root Status (D3:F0)                                    |       |

| 6.1.46 PEGLC3—PCI Express* Legacy Control (D3:F0)                   |       |

| 6.1.47 VCECH3—Virtual Channel Enhanced Capability Header (D3:F0).   |       |

| 6.1.48 PVCCAP31—Port VC Capability Register 1 (D3:F0)               | 178   |

| 6.1.49 PVCCAP32—Port VC Capability Register 2 (D3:F0)               | 178   |

| 6.1.50 PVCCTL3—Port VC Control (D3:F0)                              | 179   |

| 6.1.51 VC0RCAP3—VC0 Resource Capability (D3:F0)                     | 179   |

| 6.1.52 VC0RCTL3—VC0 Resource Control (D3:F0)                        |       |

| 6.1.53 VC0RSTS3—VC0 Resource Status (D3:F0)                         |       |

| 6.1.54 VC1RCAP3—VC1 Resource Capability (D3:F0)                     | 179   |

| 6.1.55 VC1RCTL3—VC1 Resource Control (D3:F0)                        | 180   |

| 6.1.56 VC1RSTS3—VC1 Resource Status (D3:F0)                         | 180   |

| 6.1.57 RCLDECH3—Root Complex Link Declaration Enhanced Capabilit    |       |

| Header (D3:F0)                                                      |       |

| 6.1.58 ESD3—Element Self Description (D3:F0)                        |       |

| 6.1.59 LE1D3—Link Entry 1 Description (D3:F0)                       |       |

| 6.1.60 LE1A3—Link Entry 1 Address (D3:F0)                           |       |

| 6.1.61 LE2D3—Link Entry 2 Description (D3:F0)                       |       |

| 6.1.62 LE2A3— Link Entry 2 Address (D3:F0)                          | 183   |

| 6.1.63 UESTS3—Uncorrectable Error Status (D3:F0)                    | 192   |

| 6.1.64 UEMSK3—Uncorrectable Error Mask (D3:F0)                      |       |

| 0.1.07 OLIVIONO-ONCONCLADIC ENDIVIDENT (D3.FU)                      | 105   |

|       | 6.1.65<br>6.1.66<br>6.1.67 | CESTS3—Correctable Error Status (D3:F0)<br>CEMSK3—Correctable Error Mask (D3:F0)<br>PEGSSTS3—PCI Express* Sequence Status (D3:F0) | 184 |

|-------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-----|

|       |                            |                                                                                                                                   |     |

|       |                            | erface (DMI) RCRB                                                                                                                 |     |

| 7.1   |                            | RB Configuration Register Details                                                                                                 |     |

|       | 7.1.1                      | DMIVCECH—DMI Virtual Channel Enhanced Capability Header .                                                                         |     |

|       | 7.1.2                      | DMIPVCCAP1—DMI Port VC Capability Register 1                                                                                      |     |

|       | 7.1.3                      | DMIPVCCAP2—DMI Port VC Capability Register 2                                                                                      |     |

|       | 7.1.4                      | DMIPVCCTL—DMI Port VC Control                                                                                                     |     |

|       | 7.1.5<br>7.1.6             | DMIVC0RCAP—DMI VC0 Resource Capability<br>DMIVC0RCTL0—DMI VC0 Resource Control                                                    |     |

|       | 7.1.7                      | DMIVCORSTS—DMI VCO Resource Status                                                                                                |     |

|       | 7.1.7                      | DMIVC1RCAP—DMI VC0 Resource Capability                                                                                            |     |

|       | 7.1.9                      | DMIVC1RCTL1—DMI VC1 Resource Control                                                                                              |     |

|       | 7.1.10                     | DMIVC1RSTS—DMI VC1 Resource Status                                                                                                |     |

|       | 7.1.11                     | DMILCAP—DMI Link Capabilities                                                                                                     |     |

|       | 7.1.12                     | DMILCTL—DMI Link Control                                                                                                          |     |

|       | 7.1.13                     | DMILSTS—DMI Link Status                                                                                                           |     |

|       | 7.1.14                     | DMIUESTS—DMI Uncorrectable Error Status                                                                                           |     |

|       | 7.1.15                     | DMIUEMSK—DMI Uncorrectable Error Mask                                                                                             | 194 |

|       | 7.1.16                     | DMICESTS— DMI Correctable Error Status                                                                                            | 195 |

| Syste | m Address                  | з Мар                                                                                                                             | 197 |

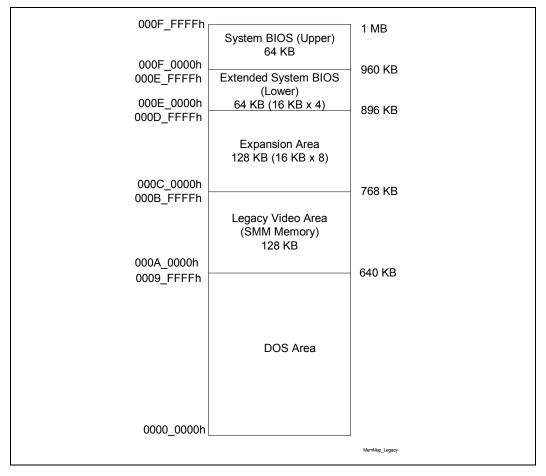

| 8.1   | Legacy                     | Address Range                                                                                                                     | 200 |

|       | 8.1.1                      | DOS Range (0h-9_FFFFh)                                                                                                            | 200 |

|       | 8.1.2                      | Legacy Video Area (A_0000h–B_FFFFh)                                                                                               | 201 |

|       | 8.1.3                      | Expansion Area (C_0000h–D_FFFFh)                                                                                                  | 202 |

|       | 8.1.4                      | Extended System BIOS Area (E_0000h–E_FFFFh)                                                                                       | 202 |

|       | 8.1.5                      | System BIOS Area (F_0000h–F_FFFFh)                                                                                                |     |

|       | 8.1.6                      | Programmable Attribute Map (PAM) Memory Area Details                                                                              |     |

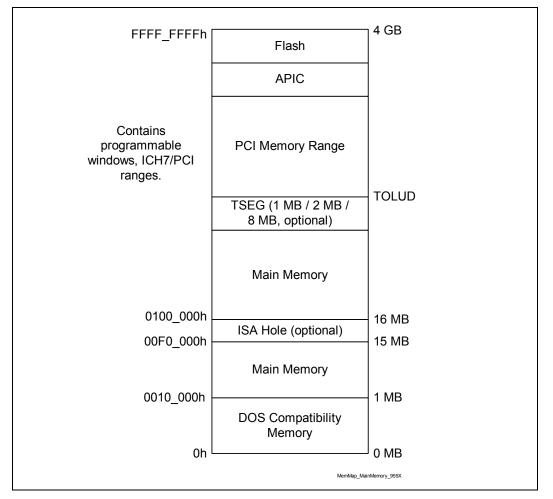

| 8.2   |                            | emory Address Range (1 MB to TOLUD)                                                                                               |     |

|       | 8.2.1                      | ISA Hole (15 MB–16 MB)                                                                                                            |     |

|       | 8.2.2                      | TSEG                                                                                                                              |     |

|       | 8.2.3                      | Pre-allocated Memory                                                                                                              |     |

| 8.3   |                            | mory Address Range (TOLUD–4 GB)                                                                                                   |     |

|       | 8.3.1                      | APIC Configuration Space (FEC0_0000h-FECF_FFFFh)                                                                                  | 206 |

|       | 8.3.2                      | HSEG (FEDA_0000h-FEDB_FFFFh)<br>FSB Interrupt Memory Space (FEE0_0000-FEEF_FFFF)                                                  | 207 |

|       | 8.3.3                      |                                                                                                                                   |     |

| ~ .   | 8.3.4                      | High BIOS Area                                                                                                                    |     |

| 8.4   |                            | emory Address Space (4 GB to Remaplimit)                                                                                          |     |

|       | 8.4.1                      | Memory Re-claim Background                                                                                                        |     |

|       | 8.4.2                      | Memory Re-mapping                                                                                                                 |     |

|       | 8.4.3                      | PCI Express* Configuration Address Space                                                                                          |     |

|       | 8.4.4                      | PCI Express* Graphics Attach                                                                                                      |     |

| 0 F   | 8.4.5<br>Sustant           | AGP DRAM Graphics Aperture                                                                                                        |     |

| 8.5   | •                          | Management Mode (SMM)                                                                                                             |     |

|       | 8.5.1                      | SMM Space Definition                                                                                                              |     |

|       | 8.5.2                      | SMM Space Restrictions                                                                                                            |     |

|       | 8.5.3<br>8 5 4             | SMM Control Combinations                                                                                                          |     |

|       | 8.5.4<br>8.5.5             | SMM Control Combinations                                                                                                          |     |

|       | 8.5.5                      | SMM Space Decode and Transaction Handling                                                                                         |     |

7

8

|    |          | 8.5.6      |               | WB Transaction to an Enabled SMM Address Space    |       |

|----|----------|------------|---------------|---------------------------------------------------|-------|

|    |          | 8.5.7      |               | hadowing                                          |       |

|    |          | 8.5.8      |               | ss Space                                          |       |

|    |          | 8.5.9      |               | ss* I/O Address Mapping                           |       |

|    |          | 8.5.10     |               | ode Rules and Cross-Bridge Address Mapping        |       |

|    |          | 8.5.11     | Legacy VC     | GA and I/O Range Decode Rules                     | 214   |

| 9  | Functio  | onal Descr | ription       |                                                   | 215   |

|    | 9.1      | Host Inte  | rface         |                                                   | 215   |

|    |          | 9.1.1      | FSB IOQ I     | Depth                                             | 215   |

|    |          | 9.1.2      | FSB OOQ       | Depth                                             | 215   |

|    |          | 9.1.3      | FSB GTL+      | - Termination                                     | 215   |

|    |          | 9.1.4      | FSB Dyna      | mic Bus Inversion                                 | 215   |

|    |          |            | 9.1.4.1       | APIC Cluster Mode Support                         | 216   |

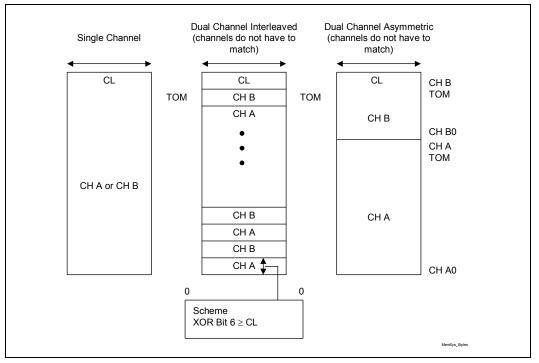

|    | 9.2      | System N   | Memory Co     | ntroller                                          | 217   |

|    |          | 9.2.1      |               | emory Configuration Registers Overview            |       |

|    |          | 9.2.2      | DRAM Te       | chnologies and Organization                       | 219   |

|    |          | •          | 9.2.2.1       | Rules for Populating DIMM Slots                   |       |

|    |          |            | 9.2.2.2       | System Memory Supported Configurations            |       |

|    |          |            | 9.2.2.3       | Main Memory DRAM Address Translation and Decoding |       |

|    |          |            | 9.2.2.4       | ECC Support                                       |       |

|    |          | 9.2.3      | DRAM Clo      | bck Generation                                    |       |

|    |          | 9.2.4      |               | Γο RAM and Resume                                 |       |

|    |          | 9.2.5      |               | Die Termination                                   |       |

|    | 9.3      |            |               |                                                   |       |

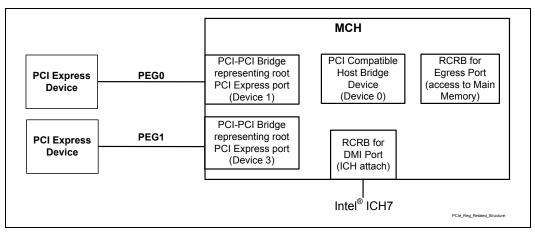

|    | 0.0      | 9.3.1      |               | ss* Architecture                                  |       |

|    |          | 9.5.1      | 9.3.1.1       | Transaction Layer                                 |       |

|    |          |            | 9.3.1.1       | Data Link Layer                                   |       |

|    |          |            | 9.3.1.2       | Physical Layer                                    |       |

|    | 0.4      | Difurente  |               |                                                   |       |

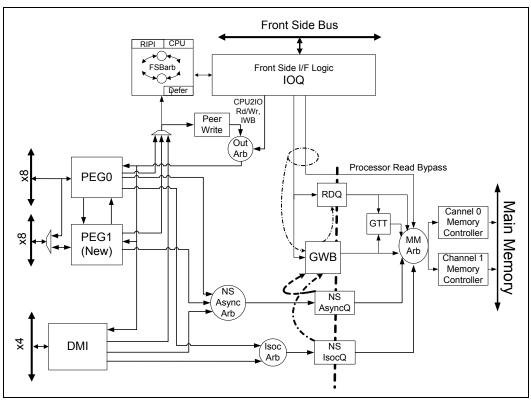

|    | 9.4      |            | •             | ess* Graphics                                     |       |

|    |          | 9.4.1      |               | lions                                             |       |

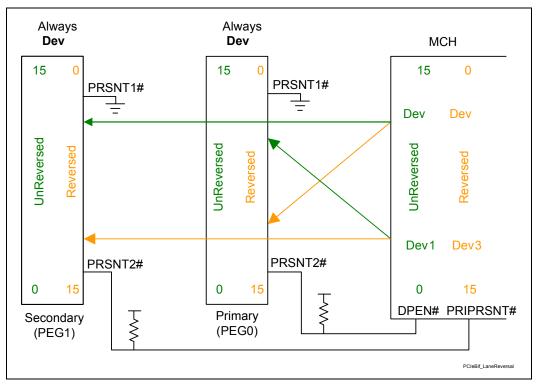

|    |          | 9.4.2      |               | ersal                                             |       |

|    |          | 9.4.3      | •             | ss* Straps                                        |       |

|    |          |            | 9.4.3.1       | Bifurcated PCI Express* Indication                |       |

|    |          |            | 9.4.3.2       | Primary Slot Device Present Indication            |       |

|    |          | 9.4.4      |               | PCI Express* Decode Rules                         |       |

|    |          | 9.4.5      |               | irmware Considerations                            |       |

|    |          | 9.4.6      |               | eer                                               |       |

|    |          | 9.4.7      |               | eer Bandwidth                                     |       |

|    |          | 9.4.8      |               | eer Latency                                       |       |

|    |          | 9.4.9      |               | aration Topology                                  |       |

|    |          | 9.4.10     | •             | ss* Interrupt and GPE Flow                        |       |

|    | 9.5      |            |               | ions                                              |       |

|    | 9.6      | Power M    | anagement     | t                                                 | 234   |

|    | 9.7      | Clocking   |               |                                                   | 234   |

| 10 | Electric | cal Charac | teristics     |                                                   | 237   |

|    | 10.1     | Absolute   | Minimum a     | and Maximum Ratings                               | 237   |

|    | 10.2     |            |               | CS                                                |       |

|    | 10.2     |            |               |                                                   |       |

|    |          | -          | -             |                                                   |       |

|    | 10.4     | DC Char    | acteristics . |                                                   | . 242 |

| 11 |

|----|

|----|

12

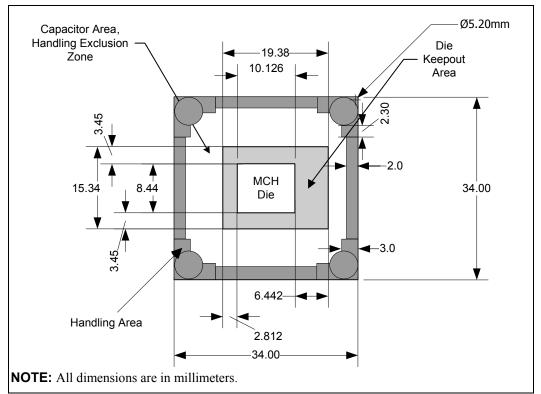

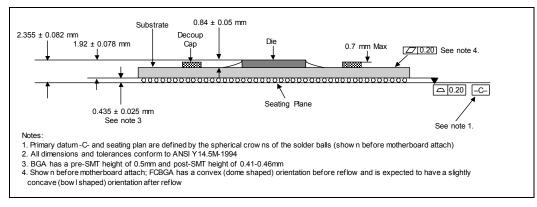

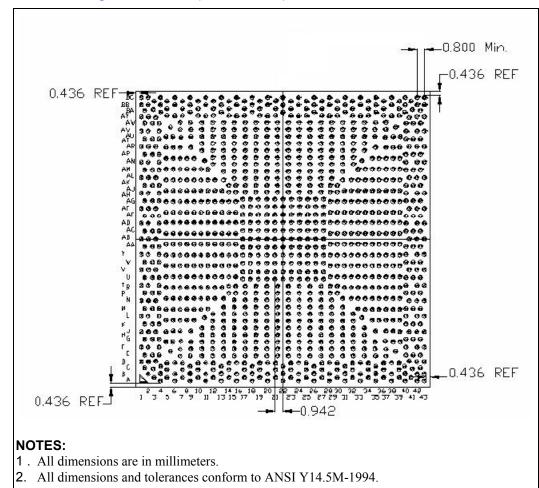

| Ballout | and Package Information        | 245 |

|---------|--------------------------------|-----|

| 11.1    | Ballout                        | 245 |

| 11.2    | Package                        | 261 |

| Testab  | ility                          | 263 |

| 12.1    | Complimentary Pins             | 263 |

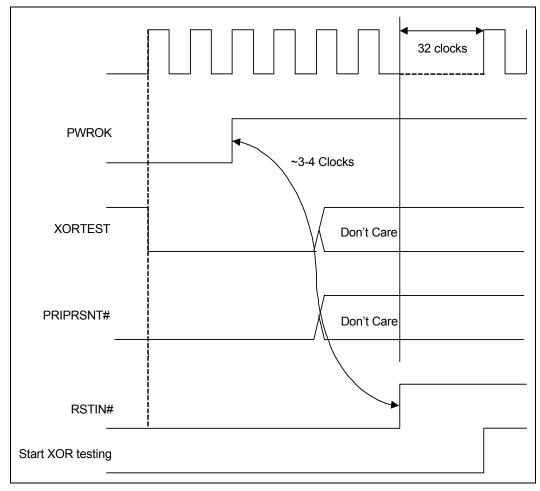

| 12.2    | XOR Test Mode Initialization   | 264 |

| 12.3    | XOR Chain Definition           | 265 |

| 12.4    | XOR Chains                     | 265 |

| 12.5    | PADs Excluded from XOR Mode(s) | 274 |

|         |                                |     |

### **Figures**

| <b>J · · · · · · · · · · · · · · · · · · ·</b>                                                    | 16  |

|---------------------------------------------------------------------------------------------------|-----|

|                                                                                                   | 26  |

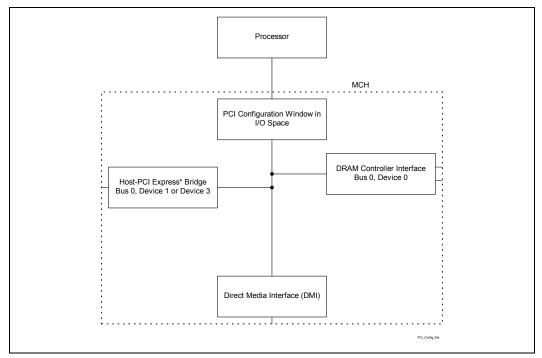

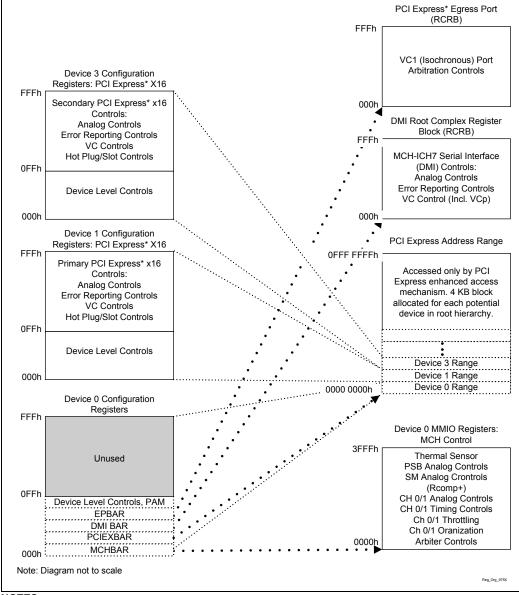

| Figure 3-1. Conceptual Intel <sup>®</sup> 975X Express Chipset Platform PCI Configuration Diagram | n41 |

| Figure 3-2. Register Organization                                                                 | 12  |

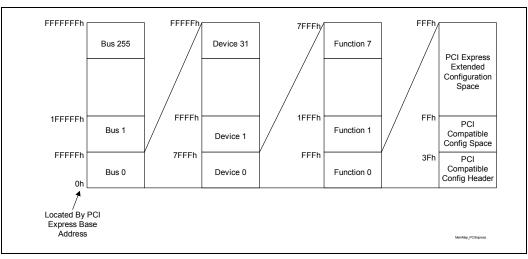

| Figure 3-3. Memory Map to PCI Express* Device Configuration Space                                 | 14  |

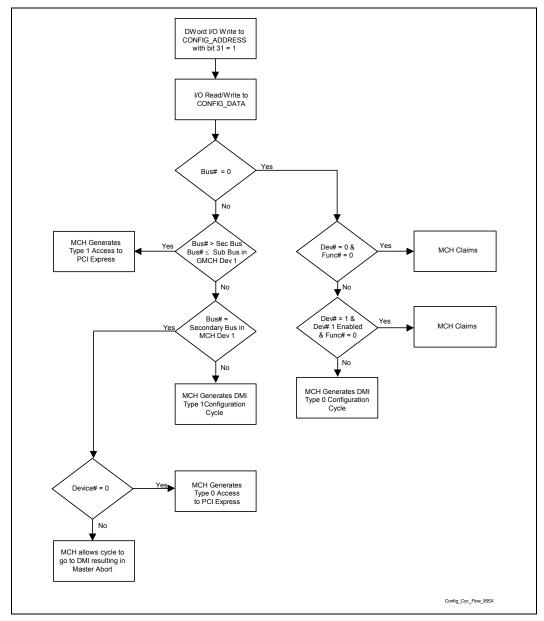

| Figure 3-4. MCH Configuration Cycle Flow Chart                                                    | 15  |

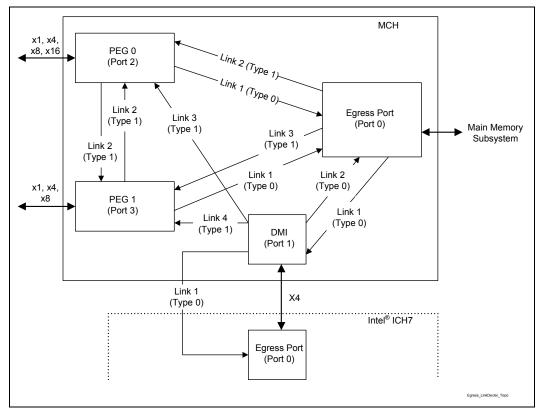

| Figure 4-1. Link Declaration Topology                                                             |     |

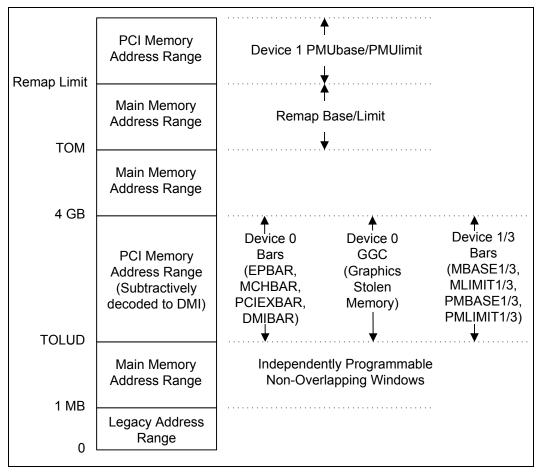

| Figure 8-1. System Address Ranges                                                                 |     |

| Figure 8-2. Microsoft MS-DOS* Legacy Address Range                                                |     |

| Figure 8-3. Main Memory Address Range                                                             |     |

| Figure 8-4. PCI Memory Address Range                                                              | )6  |

| Figure 9-1. System Memory Styles                                                                  | 18  |

| Figure 9-2. PCI Express* Related Register Structures in MCH                                       | 24  |

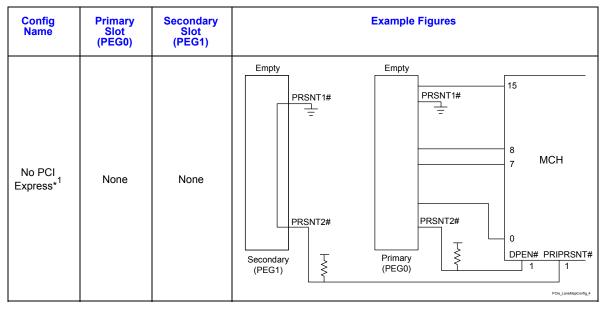

| Figure 9-3. Lane Reversal (Bifurcated PCI Express* Configuration Example)                         | 27  |

| Figure 9-4. Bifurcated PCI Express* Microarchitecture                                             | 31  |

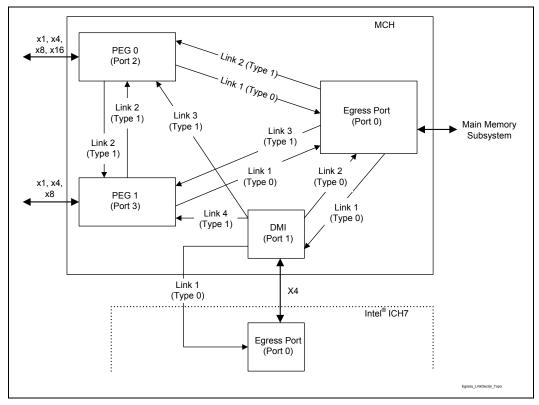

| Figure 9-5. Link Declaration Topology                                                             | 33  |

| Figure 9-6. Platform Clocking Example                                                             | 35  |

| Figure 11-1. Intel <sup>®</sup> 82975X MCH Ballout Diagram (Top View – Columns 43–30)24           | 16  |

| Figure 11-2. Intel <sup>®</sup> 82975X MCH Ballout Diagram (Top View – Columns 29–16)24           | 47  |

| Figure 11-3. Intel <sup>®</sup> 82975X MCH Ballout Diagram (Top View – Columns 15–1)              | 18  |

| Figure 11-4. MCH Package Dimensions (Top View)                                                    |     |

| Figure 11-5. MCH Package Dimensions (Side View)                                                   | 31  |

| Figure 11-6. MCH Package Dimensions (Bottom View)                                                 |     |

| Figure 12-1. XOR Test Mode Initialization Cycles                                                  |     |

### **Tables**

| Table 4-1. Host Bridge Register Address Map (D0:F0)                                   |     |

|---------------------------------------------------------------------------------------|-----|

| Table 4-2. MCHBAR Register Address Map                                                |     |

| Table 4-3. Egress Port Register Address Map                                           |     |

| Table 5-1. Host-PCI Express* Graphics Bridge Register Address Map (D1:F0)             | 105 |

| Table 6-1. Host-PCI Express* Graphics Bridge Register Address Map (D3:F0)             |     |

| Table 7-1. DMI Register Address Map                                                   |     |

| Table 8-1. Expansion Area Memory Segments                                             | 202 |

| Table 8-2. Extended System BIOS Area Memory Segments                                  | 202 |

| Table 8-3. System BIOS Area Memory Segments                                           | 203 |

| Table 8-4. Pre-Allocated Memory Example for 64-MB DRAM, 1-MB VGA and 1-MB             |     |

| TSEG                                                                                  | 205 |

| Table 8-5. SMM Space                                                                  | 211 |

| Table 8-6. SMM Control                                                                | 212 |

| Table 9-1. Sample System Memory Organization with Interleaved Channels                | 217 |

| Table 9-2. Sample System Memory Organization with Asymmetric Channels                 | 217 |

| Table 9-3. DDR2 DIMM Supported Configurations                                         |     |

| Table 9-4. DRAM Address Translation (Single Channel/Dual Asymmetric Mode)             | 221 |

| Table 9-5. DRAM Address Translation (Dual Channel Symmetric Mode)                     | 221 |

| Table 9-6. Lane Mapping Configurations for PCI Express* Graphics                      |     |

|                                                                                       |     |

| Table 9-7. Strap Combinations         Table 9-8. Peer-to-Peer Bandwidths <sup>1</sup> | 232 |

| Table 10-1. Absolute Minimum and Maximum Ratings                                      | 237 |

| Table 10-2. Non Memory Power Characteristics                                          |     |

| Table 10-3. DDR2 Power Characteristics                                                | 239 |

| Table 10-4. Signal Groups                                                             |     |

| Table 10-5. DČ Characteristics                                                        |     |

| Table 11-1. Intel <sup>®</sup> 82975X MCH Ballout – Sorted by Signal Name             | 249 |

| Table 12-1. Complimentary Pins to Drive                                               |     |

| Table 12-2. XOR Chain Outputs                                                         | 265 |

| Table 12-3. XOR Chain 0                                                               | 266 |

| Table 12-4. XOR Chain 1                                                               | 267 |

| Table 12-5. XOR Chain 2                                                               | 268 |

| Table 12-6. XOR Chain 3                                                               | 268 |

| Table 12-7. XOR Chain 4                                                               | 269 |

| Table 12-8. XOR Chain 5                                                               |     |

| Table 12-9. XOR Chain 6                                                               | 271 |

| Table 12-10. XOR Chain 7                                                              | 272 |

| Table 12-11. XOR Chain 8                                                              |     |

| Table 12-12. XOR Chain 9                                                              |     |

| Table 12-13. XOR Pad Exclusion List                                                   |     |

|                                                                                       |     |

### **Revision History**

| Rev  | Rev Description |               |

|------|-----------------|---------------|

| -001 | Initial Release | November 2005 |

§

### Intel<sup>®</sup> 82975X MCH Features

- Processor Interface

- —One Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor in the 90 nm process in the LGA775 Land Grid Array package, Intel<sup>®</sup> Pentium<sup>®</sup> D processor, or Intel<sup>®</sup> Pentium processor Extreme Edition (supports 775-Land package)

- Supports Pentium 4 processor FSB interrupt delivery

- Supports Hyper-Threading Technology<sup>1</sup> (HT Technology)

- -FSB Dynamic Bus Inversion (DBI)

- 36-bit host bus addressing for access to 8 GB of memory space

- -12-deep In-Order Queue

- 1-deep Defer Queue

- ---GTL+ bus driver with integrated GTL termination resistors

- -Supports a Cache Line Size of 64 bytes

- DMI Interface

- A chip-to-chip connection interface to Intel<sup>®</sup> ICH7

- -2 GB/s point-to-point DMI to ICH7 (1 GB/s each direction)

- 100 MHz reference clock (shared with PCI Express\* Graphics Attach).

- 32-bit downstream addressing

- -Messaging and Error Handling

- Bifurcated PCI Express\* Graphics Interface

- Bifurcated PCI Express\* Graphics x8 supported.

- Single PCI Express\* Graphics x16 supported.

- -Peer-to-Peer Writes

- --- Compatible with the PCI Express Base Specification, Revision 1.0a

- Raw bit rate on data pins of 2.5 Gb/s resulting in a real bandwidth per pair of 250 MB/s

- System Memory

- One or two 64-bit wide DDR2 SDRAM data channels

- DDR2 memory DIMM frequencies of 533 MHz and 667 MHz

- Bandwidth up to 10.7 GB/s (DDR2 667) in dual-channel Interleaved mode

- -ECC and Non-ECC memory

- 256-Mb, 512-Mb and 1-Gb DDR2 technologies

- Only x8, x16, DDR2 devices with four banks and also supports eight bank, 1-Gbit DDR2 devices.

- -Unbuffered DIMMs only

- -Page sizes of 4 KB, 8 KB, and 16 KB

- -Opportunistic refresh

- Up to 64 simultaneously open pages (four ranks of eight bank devices\* 2 channels)

- SPD (Serial Presence Detect) scheme for DIMM detection support

- --- Supports partial writes to memory, only when not using ECC

- -Suspend-to-RAM support using CKE

- -Supports configurations defined in the

- JEDEC DDR2 DIMM specification only

- Package

- 34 mm × 34 mm., 1202 balls, non-grid pattern

### **1** Introduction

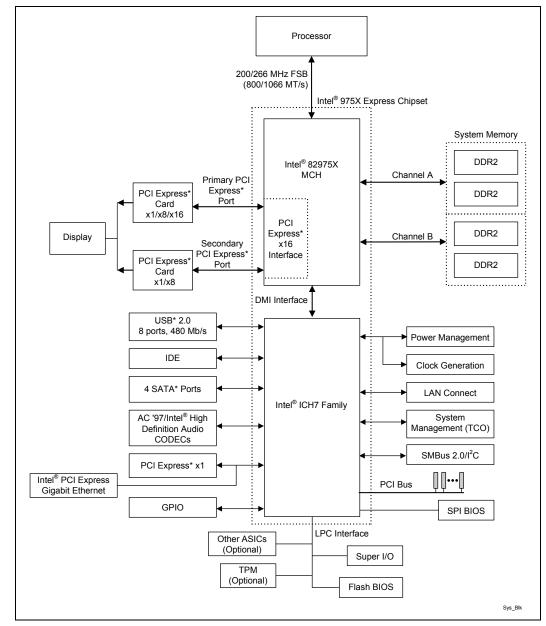

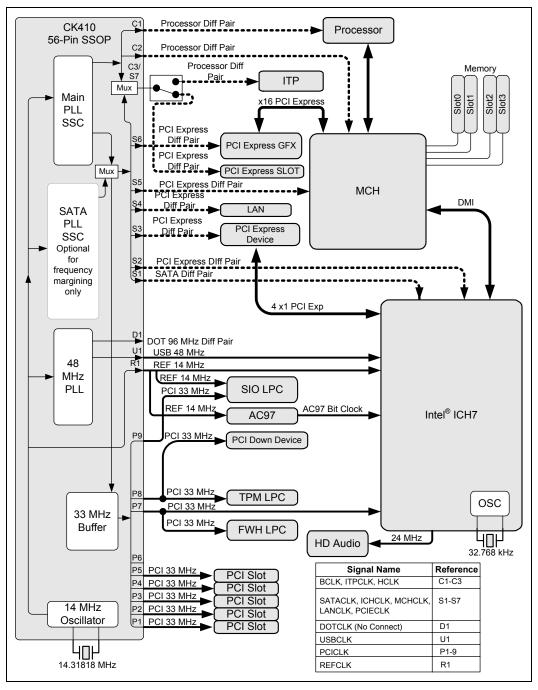

The Intel<sup>®</sup> 975X Express chipset is designed for use with Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor in the 90 nm process in the LGA775 Land Grid Array package, Intel<sup>®</sup> Pentium<sup>®</sup> D processor, and Intel<sup>®</sup> Pentium<sup>®</sup> processor Extreme Edition processor-based platforms. The chipset contains two components: Intel<sup>®</sup> 82975X Memory Controller Hub (MCH) for the host bridge and I/O Controller Hub 7 (ICH7) for the I/O subsystem. The MCH provides the interface to the processor, main memory, PCI Express\*, and the ICH7. The ICH7 is the seventh generation I/O Controller Hub and provides a multitude of I/O related functions. Figure 1-1 shows an example system block diagram for the Intel<sup>®</sup> 975X Express chipset.

This document is the datasheet for the Intel<sup>®</sup> 82975X MCH. Topics covered include; signal description, system memory map, register descriptions, a description of the MCH interfaces and major functional units, electrical characteristics, ballout definitions, and package characteristics.

*Note:* Unless otherwise specified, ICH7 refers to the Intel<sup>®</sup> 82801GB ICH7 and 82801GR ICH7R I/O Controller Hub components.

#### Figure 1-1. Intel<sup>®</sup> 975X Express Chipset System Block Diagram Example

### 1.1 Terminology

| Term                                  | Description                                                                                                                                                                                                                                                                                                                                          |  |  |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Accelerated<br>Graphics Port<br>(AGP) | Refers to the AGP/PCI interface that was previously in the MCH components. This port is not on the 82975X MCH; It has been replaced by PCI Express*.                                                                                                                                                                                                 |  |  |

| Core                                  | The internal base logic in the MCH                                                                                                                                                                                                                                                                                                                   |  |  |

| CRT                                   | Cathode Ray Tube                                                                                                                                                                                                                                                                                                                                     |  |  |

| DED                                   | Double-bit Error Detect                                                                                                                                                                                                                                                                                                                              |  |  |

| DBI                                   | Dynamic Bus Inversion                                                                                                                                                                                                                                                                                                                                |  |  |

| DDR                                   | Double Data Rate SDRAM memory technology                                                                                                                                                                                                                                                                                                             |  |  |

| DDR2                                  | A second generation Double Data Rate SDRAM memory technology                                                                                                                                                                                                                                                                                         |  |  |

| DMI                                   | Direct Media Interface. This is the interface between the MCH and ICH7.                                                                                                                                                                                                                                                                              |  |  |

| ECC                                   | Error Correcting Code                                                                                                                                                                                                                                                                                                                                |  |  |

| FSB                                   | Front Side Bus. This term is synonymous with Host bus or processor bus                                                                                                                                                                                                                                                                               |  |  |

| Full Reset                            | Full reset is when PWROK is de-asserted. Warm reset is when both RSTIN# and PWROK are asserted.                                                                                                                                                                                                                                                      |  |  |

| Host                                  | This term is used synonymously with processor.                                                                                                                                                                                                                                                                                                       |  |  |

| INTx                                  | An interrupt request signal where X stands for interrupts A,B,C, and D                                                                                                                                                                                                                                                                               |  |  |

| Intel <sup>®</sup> ICH7               | Seventh generation I/O Controller Hub component that contains additional functionality compared to previous ICH components. The I/O Controller Hub component that contains the primary PCI interface, LPC interface, USB2, ATA-100, and other I/O functions. It communicates with the MCH over a proprietary interconnect called DMI.                |  |  |

| МСН                                   | Intel <sup>®</sup> 82975X Memory Controller Hub component that contains the processor interface, DRAM controller, and x16 PCI Express port (typically the external graphics interface). It communicates with the I/O controller hub (Intel <sup>®</sup> ICH7*) and other I/O controller hubs over the DMI interconnect.                              |  |  |

| MSI                                   | Message Signaled Interrupt. A transaction initiated outside the host, conveying interrupt information to the receiving agent through the same path that normally carries read and write commands.                                                                                                                                                    |  |  |

| PCI Express*                          | Third generation input/output graphics attach called PCI Express Graphics. It is a high-<br>speed serial interface whose configuration is software compatible with the existing PCI<br>specifications. The specific PCI Express implementation intended for connecting the<br>MCH to an external graphics controller is a x16 link and replaces AGP. |  |  |

| Primary PCI                           | The physical PCI bus that is driven directly by the ICH7 component. Communication between Primary PCI and the MCH occurs over DMI. Note that the Primary PCI bus is <b>not</b> PCI Bus 0 from a configuration standpoint.                                                                                                                            |  |  |

| Processor                             | Refers to the Intel <sup>®</sup> Pentium <sup>®</sup> 4 processor in the 90 nm process in the LGA775 Land<br>Grid Array package, Intel <sup>®</sup> Pentium D processor, and Intel <sup>®</sup> Pentium <sup>®</sup> processor<br>Extreme Edition.                                                                                                   |  |  |

| SCI                                   | System Control Interrupt. Used in ACPI protocol.                                                                                                                                                                                                                                                                                                     |  |  |

| Term | Description                                                                                                                                                                                                                       |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SEC  | Single-bit Error Correct                                                                                                                                                                                                          |

| SERR | System Error. An indication that an unrecoverable error has occurred on an I/O bus.                                                                                                                                               |

| SMI  | System Management Interrupt. SMI is used to indicate any of several system conditions such as thermal sensor events, throttling activated, access to System Management RAM, chassis open, or other system state related activity. |

| Rank | A unit of DRAM corresponding to eight x8 SDRAM devices in parallel or four x16 SDRAM devices in parallel, ignoring ECC. These devices are usually, but not always, mounted on a single side of a DIMM.                            |

| TOLM | Top Of Low Memory. The highest address below 4 GB for which a processor-initiated memory read or write transaction will create a corresponding cycle to DRAM on the memory interface.                                             |

| VCO  | Voltage Controlled Oscillator                                                                                                                                                                                                     |

### **1.2 Reference Documents**

| Document Name                                                                | Doc Number/ Location                                                |

|------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Intel <sup>®</sup> I/O Controller Hub 7 (ICH7) Family Datasheet              | http://developer.intel.com//design/chip<br>sets/datashts/307013.htm |

| Intel <sup>®</sup> 975X Express Chipset Thermal Mechanical Design Guidelines | http://developer.intel.com/design/chips<br>ets/designex/310157.htm  |

| Intel <sup>®</sup> 975X Express Chipset Specification Update                 | http://developer.intel.com/design/chips<br>ets/specupdt/310159.htm  |

| Advanced Configuration and Power Interface Specification,<br>Revision 2.0    | http://www.acpi.info/                                               |

| Advanced Configuration and Power Interface Specification,<br>Revision 1.0b   | http://www.acpi.info/                                               |

| The PCI Local Bus Specification, Revision 2.3                                | http://www.pcisig.com/specifications                                |

| PCI Express* Specification, Revision 1.0a                                    | http://www.pcisig.com/specifications                                |

### 1.3 MCH Overview

The MCH connects to the processor as shown in Figure 1-1. A major role of the MCH in a system is to manage the flow of information between its four interfaces: the processor interface (FSB), the System Memory interface (DRAM controller), the Dual External Graphics interface (PCI Express\*), and the I/O Controller through DMI interface. This includes arbitrating between the four interfaces when each initiates transactions. The processor interface supports the Pentium 4 processor subset of the Extended Mode of the Scalable Bus Protocol.

The MCH supports one or two channels of DDR2 SDRAM. It also supports PCI Express based external graphics attach. To increase system performance, the MCH incorporates several queues and a write cache. The MCH also contains advanced power management logic.

#### 1.3.1 Host Interface

The MCH is optimized for the Pentium<sup>®</sup> 4 processor in the 90 nm process in the LGA775 Land Grid Array package, Pentium<sup>®</sup> D processor, and Pentium<sup>®</sup> processor Extreme Edition in a LGA775 socket. The MCH supports FSB frequencies of 200 MHz (800 MT/s) and 266 MHz (1066 MT/s) using a scalable FSB Vcc\_CPU. The MCH supports the Pentium 4 processor subset of the Extended Mode Scaleable Bus Protocol. The primary enhancements over the Compatible Mode P6 bus protocol are source synchronous double-pumped (2x) address and source synchronous quad-pumped (4x) data. Other MCH supported features of the host interface include: Hyper-Threading Technology (HT Technology), Pentium 4 processor FSB interrupt delivery, FSB Dynamic Bus Inversion (DBI), 12-deep in-order queue, and a 1-deep defer queue.

The MCH supports 36-bit host addressing, decoding up to 8 GB of the processor's usable memory address space. Host-initiated I/O cycles are decoded to PCI Express, DMI, or the MCH configuration space. Host-initiated memory cycles are decoded to PCI Express, DMI or main memory. PCI Express device accesses to non-cacheable system memory are not snooped on the host bus. Memory accesses initiated from PCI Express\* using PCI semantics and from DMI to system SDRAM will be snooped on the host bus.

#### 1.3.2 System Memory Interface

The MCH integrates a system memory DDR2 controller with two, 64-bit wide interfaces. Only Double Data Rate (DDR2) memory is supported; consequently, the buffers support only SSTL\_1.8 V signal interfaces. The memory controller interface is fully configurable through a set of control registers. Features of the MCH memory controller include:

- Maximum memory size is 8 GB.

- Directly supports one or two channels of memory (each channel consisting of 64 data lines)

- The memory channels are asymmetric: "Stacked" channels are assigned addresses serially. Channel B addresses are assigned after all Channel A addresses.

- The memory channels are interleaved: Addresses are ping-ponged between the channels after each cache line (64-B boundary).

- Available bandwidth up to 5.3 GB/s (DDR2 667) for single-channel mode or dual-channel asymmetric mode and 10.7 GB/s (DDR2 667) in dual-channel Interleaved mode.

- Supports standard ECC (Error Correcting Code) x8 only or Non-ECC x8 and x16 DIMMs.

- Supports DDR2 memory DIMM frequencies of 533 and 667 MHz. The speed used in all channels is the speed of the slowest DIMM in the system.

- Supports 256-Mb, 512-Mb and 1-Gb DDR2 technologies for x8 and x16 devices.

- Supports four banks for all DDR2 devices up to 512-Mbit density. Supports eight banks for 1-Gbit DDR2 devices.

- DDR2-667 4-4-4 is NOT supported

- Supports only unbuffered DIMMs.

- Supports opportunistic refresh.

- In dual channel mode the MCH supports 32 simultaneously open pages.

- SPD (Serial Presence Detect) scheme for DIMM detection support.

- Suspend-to-RAM support using CKE.

- Supports configurations defined in the JEDEC DDR2 DIMM specification only.

- Directly supports two channels of ECC or non-ECC DDR2 DIMMs.

- Supports Partial Writes to memory using Data Mask (DM) signals, only when not using ECC.

- Supports a burst length of 8 for single-channel and dual-channel interleaved and asymmetric operating modes.

- Supports Enhanced Memory Interleave.

#### 1.3.3 PCI Express\* Graphics Interface

The PCI Express interface supports 16 bi-directional lanes used for next generation graphics attach. Each PCI Express graphic lane supports a bi-directional transfer rate of 2.5 Gb/s for a theoretical bandwidth of 8 GBs when in x16 mode. Features of the PCI Express interface include:

- One 16-lane PCI Express port intended for graphics attach, compatible to the *PCI Express*\* *Base Specification, Revision 1.0a.*

- A base PCI Express frequency of 2.5 Gb/s only.

- Raw bit-rate on the data pins of 2.5 Gb/s, resulting in a real bandwidth per pair of 250 MB/s given the 8b/10b encoding used to transmit data across this interface.

- Maximum theoretical realized bandwidth on the interface of 4 GB/s in each direction simultaneously, for an aggregate of 8 GB/s when x16.

- PCI Express extended configuration space. The first 256 bytes of configuration space alias directly to the PCI compatibility configuration space. The remaining portion of the fixed 4-KB block of memory-mapped space above that (starting at 100h) is known as extended configuration space.

- PCI Express enhanced addressing mechanism. Accessing the device configuration space in a flat memory mapped fashion.

- Automatic discovery, negotiation, and training of link out of reset.

- Supports traditional PCI style traffic (asynchronous snooped, PCI ordering).

- Supports traditional AGP style traffic (asynchronous non-snooped, PCI Express-relaxed ordering).

- Hierarchical PCI-compliant configuration mechanism for downstream devices (i.e., normal PCI 2.3 configuration space as a PCI-to-PCI bridge).

- Supports "static" lane numbering reversal. This method of lane reversal is controlled by a Hardware Reset strap, and reverses both the receivers and transmitters for all lanes (e.g., TX15->TX0, RX15->RX0). This method is transparent to all external devices and is different than lane reversal as defined in the PCI Express specification. In particular, link initialization is not affected by static lane reversal.

#### **1.3.4 Bifurcated PCI Express\* Graphics Supported Features**

- Bifurcated PCI Express\* Graphics x8 supported.

- Single PCI Express\* Graphics x16 supported.

- Peer-to-Peer Writes.

#### 1.3.5 Direct Media Interface (DMI)

Direct Media Interface (DMI) is the chip-to-chip connection between the MCH and ICH7. This highspeed interface integrates advanced priority-based servicing allowing for concurrent traffic and true isochronous transfer capabilities. Base functionality is completely software transparent permitting current and legacy software to operate normally.

To provide for true isochronous transfers and configurable Quality of Service (QoS) transactions, the ICH7 supports two virtual channels on DMI: VC0 and VC1. These two channels provide a fixed arbitration scheme where VC1 is always the highest priority. VC0 is the default conduit of traffic for DMI and is always enabled. VC1 must be specifically enabled and configured at both ends of the DMI link (i.e., the Intel ICH7 and MCH). Configuration registers for DMI, virtual channel support, and DMI active state power management (ASPM) are in the RCRB space in the MCH Register Description. Features of the DMI include:

- A chip-to-chip connection interface to Intel ICH7.

- 2 GB/s point-to-point DMI to ICH7 (1 GB/s each direction).

- 100 MHz reference clock (shared with PCI Express graphics attach).

- 32-bit downstream addressing.

- APIC and MSI interrupt messaging support. MCH will send Intel-defined "End Of Interrupt" broadcast message when initiated by the processor.

- Message Signaled Interrupt (MSI) messages.

- SMI, SCI, and SERR error indication.

- Legacy support for ISA regime protocol (PHOLD/PHOLDA) required for parallel port DMA, floppy drive, and LPC bus masters.

#### 1.3.6 System Interrupts

- Supports both 8259 and Pentium 4 processor FSB interrupt delivery mechanisms.

- Supports interrupts signaled as upstream memory writes from PCI Express and DMI.

MSIs routed directly to FSB.

- From I/OxAPICs.

- Provides redirection for IPI (Inter-Processor Interrupts) and upstream interrupts to the FSB.

#### 1.3.7 MCH Clocking

The Differential FSB clock of 200/266 MHz (HCLKP/HCLKN) supports transfer rates of 800/1066 MT/s. The Host PLL generates 2X, 4X, and 8X versions of the host clock for internal optimizations. The MCH core clock is synchronized to the host clock.

The internal and external memory clocks of 266 MHz and 333 MHz are generated from one of two MCH PLLs that use the Host clock as a reference. Also included are 2x and 4x clocks for internal optimizations.

The PCI Express\* core clock of 250 MHz is generated from a separate PCI Express PLL. This clock uses the fixed 100 MHz serial reference clock (GCLKP/GCLKN) for reference.

All of the above mentioned clocks are capable of tolerating Spread Spectrum clocking as defined in the Clock Generator specification. Host, Memory, and PCI Express PLLs, and all associated internal clocks are disabled until PWROK is asserted.

#### **1.3.8 Power Management**

The MCH power management support includes:

- PC99 suspend to DRAM support ("STR", mapped to ACPI state S3)

- SMRAM space remapping to A0000h (128 KB)

- Supports extended SMRAM space above 256 MB, additional 1-MB TSEG from the Top of Low Usable DRAM (TOLUD), and cacheable (cacheablility controlled by the processor)

- ACPI Revision 1.0 compatible power management

- Supports processor states: C0 and C1

- Supports system states: S0, S1D, S3, S4, and S5

- Supports processor Thermal Management 2 (TM2)

- Microsoft Windows NT\* Hardware Design Guide v1.0 compliant

§

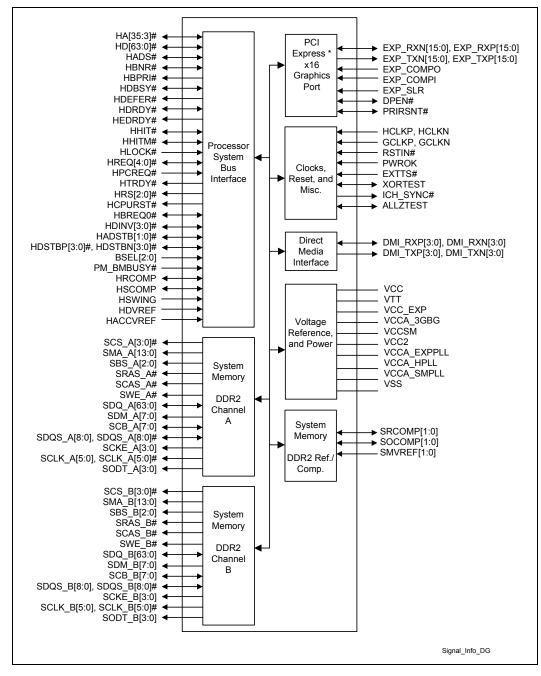

### 2 Signal Description

This chapter provides a detailed description of MCH signals. The signals are arranged in functional groups according to their associated interface.

The following notations are used to describe the signal type:

| PCIE     | PCI Express* interface signals. These signals are compatible with PCI Express 1.0 Signaling Environment AC Specifications and are AC coupled. The buffers are not 3.3 V tolerant. Differential voltage spec = $( D+-D- ) * 2 = 1.2 V_{max}$ . Single-ended maximum = 1.5 V. Single-ended minimum = 0 V.    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|