This device is designed specifically to power IMVP Mobile Processors under a strict disclosure agreement with Intel. The end user must have a current *CNDA* Agreement in place with Intel. For more information please contact IMVP@list.ti.com.

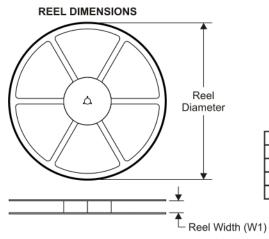

## PACKAGE MATERIALS INFORMATION

www.ti.com 8-Apr-2009

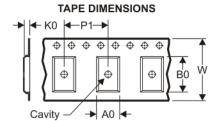

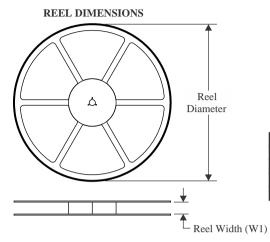

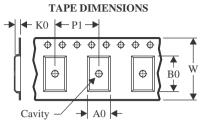

## TAPE AND REEL INFORMATION

|    |   | Dimension designed to accommodate the component width     |

|----|---|-----------------------------------------------------------|

|    |   | Dimension designed to accommodate the component length    |

| K  | 0 | Dimension designed to accommodate the component thickness |

| ٧  | ٧ | Overall width of the carrier tape                         |

| ГР | 1 | Pitch between successive cavity centers                   |

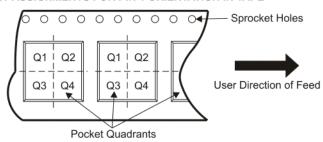

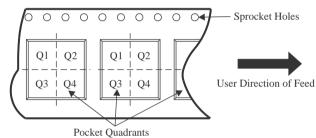

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

### \*All dimensions are nominal

| Device        | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|---------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPS51610IRHBR | QFN             | RHB                | 32 | 3000 | 330.0                    | 12.4                     | 5.3     | 5.3     | 1.5     | 8.0        | 12.0      | Q2               |

| TPS51610IRHBT | QFN             | RHB                | 32 | 250  | 180.0                    | 12.4                     | 5.3     | 5.3     | 1.5     | 8.0        | 12.0      | Q2               |

| TPS51610RHBR  | QFN             | RHB                | 32 | 3000 | 330.0                    | 12.4                     | 5.3     | 5.3     | 1.5     | 8.0        | 12.0      | Q2               |

| TPS51610RHBT  | QFN             | RHB                | 32 | 250  | 180.0                    | 12.4                     | 5.3     | 5.3     | 1.5     | 8.0        | 12.0      | Q2               |

www.ti.com 8-Apr-2009

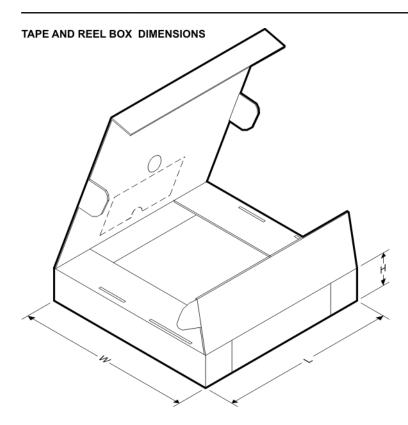

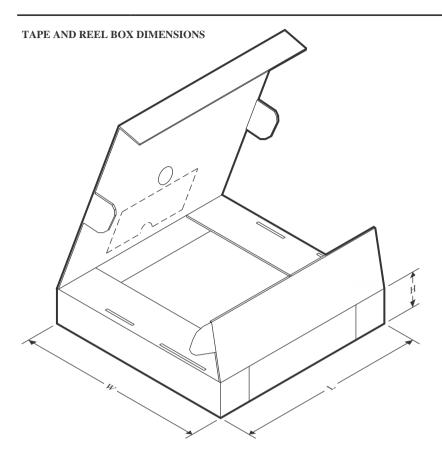

\*All dimensions are nominal

| 7 till dillitoriolorio di o mominar |              |                 |      |      |             |            |             |

|-------------------------------------|--------------|-----------------|------|------|-------------|------------|-------------|

| Device                              | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

| TPS51610IRHBR                       | QFN          | RHB             | 32   | 3000 | 346.0       | 346.0      | 29.0        |

| TPS51610IRHBT                       | QFN          | RHB             | 32   | 250  | 190.5       | 212.7      | 31.8        |

| TPS51610RHBR                        | QFN          | RHB             | 32   | 3000 | 346.0       | 346.0      | 29.0        |

| TPS51610RHBT                        | QFN          | RHB             | 32   | 250  | 190.5       | 212.7      | 31.8        |

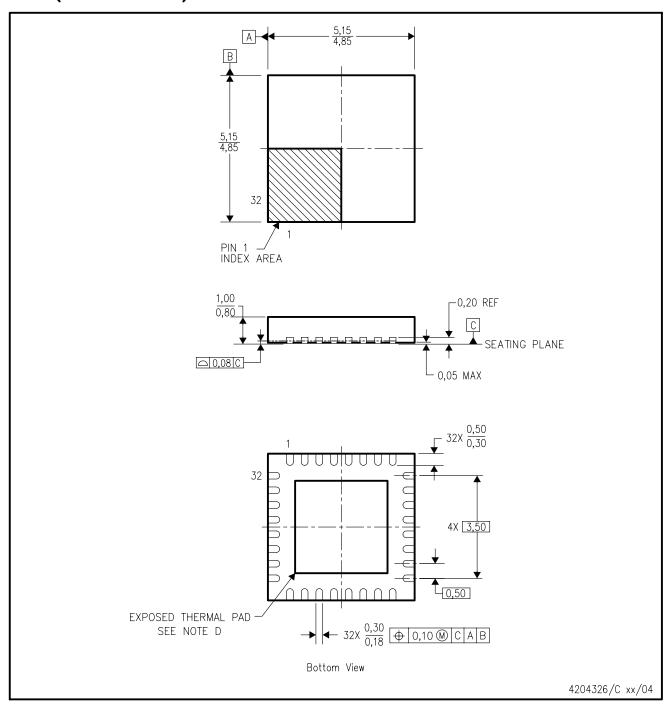

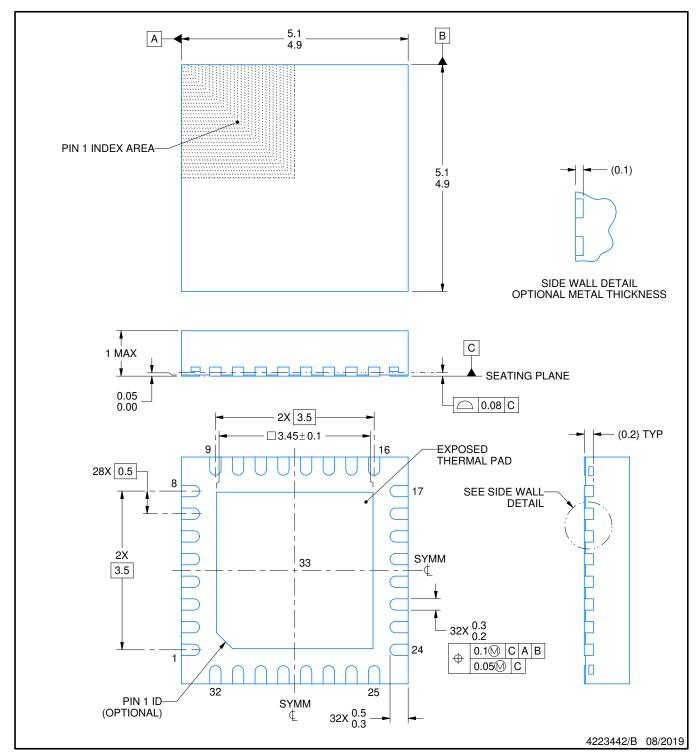

# RHB (S-PQFP-N32)

# PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. QFN (Quad Flatpack No-Lead) Package configuration.

- D The Package thermal pad must be soldered to the board for thermal and mechanical performance. See product data sheet for details regarding the exposed thermal pad dimensions.

- E. Falls within JEDEC MO-220.

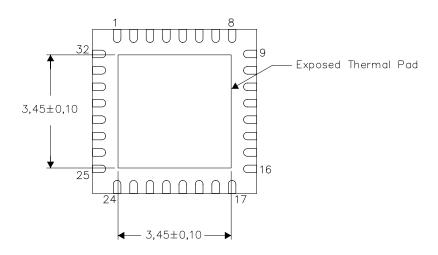

### THERMAL PAD MECHANICAL DATA

RHB (S-PVQFN-N32)

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

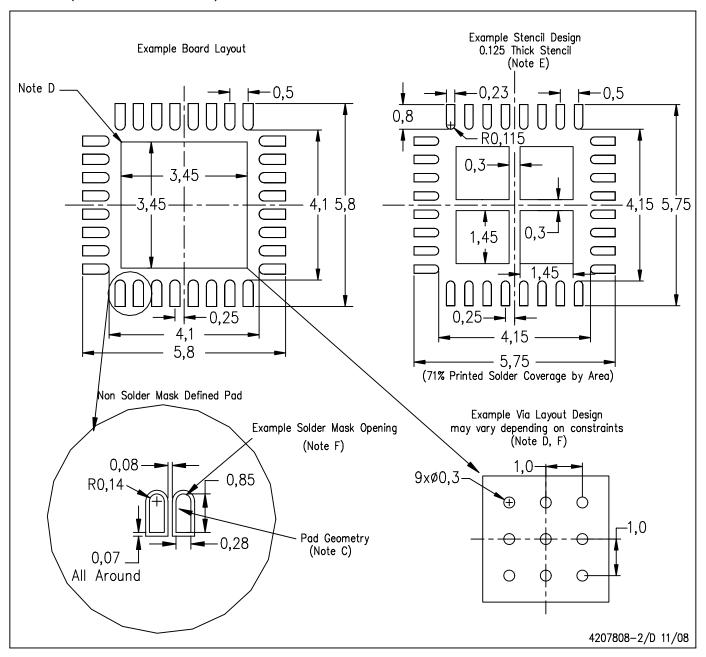

# RHB (S-PQFP-N32)

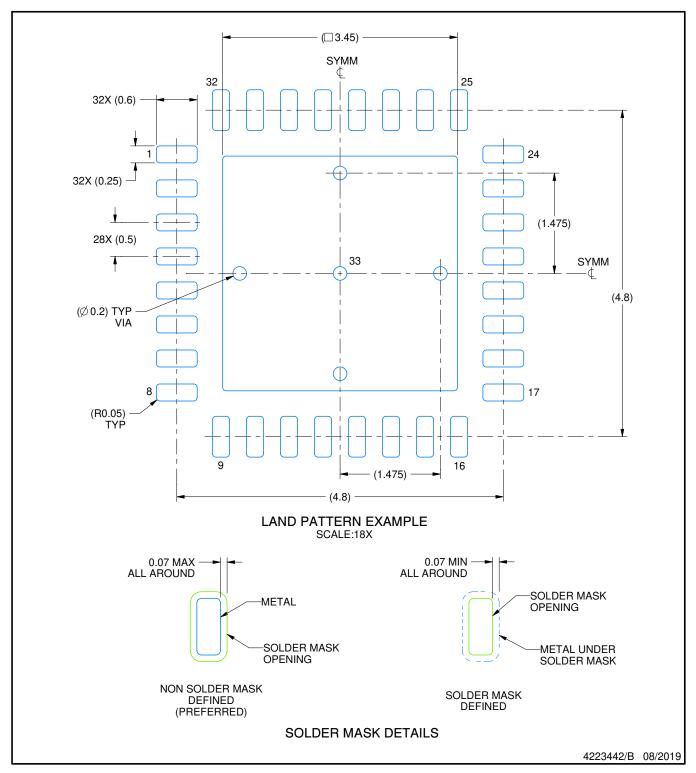

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SCBA017, SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for recommended solder mask tolerances and via tenting recommendations for vias placed in the thermal pad.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS51611RHBR | VQFN            | RHB                | 32 | 3000 | 330.0                    | 12.4                     | 5.3        | 5.3        | 1.5        | 8.0        | 12.0      | Q2               |

| TPS51611RHBT | VQFN            | RHB                | 32 | 250  | 180.0                    | 12.4                     | 5.3        | 5.3        | 1.5        | 8.0        | 12.0      | Q2               |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS51611RHBR | VQFN         | RHB             | 32   | 3000 | 356.0       | 356.0      | 35.0        |

| TPS51611RHBT | VQFN         | RHB             | 32   | 250  | 210.0       | 185.0      | 35.0        |

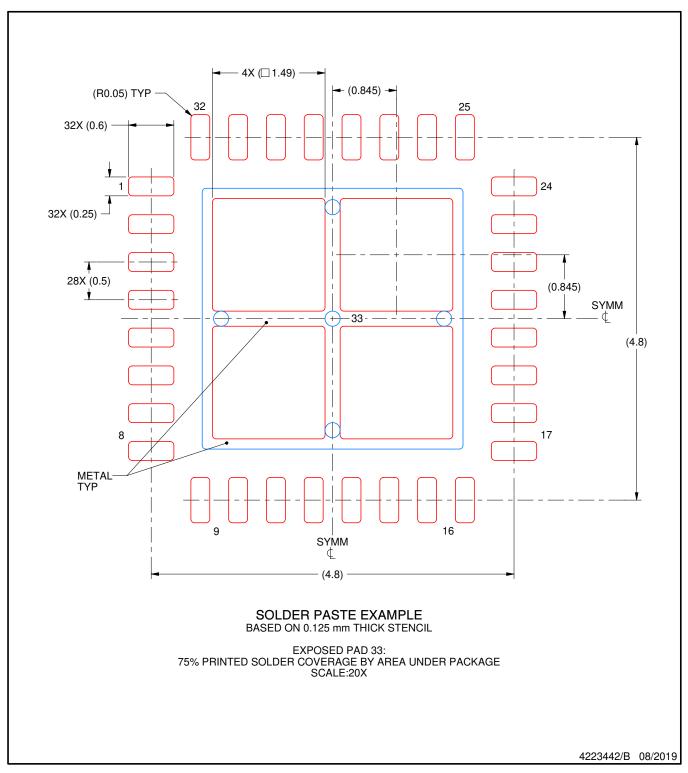

5 x 5, 0.5 mm pitch

PLASTIC QUAD FLATPACK - NO LEAD

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

4224745/A

PLASTIC QUAD FLATPACK - NO LEAD

#### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for thermal and mechanical performance.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

PLASTIC QUAD FLATPACK - NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated