## Multiple MOSFET Driver IC

#### 1 Overview

#### **Features**

- Four half-bridge gate drivers for external N-channel MOSFETs

- Control of reverse battery protection MOSFET

- Adaptive MOSFET gate control

- Improved electromagnetic emission

- Reduced switching losses in PWM mode

- 24-bit Serial Peripheral Interface

- One current sense amplifier with configurable gain

- High-side and low-side capable for protection and diagnosis

- Drain-source monitoring for short circuit detection

- Overtemperature warning and shutdown

- Timeout watchdog

- Detailed off-state diagnostic (open load, short circuit to battery or short circuit to GND) via SPI

- Three PWM inputs

- High-side and low-side PWM capable

- Active free-wheeling

- Up to 25 kHz PWM frequency

- Low current consumption in sleep mode

- · Leadless power package with support of optical lead tip inspection

- Green Product (RoHS compliant)

- AEC Qualified

## **Potential applications**

- Seat control and extended functions (steering column adjustment, gas pedal adjustment)

- Central door lock

- Body control module (cargo cover, washer pump, window lift, rear wiper ...)

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100.

#### **Multiple MOSFET Driver IC**

#### Overview

## **Description**

The TLE92104-131 is a Multi-MOSFET driver IC dedicated to control up to eight n-channel MOSFETs. It includes four half-bridges for DC motor control applications such as automotive power seat control or other applications.

A 24-bit Serial Peripheral Interface (SPI) is used to configure the TLE92104-131 and to control the half-bridges. It also allows the read out of the status registers for diagnostic purpose.

The TLE92104-131 offers a wide range of diagnostic features such as the monitoring of the supply voltage, the charge pump voltage, temperature warning and over-temperature shutdown. Each gate driver monitors independently its external MOSFET drain-source voltage for fault conditions.

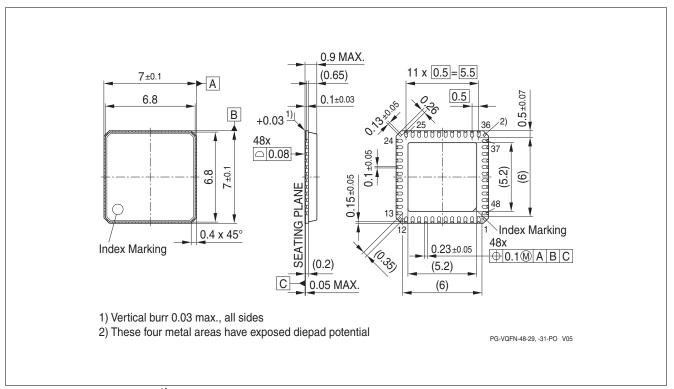

The device is housed in a VQFN-48 with exposed pad supporting lead tip inspection. The package provides a good thermal performance and minimizes the required PCB space.

| Туре         | Package    | Marking        |

|--------------|------------|----------------|

| TLE92104-131 | PG-VQFN-48 | TLE92104-131QX |

# **TLE92104-131**Multiple MOSFET Driver IC

## **Table of contents**

| 1                  | Overview                                                                     | 1    |

|--------------------|------------------------------------------------------------------------------|------|

| 2                  | Block diagram                                                                | 5    |

| 2.1                | Voltage and current definition                                               | 6    |

| 3                  | Pin configuration                                                            | 7    |

| 3.1                | Pin assignment                                                               | 7    |

| 3.2                | Pin definitions and functions                                                | 8    |

| 4                  | General product characteristics                                              | . 10 |

| 4.1                | Absolute maximum ratings                                                     |      |

| 4.2                | Functional range                                                             | . 11 |

| 4.3                | Thermal resistance                                                           | . 13 |

| 5                  | General description                                                          | . 14 |

| 5.1                | Power supply                                                                 | . 14 |

| 5.2                | Operation modes                                                              | . 14 |

| 5.2.1              | Normal mode                                                                  | . 14 |

| 5.2.2              | Sleep mode                                                                   | . 15 |

| 5.2.3              | Fail Safe Mode                                                               |      |

| 5.3                | Reset behavior                                                               |      |

| 5.4                | Charge pump                                                                  |      |

| 5.5                | Frequency modulation                                                         |      |

| 5.6                | Electrical characteristics                                                   |      |

| 5.6.1              | Electrical characteristics: supply                                           |      |

| 5.6.2              | Electrical characteristics: logic inputs PWMx, EN                            |      |

| 5.6.3              | Electrical characteristics charge pump                                       |      |

| 6                  | Floating gate drivers                                                        |      |

| 6.1                | MOSFET control with bridge driver in active mode (BD_PASS = 0 and EN = High) |      |

| 6.2                | Static activation with bridge driver in active mode (BD_PASS = 0)            |      |

| 6.2.1              | Static activation of a high-side MOSFET                                      |      |

| 6.2.2              | Static activation of a low-side MOSFET                                       |      |

| 6.2.3              | Turn-off of the high-side and low-side MOSFETs of a half-bridge              |      |

| 6.3                | PWM operation with bridge driver in active mode (BD_PASS = 0)                |      |

| 6.3.1              | Determination of the active and free-wheeling MOSFET                         |      |

| 6.3.2              | Configuration in PWM mode                                                    |      |

| 6.3.3              | PWM operation with adaptive gate control                                     |      |

| 6.3.3.1<br>6.3.3.2 | High-side PWM with adaptive gate control, motor operating as load            |      |

| 6.3.3.3            | Low-side PWM with adaptive gate control, motor operating as load             |      |

| 6.3.3.4            | Low-side PWM with adaptive gate control, motor operating as generator        |      |

| 6.3.3.5            | Status bits for regulation of turn-on and turn-off delay times               |      |

| 6.3.3.6            | Precharge and predischarge phases with <b>EN_DEEP_AD</b> = 1                 |      |

| 6.3.4              | PWM operation without adaptive gate control                                  |      |

| 6.3.4.1            | PWM operation without adaptive gate control, AGC[1:0] = (0,0)                |      |

| 6.3.4.2            | PWM operation without adaptive gate control, AGC[1:0] = (0,0)                |      |

| 6.3.5              | PWM operation at high and low duty cycles                                    |      |

| 6.3.6              | Gate driver current                                                          |      |

| 6.4                | Passive discharge                                                            |      |

|                    | 3                                                                            |      |

## **Multiple MOSFET Driver IC**

| 12     | Revision History                                                  | 145 |

|--------|-------------------------------------------------------------------|-----|

| 11     | Package outlines                                                  | 144 |

| 10     | Application information                                           |     |

| 9.2.1  | General status register                                           |     |

| 9.2    | Status register                                                   |     |

| 9.1.2  | Half-bridge control                                               |     |

| 9.1.1  | General Control Registers and Protection Settings                 |     |

| 9.1    | Control registers                                                 |     |

| 9      | Register specification                                            |     |

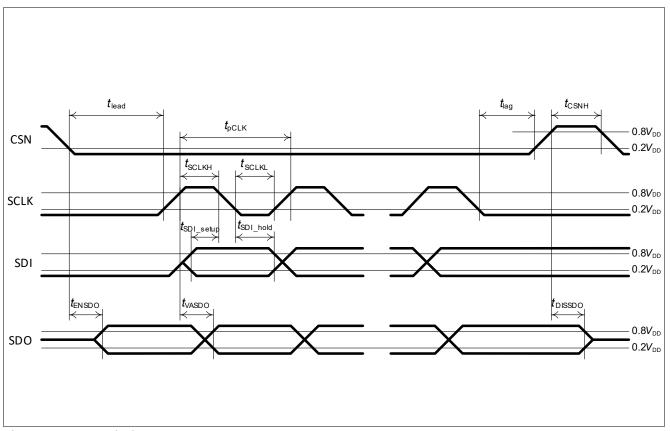

| 8.6    | SPI electrical characteristics: timings                           |     |

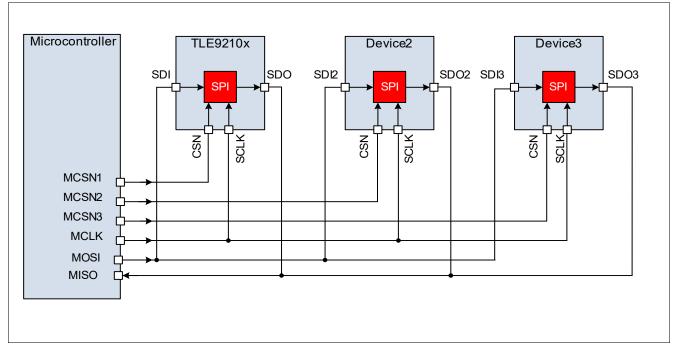

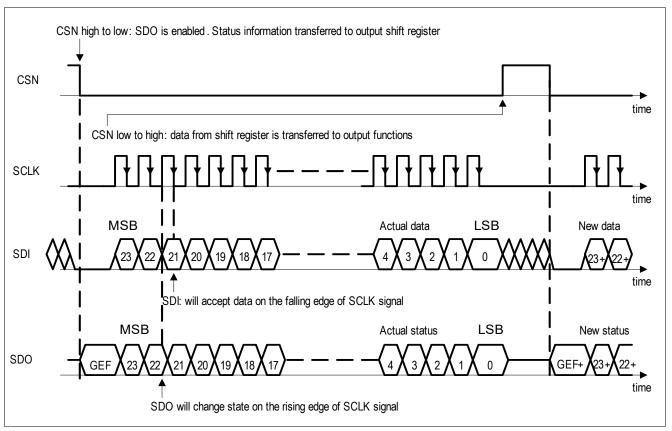

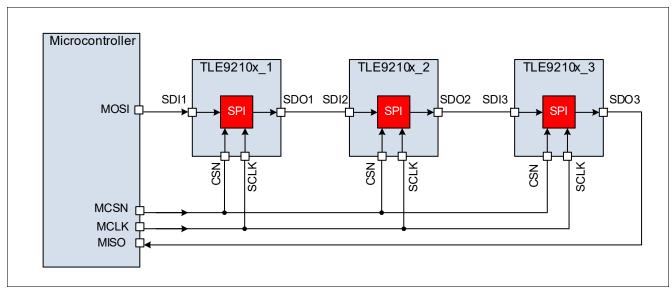

| 8.5    | Daisy chain                                                       |     |

| 8.4    | SPI error detection                                               |     |

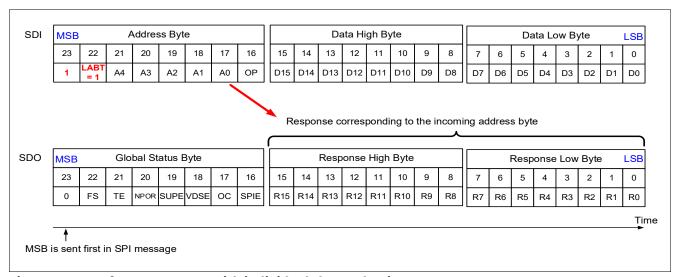

| 8.3    | Global status byte                                                |     |

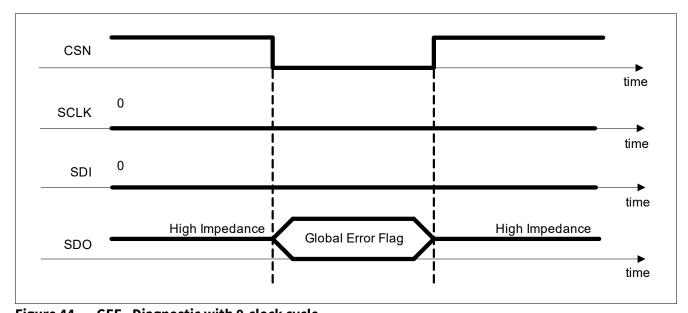

| 8.2    | Global Error Flag (GEF)                                           |     |

| 8.1    | SPI protocol with independent slave selection                     |     |

| 8      | Serial Peripheral Interface - SPI                                 |     |

| 7.11   | Electrical characteristics protections and diagnostics            |     |

| 7.10.5 | CSO outputs capacitor                                             |     |

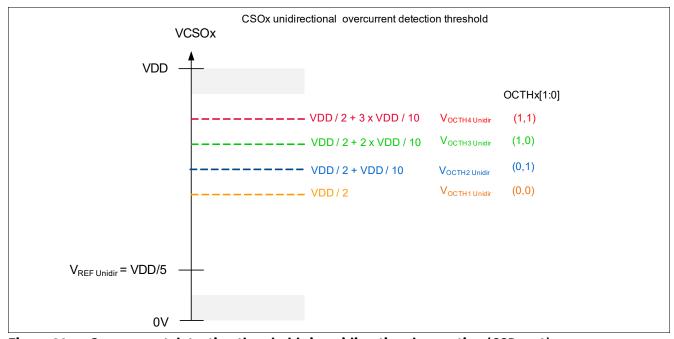

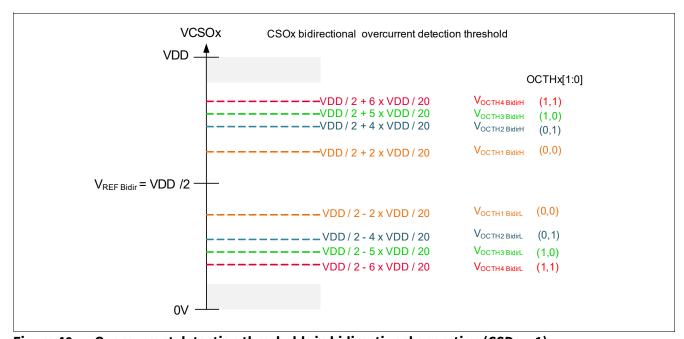

| 7.10.4 | Overcurrent detection                                             |     |

| 7.10.3 | High-side and low-side setting                                    |     |

| 7.10.2 | Gain configuration                                                |     |

| 7.10.1 | Unidirectional and bidirectional operation                        |     |

| 7.10   | Current sense amplifier                                           |     |

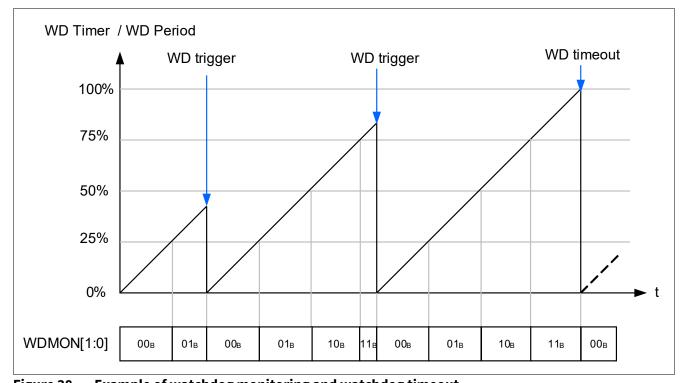

| 7.9    | Timeout watchdog                                                  |     |

| 7.8    | Switching parameters of MOSFETs in PWM mode                       |     |

| 7.7.4  | Charge pump undervoltage                                          |     |

| 7.7.3  | V <sub>DD</sub> undervoltage                                      |     |

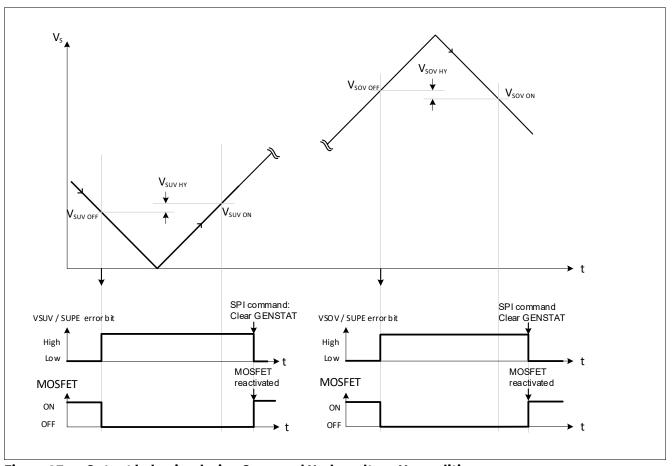

| 7.7.2  | $V_{\rm S}$ overvoltage with bridge driver in active mode         |     |

| 7.7.1  | <i>V</i> <sub>S</sub> undervoltage                                |     |

| 7.7    | $V_{S}$ overvoltage and undervoltage shutdown                     |     |

| 7.6    | Temperature monitoring                                            |     |

| 7.5    | OFF-state diagnostic                                              | 70  |

| 7.4.3  | Mapping of cross-current protection and blank times               |     |

| 7.4.2  | Drain-source overvoltage blank time in bridge driver active mode  |     |

| 7.4.1  | Cross-current protection                                          |     |

| 7.4    | Cross-current protection and drain-source overvoltage blank time  |     |

| 7.3    | Drain-source voltage monitoring with bridge driver in active mode |     |

| 7.2    | Safe switch (optional)                                            |     |

| 7.1    | Reverse polarity protection                                       |     |

| 7      | Protections and diagnostics                                       | 65  |

| 6.6    | Electrical characteristics gate driver                            |     |

| 6.5    | Bridge driver in passive mode                                     | 62  |

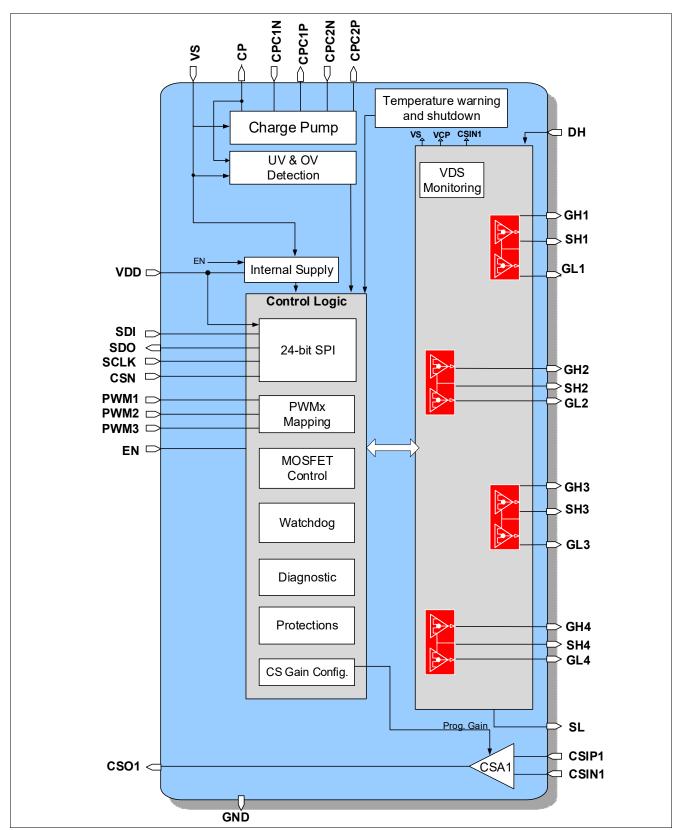

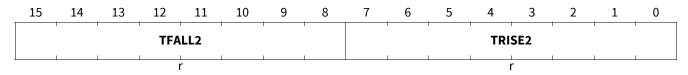

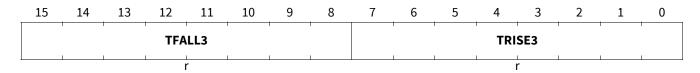

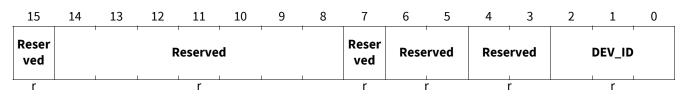

**Block diagram**

#### **Block diagram** 2

Figure 1 **Block diagram**

#### **Block diagram**

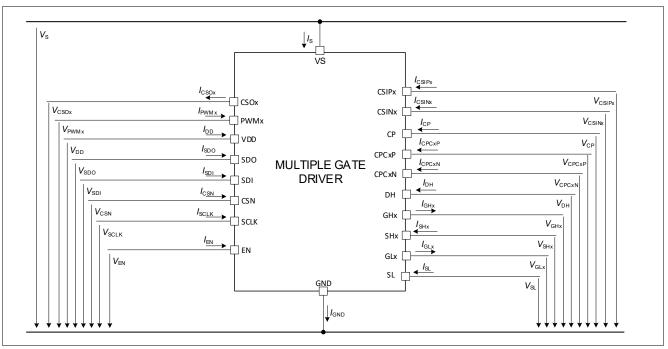

## 2.1 Voltage and current definition

Figure 2 shows terms used in this datasheet, with associated convention for positive value.

Figure 2 Voltage and current definition

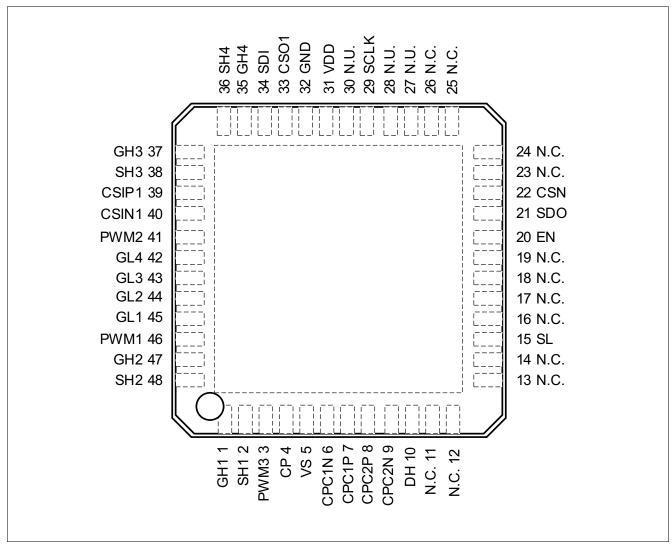

Pin configuration

#### **Pin configuration** 3

#### Pin assignment 3.1

Figure 3 Pin configuration TLE92104-131QX

## **Multiple MOSFET Driver IC**

Pin configuration

#### Pin definitions and functions 3.2

Pin configuration TLE92104-131QX Table 1

| Pin | Symbol | Function                                                                                                                                 |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | GH1    | Gate high-side 1                                                                                                                         |

|     |        | Analog I/O pin to turn on/off high-side MOSFET 1. Connect to the gate of high-side MOSFET 1.                                             |

| 2   | SH1    | Source high-side 1                                                                                                                       |

|     |        | Connection to source of high-side MOSFET 1.                                                                                              |

| 3   | PWM3   | PWM input 3                                                                                                                              |

| 4   | СР     | Charge Pump Output                                                                                                                       |

| 5   | VS     | <b>Supply Voltage</b> Device supply voltage. Connect this pin to the supply (battery) voltage with a reverse battery protection circuit. |

| 6   | CPC1N  | Negative connection to Charge Pump Capacitor 1                                                                                           |

| 7   | CPC1P  | Positive connection to Charge Pump Capacitor 1                                                                                           |

| 8   | CPC2P  | Positive connection to Charge Pump Capacitor 2                                                                                           |

| 9   | CPC2N  | Negative connection to Charge Pump Capacitor 2                                                                                           |

| 10  | DH     | <b>Drain input for high-sides</b> Input for the drains of high-side MOSFETs. Refer to <b>Chapter 7.3</b> .                               |

| 11  | N.C.   | Not connected                                                                                                                            |

| 12  | N.C.   | Not connected                                                                                                                            |

| 13  | N.C.   | Not connected                                                                                                                            |

| 14  | N.C.   | Not connected                                                                                                                            |

| 15  | SL     | Source low-side                                                                                                                          |

|     |        | Common connection to the source of the low-side MOSFETs.                                                                                 |

| 16  | N.C.   | Not connected                                                                                                                            |

| 17  | N.C.   | Not connected                                                                                                                            |

| 18  | N.C.   | Not connected                                                                                                                            |

| 19  | N.C.   | Not connected                                                                                                                            |

| 20  | EN     | Enable input with internal pull-down                                                                                                     |

| 21  | SDO    | Serial Data Output                                                                                                                       |

| 22  | CSN    | Chip Select Not with internal pull-up                                                                                                    |

| 23  | N.C.   | Not connected                                                                                                                            |

| 24  | N.C.   | Not connected                                                                                                                            |

| 25  | N.C.   | Not connected                                                                                                                            |

| 26  | N.C.   | Not connected                                                                                                                            |

| 27  | N.U.   | Not used pin to be connected to GND                                                                                                      |

| 28  | N.U.   | Not used pin to be connected to GND                                                                                                      |

| 29  | SCLK   | Serial Clock Input with internal pull-down                                                                                               |

| 30  | N.U.   | Not used pin to be connected to GND                                                                                                      |

# TLE92104-131 Multiple MOSFET Driver IC

#### **Pin configuration**

Table 1 Pin configuration TLE92104-131QX

| Pin | Symbol | Function                                                               |

|-----|--------|------------------------------------------------------------------------|

| 31  | VDD    | Logic supply                                                           |

| 32  | GND    | Ground connection                                                      |

| 33  | CSO1   | Current Sense Amplifier Output1                                        |

| 34  | SDI    | Serial Data Input with internal pull-down                              |

| 35  | GH4    | Gate high-side 4                                                       |

| 36  | SH4    | Source high-side 4                                                     |

| 37  | GH3    | Gate high-side 3                                                       |

| 38  | SH3    | Source high-side 3                                                     |

| 39  | CSIP1  | Non-inverting input of the Current Sense Amplifier 1                   |

| 40  | CSIN1  | Inverting input of the Current Sense Amplifier 1                       |

| 41  | PWM2   | PWM input 2                                                            |

| 42  | GL4    | Gate low-side 4                                                        |

| 43  | GL3    | Gate low-side 3                                                        |

| 44  | GL2    | Gate low-side 2                                                        |

| 45  | GL1    | Gate low-side 1                                                        |

| 46  | PWM1   | PWM input 1                                                            |

| 47  | GH2    | Gate high-side 2                                                       |

| 48  | SH2    | Source high-side 2                                                     |

|     | E.P.   | Exposed pad                                                            |

|     |        | For cooling purpose only, do not use as electrical GND <sup>1)</sup> . |

<sup>1)</sup> The exposed pad at the bottom of the package allows better power dissipation from TLE92104-131 via the PCB. The exposed pad must be left floating or connected to GND (recommended) for best EMC and thermal performance.

## **Multiple MOSFET Driver IC**

#### **General product characteristics**

#### **General product characteristics** 4

#### **Absolute maximum ratings** 4.1

#### Absolute maximum ratings1) Table 2

$T_i = -40$ °C to 150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                         | Symbol                                                 |                     | Value | s                     | Unit | Note or<br>Test Condition | Number   |

|---------------------------------------------------|--------------------------------------------------------|---------------------|-------|-----------------------|------|---------------------------|----------|

|                                                   |                                                        | Min.                | Тур.  | Max.                  |      |                           |          |

| Voltages                                          | •                                                      |                     |       |                       | •    |                           | •        |

| Supply voltage                                    | V <sub>S</sub>                                         | -0.3                | -     | 40                    | V    | -                         | P_4.1.1  |

| PWM input voltages (PWMx)                         | $V_{\text{PWMx}}$                                      | -0.3                | _     | V <sub>DD</sub> + 0.3 | V    | /  < 10 mA                | P_4.1.2  |

| Logic input voltages (SDI, SCLK, CSN, EN)         | $V_{\rm SDI}, V_{\rm SCLK}, \ V_{\rm CSN}, V_{\rm EN}$ | -0.3                | _     | V <sub>DD</sub> + 0.3 | V    | /  < 10 mA                | P_4.1.3  |

| Voltage range and SDO                             | $V_{SDO}$                                              | -0.3                | _     | V <sub>DD</sub> + 0.3 | V    | /  < 10 mA                | P_4.1.4  |

| Voltage range at CSIPx and CSINx                  | $V_{\rm CSIP}, V_{\rm CSIN}$                           | -8.0                | -     | 40                    | V    | _                         | P_4.1.5  |

| Differential input voltage range CSIPx - CSINx    | V <sub>CSIDiff</sub>                                   | -8.0                | -     | 8.0                   | V    | _                         | P_4.1.21 |

| Voltage range at DH                               | $V_{DH}$                                               | -0.3                | _     | 40                    | V    | -                         | P_4.1.6  |

| Voltage range at SL                               | $V_{SL}$                                               | -8.0                | _     | 6.0                   | V    | _                         | P_4.1.7  |

| Voltage range at SHx                              | $V_{SH}$                                               | -8.0                | -     | 40                    | V    | _                         | P_4.1.8  |

| Voltage range at GHx                              | $V_{GH}$                                               | -8.0                | _     | 40                    | V    | _                         | P_4.1.9  |

| Voltage range at GLx                              | $V_{GL}$                                               | -8.0                | -     | 24                    | V    | -                         | P_4.1.10 |

| Voltage difference between GLx and SL             | $V_{\rm GS\_LS}$                                       | -0.3                | -     | 16                    | V    | _                         | P_4.1.11 |

| Voltage difference between GHx and SHx            | $V_{\rm GS\_HS}$                                       | -1.0                | _     | 16                    | V    | 2)                        | P_4.1.23 |

| Voltage range at charge pump pins CP              | V <sub>CP</sub>                                        | V <sub>S</sub> -0.3 | -     | V <sub>S</sub> +17    | V    | _                         | P_4.1.12 |

| Voltage range at charge pump<br>pins CPC1P, CPC2P | V <sub>CPCxP</sub>                                     | -0.3                | -     | V <sub>S</sub> +17    | V    | _                         | P_4.1.22 |

| Voltage range at charge pump<br>pins CPC1N, CPC2N | V <sub>CPCxN</sub>                                     | -0.3                | -     | V <sub>S</sub> +0.3   | V    | -                         | P_4.1.24 |

| Logic supply voltage                              | $V_{DD}$                                               | -0.3                | _     | 5.5                   | V    | _                         | P_4.1.13 |

| Voltage at CSOx                                   | V <sub>CSOx</sub>                                      | -0.3                | -     | V <sub>DD</sub> + 0.3 | V    | _                         | P_4.1.14 |

| Temperatures                                      | •                                                      | ·                   | •     | •                     |      |                           | •        |

| Junction temperature                              | $T_{\rm j}$                                            | -40                 | _     | 150                   | °C   | _                         |          |

#### **Multiple MOSFET Driver IC**

#### **General product characteristics**

### **Table 2** Absolute maximum ratings<sup>1)</sup> (cont'd)

$T_{\rm j}$  = -40°C to 150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                       | Symbol               |      | Value | S    | Unit | Note or               | Number   |

|-------------------------------------------------|----------------------|------|-------|------|------|-----------------------|----------|

|                                                 |                      | Min. | Тур.  | Max. |      | <b>Test Condition</b> |          |

| Storage temperature                             | $T_{\rm stg}$        | -55  | _     | 150  | °C   | -                     | P_4.1.16 |

| ESD susceptibility                              |                      |      |       |      |      |                       |          |

| ESD susceptibility all pins                     | V <sub>ESDHBM1</sub> | -2   | _     | 2    | kV   | HBM <sup>3)</sup>     | P_4.1.17 |

| ESD susceptibility of VS and DH pins versus GND | V <sub>ESDHBM2</sub> | -4   | -     | 4    | kV   | HBM <sup>3)</sup>     | P_4.1.18 |

| ESD susceptibility all pins                     | V <sub>ESDCDM1</sub> | -500 | _     | 500  | V    | CDM <sup>4)</sup>     | P_4.1.19 |

| ESD susceptibility pin corner pins              | V <sub>ESDCDM2</sub> | -750 | -     | 750  | V    | CDM <sup>4)</sup>     | P_4.1.20 |

- 1) Not subject to production test, specified by design.

- 2)  $V_{\rm GS~GH}$  may be between -1.0 and -0.3V only if the current injected into SHx is below 4 mA

- 3) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5 k $\Omega$ , 100 pF).

- 4) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101.

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

### 4.2 Functional range

Table 3 Functional range

| Parameter                                 | Symbol       |      | Value | S                     | Unit | Note or<br>Test Condition                         | Numbe   |

|-------------------------------------------|--------------|------|-------|-----------------------|------|---------------------------------------------------|---------|

|                                           |              | Min. | Тур.  | Max.                  |      |                                                   | r       |

| Supply voltage range for normal operation | $V_{S(nor)}$ | 6.0  | -     | 28                    | V    | -                                                 | P_4.2.1 |

| Extended supply voltage range             | $V_{S(ext)}$ | 5.5  | -     | 6                     | V    | <sup>1)</sup> Parameter<br>deviations<br>possible | P_4.2.7 |

| Extended supply voltage range             | $V_{S(ext)}$ | 28   | -     | V <sub>SOV_OFF2</sub> | V    | <sup>1)</sup> Parameter<br>deviations<br>possible | P_4.2.2 |

| Supply voltage transients slew rate       | $dV_S/dt$    | -10  | -     | 10                    | V/µs | 1)                                                | P_4.2.3 |

| Logic supply voltage                      | $V_{\rm DD}$ | 3.0  | _     | 5.5                   | V    | _                                                 | P_4.2.4 |

## **Multiple MOSFET Driver IC**

#### **General product characteristics**

Functional range (cont'd) Table 3

| Parameter               | Symbol                                         |      | Value | S               | Unit | Note or<br>Test Condition | Numbe   |

|-------------------------|------------------------------------------------|------|-------|-----------------|------|---------------------------|---------|

|                         |                                                | Min. | Тур.  | Max.            |      |                           | r       |

| SPI logic input voltage | $V_{\rm SDI}$ , $V_{\rm SCLK}$ , $V_{\rm CSN}$ | 0    | -     | V <sub>DD</sub> | V    | -                         | P_4.2.5 |

| Junction temperature    | $T_{\rm j}$                                    | -40  | _     | 150             | °C   | -                         | P_4.2.6 |

<sup>1)</sup> Not subject to production test, specified by design.

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

### **Multiple MOSFET Driver IC**

#### **General product characteristics**

#### 4.3 Thermal resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more

information, go to www.jedec.org.

#### Table 4 Thermal resistance

| Parameter           | Symbol         | Values |      | Values |     | Note or               | Number |

|---------------------|----------------|--------|------|--------|-----|-----------------------|--------|

|                     |                | Min.   | Тур. | Max.   |     | <b>Test Condition</b> |        |

| Junction to case    | $R_{thJC}$     | _      | 7.1  | _      | K/W | 1)                    |        |

| Junction to ambient | $R_{\rm thJA}$ | _      | 31   | _      | K/W | 1)2)                  |        |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70 mm Cu, 2 × 35 mm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

#### **General description**

### 5 General description

### 5.1 Power supply

The Multiple MOSFET Driver IC requires two power supplies:  $V_{\rm S}$  and  $V_{\rm DD}$ .

$V_{\rm DD}$  supplies the I/O buffers (including the SPI pins) and the internal voltage regulator for the logic.  $V_{\rm DD}$  allows the flexibility of a 3.3 V or a 5.0 V logic interface.

$V_{\rm S}$  supplies the charge pump for the MOSFET gate drivers. The  $V_{\rm S}$  pin must be connected to the battery through a reverse battery protection.

Both supplies are separated so that the information stored in the logic remains intact in the event of voltage drop on  $V_S$ .  $V_{DD}$  and  $V_S$  should be decoupled with ceramic capacitors connected close to the supply and ground planes.

#### 5.2 Operation modes

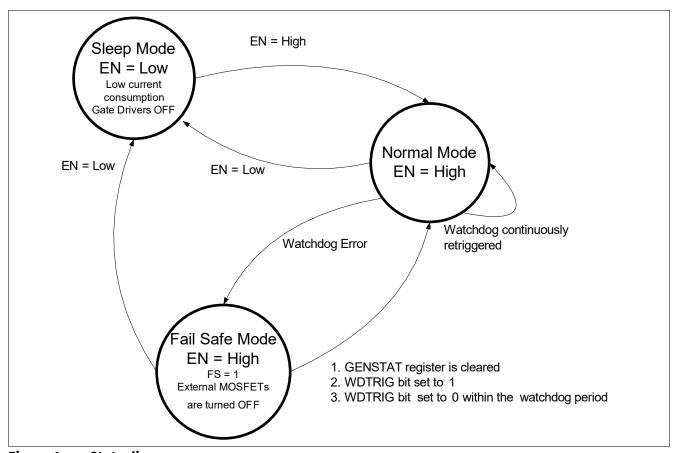

Figure 4 State diagram

Note: The state diagram is valid for  $V_S$  and  $V_{DD}$  within the nominal operating range. For  $V_S$  and  $V_{DD}$  outside of the nominal range, refer to **Chapter 7.7**, respectively **Chapter 5.2.2**.

#### 5.2.1 Normal mode

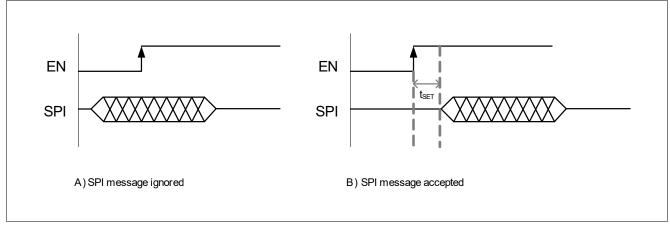

The TLE92104-131 enters Normal Mode by setting EN pin to High and waiting for the SPI setup time  $t_{\text{SET\_SPI}}$ . In normal mode, the MOSFET gate drivers are enabled and can be configured through the SPI interface, provided

#### **Multiple MOSFET Driver IC**

#### **General description**

that the voltages applied to  $V_{DD}$  and  $V_{S}$  are within the operating range. The watchdog must be retriggered correctly in order to stay in Normal Mode (see **Chapter 7.9**).

#### 5.2.2 Sleep mode

The Multiple MOSFET Driver IC enters Sleep Mode by setting EN pin to Low. The transition to the sleep mode is delayed by  $t_{DSLEEP}^{1)}$  (max tCCP of active half-bridges + 3  $\mu$ s) in order to actively turn-off the external MOSFETs. In this mode, the internal regulator and the internal circuitry are deactivated, and the SPI registers are reset.

The current consumption of  $V_{DD}$  is reduced to  $I_{DD_Q}$ . The current consumption of  $V_S$  is reduced to  $I_{SQ}$  or  $I_{SQ}$  +  $I_{SO}$  BRAKE.

The  $V_S$  current consumption is  $I_{SQ}$  if  $V_S$  never drops below  $V_{SLEEP\_SET}$  after entering sleep mode.

The  $V_S$  current consumption is  $I_{SQ} + I_{SQ\_BRAKE}$  if  $V_S$  has recovered from a voltage below  $V_{SLEEP\_SET}$  (i.e.  $V_S$  has ramped up from a voltage below  $V_{SLEEP\_SET}$ )

The internal resistors  $R_{GGND}$  between GHx/GLx and GND are activated to discharge the gate of the external MOSFETs.

Note:

If EN is set to Low for a duration shorter than ( $t_{\text{ENL\_FILT}}$ , 8  $\mu$ s max.), and EN is set to High again, then device does not go in sleep mode and the registers are not reset. The half-bridges are reactivated according to the settings of the control registers when EN is High.

#### 5.2.3 Fail Safe Mode

In case of watchdog error (see **Chapter 7.9**), the device enters Fail Safe Mode, FS bit is set (see **Global status byte**) and the external MOSFETs are actively discharged with the static discharge current (**Chapter 6.2**) during the max. configured tHBxCCP active (**Chapter 7.4.1**). Then the bridge driver is set to passive mode (the passive discharge path is activated, **Chapter 6.4**, all external MOSFETs are latched off, and the charge pump is deactivated). To resume Normal Mode the microcontroller must execute the following sequence<sup>2)</sup>:

- 1. Clear **GENSTAT** register.

- 2. Write WDTRIG bit to 1 (**GENCTRL1**) within the watchdog period.

- 3. Write WDTRIG bit to 0 within the watchdog period<sup>3)</sup>.

In fail safe mode, the control registers are frozen to their default value, at the exception of **WDTRIG**, **CCSO**, **CSA1L**. Any write command (except for WDTRIG bit) or clear command (except for GENSTAT) will be discarded in this mode and sets SPIE bit (**Global status byte**).

A clear command to **GENSTAT** in fail safe mode does not reset any failure flag reported by this status register. The control and status registers can be read in this mode before the start of the exit sequence without SPIE bit being set.

<sup>1)</sup> SPI Frames are ignored during t<sub>DSLEEP</sub>.

<sup>2)</sup> The exit sequence must be strictly followed to leave fail safe mode. If a SPI frame not belonging to the sequence is added, then the device stays in fail safe mode and the microcontroller must restart the complete sequence to enter normal mode.

<sup>3)</sup> During Fail Safe Mode, the charge pump is deactivated and **CPUV** is set. Therefore, recovering from Fail Safe Mode, **GENSTAT** must be cleared again at the end of the Fail Safe exit sequence to re-activate of the gate drivers.

### **Multiple MOSFET Driver IC**

#### **General description**

#### 5.3 Reset behavior

The following events trigger a Power On Reset:

#### **V**<sub>DD</sub> undervoltage reset:

If  $V_{\rm DD} < V_{\rm DD\,PoffR}$  the digital block is deactivated and the outputs are switched off. The digital block is reset once  $V_{\rm DD} > V_{\rm DD\,PoR}$ . Then NPOR bit (negated power-on reset bit, see **Global status byte**) is reset to 0 to report the reset condition.

#### Reset on EN pin:

If the EN pin is pulled low, the logic content is reset and the device enters sleep mode. Once the device enters Normal Mode (after  $\mathbf{t}_{\mathtt{SET\_SPI}}$  with EN = high and  $V_{\mathtt{DD}} > V_{\mathtt{DD\ POR}}$ ), the NPOR bit is reset to 0 to report the reset condition.

NPOR is set to 1 when **GENSTAT** is cleared.

## **Multiple MOSFET Driver IC**

#### **General description**

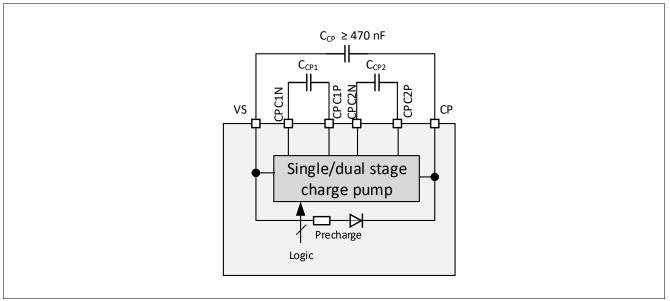

#### 5.4 **Charge pump**

A dual-stage charge pump supplies the gate drivers for the high-side and low-side MOSFETs. It requires three external capacitors connected between CPC1N and CPC1P, CPC2N and CPC2P, VS and CP.

Figure 5 **Charge pump**

CPSTGA = 0 (default, see **GENCTRL2**), the device operates with the dual-stage charge pump.

If CPSTGA = 1 (GENCTRL2), the device switches automatically to single-stage or dual-stage charge pump automatically:

- If  $V_S > V_{CPSO\,DS}$ : the TLE92104-131 switches from a dual-stage to a single-stage charge pump.

- If  $V_S < V_{CPSO,SD}$ : the TLE92104-131 switches from single-stage to dual-stage charge pump.

The operation with the single-stage charge pump reduces the current consumption from the VS pin.

#### 5.5 **Frequency modulation**

A modulation of the charge pump frequency can be activated to reduce the peak emission. The modulation frequency can be selected based on the resolution bandwidth of the peak detector during EMC testing.

The modulation frequency is set by the control bit FMODE in **GENCTRL1**

- FMODE = 0: No modulation.

- FMODE = 1: Modulation frequency = 15.6 kHz (default).

## **Multiple MOSFET Driver IC**

#### **General description**

#### **Electrical characteristics** 5.6

#### **Electrical characteristics: supply** 5.6.1

#### Table 5 **Electrical characteristics: supply**

$V_{\rm S}$  = 6.0 V to 18 V if VSOVTH = 0,  $V_{\rm S}$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{\rm DD}$  = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                          | Symbol                          | Values |      |                       | Unit | Note or                                                                                                                                                                   | Number   |

|----------------------------------------------------|---------------------------------|--------|------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                    |                                 | Min.   | Тур. | Max.                  |      | <b>Test Condition</b>                                                                                                                                                     |          |

| Current consumption, EN =                          | LOW)                            | •      | •    |                       |      |                                                                                                                                                                           |          |

| Supply quiescent current                           | I <sub>SQ</sub>                 | -      | 2    | 5                     | μΑ   | $T_{\rm j}$ < 85°C, $V_{\rm S}$ = 13.5 V                                                                                                                                  | P_5.5.1  |

| Supply quiescent current                           | I <sub>SQ2</sub>                | -      | 5    | 7                     | μΑ   | $T_{\rm j}$ < 85°C, $V_{\rm S}$ < 25 V                                                                                                                                    | P_5.5.61 |

| Additional supply quiescent current, brake enabled | I <sub>SQ_BRAKE</sub>           | -      | 5    | 7.5                   | μΑ   | $T_{\rm j}$ < 85°C,<br>$V_{\rm S}$ = 13.5 V <sup>1)</sup>                                                                                                                 | P_5.5.60 |

| Logic Supply quiescent current                     | $I_{\mathrm{DD}_{-}\mathrm{Q}}$ | -      | 1    | 3                     | μΑ   | <i>T</i> <sub>j</sub> < 85°C                                                                                                                                              | P_5.5.3  |

| Total quiescent current                            | $I_{DD_Q} + I_{SQ}$             | -      | 3    | 8                     | μΑ   | $T_{\rm j}$ < 85°C, $V_{\rm S}$ = 13.5 V                                                                                                                                  | P_5.5.5  |

| EN Low filter time                                 | t <sub>DSLEEP</sub>             | -      | -    | Max.<br>tCCP+<br>3 μs | μs   | <sup>2)3)</sup> <b>BD_PASS</b> = 0                                                                                                                                        | P_5.5.49 |

| EN Low filter time                                 | t <sub>ENL_FILT</sub>           | 1      | _    | 8                     | μs   | 2)                                                                                                                                                                        | P_5.5.51 |

| VS for LS1-4 setting                               | V <sub>SLEEP_SET</sub>          | -      | _    | 5.5                   | V    |                                                                                                                                                                           | P_5.5.63 |

| Current consumption, EN =                          |                                 |        |      |                       |      |                                                                                                                                                                           | 1        |

| Supply current                                     | I <sub>S1</sub>                 | -      | 45   | 55                    | mA   | $HBxVDSTH = 001_B,$ $BD_PASS = 0,$ $I_{CP} = 0 \text{ mA}$                                                                                                                | P_5.5.6  |

| Supply current                                     | I <sub>52</sub>                 | -      | 83   | 100                   | mA   | $8 \text{ V} < V_S < 28 \text{ V}$<br>$\text{HBxVDSTH} = 001_B$ ,<br>$\text{BD\_PASS} = 0$ ,<br>$I_{\text{CP}} = -12 \text{ mA}$ ,<br>dual stage CP                       | P_5.5.7  |

| Supply current                                     | I <sub>53</sub>                 | -      | 55   | 70                    | mA   | $18 \text{ V} < V_{\text{S}} < 28 \text{ V}$<br>$\text{HBxVDSTH} = 001_{\text{B}},$<br>$\text{BD\_PASS} = 0,$<br>$I_{\text{CP}} = -12 \text{ mA}^{2},$<br>single stage CP | P_5.5.56 |

| Supply current                                     | I <sub>S4</sub>                 | -      | 55   | 70                    | mA   | $V_S = 6 \text{ V},$<br>$HBxVDSTH = 001_B,$<br>$BD\_PASS = 0,$<br>$I_{CP} = -6 \text{ mA}^{2}$                                                                            | P_5.5.57 |

| Supply current                                     | I <sub>S_BD_PASS</sub>          | -      | 10   | 20                    | mA   | HBxMODE=00 <sub>B</sub> , BD_PASS = 1                                                                                                                                     | P_5.5.54 |

# TLE92104-131 Multiple MOSFET Driver IC

# infineon

#### **General description**

## Table 5 Electrical characteristics: supply (cont'd)

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_j$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                 | Symbol                 |      | Values |      |    | Note or                                                                                                                         | Number   |

|-------------------------------------------|------------------------|------|--------|------|----|---------------------------------------------------------------------------------------------------------------------------------|----------|

|                                           |                        | Min. | Тур.   | Max. |    | <b>Test Condition</b>                                                                                                           |          |

| Logic supply current                      | I <sub>DD1</sub>       | _    | 3      | 4    | mA | SPI not active,<br>CSA1 off, all I <sub>PDDiag</sub><br>off, <b>BD_PASS=</b> 0                                                  | P_5.5.8  |

| Logic supply current                      | I <sub>DD2</sub>       | -    | 3      | 3.8  | mA | 4) Additional VDD<br>current per CSA on,<br>VCSOx = 4.5 V,<br>LS shunt, CCSO = 1<br>CSAxL = 0,<br>IPDDiag off                   | P_5.5.52 |

| Logic supply current                      | I <sub>DD3</sub>       | -    | 2      | 2.8  | mA | 4) Additional VDD<br>current per CSA on,<br>CCSO = 0,<br>VCSOx = 4.5 V,<br>LS shunt,<br>CSAxL = 0,<br>IPDDiag off               | P_5.5.55 |

| Logic supply current                      | I <sub>DD4</sub>       | -    | 6      | 7    | mA | 5) Additional VDD<br>current per CSA on,<br>VCSOx = 4.5 V,<br>HS shunt,<br>VSOVTH = 1<br>CSAxL = 1,<br>I <sub>PDDiag</sub> off  | P_5.5.58 |

| Logic supply current                      | I <sub>DD5</sub>       | -    | 4.2    | 5.2  | mA | 5) Additional VDD<br>current per CSA on,<br>VSOVTH = 0,<br>VCSOx = 4.5 V,<br>HS shunt,<br>CSAxL = 1,<br>I <sub>PDDiag</sub> off | P_5.5.59 |

| Additional logic supply current pull-down | I <sub>DD_PDDiag</sub> | _    | 1.5    | 2    | mA | Additional VDD current when all $I_{\text{PDDiag}}$ are on                                                                      | P_5.5.53 |

| VS with active bridge dri                 | ver (BD_PASS           | = o) | ·      | ·    |    |                                                                                                                                 |          |

| UV switch ON voltage                      | $V_{\sf SUVON}$        | _    | -      | 5.5  | ٧  | V <sub>s</sub> increasing                                                                                                       | P_5.5.11 |

| UV switch OFF voltage                     | V <sub>SUV OFF</sub>   | 4.0  | 4.5    | 5.0  | V  | V <sub>S</sub> decreasing                                                                                                       | P_5.5.12 |

| UV ON/OFF hysteresis                      | V <sub>SUV HY</sub>    | -    | 0.5    | _    | V  | V <sub>SUV ON</sub> - V <sub>SUV OFF</sub> 2)                                                                                   | P_5.5.13 |

| OV switch OFF voltage<br>VSOVTH = 0       | V <sub>SOV OFF1</sub>  | 19   | -      | 21   | V  | V <sub>s</sub> increasing                                                                                                       | P_5.5.14 |

| OV switch ON voltage<br>VSOVTH = 0        | V <sub>SOV ON1</sub>   | 18   | -      | 20   | V  | $V_{\rm S}$ decreasing                                                                                                          | P_5.5.15 |

#### **Multiple MOSFET Driver IC**

#### **General description**

#### Table 5 **Electrical characteristics: supply (cont'd)**

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_i$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                        | Symbol                 | Values                                           |      |      | Unit | Note or                                       | Number   |

|--------------------------------------------------|------------------------|--------------------------------------------------|------|------|------|-----------------------------------------------|----------|

|                                                  |                        | Min.                                             | Тур. | Max. |      | <b>Test Condition</b>                         |          |

| OV switch OFF voltage<br>VSOVTH = 1              | V <sub>SOV OFF2</sub>  | 29                                               | -    | 31   | V    | $V_{\rm S}$ increasing                        | P_5.5.16 |

| OV switch ON voltage<br>VSOVTH = 1               | V <sub>SOV ON2</sub>   | 28                                               | -    | 30   | V    | $V_{\rm S}$ decreasing                        | P_5.5.17 |

| OV ON/OFF hysteresis                             | V <sub>SOV HY</sub>    | _                                                | 1    | _    | V    | V <sub>SUV ON</sub> - V <sub>SUV OFF</sub> 2) | P_5.5.18 |

| VS undervoltage filter time                      | t <sub>VSUV_FILT</sub> | 7                                                | 10   | 13   | μs   | 1)                                            | P_5.5.47 |

| VS overvoltage filter time                       | t <sub>VSOV_FILT</sub> | 7                                                | 10   | 13   | μs   | 2)                                            | P_5.5.48 |

| CP turn-off delay after VS overvoltage detection | $t_{D\_CPVSOV}$        | 12.8                                             | 16   | 19.2 | μs   | 2)                                            | P_5.5.50 |

| VDD                                              |                        | <del>-                                    </del> |      |      | *    |                                               | •        |

| V <sub>DD</sub> Power-On-Reset                   | V <sub>DD POR</sub>    | 2.40                                             | 2.60 | 2.80 | V    | V <sub>DD</sub> increasing                    | P_5.5.19 |

| V <sub>DD</sub> Power-Off-Reset                  | V <sub>DD POffR</sub>  | 2.30                                             | 2.50 | 2.70 | V    | V <sub>DD</sub> decreasing                    | P_5.5.20 |

| V <sub>DD</sub> Power-On-Reset<br>Hysteresis     | V <sub>DD POR HY</sub> | -                                                | 0.1  | -    | V    | $V_{\rm DDPOR}$ - $V_{\rm DDPOffR}^{2)}$      | P_5.5.21 |

- 1) Additional quiescent current if VS drops below V<sub>SLEEP\_SET</sub>.

- 2) Not subject to production test, specified by design.

- 3) Max. cross-current protection time of the active half-bridges.

- 4) Parameter independent of **VSOVTH**.

- 5) Parameter independent of CCSO.

#### 5.6.2 **Electrical characteristics: logic inputs PWMx, EN**

#### **Electrical characteristics: PWMx, EN**

$V_S$  = 6.0 V to 18 V if VSOVTH = 0,  $V_S$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{DD}$  = 3.0 V to 5.5 V,  $T_i$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter             | Symbol            | Values                |                        | Unit                  | Note or | Number                |          |

|-----------------------|-------------------|-----------------------|------------------------|-----------------------|---------|-----------------------|----------|

|                       |                   | Min.                  | Тур.                   | Max.                  |         | <b>Test Condition</b> |          |

| EN high voltage       | V <sub>ENH</sub>  | 0.7 × V <sub>DD</sub> | -                      | -                     | V       | _                     | P_5.5.22 |

| EN low voltage        | $V_{ENL}$         | -                     | -                      | 0.3 × V <sub>DD</sub> | V       | _                     | P_5.5.23 |

| EN hysteresis         | V <sub>ENHY</sub> | -                     | 0.12 × V <sub>DD</sub> | -                     | V       | 1)                    | P_5.5.24 |

| EN pull-down resistor | $R_{PD_{EN}}$     | 30                    | 40                     | 50                    | kΩ      | _                     | P_5.5.25 |

| PWMx high voltage     | V <sub>PWMH</sub> | 0.7 × V <sub>DD</sub> | -                      | _                     | V       | _                     | P_5.5.26 |

| PWMx low voltage      | $V_{PWML}$        | _                     | _                      | 0.3 × V <sub>DD</sub> | V       | -                     | P_5.5.27 |

## **Multiple MOSFET Driver IC**

#### **General description**

#### **Electrical characteristics: PWMx, EN** Table 6

$V_{\rm S}$  = 6.0 V to 18 V if VSOVTH = 0,  $V_{\rm S}$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{\rm DD}$  = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter               | Symbol               |      | Values                 |      | Unit | Note or               | Number   |

|-------------------------|----------------------|------|------------------------|------|------|-----------------------|----------|

|                         |                      | Min. | Тур.                   | Max. |      | <b>Test Condition</b> |          |

| PWMx hysteresis         | $V_{PWMHY}$          | -    | 0.12 × V <sub>DD</sub> | _    | V    | 1)                    | P_5.5.28 |

| PWMx pull-down resistor | R <sub>PD_PWMx</sub> | 30   | 40                     | 50   | kΩ   | -                     | P_5.5.29 |

<sup>1)</sup> Not subject to production test, specified by design.

#### **Electrical characteristics charge pump** 5.6.3

#### Table 7 **Electrical characteristics: charge pump**

$V_S = 6.0 \text{ V to } 18 \text{ V if VSOVTH} = 0$ ,  $V_S = 6.0 \text{ V to } 28 \text{ V if VSOVTH} = 1$ ;  $V_{DD} = 3.0 \text{ V to } 5.5 \text{ V}$ ,  $T_i = -40 ^{\circ}\text{C}$  to  $150 ^{\circ}\text{C}$ , all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                              | Symbol                 | Values |      |      | Unit | Unit Note or                                                                   | Number   |

|--------------------------------------------------------|------------------------|--------|------|------|------|--------------------------------------------------------------------------------|----------|

|                                                        |                        | Min.   | Тур. | Max. |      | <b>Test Condition</b>                                                          |          |

| Charge Pump Frequency                                  | $f_{\sf CP}$           | _      | 250  | _    | kHz  | 3)                                                                             | P_5.5.30 |

| Output Voltage VCP vs. VS                              | V <sub>CPmin</sub>     | 8.5    | -    | -    | V    | $V_{\rm S} = 6  \rm V$ ,<br>$I_{\rm CP} = -6  \rm mA$                          | P_5.5.31 |

| Regulated output voltage VCP vs. VS, CPSTGA = 0        | V <sub>CP1</sub>       | 11     | 15   | 17   | V    | $8 \text{ V} < V_{\text{S}} < 28 \text{ V},$ $I_{\text{CP}} = -12 \text{ mA}$  | P_5.5.32 |

| Regulated output voltage<br>VCP vs. VS, CPSTGA = 1     | V <sub>CP2</sub>       | 12     | 15   | 17   | V    | $18 \text{ V} < V_{\text{S}} < 28 \text{ V},$ $I_{\text{CP}} = -12 \text{ mA}$ | P_5.5.41 |

| Turn-on time, CPSTGA = 0                               | t <sub>ON_VCP1</sub>   | 10     | 40   | 80   | μs   | $8 \text{ V} < V_{\text{S}} < 28 \text{ V}$<br>(25%) <sup>1)2)3)4)</sup>       | P_5.5.34 |

| Rise time, CPSTGA = 0                                  | $t_{RISE\_VCP1}$       | 10     | 60   | 100  | μs   | $8 \text{ V} < V_{\text{S}} < 28 \text{ V}$<br>(25%-75%) <sup>1)2)3)4)</sup>   | P_5.5.35 |

| Turn-on time, CPSTGA = 1                               | t <sub>ON_VCP2</sub>   | 10     | 40   | 80   | μs   | $18 \text{ V} < V_{\text{S}} < 28 \text{ V}$ $(25\%)^{1(2)3(5)}$               | P_5.5.36 |

| Rise time, CPSTGA = 1                                  | t <sub>RISE_VCP2</sub> | 10     | 60   | 100  | μs   | $18 \text{ V} < V_{\text{S}} < 28 \text{ V}$ $(25\%-75\%)^{1/2/3/5}$           | P_5.5.37 |

| Charge Pump Undervoltage (referred to VS)              | V <sub>CPUV1</sub>     | 5.5    | 6    | 6.5  | V    | CPUVTH = 0,<br>VCP falling                                                     | P_5.5.38 |

| Charge Pump Undervoltage (referred to VS)              | V <sub>CPUV2</sub>     | 7      | 7.5  | 8    | V    | CPUVTH = 1,<br>VCP falling                                                     | P_5.5.42 |

| Automatic switch over dual to single stage charge pump | V <sub>CPSO DS</sub>   | 16     | 17   | 18   | V    | CPSTGA = 1                                                                     | P_5.5.43 |

| Automatic switch over single to dual stage charge pump | V <sub>CPSO SD</sub>   | 15.5   | 16.5 | 17.5 | V    | CPSTGA = 1                                                                     | P_5.5.44 |

| Charge pump switch over hysteresis                     | V <sub>CPSO HY</sub>   | -      | 0.5  | -    | V    | <sup>3)</sup> <b>CPSTGA</b> = 1,<br>$V_{\text{CPSO DS}} - V_{\text{CPSO SD}}$  | P_5.5.45 |

| Charge Pump Undervoltage<br>Filter Time                | $t_{CPUV}$             | 51     | 64   | 77   | μs   | 3)                                                                             | P_5.5.39 |

### **Multiple MOSFET Driver IC**

#### **General description**

#### Table 7 **Electrical characteristics: charge pump**

$V_{\rm S}$  = 6.0 V to 18 V if VSOVTH = 0,  $V_{\rm S}$  = 6.0 V to 28 V if VSOVTH = 1;  $V_{\rm DD}$  = 3.0 V to 5.5 V,  $T_{\rm j}$  = -40°C to 150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                          | Symbol             |      | Values |      |    | Note or                                                | Number |

|------------------------------------|--------------------|------|--------|------|----|--------------------------------------------------------|--------|

|                                    |                    | Min. | Тур.   | Max. |    | <b>Test Condition</b>                                  |        |

| Charge pump minimum output current | I <sub>CPOC1</sub> | -    | -      | -12  | mA | $^{2)3)4)} V_S = 13.5 \text{ V};$<br><b>CPSTGA</b> = 0 |        |

| Charge pump minimum output current | I <sub>CPOC2</sub> | -    | -      | -12  | mA | $^{2)3)5)} V_S = 18 \text{ V};$ <b>CPSTGA</b> = 1      |        |

- 1) Parameter dependent on the capacitance  $C_{CP}$ .

- 2)  $C_{CPC1} = C_{CPC2} = 220 \text{ nF}, C_{CP} = 470 \text{ nF}, I_{CP} = 0 \text{ mA}.$

- 3) Not subject to production test, specified by design.

- 4) Dual stage charge pump.

- 5) Single stage charge pump.

#### **Multiple MOSFET Driver IC**

#### Floating gate drivers

#### Floating gate drivers 6

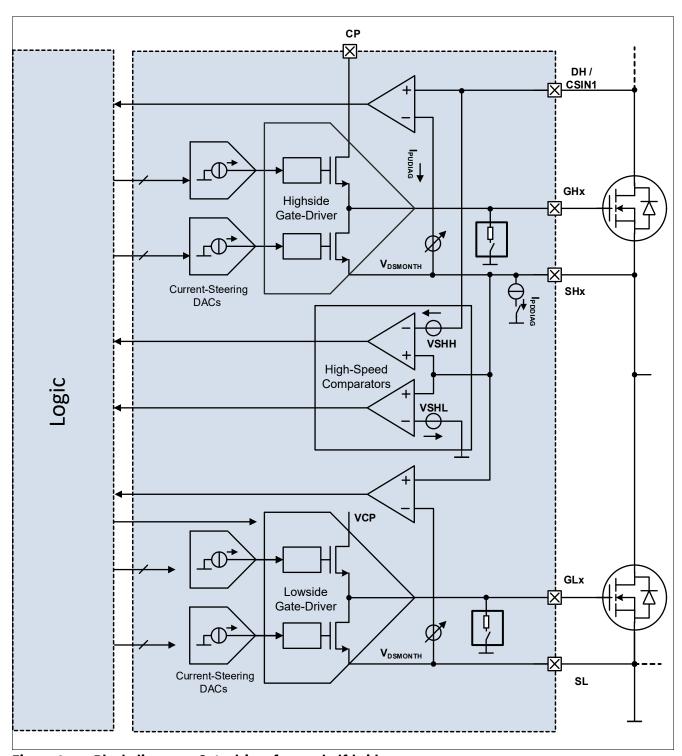

The TLE92104-131 integrates eight floating gate drivers capable of controlling a wide range of n-channel MOSFETs. They are configured as four high-sides and low-sides, building four half-bridges.

This section describes the MOSFET control by the gate drivers.

After power-on reset, the bridge driver is in passive mode (default value of BD\_PASS = 1 and all HBxMODE=00<sub>B</sub>). Refer to **Chapter 6.4** and **Chapter 6.5**.

The bridge driver is in active mode by setting BD\_PASS to 0. Chapter 6.1, Chapter 6.2 and Chapter 6.3 describes the static and PWM control in active mode.

Attention: It is highly recommended to have all HBxMODE bits set to 00<sub>B</sub> or 11<sub>B</sub> before setting BD\_PASS to 0 in order to avoid wrong drain-source overvoltage detection.

Table 8 Operating modes of the gate driver

| EN   | BD_PASS | HBxMODE[1:0]                                   | <b>Gate driver</b>   | Comment                               | Chapter                                   |

|------|---------|------------------------------------------------|----------------------|---------------------------------------|-------------------------------------------|

| High | 0       | х                                              | Active <sup>1)</sup> |                                       | Chapter 6.1<br>Chapter 6.2<br>Chapter 6.3 |

| High | 1       | One HBxMODE = $01_{\rm B}$ or $10_{\rm B}$     | Active <sup>1)</sup> | Equivalent to EN=High and BD_PASS = 0 | Chapter 6.1<br>Chapter 6.2<br>Chapter 6.3 |

| High | 1       | All HBxMODE=00 <sub>B</sub> or 11 <sub>B</sub> | Passive              |                                       | Chapter 6.5                               |

| Low  | х       | х                                              | Passive              |                                       | Chapter 6.5                               |

<sup>1)</sup> Provided that no VS overvoltage, VS undervoltage, CP undervoltage or overtemperature failure are detected, and TLE92104-131 is not in Fail Safe Mode.

#### Floating gate drivers

Figure 6 Block diagram - Gate driver for one half-bridge

#### **Multiple MOSFET Driver IC**

#### Floating gate drivers

#### 6.1 MOSFET control with bridge driver in active mode (BD PASS = 0 and EN = High)

Depending on the configuration bits HBxMODE[1:0] (**HBMODE**, **Table 9** and **Table 11**), each high-side and low-side MOSFETs can be:

- deactivated

- activated (statically, no PWM)

- activated in PWM mode (Chapter 6.3, PWMSET)

Table 9 Half-bridge mode selection

| Configuration of HSx/LSx <sup>1)</sup>                                                       |

|----------------------------------------------------------------------------------------------|

| LSx and HSx MOSFETs are actively kept OFF (default)                                          |

| LSx MOSFET is ON (static or PWM, refer to <b>Table 11</b> ), HSx MOSFET is actively kept OFF |

| HSx MOSFET is ON (static or PWM, refer to <b>Table 11</b> ), LSx MOSFET is actively kept OFF |

| Reserved - LSx and HSx MOSFETs are actively kept OFF                                         |

|                                                                                              |

<sup>1)</sup>  $x = 1 \dots 4$ .

#### 6.2 Static activation with bridge driver in active mode (BD\_PASS = 0)

In this section, we consider the static activation of the high-side and low-side MOSFET of the half-bridge x, x = 1...4. Refer to **Table 11** for the setting of a high-side or low-side in the static or PWM operation.

If HBx is not mapped to any activated PWM channel, the low-side or high-side MOSFET of HBx is statically activated (no PWM) by setting HBxMODE[1:0] to respectively (0,1) or (1,0).

The configured cross-current protection and the Drain-Source overvoltage blank times for the Half-Bridge x are noted  $t_{\text{HBxCCP}}$  and  $t_{\text{HBxBLANK}}$  (refer to **Chapter 7.4**).

The charge and discharge currents applied to the static controlled Half-Bridge x are noted ICHGSTx (ST\_ICHG).

IHARDOFF is the maximum current that the gate drivers can sink. It corresponds to the discharge current when IDCHGx[4:0] =  $31_D$  (See **PWM\_IDCHG\_ACT**). This current is used to the keep a MOSFET off, when the opposite MOSFET of the same half-bridge is being turned on. This feature avoids parasitic cross-current conduction.

ICHGSTx is the current sourced, respectively sunk, by the gate driver to turn-on the high-side x or low-side x. ICHGSTx is configured in the control register **ST\_ICHG**.

Table 10 Static charge and discharge currents

| ICHGSTx[3:0] <sup>1)</sup> | Nom. charge current [mA] <sup>2)</sup> | Nom. discharge current [mA] <sup>3)</sup> | Max. deviation to typ. values |

|----------------------------|----------------------------------------|-------------------------------------------|-------------------------------|

| 0000 <sub>B</sub>          | 1.0                                    | 1.0                                       | +/- 60%                       |

| 0001 <sub>B</sub>          | 2.0                                    | 2.8                                       | +/- 60 %                      |

| 0010 <sub>B</sub>          | 4.5                                    | 5.7                                       | +/- 60 %                      |

| 0011 <sub>B</sub>          | 8.0                                    | 9.4                                       | +/- 38 %                      |

| 0100 <sub>B</sub>          | 12.5                                   | 14.2                                      | +/- 38 %                      |

| 0101 <sub>B</sub>          | 17.8                                   | 19.7                                      | +/- 38 %                      |

#### **Multiple MOSFET Driver IC**

#### Floating gate drivers

Table 10 Static charge and discharge currents

| ICHGSTx[3:0] <sup>1)</sup> | Nom. charge current [mA] <sup>2)</sup> | Nom. discharge current [mA] <sup>3)</sup> | Max. deviation to typ. values |

|----------------------------|----------------------------------------|-------------------------------------------|-------------------------------|

| 0110 <sub>B</sub>          | 23.9                                   | 26.0                                      | +/- 38 %                      |

| 0111 <sub>B</sub>          | 30.0                                   | 32.0                                      | +/- 28 %                      |

| 1000 <sub>B</sub>          | 37.1                                   | 39.5                                      | +/- 28 %                      |

| 1001 <sub>B</sub>          | 44.3                                   | 46.8                                      | +/- 28 %                      |

| 1010 <sub>B</sub>          | 52.3                                   | 54.7                                      | +/- 28 %                      |

| 1011 <sub>B</sub>          | 60.2                                   | 62.5                                      | +/- 28 %                      |

| 1100 <sub>B</sub>          | 68.3                                   | 70.6                                      | +/- 28 %                      |

| 1101 <sub>B</sub>          | 76.8                                   | 78.5                                      | +/- 28 %                      |

| 1110 <sub>B</sub>          | 86.0                                   | 87.0                                      | +/- 28 %                      |

| 1111 <sub>B</sub>          | 96.0                                   | 95.0                                      | +/- 25 %                      |

<sup>1)</sup> Refer to ST ICHG

- 2)  $V_S \ge 8V$  and  $V_{GS} \le V_{GS(ON)1}$  if ICHGSTx  $\le 7_D$ ,  $V_S \ge 8V$  and  $V_{GS} \le V_{GS(ON)2}$  if ICHGSTx  $\ge 8_D$

- 3)  $V_{GS} \ge V_{GS(OFF)1}$  if ICHGSTx  $\le 7_D$ ,  $V_{GS} \ge V_{GS(OFF)2}$  if ICHGSTx  $\ge 8_D$

IHOLD is the hold current used to keep the gate of the external MOSFETs in the desired state. This parameter is configurable with the **IHOLD** control bit in **GENCTRL2**.

#### If IHOLD = 0:

- the MOSFETs are kept ON with the current I<sub>CHG8</sub> (12.5 mA typ.)

- the MOSFETs are kept OFF with the current I<sub>DCHG8</sub> (14.2 mA typ.)

#### If **IHOLD** = 1:

- the MOSFETs are kept ON with the current I<sub>CHG12</sub> (23.9 mA typ.)

- the MOSFETs are kept with the current I<sub>DCHG12</sub> (26.0 mA typ.)

# The static discharge current is applied to turn off the MOSFETs when the bridge driver is in active mode when the following failures occur:

- V<sub>S</sub> undervoltage/overvoltage

- Overtemperature

- V<sub>DS</sub> overvoltage

- Charge pump undervoltage

- Overcurrent if OCEN = 1

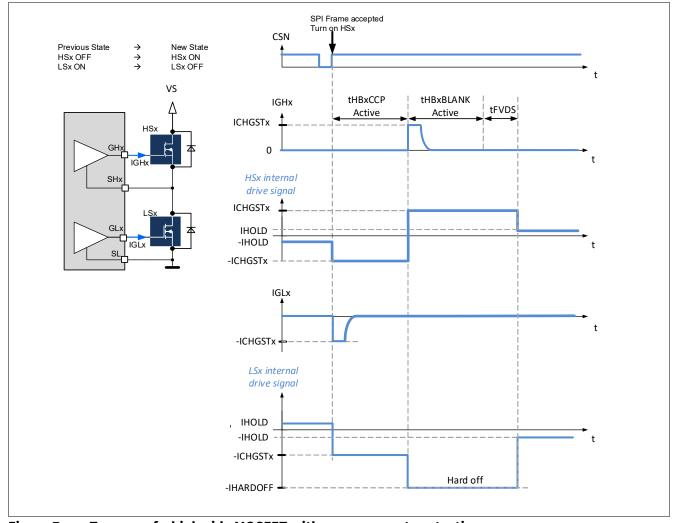

#### 6.2.1 Static activation of a high-side MOSFET

#### Turn-on with cross-current protection

If LSx is ON (HBxMODE[1:0] =  $01_B$ ), before the activation of HSx (HBxMODE[1:0] =  $10_B$ ) then the high-side MOSFET is turned on after a cross-current protection time (refer to **Figure 7**):

- after the CSN rising edge and for the duration  $t_{\text{HBxCCP Active}}$ :

- the high-side MOSFET is kept OFF with the current -ICHGSTx

- the gate of the low-side MOSFET is discharged with the current -ICHGSTx

### **Multiple MOSFET Driver IC**

#### Floating gate drivers

- at the end of  $t_{\rm HBxCCP\ Active}$  and for the duration  $t_{\rm HBxBLANK\ Active}$  +  $t_{\rm FVDS}$ :

- the gate of the high-side MOSFET is charged with the current ICHGSTx

- low-side MOSFET is kept OFF with the current -IHARDOFF (hard off phase)

- at the end of t<sub>EVDS</sub>:

- the drive current of the high-side MOSFET is reduced to IHOLD

- the drive current of the low-side MOSFET is set to -IHOLD

Figure 7 Turn-on of a high-side MOSFET with cross-current protection

Note: The CSN rising edge must be synchronized with the device logic. Therefore SPI commands are executed with a delay of up to 3 µs after the CSN rising edge.

Floating gate drivers

### **Multiple MOSFET Driver IC**

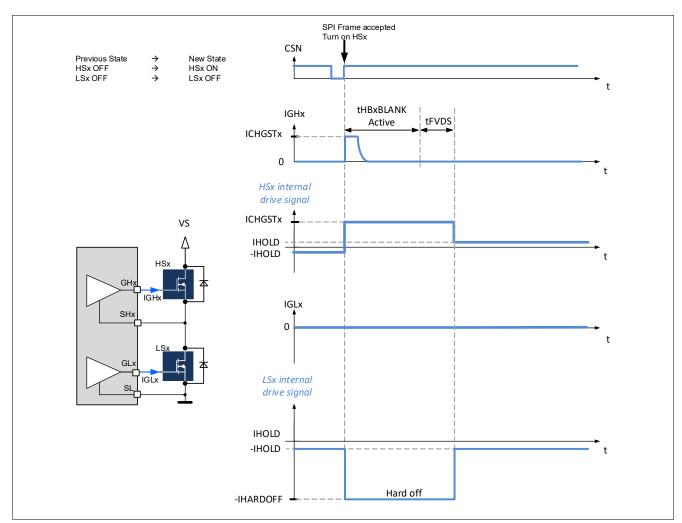

Turn-on without cross-current protection

If LSx is OFF (HBxMODE[1:0] =  $00_B$ ), before the activation of HSx (HBxMODE[1:0] =  $10_B$ ), then the high-side MOSFET is turned on without cross-current protection (refer to **Figure 8**):

- after the CSN rising edge and for a duration  $t_{\rm HBxBLANK\ Active}$  +  $t_{\rm FVDS}$ :

- the gate of the high-side MOSFET is charged with the current ICHGSTx

- the low-side MOSFET is kept OFF with the current -IHARDOFF

- at the end of  $t_{FVDS}$ :

- the drive current of the high-side MOSFET is reduced to IHOLD

- the drive current of the low-side MOSFET is set to -IHOLD

Figure 8 Turn-on of a high-side MOSFET without cross-current protection

Note: The CSN rising edge must be synchronized with the device logic. Therefore SPI commands are executed with a delay of up to 3 µs after the CSN rising edge.

### **Multiple MOSFET Driver IC**

#### Floating gate drivers

#### 6.2.2 Static activation of a low-side MOSFET

The description of the static activation of a low-side x differs from the description of **Chapter 6.2.1** only by exchanging high-side x and low-side x.

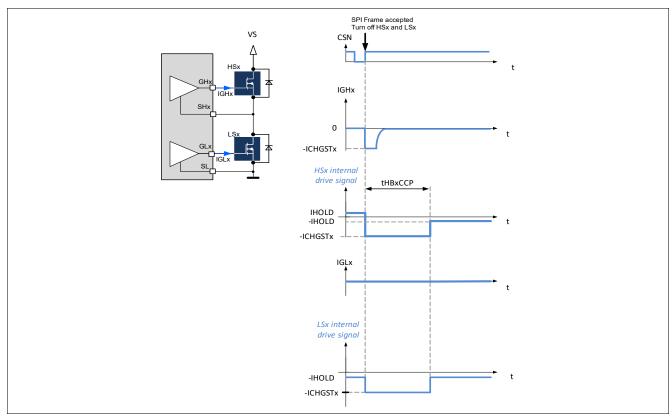

### 6.2.3 Turn-off of the high-side and low-side MOSFETs of a half-bridge

When the TLE92104-131 receives a SPI to turn-off both the high-side and low-side MOSFETs of the half-bridge x (HBxMODE[1:0] = (0,0) or (1,1)):

- the gate of HSx and LSx are discharged with the current -ICHGSTx for the duration  $t_{\text{HBxCCP Active}}$  (Figure 9)

- at the end of t<sub>HBxCCP Active</sub>, the drive current of HSx and LSx are reduced to -IHOLD

Figure 9 Turn-off of the high-side and low-side MOSFETs of a half-bridge

Note: The CSN rising edge must be synchronized with the device logic. Therefore SPI commands are executed with a delay of up to 3 µs after the CSN rising edge.

#### **Multiple MOSFET Driver IC**

#### Floating gate drivers

#### 6.3 PWM operation with bridge driver in active mode (BD\_PASS = 0)

The TLE92104-131 integrates three PWM channels. The pins PWM1,PWM2 and PWM3 provide the PWM signal for each PWM channel.

One half-bridge can be mapped to one of the PWM channels according the settings of the control registers **HBMODE** and **PWMSET** (see **Table 11**):

- PWMxEN in PWMSET, enables or disables the PWM channel x

- The control bits PWMx\_HB[2:0] in PWMSET select the half-bridge

- The control bits HBMODE[1:0] (**HBMODE**) of the half-bridge selected by PWMx\_HB[2:0] configures the low-side or the high-side MOSFET in PWM mode

Example: the following bits must be set to map the low-side of HB3 to the PWM channel 2 (start sequence with PWM):

- 1. Set HB3MODE[1:0] to (0,0): HB3 is in high impedance

- 2. Set PWM2HB[2:0] to (x,1,0) and set PWM2EN to 1 (HB3 stays in high impedance, independently from the signal present at the PWM2 pin)

- 3. Set HB3MODE[1:0] to (0,1): PWM2 is applied to the low-side of HB3

Table 11 PWM channel settings

| PWMxEN <sup>1)</sup>    | PWMx_HB[2:0]                         | HByMODE[1:0] <sup>2)</sup> | PWMx channel setting <sup>1)</sup>   |

|-------------------------|--------------------------------------|----------------------------|--------------------------------------|

| $\overline{0_{B}}$      | don't care                           | don't care                 | no PWM operation                     |

| don't care <sub>B</sub> | don't care <sub>B</sub>              | 00 <sub>B</sub>            | no PWM operation on the selected HB  |

| don't care <sub>B</sub> | don't care <sub>B</sub>              | 11 <sub>B</sub>            | no PWM operation on the selection HB |

| 1 <sub>B</sub>          | 000 <sub>B</sub> or 100 <sub>B</sub> | 01 <sub>B</sub>            | Low-side of HB1 is mapped to PWMx    |

| 1 <sub>B</sub>          | 001 <sub>B</sub> or 101 <sub>B</sub> | 01 <sub>B</sub>            | Low-side of HB2 is mapped to PWMx    |

| 1 <sub>B</sub>          | 010 <sub>B</sub> or 110 <sub>B</sub> | 01 <sub>B</sub>            | Low-side of HB3 is mapped to PWMx    |

| 1 <sub>B</sub>          | 011 <sub>B</sub> or 111 <sub>B</sub> | 01 <sub>B</sub>            | Low-side of HB4 is mapped to PWMx    |

| 1 <sub>B</sub>          | 000 <sub>B</sub> or 100 <sub>B</sub> | 10 <sub>B</sub>            | High-side of HB1 is mapped to PWMx   |

| 1 <sub>B</sub>          | 001 <sub>B</sub> or 101 <sub>B</sub> | 10 <sub>B</sub>            | High-side of HB2 is mapped to PWMx   |

| 1 <sub>B</sub>          | 010 <sub>B</sub> or 110 <sub>B</sub> | 10 <sub>B</sub>            | High-side of HB3 is mapped to PWMx   |

| 1 <sub>B</sub>          | 011 <sub>B</sub> or 111 <sub>B</sub> | 10 <sub>B</sub>            | High-side of HB4 is mapped to PWMx   |

<sup>1)</sup> x = 1 ... 3.

Note:

An SPI error is reported if one half-bridge is mapped to several activated PWM channels. In this case the external MOSFETs of the impacted half-bridge are turned-off and the corresponding status bit (HBxPWME) of the HBVOUT\_PWMERR register is set.

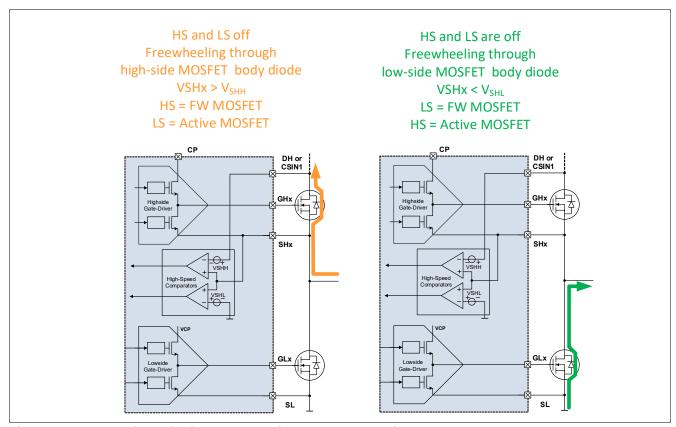

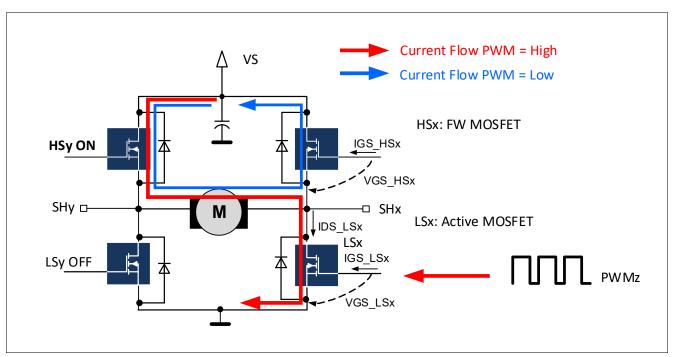

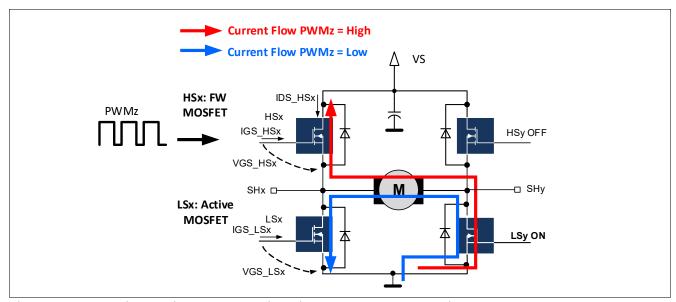

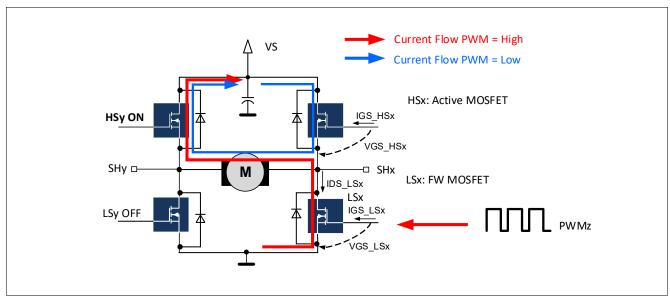

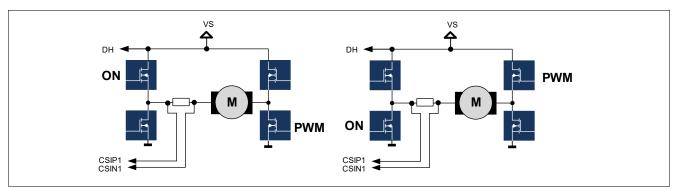

### 6.3.1 Determination of the active and free-wheeling MOSFET

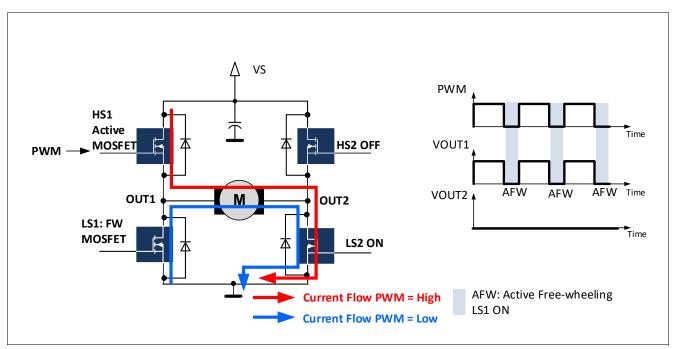

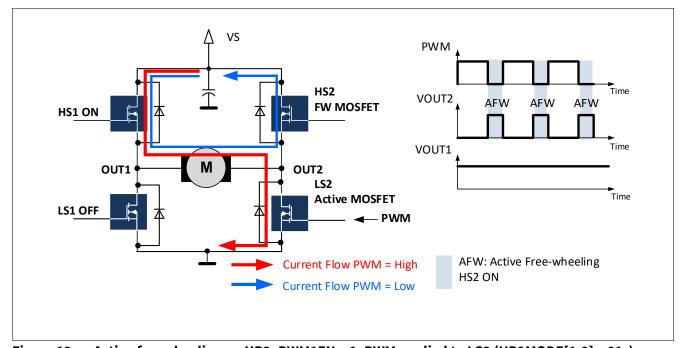

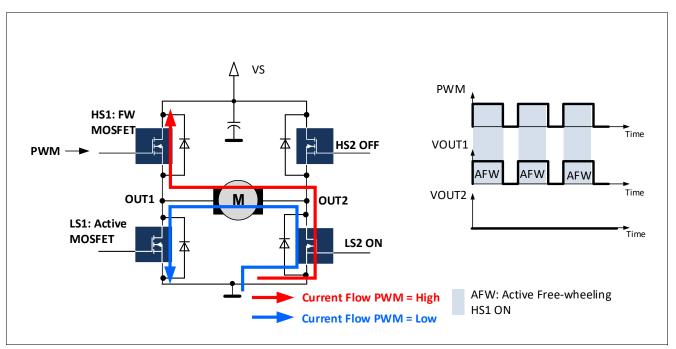

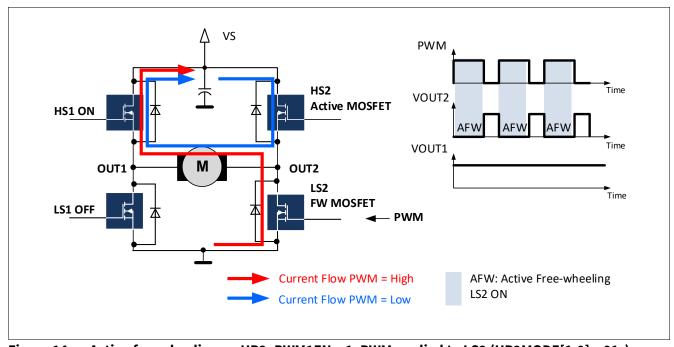

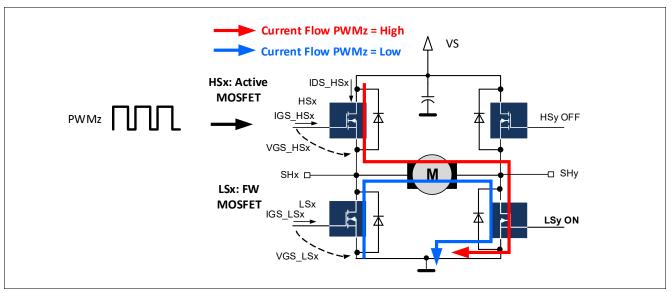

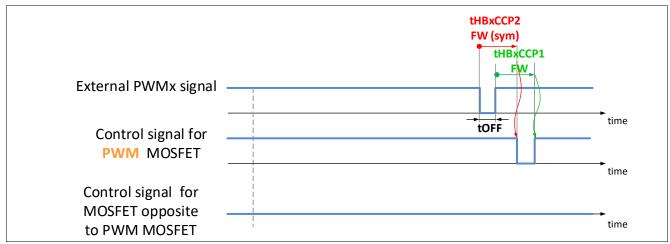

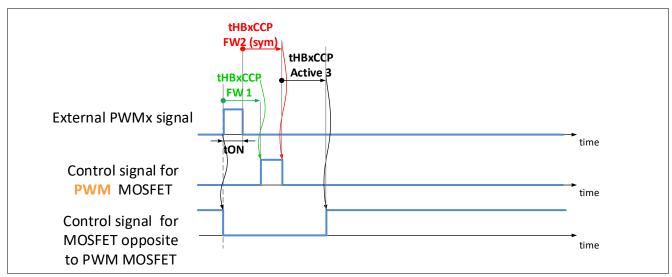

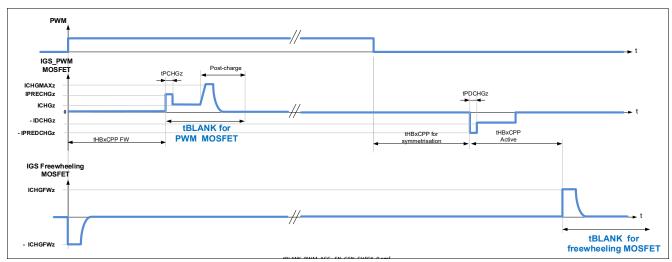

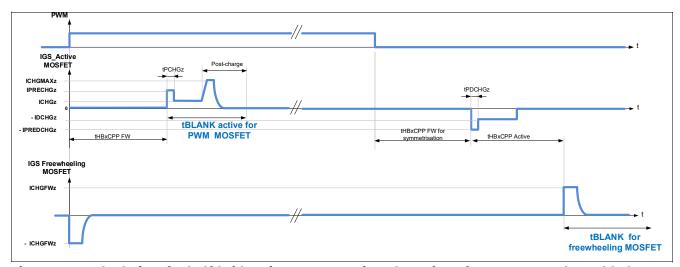

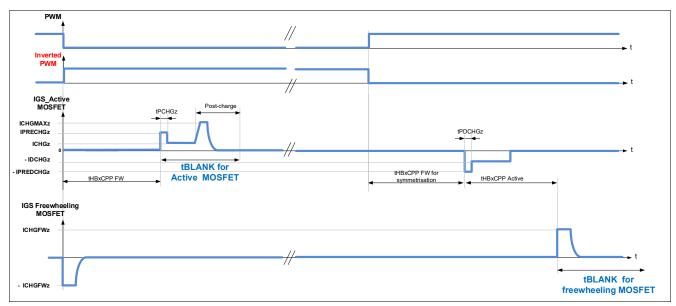

An active free-wheeling is automatically implemented when a half-bridge is activated in PWM mode to reduce the power dissipation of the free-wheeling (FW) MOSFET: If the active MOSFET is OFF, the opposite (free-wheeling) MOSFET of the same half-bridge is actively turned on. See **Figure 11**, **Figure 12**, **Figure 13**, **Figure 14**, .

<sup>2)</sup> the half-bridge y is selected by the PWMx\_HB[2:0] bits.

# infineon

#### Floating gate drivers

If **EN\_GEN\_CHECK** = 0: the PWM MOSFET is considered as the active MOSFET and the opposite MOSFET of the same half-bridge is considered as the free-wheeling MOSFET.

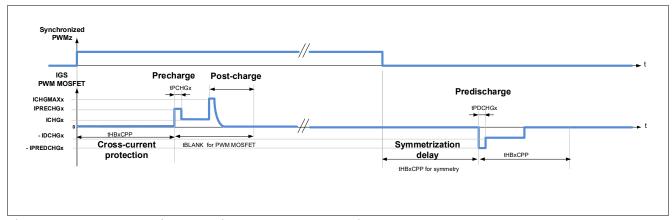

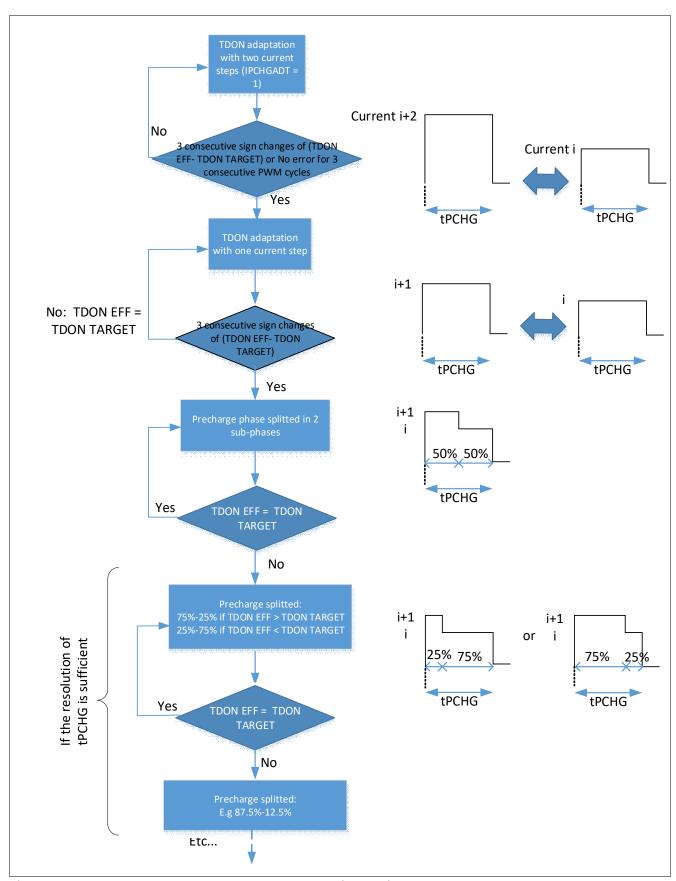

If **EN\_GEN\_CHECK** = 1: At the end of the cross-current protection times (tHBxCCP Active, tHBxCCP FW) of each MOSFET (both MOSFETs are supposed to be off) the device detects which MOSFET of the half-bridge is the active MOSFET and which MOSFET is the FW MOSFET (**Figure 10**).

- If VSHx > V<sub>SHH</sub>: The high-side MOSFET is the FW MOSFET and the low-side MOSFET is the active MOSFET

- If VSHx < V<sub>SHL</sub>: Then the low-side MOSFET is the FW MOSFET and the high-side MOSFET is the active MOSFET

- If V<sub>SHL</sub> < VSHx < V<sub>SHH</sub>: No clear distinction between the FW MOSFET and the active MOSFET. The MOSFET to be turned on is considered as the active MOSFET.

Figure 10 Detection principle of the active and freewheeling MOSFET

Note: The PWM signal is applied to the MOSFET selected by HBxMODE[1:0], independently from the freewheeling and the active MOSFET.

Note: It is not possible to determine the active or FW MOSFET if the PWM on-time is shorter than tHBxCCP FW, or if the PWM-off-time is shorter than tHBxCCP Active (Refer to **Chapter 6.3.5**). In this case, the PWM MOSFET is considered as the active MOSFET. In other words, it is assumed that the motor operates as load.

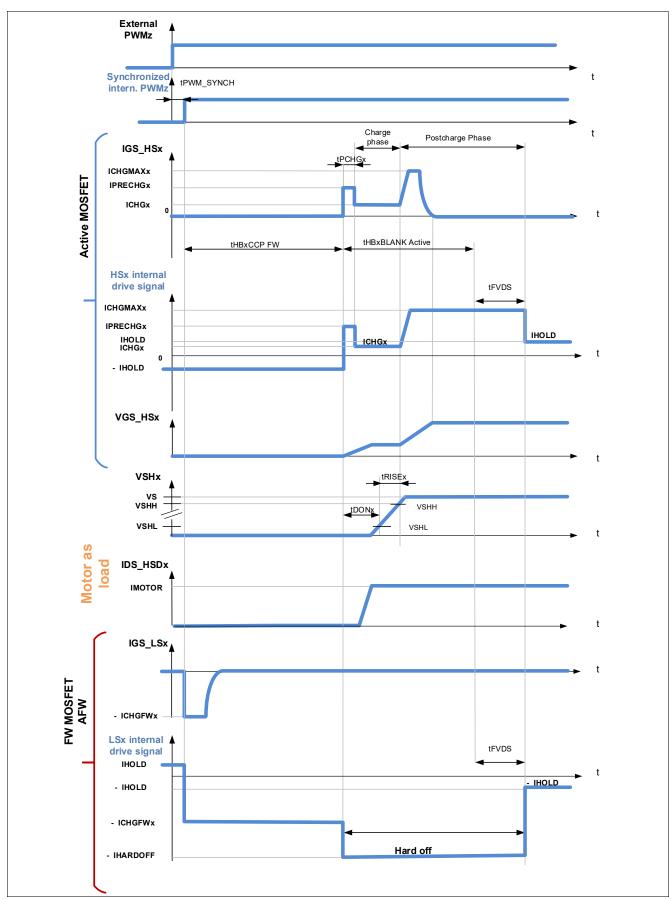

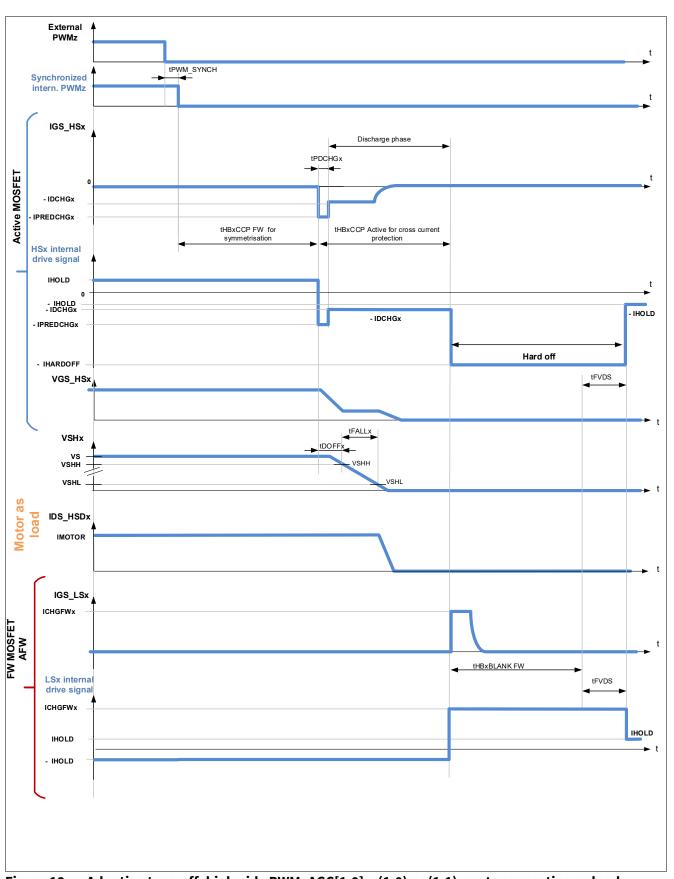

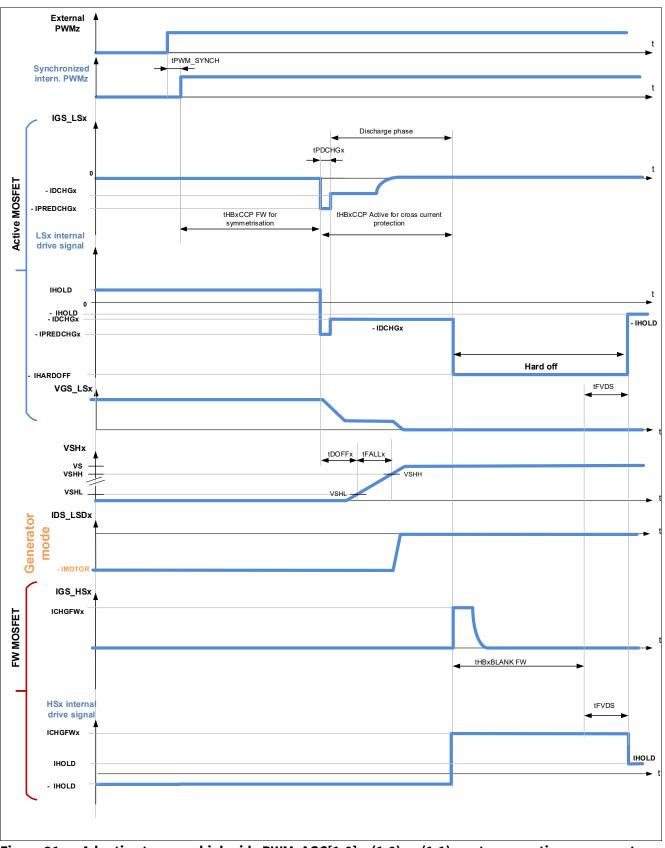

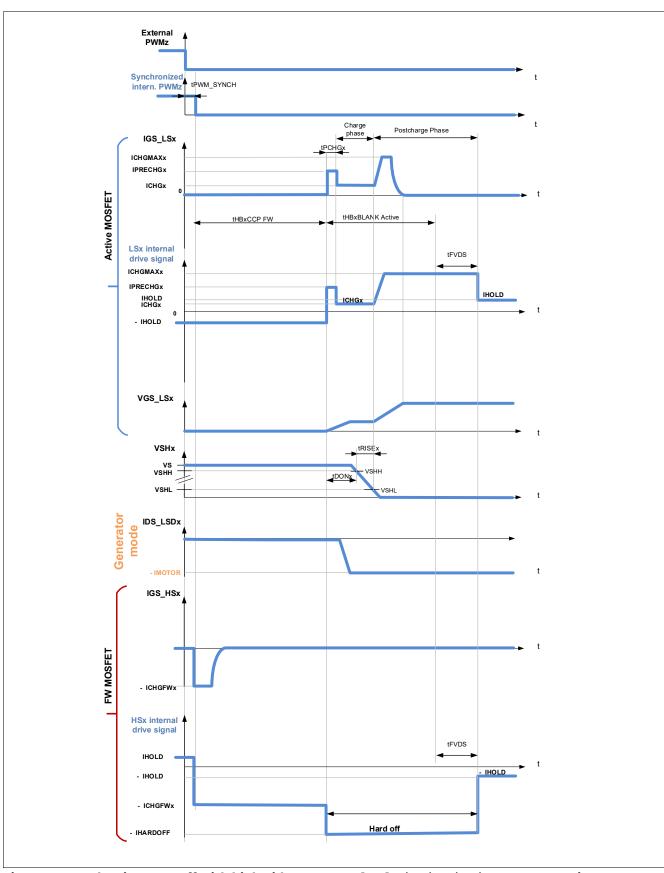

Figure 11, Figure 12 show examples of free-wheeling and active MOSFET when the motor operates as load.

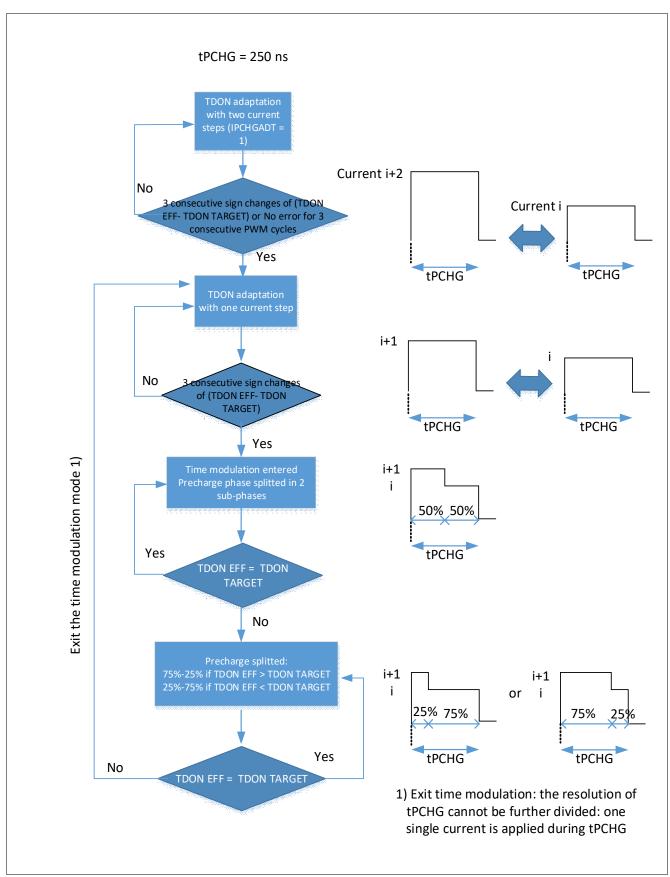

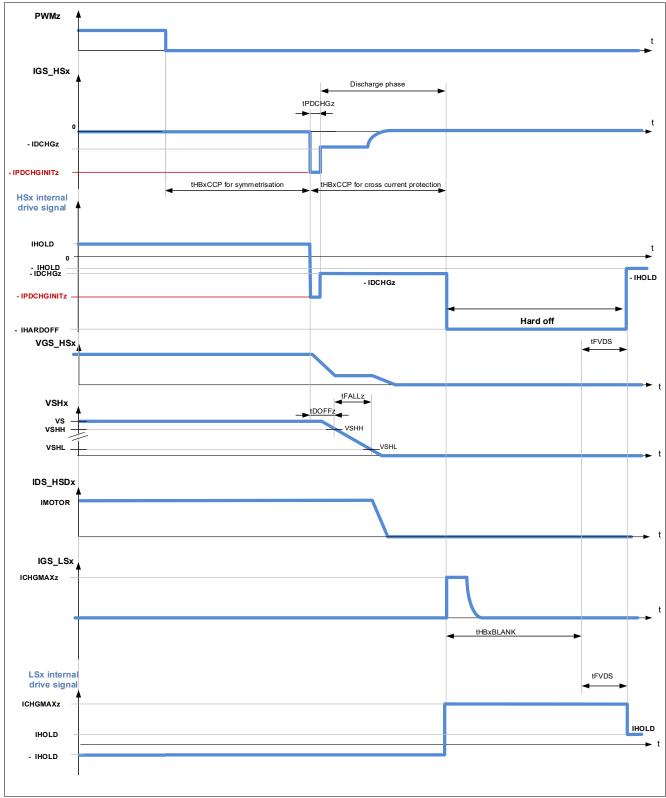

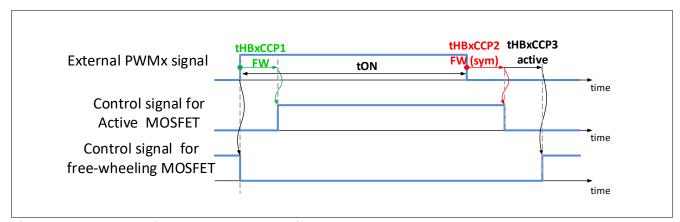

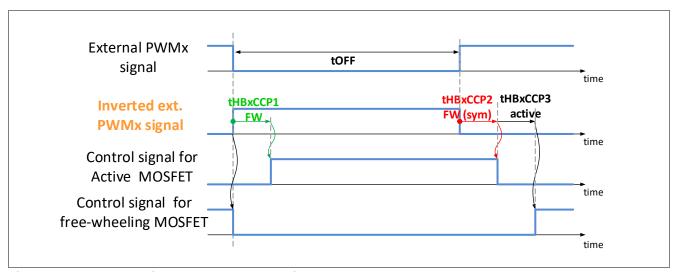

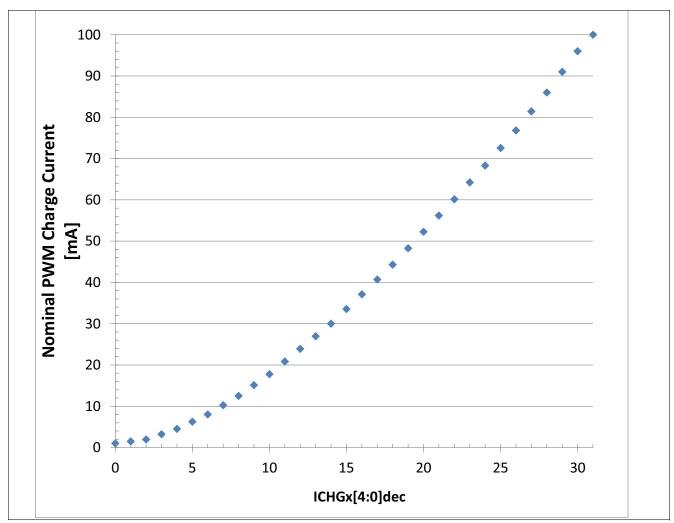

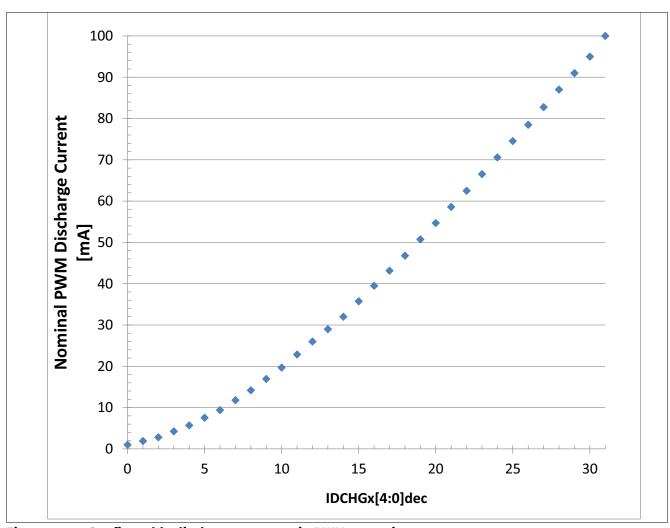

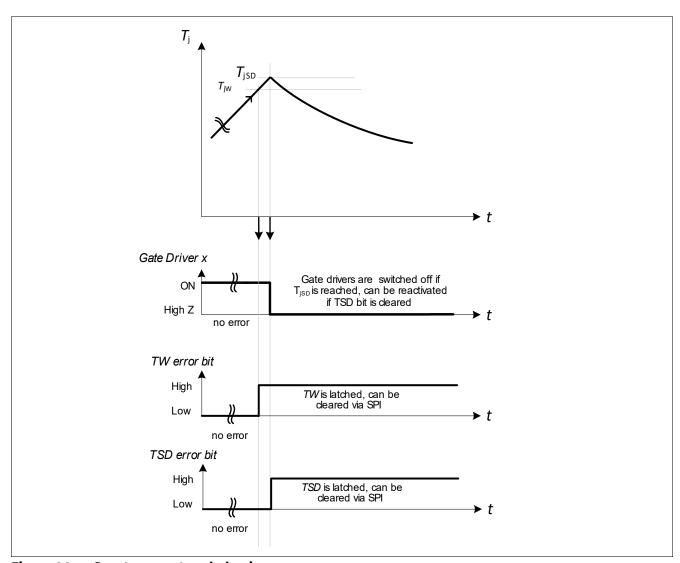

# infineon