# **FMC-CE Hardware User Guide**

UG-FMC-CE (v1.1) August 23, 2010

Xilinx is disclosing this user guide, manual, release note, and/or specification (the "Documentation") to you solely for use in the development of designs to operate with Xilinx hardware devices. You may not reproduce, distribute, republish, download, display, post, or transmit the Documentation in any form or by any means including, but not limited to, electronic, mechanical, photocopying, recording, or otherwise, without the prior written consent of Xilinx. Xilinx expressly disclaims any liability arising out of your use of the Documentation. Xilinx reserves the right, at its sole discretion, to change the Documentation without notice at any time. Xilinx assumes no obligation to correct any errors contained in the Documentation, or to advise you of any corrections or updates. Xilinx expressly disclaims any liability in connection with technical support or assistance that may be provided to you in connection with the Information.

THE DOCUMENTATION IS DISCLOSED TO YOU "AS-IS" WITH NO WARRANTY OF ANY KIND. XILINX MAKES NO OTHER

WARRANTIES, WHETHER EXPRESS, IMPLIED, OR STATUTORY, REGARDING THE DOCUMENTATION, INCLUDING ANY

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NONINFRINGEMENT OF THIRD-PARTY RIGHTS. IN NO EVENT WILL XILINX BE LIABLE FOR ANY CONSEQUENTIAL, INDIRECT, EXEMPLARY, SPECIAL, OR INCIDENTAL DAMAGES, INCLUDING ANY LOSS OF DATA OR LOST PROFITS, ARISING FROM YOUR USE OF THE DOCUMENTATION.

© 2009–2010 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

#### **Revision History**

The following table shows the revision history for this document

| Date    | Version | Revision                                                                         |

|---------|---------|----------------------------------------------------------------------------------|

| 2/26/10 | v0.9.0  | Internal draft                                                                   |

| 3/10/10 | v1.0    | First release                                                                    |

| 8/23/10 | v1.1    | UCFs updated to reflect changes in the FMC-CE board with additional verification |

# **Contents**

| About This Guide                                                        | 1        |

|-------------------------------------------------------------------------|----------|

| FMC-CE Card                                                             | 1        |

| Overview                                                                | 1        |

| Features                                                                | 1        |

| Appendix A: UCF for SP605                                               | 10       |

| Appendix B: UCF for ML605                                               | 13       |

| Appendix C: VITA 57.1 FMC LPC (J63) and HPC (J64) Connector Pinout      | 18       |

| Table of Tables                                                         |          |

|                                                                         | _        |

| Table 1. Slide Switch FMC connections                                   |          |

| Table 3. Button FMC Connections                                         |          |

| Table 4. FMC Connections for LEDs Adjacent to Push Buttons              |          |

| Table 5. Rotary Switch FMC Connections                                  |          |

| Table 6. LCD FMC Connections                                            |          |

| Table 7. Audio FMC Connections                                          |          |

| Table 8. SMA FMC Connections                                            |          |

| Table 9. Leftmost PMOD FMC Connections                                  |          |

| Table 10. Center PMOD FMC Connection                                    |          |

| Table 11. Rightmost PMD FMC Connections                                 | <u>C</u> |

|                                                                         |          |

| Table of Figures                                                        |          |

| Figure 1. FMC-CE Card with Features Annotated                           |          |

| Figure 2. Slide Switch Schematics                                       |          |

| Figure 3. Schematic of LEDs for Both the Linear Array and Rosetta Array |          |

| Figure 4. Schematic for Buttons                                         |          |

| Figure 5. Rotary Switch Schematic                                       | 5        |

| Figure 6 SMA Schematics                                                 | 7        |

#### **About This Guide**

The purpose is of this document is to convey the necessary information to the designer to successfully use the capabilities of the FMC-CE I/O expansion card.

Each feature is independently described and contains a connection table. This table includes the name of the signal, its location on the FMC, the voltage at which it must be programmed by the FPGA, and a brief description of its function. Where the term "any" is provided, the FPGA may provide use voltage as the FPGAs signals are passed directly to the device and not through any level shifter.

#### **FMC-CE Card**

#### **Overview**

The FMC-CE card is meant to be used with a Xilinx demonstration/evaluation board equipped with an FMC connector. This board extends the I/O capabilities of the base platform and provides an I/O consistency among various platforms.

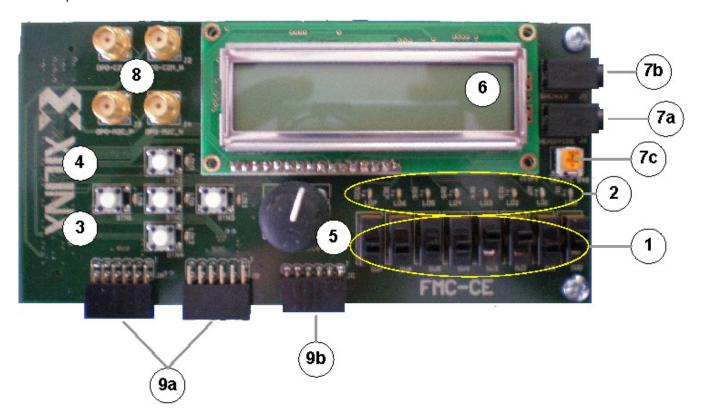

Figure 1. FMC-CE Card with Features Annotated

#### **Features**

The FMC-CE card provides the following features:

- 1) Linear array of 8 slide switches

- 2) Linear array of 8 LEDs co-located with the 8 slide switches

- 3) Rosetta pattern of 5 push button switches

- 4) Rosetta pattern of 5 LEDs, co-located with the push button switches

- 5) A Rotary/push-button switch

- 6) An LCD display (2x16).

- 7) Headphone jack (7a), speaker jack (7b) with a volume control (7c).

- 8) 4 SMA connectors

- 9) 2 Digilent dual PMOD connectors (9a), 1 Digilent single PMOD connector (9b)

#### **Detailed Description**

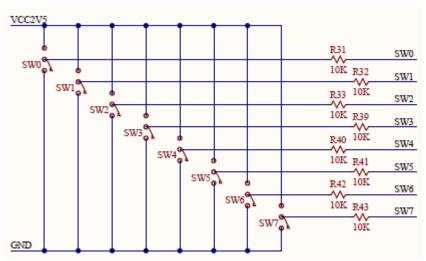

1. 8 Slide switches: One side of each of the eight slide switches is tied to GND, while the other side is pulled up to 2.5V. There is a 10K series resistor for each switch which enables these signals to be used at lower voltages without damaging the FPGA. These switches are silkscreened SW0-SW7. SW0 is on the right most side.

Figure 2. Slide Switch Schematics

| Signal Name | Pin | Voltage | Description |

|-------------|-----|---------|-------------|

| Switch 0    | G33 | ≤2.5V   |             |

| Switch 1    | H32 | ≤2.5V   |             |

| Switch 2    | H31 | ≤2.5V   |             |

| Switch 3    | G31 | ≤2.5V   |             |

| Switch 4    | G30 | ≤2.5V   |             |

| Switch 5    | H29 | ≤2.5V   |             |

| Switch 6    | H28 | ≤2.5V   |             |

| Switch 7    | G28 | ≤2.5V   |             |

**Table 1. Slide Switch FMC connections**

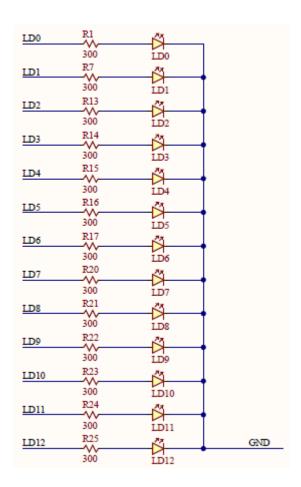

2. There are 8 LED's in a linear fashion, co-located with the slide switches. Each is tied to GND through a 300 Ohm resistor. LD0 is on the right most side. The LEDs illuminate with voltages as low as LVCMOS12.

Figure 3. Schematic of LEDs for Both the Linear Array and Rosetta Array

| Signal Name  | Pin | Voltage | Description                   |

|--------------|-----|---------|-------------------------------|

| LED linear 0 | D27 | any     | Voltage must be sufficient to |

|              |     |         | cross the "on" threshold –    |

|              |     |         | need to verify, as this might |

|              |     |         | be changed from "any" to >=   |

|              |     |         | some voltage.                 |

| LED linear 1 | D26 | any     |                               |

| LED linear 2 | C26 | any     |                               |

| LED linear 3 | D24 | any     |                               |

| LED linear 4 | D23 | any     |                               |

| LED linear 5 | C23 | any     |                               |

| LED linear 6 | C22 | any     |                               |

| LED linear 7 | D21 | any     |                               |

**Table 2. Linear LED Connections**

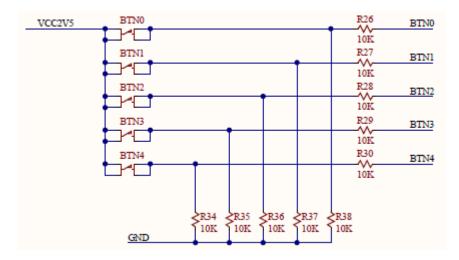

3. The 5 buttons are pulled to GND through a 10K resistor and pulled up to 2.5 V when pressed. When not pressed the button is pulled up to 2.5 V. A series resister (10K Ohms) bleeds off excess voltage if the FPGA is programmed to an IO standard below 2.5 V. These are marked BTN0-4.

**Figure 4. Schematic for Buttons**

| Signal Name | Pin | Voltage | Description                                                                                                                      |

|-------------|-----|---------|----------------------------------------------------------------------------------------------------------------------------------|

| Button 0    | H14 | 2.5V    | Center                                                                                                                           |

|             |     |         | Voltage must be sufficient to cross the "on" threshold – need to verify, as this might be changed from "any" to >= some voltage. |

| Button 1    | G15 | 2.5V    | West                                                                                                                             |

| Button 2    | G18 | 2.5V    | North                                                                                                                            |

| Button 3    | H13 | 2.5V    | East                                                                                                                             |

| Button 4    | G12 | 2.5V    | South                                                                                                                            |

**Table 3. Button FMC Connections**

4. Then there are 5 LED's co-located with the buttons (BTN0-BTN4) in a Rosetta pattern. Each LED is pulled to GND via a 300 Ohm resistor. The schematics are show in (2) Linear LEDs

| Signal Name   | Pin | Voltage | Description                   |

|---------------|-----|---------|-------------------------------|

| LED Rosetta 0 | H16 | any     | Center                        |

|               |     |         |                               |

|               |     |         | Voltage must be sufficient to |

|               |     |         | cross the "on" threshold –    |

|               |     |         | need to verify, as this might |

|               |     |         | be changed from "any" to >=   |

|               |     |         | some voltage.                 |

| Signal Name   | Pin | Voltage | Description |

|---------------|-----|---------|-------------|

| LED Rosetta 1 | G16 | any     | West        |

| LED Rosetta 2 | G19 | any     | North       |

| LED Rosetta 3 | H17 | any     | East        |

| LED Rosetta 4 | G13 | any     | South       |

**Table 4. FMC Connections for LEDs Adjacent to Push Buttons**

5. Rotary Push-button LED linear labeled ROT-1

Figure 5. Rotary Switch Schematic

| Signal Name | Pin | Voltage | Description               |

|-------------|-----|---------|---------------------------|

| Rot-A       | G21 | 2.5V    | Reference waveform        |

| Rot-B       | H19 | 2.5V    | Quadrature waveform       |

| Rot-Switch  | H20 | 2.5V    | Activated by pressing the |

|             |     |         | knob                      |

**Table 5. Rotary Switch FMC Connections**

6. LCD (ST Micro ST7066) display with LVCMOS25 inputs. This dual row 16 character per row uses an industry standard controller (Samsung KS0066U) and sports a 4 or 8 bit data interface. No backlight is provided for the LCD, and the contrast if fixed.

This LCD supports 5x8 and 5x10 dot matrix characters and a programmable 4 or 8 bit MPU interface. Support for custom characters is provided as is a wide range of instruction functions such as clear, cursor home, display on/off, cursor shift, and display shift.

| Signal Name | Pin | Voltage | Description                                                                                                                                                               |

|-------------|-----|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCD Data 0  | G22 | 2.5V    | Four low order bi-directional tristate data bus pins. Used for data transfer and receive between the MPU and the ST7066.  These pins are not used during 4-bit operation. |

| LCD Data 1  | H22 | 2.5V    | As above                                                                                                                                                                  |

| LCD Data 2  | H23 | 2.5V    | As above                                                                                                                                                                  |

| Signal Name | Pin | Voltage | Description                                                                                                               |

|-------------|-----|---------|---------------------------------------------------------------------------------------------------------------------------|

| LCD Data 3  | G24 | 2.5V    | As above                                                                                                                  |

| LCD Data 4  | G25 | 2.5V    | Four high order bi-directional tristate data bus pins. Used for data transfer and receive between the MPU and the ST7066. |

| LCD Data 5  | H25 | 2.5V    | As above                                                                                                                  |

| LCD Data 6  | H26 | 2.5V    | As above                                                                                                                  |

| LCD Data 7  | G27 | 2.5V    | As above. Additionally DB7                                                                                                |

|             |     |         | can be used as a busy flag.                                                                                               |

| LCD - RS    | C19 | 2.5V    | Register Select. 0: Instruction                                                                                           |

|             |     |         | register (for write) and busy                                                                                             |

|             |     |         | flag and address counter for                                                                                              |

|             |     |         | read.                                                                                                                     |

|             |     |         | 1: Data register for read and                                                                                             |

|             |     |         | write                                                                                                                     |

| LCD – R/W   | D20 | 2.5V    | Read (1)/ Write(0) control                                                                                                |

| LCD – E     | C18 | 2.5V    | Enable - Starts data read/write.                                                                                          |

**Table 6. LCD FMC Connections**

7. Both the (a and b) stereo head set jack and a mono speaker jack are controlled via potentiometer volume control (7c). Dual DAC121S101s (12-bit) digital to analog converters (DACs) provide stereo input into a LM4838 2W Stereo Audio Amplifier. Each 12-bit DAC supports a data rate of up to 30MHz and is compatible with SPI, QSPI, NICROWIRE, and DSP interfaces. The effective conversion rate is has a conversion frequency of about 1.75MHz – well above the audio range. Both DAC outputs (right and left channels) are then fed in the Audio Amplifier and are available through a mono speaker connector (left channel only) on J5, and a stereo headphone connector on J6. Both output volumes are controlled via the potentiometer R47, which is clearly labeled on the board.

Key specifications for part DAC121S101 from National Semiconductor:

DNL: +0.25, -0.15 LSB (typ)

Output Settling Time: 8 us (typ)

Zero Code Error: 4mV

Full Scale Error: -0.06%

| Signal Name           | Pin | Voltage | Description               |

|-----------------------|-----|---------|---------------------------|

| Audio DAC clock left  | H37 | 2.5V    | 30MHz max SPI             |

| Audio DAC data left   | G37 | 2.5V    | 16 bit frames             |

| Audio DAC sync left   | H38 | 2.5V    | Marks start of data frame |

| Audio DAC clock right | H35 | 2.5V    | 30MHz max SPI             |

| Audio DAC data right  | H34 | 2.5V    | 16 bit frames             |

| Signal Name          | Pin | Voltage | Description               |

|----------------------|-----|---------|---------------------------|

| Audio DAC sync right | G36 | 2.5V    | Marks start of data frame |

**Table 7. Audio FMC Connections**

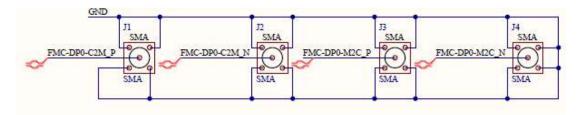

8. There are 4 SMA audio connectors J1 through J4. The silkscreen calls out the positive and negative sides for Rx and Tx, however, these are straight through connections to the FMC, which allows the designer to use them as he/she sees fit.

Figure 6. SMA Schematics

| Signal Name | Pin | Voltage | Description     |

|-------------|-----|---------|-----------------|

| SMA-1       | C2  | any     | J1 – north west |

| SMA-2       | C3  | any     | J2 – north east |

| SMA-3       | C6  | any     | J3 – south west |

| SMA-4       | C7  | any     | J4 – south east |

**Table 8. SMA FMC Connections**

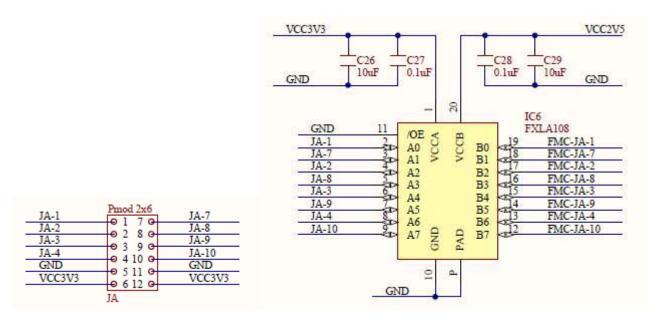

9. PMOD connectors: Two 12 pin "Dual" PMOD connectors are available on JA and JC, and a single 6 pin PMOD is available on JB. These connectors are intended as connection points for Digilent's expansion boards. The voltage, as always, represents the FPGA's input and output voltage. There are voltage translators on the FMC-CE card that translate the PMOD's I/O to 3.3V.

**Figure 7. PMOD Connector and Schematics**

## **Leftmost PMOD connector (dual)**

| Signal Name | Pin | Voltage | Description |

|-------------|-----|---------|-------------|

| PMOD-JA-1   | H11 | 2.5V    | 1/0         |

| PMOD-JA-2   | H10 | 2.5V    | I/O         |

| PMOD-JA-3   | Н8  | 2.5V    | I/O         |

| PMOD-JA-4   | H7  | 2.5V    | I/O         |

| PMOD-JA-5   |     |         | Ground      |

| PMOD-JA-6   |     |         | 3.3V Power  |

| PMOD-JA-7   | G10 | 2.5V    | I/O         |

| PMOD-JA-8   | G9  | 2.5V    | I/O         |

| PMOD-JA-9   | G7  | 2.5V    | I/O         |

| PMOD-JA-10  | G6  | 2.5V    | I/O         |

| PMOD-JA-11  |     |         | Ground      |

| PMOD-JA-12  |     |         | 3.3V Power  |

**Table 9. Leftmost PMOD FMC Connections**

# **Center PMOD connector (dual)**

| Signal Name | Pin | Voltage | Description |

|-------------|-----|---------|-------------|

| PMOD-JB-1   | D14 | 2.5V    | I/O         |

| PMOD-JB-2   | D12 | 2.5V    | 1/0         |

| PMOD-JB-3   | C11 | 2.5V    | 1/0         |

| PMOD-JB-4   | D9  | 2.5V    | 1/0         |

| PMOD-JB-5   |     |         | Ground      |

| PMOD-JB-6   |     |         | 3.3V Power  |

| PMOD-JB-7   | C14 | 2.5V    | I/O         |

| PMOD-JB-8   | D11 | 2.5V    | I/O         |

| PMOD-JB-9   | C10 | 2.5V    | I/O         |

| PMOD-JB-10  | D8  | 2.5V    | I/O         |

| Signal Name | Pin | Voltage | Description |

|-------------|-----|---------|-------------|

| PMOD-JB-11  |     | Gnd     | Ground      |

| PMOD-JB-12  |     |         | 3.3V Power  |

**Table 10. Center PMOD FMC Connection**

# Rightmost PMOD connector (single)

| Signal Name | Pin | Voltage | Description |

|-------------|-----|---------|-------------|

| PMOD-JC-1   | D18 | 2.5V    | I/O         |

| PMOD-JC-2   | D17 | 2.5V    | I/O         |

| PMOD-JC-3   | D15 | 2.5V    | I/O         |

| PMOD-JC-4   | C15 | 2.5V    | I/O         |

| PMOD-JC-5   | 1   |         | Ground      |

| PMOD-JC-6   |     |         | 3.3V Power  |

**Table 11. Rightmost PMD FMC Connections**

### **Appendix A: UCF for SP605**

```

# User Constraint File for FMC-CE card when attached to a Xilinx SP605

#

pin locations only!

# 2/19/2010

#

# Device

# spartan6 xc6slx45t fgg484 SPEED GRADE = -2 ?ES silicon boards?

# spartan6 xc6slx45t fgg484 SPEED_GRADE = -3 ?production silicon boards?

#

# *** peripherals ***

# LCD

NET "LCD_data_pins<0>" LOC = "R8"; # gpio_lcd_db8

NET "LCD_data_pins<1>" LOC = "R11";

NET "LCD_data_pins<2>" LOC = "T11";

NET "LCD_data_pins<3>" LOC = "V7";

NET "LCD_data_pins<4>" LOC = "W8";

NET "LCD_data_pins<5>" LOC = "V11";

NET "LCD_data_pins<6>" LOC = "W11";

NET "LCD data pins<7>" LOC = "W14";

NET "LCD data pins<*>" IOSTANDARD = LVCMOS25 | DRIVE = 4 | SLEW = SLOW;

NET "LCD E pin" LOC = "C17" | PULLDOWN | IOSTANDARD = LVCMOS25;

NET "LCD_RS_pin" LOC = "A17" | IOSTANDARD = LVCMOS25;

NET "LCD RW pin" LOC = "Y11" | IOSTANDARD = LVCMOS25;

# linear LEDs (8)

NET "LED_linear_pins<7>" LOC = "AB11";

NET "LED_linear_pins<6>" LOC = "T12";

NET "LED_linear_pins<5>" LOC = "U12";

NET "LED_linear_pins<4>" LOC = "U9";

NET "LED linear pins<3>" LOC = "V9";

NET "LED linear pins<2>" LOC = "AA10";

NET "LED_linear_pins<1>" LOC = "U14";

NET "LED linear pins<0>" LOC = "U13";

NET "LED linear pins<*>" IOSTANDARD = LVCMOS25 | DRIVE = 4 | SLEW = SLOW;

# rosetta leds (5)

NET "LED rosetta pins<0>" LOC = "H14";

# CONN BUT LED0 - center

NET "LED_rosetta_pins<1>" LOC = "G13";

# CONN_BUT_LED1 - west

NET "LED rosetta pins<2>" LOC = "A5";

# CONN BUT LED2 - north

NET "LED rosetta pins<3>" LOC = "G15";

# CONN BUT LED3 - east

NET "LED rosetta pins<4>" LOC = "A20";

# CONN BUT LED4 - south

NET "LED_rosetta_pins<*>" IOSTANDARD = LVCMOS25# CONN_BUT-all

```

```

# rosetta buttons (5)

NET "button_pins<0>" LOC = "A2";

# CONN BUTO - center

NET "button_pins<1>" LOC = "H13";

# CONN_BUT1 - west

NET "button pins<2>" LOC = "C5";

# CONN BUT2 - north

NET "button_pins<3>" LOC = "B2";

# CONN BUT3 - east

NET "button pins<4>" LOC = "B20";

# CONN BUT4 - south

NET "button_pins<*>" IOSTANDARD = LVCMOS25

# CONN_BUT-all

# slide switches (8)

NET "switch_pins<0>" LOC = "U16";

# CONN_SLDSW0 - rightmost

NET "switch_pins<1>" LOC = "AB16";

# CONN SLDSW1

NET "switch_pins<2>" LOC = "AA16";

# CONN_SLDSW2

NET "switch_pins<3>" LOC = "U15";

# CONN SLDSW3

NET "switch_pins<4>" LOC = "T15";

# CONN_SLDSW4

NET "switch pins<5>" LOC = "AB14";

# CONN SLDSW5

NET "switch_pins<6>" LOC = "AA14";

# CONN_SLDSW6

NET "switch_pins<7>" LOC = "Y14";

# CONN_SLDSW7 - leftmost

NET "switch_pins<*>" IOSTANDARD = LVCMOS25; # CONN_SLDSW-all

# ROTARY ENCODER & SWITCH

NET "ROTARY_ENC_A_pin"

LOC="R9" | IOSTANDARD = LVCMOS25;

NET "ROTARY ENC B pin"

LOC="D18" | IOSTANDARD = LVCMOS25;

NET "ROTARY_ENC_SWITCH_pin"

LOC="D19" | IOSTANDARD = LVCMOS25;

# SPI audio dac left

NET "AUDIO DAC left MOSI pin"

LOC="AB17" | IOSTANDARD = LVCMOS25;

LOC="W17" | IOSTANDARD = LVCMOS25;

NET "AUDIO_DAC_left_SCK_pin"

NET "AUDIO_DAC_left_SS_pin"

LOC="Y18" | IOSTANDARD = LVCMOS25;

# SPI audio dac right

NET "AUDIO DAC right MOSI pin"

LOC="Y15" | IOSTANDARD = LVCMOS25;

NET "AUDIO_DAC_right_SCK_pin"

LOC="AB15" | IOSTANDARD = LVCMOS25;

NET "AUDIO DAC right SS pin"

LOC="Y17" | IOSTANDARD = LVCMOS25;

# Aux I/O 8 bit 2 x 4 connector JA

NET "AUX JA<1>"

LOC="A19";

LOC="C19";

NET "AUX_JA<2>"

NET "AUX_JA<3>"

LOC="F9";

NET "AUX_JA<4>"

LOC="G8";

NET "AUX JA<7>"

LOC="A18";

NET "AUX JA<8>"

LOC="B18";

NET "AUX JA<9>"

LOC="F10";

NET "AUX JA<10>" LOC="G9";

NET "AUX JA<*>" IOSTANDARD = LVCMOS25;

# Aux I/O 8 bit 2 x 4 connector JB

NET "AUX_JB<1>"

LOC="F7";

LOC="A4";

NET "AUX_JB<2>"

NET "AUX_JB<3>"

LOC="D5";

NET "AUX_JB<4>"

LOC="F15";

```

```

NET "AUX_JB<7>" LOC="H10";

NET "AUX_JB<8>" LOC="C4";

NET "AUX_JB<9>" LOC="D4";

NET "AUX_JB<10>" LOC="F14";

NET "AUX_JB<*>" IOSTANDARD = LVCMOS25;

# Aux I/O 4 bit 1 x 4 connector JC

NET "AUX_JC<1>" LOC="F17";

NET "AUX_JC<2>" LOC="G16";

NET "AUX_JC<3>" LOC="F8";

NET "AUX_JC<4>" LOC="H11";

NET "AUX_JC<*>" IOSTANDARD = LVCMOS25;

```

## **Appendix B: UCF for ML605**

As there are two FMC connectors on the board: J63 and J64, there are two possible connections for each signal, depending on which connector the FMC-CE is plugged in to.

When plugged into J63:

```

# User Constraint File for FMC-CE card when attached to a Xilinx ML605 - J63

pin locations only!

# 2/26/2010

# Device

# Virtex6 xc6vlx240t fgg1156 SPEED GRADE = -1

# *** peripherals ***

# LCD

NET "LCD_data_pins<0>" LOC = "R29"; # gpio_lcd_db8

NET "LCD_data_pins<1>" LOC = "M30";

NET "LCD data pins<2>" LOC = "N30";

NET "LCD_data_pins<3>" LOC = "N27";

NET "LCD data pins<4>" LOC = "P27";

NET "LCD_data_pins<5>" LOC = "R26";

NET "LCD_data_pins<6>" LOC = "T26";

NET "LCD_data_pins<7>" LOC = "P31";

NET "LCD_data_pins<*>" IOSTANDARD = LVCMOS25 | DRIVE = 4 | SLEW = SLOW;

NET "LCD_E_pin" LOC = "C33" | PULLDOWN | IOSTANDARD = LVCMOS25;

NET "LCD RS pin" LOC = "B34" | IOSTANDARD = LVCMOS25;

NET "LCD RW pin" LOC = "N28" | IOSTANDARD = LVCMOS25;

# linear LEDs (8)

NET "LED linear pins<7>" LOC = " N29 ";

NET "LED_linear_pins<6>" LOC = " L29 ";

NET "LED_linear_pins<5>" LOC = " L30";

NET "LED_linear_pins<4>" LOC = " R28";

NET "LED_linear_pins<3>" LOC = " R27 ";

NET "LED_linear_pins<2>" LOC = " R31";

NET "LED_linear_pins<1>" LOC = " L33";

NET "LED linear pins<0>" LOC = " M32";

NET "LED linear pins<*>" IOSTANDARD = LVCMOS25 | DRIVE = 4 | SLEW = SLOW;

# rosetta leds (5)

NET "LED rosetta pins<0>" LOC = "D31";

# CONN BUT LED0 - center

NET "LED rosetta pins<1>" LOC = "E33";

# CONN BUT LED1 - west

```

```

NET "LED_rosetta_pins<2>" LOC = "B33";

# CONN_BUT_LED2 - north

NET "LED_rosetta_pins<3>" LOC = "D32";

# CONN BUT LED3 - east

NET "LED_rosetta_pins<4>" LOC = "K29";

# CONN_BUT_LED4 - south

NET "LED rosetta pins<*>" IOSTANDARD = LVCMOS25# CONN BUT-all

# rosetta buttons (5)

NET "button_pins<0>" LOC = "H32";

# CONN_BUTO - center

NET "button pins<1>" LOC = "E32";

# CONN BUT1 - west

NET "button_pins<2>" LOC = "A33";

# CONN BUT2 - north

NET "button_pins<3>" LOC = "G32";

# CONN_BUT3 - east

NET "button_pins<4>" LOC = "J30";

# CONN BUT4 - south

NET "button_pins<*>" IOSTANDARD = LVCMOS25

# CONN_BUT-all

# slide switches (8)

NET "switch pins<0>" LOC = "M31";

# CONN SLDSW0 - rightmost

NET "switch_pins<1>" LOC = "M33";

# CONN_SLDSW1

NET "switch_pins<2>" LOC = "N33";

# CONN_SLDSW2

NET "switch_pins<3>" LOC = "P34";

# CONN_SLDSW3

NET "switch_pins<4>" LOC = "N34";

# CONN_SLDSW4

NET "switch_pins<5>" LOC = "P32";

# CONN SLDSW5

NET "switch_pins<6>" LOC = "N32";

# CONN SLDSW6

NET "switch_pins<7>" LOC = "P30";

# CONN SLDSW7 - leftmost

NET "switch_pins<*>" IOSTANDARD = LVCMOS25; # CONN_SLDSW-all

# ROTARY ENCODER & SWITCH

LOC="P29" | IOSTANDARD = LVCMOS25;

NET "ROTARY ENC A pin"

LOC="C32" | IOSTANDARD = LVCMOS25;

NET "ROTARY_ENC_B_pin"

NET "ROTARY_ENC_SWITCH_pin"

LOC="B32" | IOSTANDARD = LVCMOS25;

# SPI audio dac left

NET "AUDIO DAC left MOSI pin"

LOC="K31" | IOSTANDARD = LVCMOS25;

NET "AUDIO DAC left SCK pin"

LOC="N25" | IOSTANDARD = LVCMOS25;

NET "AUDIO DAC left SS pin" LOC="M25" | IOSTANDARD = LVCMOS25;

# SPI audio dac right

NET "AUDIO DAC right MOSI pin"

LOC="M26" | IOSTANDARD = LVCMOS25;

NET "AUDIO_DAC_right_SCK_pin"

LOC="M27" | IOSTANDARD = LVCMOS25;

NET "AUDIO_DAC_right_SS_pin"

LOC="K32" | IOSTANDARD = LVCMOS25;

# Aux I/O 8 bit 2 x 4 connector JA

NET "AUX JA<1>"

LOC="J29";

NET "AUX JA<2>"

LOC="K28";

NET "AUX JA<3>"

LOC="H30";

NET "AUX JA<4>"

LOC="G31";

NET "AUX_JA<7>"

LOC="J32";

NET "AUX_JA<8>"

LOC="J31";

NET "AUX JA<9>"

LOC="K27";

NET "AUX_JA<10>" LOC="K26";

NET "AUX_JA<*>" IOSTANDARD = LVCMOS25;

```

```

NET "AUX_JB<2>"

LOC="H33";

NET "AUX JB<3>"

LOC="J34";

NET "AUX JB<4>"

LOC="E31";

NET "AUX JB<7>"

LOC="F30";

NET "AUX_JB<8>"

LOC="H34";

NET "AUX JB<9>"

LOC="K33";

NET "AUX_JB<10>" LOC="F31";

NET "AUX_JB<*>" IOSTANDARD = LVCMOS25;

# Aux I/O 4 bit 1 x 4 connector JC

NET "AUX_JC<1>" LOC="C34";

NET "AUX JC<2>"

LOC="D34";

NET "AUX_JC<3>"

LOC="L26";

NET "AUX_JC<4>"

LOC="G30";

NET "AUX_JC<*>" IOSTANDARD = LVCMOS25;

# SMA connector

NET "DIFSIG_1_p" LOC = "D1";

NET "DIFSIG_1_n" LOC = "D2";

NET "DIFSIG_2_p" LOC = "G3";

NET "DIFSIG_2_n" LOC = "G4";

When plugged into J64:

# User Constraint File for FMC-CE card when attached to a Xilinx ML605 - J64

pin locations only!

# 2/26/2010

# Device

# Virtex6 xc6vlx240t fgg1156 SPEED_GRADE = -1

# *** peripherals ***

# LCD

NET "LCD_data_pins<0>" LOC = "AL24";

#gpio_lcd_db8

NET "LCD_data_pins<1>" LOC = "AN25";

NET "LCD_data_pins<2>" LOC = "AN24";

NET "LCD_data_pins<3>" LOC = "AP27";

NET "LCD_data_pins<4>" LOC = "AP26";

```

# Aux I/O 8 bit 2 x 4 connector JB

LOC="L25";

NET "AUX\_JB<1>"

```

NET "LCD_data_pins<5>" LOC = "AN29";

NET "LCD_data_pins<6>" LOC = "AP29";

NET "LCD_data_pins<7>" LOC = "AN28";

NET "LCD_data_pins<*>" IOSTANDARD = LVCMOS25 | DRIVE = 4 | SLEW = SLOW;

NET "LCD_E_pin" LOC = "AN19" | PULLDOWN | IOSTANDARD = LVCMOS25;

NET "LCD_RS_pin" LOC = "AN20" | IOSTANDARD = LVCMOS25;

NET "LCD RW pin" LOC = "AN27" | IOSTANDARD = LVCMOS25;

# linear LEDs (8)

NET "LED_linear_pins<7>" LOC = "AM27";

NET "LED_linear_pins<6>" LOC = "AH25";

NET "LED_linear_pins<5>" LOC = "AJ25";

NET "LED linear pins<4>" LOC = "AL26";

NET "LED_linear_pins<3>" LOC = "AM26";

NET "LED_linear_pins<2>" LOC = "AP30";

NET "LED_linear_pins<1>" LOC = "AM25";

NET "LED_linear_pins<0>" LOC = "AL25";

NET "LED linear pins<*>" IOSTANDARD = LVCMOS25 | DRIVE = 4 | SLEW = SLOW;

# rosetta leds (5)

NET "LED rosetta pins<0>" LOC = "AM22";

# CONN BUT LED0 - center

NET "LED rosetta pins<1>" LOC = "AL21";

# CONN BUT LED1 - west

NET "LED rosetta pins<2>" LOC = "AN23";

# CONN BUT LED2 - north

NET "LED_rosetta_pins<3>" LOC = "AN22";

# CONN_BUT_LED3 - east

NET "LED_rosetta_pins<4>" LOC = "AJ22";

# CONN_BUT_LED4 - south

NET "LED rosetta pins<*>" IOSTANDARD = LVCMOS25# CONN BUT-all

# rosetta buttons (5)

NET "button_pins<0>" LOC = " AJ21"; # CONN_BUT0 - center

NET "button_pins<1>" LOC = " AM21"; # CONN_BUT1 - west

NET "button pins<2>" LOC = " AP22"; # CONN BUT2 - north

NET "button pins<3>" LOC = " AK21"; # CONN BUT3 - east

NET "button pins<4>" LOC = " AK22"; # CONN BUT4 - south

NET "button_pins<*>" IOSTANDARD = LVCMOS25

# CONN_BUT-all

# slide switches (8)

NET "switch pins<0>" LOC = "AL29";

# CONN SLDSW0 - rightmost

NET "switch_pins<1>" LOC = "AJ27";

# CONN_SLDSW1

NET "switch pins<2>" LOC = "AK27";

# CONN SLDSW2

NET "switch pins<3>" LOC = "AK28";

# CONN SLDSW3

NET "switch_pins<4>" LOC = "AL28";

# CONN SLDSW4

NET "switch pins<5>" LOC = "AM30"; # CONN SLDSW5

NET "switch_pins<6>" LOC = "AN30"; # CONN_SLDSW6

NET "switch pins<7>" LOC = "AM28"; # CONN SLDSW7 - leftmost

NET "switch_pins<*>" IOSTANDARD = LVCMOS25; # CONN_SLDSW-all

```

# ROTARY ENCODER & SWITCH

```

NET "ROTARY ENC A pin"

LOC="AK23" | IOSTANDARD = LVCMOS25;

NET "ROTARY ENC B pin"

LOC="AM23" | IOSTANDARD = LVCMOS25;

NET "ROTARY_ENC_SWITCH_pin"

LOC="AL23" | IOSTANDARD = LVCMOS25;

# SPI audio dac left

NET "AUDIO DAC left MOSI pin"

LOC="AH24" | IOSTANDARD = LVCMOS25;

NET "AUDIO_DAC_left_SCK_pin"

LOC="AG25" | IOSTANDARD = LVCMOS25;

NET "AUDIO DAC left SS pin" LOC="AG26" | IOSTANDARD = LVCMOS25;

# SPI audio dac right

NET "AUDIO DAC right MOSI pin"

LOC="AJ24" | IOSTANDARD = LVCMOS25;

LOC="AK24" | IOSTANDARD = LVCMOS25;

NET "AUDIO_DAC_right_SCK_pin"

LOC="AH23" | IOSTANDARD = LVCMOS25;

NET "AUDIO_DAC_right_SS_pin"

# Aux I/O 8 bit 2 x 4 connector JA

NET "AUX_JA<1>"

LOC="AE19";

NET "AUX_JA<2>"

LOC="AF19";

NET "AUX_JA<3>"

LOC="AD20";

NET "AUX_JA<4>"

LOC="AC20";

NET "AUX JA<7>"

LOC="AD19";

NET "AUX JA<8>"

LOC="AC19";

NET "AUX JA<9>"

LOC="AF21";

NET "AUX_JA<10>" LOC="AF20";

NET "AUX JA<*>" IOSTANDARD = LVCMOS25;

# Aux I/O 8 bit 2 x 4 connector JB

NET "AUX_JB<1>"

LOC="AM18";

NET "AUX JB<2>"

LOC="AH22";

NET "AUX JB<3>"

LOC="AG21";

NET "AUX JB<4>"

LOC="AL19";

NET "AUX JB<7>"

LOC="AM20";

NET "AUX JB<8>"

LOC="AG22";

NET "AUX JB<9>"

LOC="AG20";

NET "AUX JB<10>" LOC="AK19";

NET "AUX JB<*>" IOSTANDARD = LVCMOS25;

# Aux I/O 4 bit 1 x 4 connector JC

NET "AUX_JC<1>"

LOC="AN18";

NET "AUX JC<2>"

LOC="AP19";

NET "AUX JC<3>"

LOC="AL18";

NET "AUX JC<4>"

LOC="AL20";

NET "AUX JC<*>" IOSTANDARD = LVCMOS25;

# SMA connector

NET "DIFSIG_1_p" LOC = "AB1";

NET "DIFSIG 1 n" LOC = "AB2";

NET "DIFSIG_2_p" LOC = "AC3";

NET "DIFSIG_2_n" LOC = "AC4";

```

## Appendix C: VITA 57.1 FMC LPC (J63) and HPC (J64) Connector Pinout

```

NET "FMC HPC CLKO M2C N"

LOC = "K23"; ## H5 on J64

NET "FMC HPC CLKO M2C P"

LOC = "K24"; ## H4 on J64

NET "FMC HPC CLK1 M2C N"

LOC = "AP21"; ## G3 on J64

NET "FMC HPC CLK1 M2C P"

LOC = "AP20"; ## G2 on J64

NET "FMC_HPC_CLK2_M2C_IO_N"

LOC = "AC30"; ## 15 on U83

NET "FMC HPC CLK2 M2C IO P"

LOC = "AD30"; ## 16 on U83

NET "FMC HPC CLK2 M2C MGT C N"

LOC = "AB5"; ## 2 on series C399 0.1uF

NET "FMC HPC CLK2 M2C MGT C P"

LOC = "AB6"; ## 2 on series C398 0.1uF

NET "FMC HPC CLK3 M2C IO N"

LOC = "AF34"; ## J3 on J64

NET "FMC_HPC_CLK3_M2C_IO_P"

LOC = "AE34"; ## J2 on J64

NET "FMC HPC CLK3 M2C MGT C N"

LOC = "AH5"; ## 2 on series C397 0.1uF

LOC = "AH6"; ## 2 on series C396 0.1uF

NET "FMC_HPC_CLK3_M2C_MGT_C_P"

NET "FMC HPC DP0 C2M N"

LOC = "AB2"; ## C3 on J64

NET "FMC HPC DP0 C2M P"

LOC = "AB1"; ## C2 on J64

NET "FMC HPC DP0 M2C N"

LOC = "AC4"; ## C7 on J64

NET "FMC HPC DP0 M2C P"

LOC = "AC3"; ## C6 on J64

NET "FMC HPC DP1 C2M N"

LOC = "AD2"; ## A23 on J64

NET "FMC HPC DP1 C2M P"

LOC = "AD1"; ## A22 on J64

NET "FMC HPC DP1 M2C N"

LOC = "AE4"; ## A3 on J64

NET "FMC HPC DP1 M2C P"

LOC = "AE3"; ## A2 on J64

NET "FMC_HPC_DP2_C2M_N"

LOC = "AF2"; ## A27 on J64

NET "FMC HPC DP2 C2M P"

LOC = "AF1"; ## A26 on J64

NET "FMC HPC DP2 M2C N"

LOC = "AF6"; ## A7 on J64

NET "FMC HPC DP2 M2C P"

LOC = "AF5"; ## A6 on J64

NET "FMC HPC DP3 C2M N"

LOC = "AH2"; ## A31 on J64

NET "FMC HPC DP3 C2M P"

LOC = "AH1"; ## A30 on J64

NET "FMC_HPC_DP3_M2C_N"

LOC = "AG4"; ## A11 on J64

NET "FMC HPC DP3 M2C P"

LOC = "AG3"; ## A10 on J64

NET "FMC HPC DP4 C2M N"

LOC = "AK2"; ## A35 on J64

NET "FMC HPC DP4 C2M P"

LOC = "AK1"; ## A34 on J64

NET "FMC_HPC_DP4_M2C_N"

LOC = "AJ4"; ## A15 on J64

NET "FMC_HPC_DP4_M2C_P"

LOC = "AJ3"; ## A14 on J64

NET "FMC HPC DP5 C2M N"

LOC = "AM2"; ## A39 on J64

NET "FMC HPC DP5 C2M P"

LOC = "AM1"; ## A38 on J64

NET "FMC HPC DP5 M2C N"

LOC = "AL4"; ## A19 on J64

NET "FMC_HPC_DP5_M2C_P"

LOC = "AL3"; ## A18 on J64

NET "FMC_HPC_DP6_C2M_N"

LOC = "AN4"; ## B37 on J64

NET "FMC HPC DP6 C2M P"

LOC = "AN3"; ## B36 on J64

NET "FMC HPC DP6 M2C N"

LOC = "AM6"; ## B17 on J64

NET "FMC HPC DP6 M2C P"

LOC = "AM5"; ## B16 on J64

LOC = "AP2"; ## B33 on J64

NET "FMC_HPC_DP7_C2M_N"

NET "FMC HPC DP7 C2M P"

LOC = "AP1"; ## B32 on J64

```

NET "FMC\_HPC\_DP7\_M2C\_N" LOC = "AP6"; ## B13 on J64 NET "FMC HPC DP7 M2C P" LOC = "AP5"; ## B12 on J64 LOC = "AD5"; ## D5 on J64 NET "FMC HPC GBTCLKO M2C N" NET "FMC HPC GBTCLKO M2C P" LOC = "AD6"; ## D4 on J64 NET "FMC HPC GBTCLK1 M2C N" LOC = "AK5"; ## B21 on J64 NET "FMC HPC GBTCLK1 M2C P" LOC = "AK6"; ## B20 on J64 NET "FMC HPC HA00 CC N" LOC = "AF33"; ## F5 on J64 NET "FMC HPC HA00 CC P" LOC = "AE33"; ## F4 on J64 LOC = "AC29"; ## E3 on J64 NET "FMC HPC HA01 CC N" LOC = "AD29"; ## E2 on J64 NET "FMC HPC HA01 CC P" NET "FMC HPC HA02 N" LOC = "AC25"; ## K8 on J64 NET "FMC HPC HA02 P" LOC = "AB25"; ## K7 on J64 NET "FMC\_HPC\_HA03\_N" LOC = "Y26"; ## J7 on J64 NET "FMC HPC HA03 P" LOC = "AA25"; ## J6 on J64 NET "FMC HPC HA04 N" LOC = "AC28": ## F8 on J64 LOC = "AB28"; ## F7 on J64 NET "FMC HPC HA04 P" NET "FMC\_HPC\_HA05\_N" LOC = "AC27"; ## E7 on J64 NET "FMC\_HPC\_HA05\_P" LOC = "AB27"; ## E6 on J64 LOC = "AA29"; ## K11 on J64 NET "FMC HPC HA06 N" NET "FMC HPC HA06 P" LOC = "AA28"; ## K10 on J64 LOC = "AB26"; ## J10 on J64 NET "FMC HPC HA07 N" LOC = "AA26"; ## J9 on J64 NET "FMC\_HPC\_HA07\_P" LOC = "AF31"; ## F11 on J64 NET "FMC HPC HA08 N" NET "FMC\_HPC\_HA08 P" LOC = "AG31"; ## F10 on J64 NET "FMC HPC HA09 N" LOC = "AB31"; ## E10 on J64 NET "FMC HPC HA09 P" LOC = "AB30"; ## E9 on J64 NET "FMC\_HPC\_HA10\_N" LOC = "AC34"; ## K14 on J64 NET "FMC HPC HA10 P" LOC = "AD34"; ## K13 on J64 LOC = "AG32"; ## J13 on J64 NET "FMC\_HPC\_HA11\_N" LOC = "AG33": ## J12 on J64 NET "FMC HPC HA11 P" NET "FMC HPC HA12 N" LOC = "AE32"; ## F14 on J64 NET "FMC\_HPC\_HA12\_P" LOC = "AD32"; ## F13 on J64 NET "FMC\_HPC\_HA13\_N" LOC = "AD31"; ## E13 on J64 LOC = "AE31"; ## E12 on J64 NET "FMC HPC HA13 P" LOC = "AA31"; ## J16 on J64 NET "FMC HPC HA14 N" LOC = "AA30"; ## J15 on J64 NET "FMC HPC HA14 P" LOC = "AC32"; ## F17 on J64 NET "FMC HPC HA15 N" NET "FMC\_HPC\_HA15\_P" LOC = "AB32"; ## F16 on J64 LOC = "AB33"; ## E16 on J64 NET "FMC\_HPC\_HA16\_N" NET "FMC\_HPC\_HA16\_P" LOC = "AC33"; ## E15 on J64 NET "FMC HPC HA17 CC N" LOC = "W30"; ## K17 on J64 NET "FMC HPC HA17 CC P" LOC = "V30"; ## K16 on J64 NET "FMC HPC HA18 N" LOC = "T34"; ## J19 on J64 NET "FMC\_HPC\_HA18\_P" LOC = "T33"; ## J18 on J64

NET "FMC HPC HA19 N" LOC = "U32"; ## F20 on J64 NET "FMC HPC HA19 P" LOC = "U33"; ## F19 on J64 NET "FMC HPC HA20 N" LOC = "V33"; ## E19 on J64 NET "FMC HPC HA20 P" LOC = "V32"; ## E18 on J64 NET "FMC HPC HA21 N" LOC = "U30"; ## K20 on J64 NET "FMC HPC HA21 P" LOC = "U31"; ## K19 on J64 NET "FMC HPC HA22 N" LOC = "V29"; ## J22 on J64 NET "FMC\_HPC\_HA22\_ P" LOC = "U28"; ## J21 on J64 LOC = "U27"; ## K23 on J64 NET "FMC HPC HA23 N" LOC = "U26"; ## K22 on J64 NET "FMC HPC HA23 P" NET "FMC HPC HB00 CC N" LOC = "AG30"; ## K26 on J64 NET "FMC HPC HB00 CC P" LOC = "AF30"; ## K25 on J64 NET "FMC\_HPC\_HB01\_ N" LOC = "AM32"; ## J25 on J64 NET "FMC HPC HB01 P" LOC = "AN32"; ## J24 on J64 NET "FMC HPC HB02 N" LOC = "AP33"; ## F23 on J64 LOC = "AP32"; ## F22 on J64 NET "FMC HPC HB02 P" NET "FMC\_HPC\_HB03\_N" LOC = "AM31"; ## E22 on J64 NET "FMC HPC HB03 P" LOC = "AL30"; ## E21 on J64 LOC = "AL33"; ## F26 on J64 NET "FMC HPC HB04 N" NET "FMC HPC HB04 P" LOC = "AM33"; ## F25 on J64 LOC = "AN34"; ## E25 on J64 NET "FMC HPC HB05 N" LOC = "AN33"; ## E24 on J64 NET "FMC\_HPC\_HB05\_P" LOC = "AE26"; ## K29 on J64 NET "FMC HPC HB06 CC N" NET "FMC HPC HB06 CC P" LOC = "AF26"; ## K28 on J64 NET "FMC HPC HB07 N" LOC = "AH34"; ## J28 on J64 NET "FMC HPC HB07 P" LOC = "AJ34"; ## J27 on J64 NET "FMC\_HPC\_HB08\_N" LOC = "AK32"; ## F29 on J64 LOC = "AK33"; ## F28 on J64 NET "FMC HPC HB08 P" NET "FMC\_HPC\_HB09\_N" LOC = "AK34"; ## E28 on J64 LOC = "AL34"; ## E27 on J64 NET "FMC HPC HB09 P" NET "FMC HPC HB10 N" LOC = "AF29"; ## K32 on J64 LOC = "AF28"; ## K31 on J64 NET "FMC\_HPC\_HB10\_P" NET "FMC\_HPC\_HB11\_N" LOC = "AJ30"; ## J31 on J64 LOC = "AJ29"; ## J30 on J64 NET "FMC HPC HB11 P" LOC = "AJ32"; ## F32 on J64 NET "FMC HPC HB12 N" LOC = "AJ31"; ## F31 on J64 NET "FMC HPC HB12 P" LOC = "AH32"; ## E31 on J64 NET "FMC HPC HB13 N" NET "FMC\_HPC\_HB13\_P" LOC = "AH33"; ## E30 on J64 LOC = "AD27"; ## K35 on J64 NET "FMC\_HPC\_HB14\_N" NET "FMC\_HPC\_HB14\_P" LOC = "AE27"; ## K34 on J64 NET "FMC HPC HB15 N" LOC = "AE29"; ## J34 on J64 NET "FMC HPC HB15 P" LOC = "AE28"; ## J33 on J64 NET "FMC HPC HB16 N" LOC = "AH30"; ## F35 on J64 NET "FMC\_HPC\_HB16\_P" LOC = "AH29"; ## F34 on J64

NET "FMC\_HPC\_HB17\_CC\_N" LOC = "AG28"; ## K38 on J64 NET "FMC HPC HB17 CC P" LOC = "AG27"; ## K37 on J64 NET "FMC\_HPC\_HB18\_ N" LOC = "AD26"; ## J37 on J64 NET "FMC HPC HB18 P" LOC = "AD25"; ## J36 on J64 NET "FMC HPC HB19 N" LOC = "AK31"; ## E34 on J64 NET "FMC HPC HB19 P" LOC = "AL31"; ## E33 on J64 NET "FMC HPC LA00 CC N" LOC = "AF21"; ## G7 on J64 NET "FMC HPC LA00 CC P" LOC = "AF20"; ## G6 on J64 LOC = "AL19"; ## D9 on J64 NET "FMC HPC LA01 CC N" LOC = "AK19"; ## D8 on J64 NET "FMC HPC LA01 CC P" NET "FMC HPC LA02 N" LOC = "AD20"; ## H8 on J64 NET "FMC HPC LA02 P" LOC = "AC20"; ## H7 on J64 NET "FMC\_HPC\_LA03\_N" LOC = "AD19"; ## G10 on J64 NET "FMC HPC LA03 P" LOC = "AC19"; ## G9 on J64 NET "FMC HPC LA04 N" LOC = "AE19"; ## H11 on J64 NET "FMC HPC LA04 P" LOC = "AF19"; ## H10 on J64 NET "FMC\_HPC\_LA05\_N" LOC = "AH22"; ## D12 on J64 NET "FMC HPC LA05 P" LOC = "AG22"; ## D11 on J64 NET "FMC HPC LA06 N" LOC = "AG21"; ## C11 on J64 NET "FMC HPC LA06 P" LOC = "AG20"; ## C10 on J64 LOC = "AJ21"; ## H14 on J64 NET "FMC HPC LA07 N" LOC = "AK21"; ## H13 on J64 NET "FMC\_HPC\_LA07\_P" LOC = "AJ22"; ## G13 on J64 NET "FMC HPC LA08 N" NET "FMC\_HPC\_LA08 P" LOC = "AK22"; ## G12 on J64 NET "FMC HPC LA09 N" LOC = "AL18"; ## D15 on J64 NET "FMC HPC LA09 P" LOC = "AM18"; ## D14 on J64 NET "FMC\_HPC\_LA10\_N" LOC = "AL20"; ## C15 on J64 NET "FMC HPC LA10 P" LOC = "AM20"; ## C14 on J64 LOC = "AN22"; ## H17 on J64 NET "FMC\_HPC\_LA11\_N" LOC = "AM22"; ## H16 on J64 NET "FMC HPC LA11 P" NET "FMC HPC LA12 N" LOC = "AL21"; ## G16 on J64 NET "FMC\_HPC\_LA12\_P" LOC = "AM21"; ## G15 on J64 NET "FMC\_HPC\_LA13\_N" LOC = "AN18"; ## D18 on J64 LOC = "AP19"; ## D17 on J64 NET "FMC HPC LA13 P" LOC = "AN20"; ## C19 on J64 NET "FMC HPC LA14 N" NET "FMC HPC LA14 P" LOC = "AN19"; ## C18 on J64 LOC = "AL23"; ## H20 on J64 NET "FMC HPC LA15 N" NET "FMC\_HPC\_LA15\_P" LOC = "AM23"; ## H19 on J64 LOC = "AN23"; ## G19 on J64 NET "FMC\_HPC\_LA16\_N" NET "FMC\_HPC\_LA16\_P" LOC = "AP22"; ## G18 on J64 NET "FMC HPC LA17 CC N" LOC = "AM27"; ## D21 on J64 NET "FMC\_HPC\_LA17\_CC\_P" LOC = "AN27"; ## D20 on J64 NET "FMC HPC LA18 CC N" LOC = "AJ25"; ## C23 on J64 NET "FMC\_HPC\_LA18\_CC\_P" LOC = "AH25"; ## C22 on J64

| NET "FMC_HPC_LA19_N"                       | LOC = "AN24"; ## H23 on J64 |

|--------------------------------------------|-----------------------------|

| NET "FMC_HPC_LA19_P"                       | LOC = "AN25"; ## H22 on J64 |

| NET "FMC_HPC_LA20_N"                       | LOC = "AL24"; ## G22 on J64 |

| NET "FMC_HPC_LA20_P"                       | LOC = "AK23"; ## G21 on J64 |

| NET "FMC_HPC_LA21_N"                       | LOC = "AP29"; ## H26 on J64 |

| NET "FMC_HPC_LA21_P"                       | LOC = "AN29"; ## H25 on J64 |

| NET "FMC_HPC_LA22_N"                       | LOC = "AP26"; ## G25 on J64 |

| NET "FMC_HPC_LA22_P"                       | LOC = "AP27"; ## G24 on J64 |

| NET "FMC_HPC_LA23_N"                       | LOC = "AM26"; ## D24 on J64 |

| NET "FMC_HPC_LA23_P"                       | LOC = "AL26"; ## D23 on J64 |

| NET "FMC_HPC_LA24_N"                       | LOC = "AM30"; ## H29 on J64 |

| NET "FMC_HPC_LA24_P"                       | LOC = "AN30"; ## H28 on J64 |

| NET "FMC_HPC_LA25_N"                       | LOC = "AM28"; ## G28 on J64 |

| NET "FMC_HPC_LA25_P"                       | LOC = "AN28"; ## G27 on J64 |

| NET "FMC_HPC_LA26_N"                       | LOC = "AL25"; ## D27 on J64 |

| NET "FMC_HPC_LA26_P"                       | LOC = "AM25"; ## D26 on J64 |

| NET "FMC_HPC_LA27_N"                       | LOC = "AP31"; ## C27 on J64 |

| NET "FMC_HPC_LA27_P"                       | LOC = "AP30"; ## C26 on J64 |

| NET "FMC_HPC_LA28_N"                       | LOC = "AJ27"; ## H32 on J64 |

| NET "FMC_HPC_LA28_P"                       | LOC = "AK27"; ## H31 on J64 |

| NET "FMC_HPC_LA29_N"                       | LOC = "AK28"; ## G31 on J64 |

| NET "FMC_HPC_LA29_P"                       | LOC = "AL28"; ## G30 on J64 |

| NET "FMC_HPC_LA30_N"                       | LOC = "AK24"; ## H35 on J64 |

| NET "FMC_HPC_LA30_P"                       | LOC = "AJ24"; ## H34 on J64 |

| NET "FMC_HPC_LA31_N"                       | LOC = "AK29"; ## G34 on J64 |

| NET "FMC HPC LA31 P"                       | LOC = "AL29"; ## G33 on J64 |

| NET "FMC_HPC_LAS1_P"  NET "FMC HPC LA32 N" | LOC = "AG26"; ## H38 on J64 |

|                                            | LOC = "AG25"; ## H37 on J64 |

| NET "FMC_HPC_LA32_P"  NET "FMC_HPC_LA33_N" | •                           |

|                                            | LOC = "AH24"; ## G37 on J64 |

| NET "FMC_HPC_LA33_P"                       | LOC = "AH23"; ## G36 on J64 |

| NET "FMC_HPC_PG_M2C_LS"                    | LOC = "J27"; ## F1 on J64   |

| NET "FMC_HPC_PRSNT_M2C_L"                  | LOC = "AP25"; ## H2 on J64  |

|                                            |                             |

| ##                                         |                             |

| NET "FMC_LPC_CLK0_M2C_N"                   | LOC = "B10"; ## H5 on J63   |

| NET "FMC_LPC_CLK0_M2C_P"                   | LOC = "A10"; ## H4 on J63   |

| NET "FMC_LPC_CLK1_M2C_N"                   | LOC = "G33"; ## G3 on J63   |

| NET "FMC_LPC_CLK1_M2C_P"                   | LOC = "F33"; ## G2 on J63   |

| NET "FMC_LPC_DP0_C2M_N"                    | LOC = "D2"; ## C3 on J63    |

| NET "FMC_LPC_DP0_C2M_P"                    | LOC = "D1"; ## C2 on J63    |

| NET "FMC_LPC_DP0_M2C_N"                    | LOC = "G4"; ## C7 on J63    |

| NET "FMC_LPC_DP0_M2C_P"                    | LOC = "G3"; ## C6 on J63    |

| NET "FMC_LPC_GBTCLK0_M2C_N                 | N" LOC = "M5"; ## D5 on J63 |

| NET "FMC_LPC_GBTCLK0_M2C_F                 | D" LOC = "M6"; ## D4 on J63 |

NET "FMC LPC IIC SCL LS" LOC = "AF13"; ## 2 of Q26 NET "FMC LPC IIC SDA LS" LOC = "AG13"; ## 2 of Q27 NET "FMC LPC LA00 CC N" LOC = "K27"; ## G7 on J63 NET "FMC LPC LA00 CC P" LOC = "K26"; ## G6 on J63 NET "FMC LPC LA01 CC N" LOC = "E31"; ## D9 on J63 NET "FMC LPC LA01 CC P" LOC = "F31"; ## D8 on J63 NET "FMC LPC LA02 N" LOC = "H30"; ## H8 on J63 NET "FMC\_LPC\_LA02\_ P" LOC = "G31"; ## H7 on J63 LOC = "J32"; ## G10 on J63 NET "FMC LPC LA03 N" LOC = "J31"; ## G9 on J63 NET "FMC LPC LA03 P" NET "FMC LPC LA04 N" LOC = "J29"; ## H11 on J63 NET "FMC LPC LA04 P" LOC = "K28"; ## H10 on J63 NET "FMC\_LPC\_LA05\_N" LOC = "H33"; ## D12 on J63 LOC = "H34"; ## D11 on J63 NET "FMC LPC LA05 P" NET "FMC LPC LA06 N" LOC = "J34": ## C11 on J63 NET "FMC LPC LA06 P" LOC = "K33"; ## C10 on J63 NET "FMC\_LPC\_LA07\_N" LOC = "H32"; ## H14 on J63 NET "FMC\_LPC\_LA07\_P" LOC = "G32"; ## H13 on J63 NET "FMC LPC LA08 N" LOC = "K29"; ## G13 on J63 NET "FMC\_LPC\_LA08\_P" LOC = "J30"; ## G12 on J63 NET "FMC LPC LA09 N" LOC = "L26"; ## D15 on J63 LOC = "L25"; ## D14 on J63 NET "FMC\_LPC\_LA09\_P" LOC = "G30"; ## C15 on J63 NET "FMC LPC LA10 N" LOC = "F30"; ## C14 on J63 NET "FMC LPC LA10 P" NET "FMC LPC LA11 N" LOC = "D32"; ## H17 on J63 NET "FMC LPC LA11 P" LOC = "D31"; ## H16 on J63 NET "FMC\_LPC\_LA12\_N" LOC = "E33"; ## G16 on J63 NET "FMC LPC LA12 P" LOC = "E32"; ## G15 on J63 LOC = "C34"; ## D18 on J63 NET "FMC\_LPC\_LA13\_N" LOC = "D34"; ## D17 on J63 NET "FMC LPC LA13 P" NET "FMC LPC LA14 N" LOC = "B34"; ## C19 on J63 NET "FMC\_LPC\_LA14\_P" LOC = "C33"; ## C18 on J63 LOC = "B32"; ## H20 on J63 NET "FMC\_LPC\_LA15\_N" LOC = "C32"; ## H19 on J63 NET "FMC LPC LA15 P" NET "FMC\_LPC\_LA16\_N" LOC = "B33"; ## G19 on J63 NET "FMC LPC LA16 P" LOC = "A33"; ## G18 on J63 LOC = "N29"; ## D21 on J63 NET "FMC LPC LA17 CC N" NET "FMC\_LPC\_LA17\_CC\_P" LOC = "N28"; ## D20 on J63 NET "FMC\_LPC\_LA18\_CC\_N" LOC = "L30"; ## C23 on J63 NET "FMC\_LPC\_LA18\_CC\_P" LOC = "L29"; ## C22 on J63 NET "FMC LPC LA19 N" LOC = "N30"; ## H23 on J63 NET "FMC LPC LA19 P" LOC = "M30"; ## H22 on J63 NET "FMC LPC LA20 N" LOC = "R29"; ## G22 on J63 NET "FMC\_LPC\_LA20\_P" LOC = "P29"; ## G21 on J63

```

NET "FMC_LPC_LA21_N"

LOC = "T26"; ## H26 on J63

NET "FMC LPC LA21 P"

LOC = "R26"; ## H25 on J63

NET "FMC_LPC_LA22_N"

LOC = "P27"; ## G25 on J63

NET "FMC LPC LA22 P"

LOC = "N27"; ## G24 on J63

NET "FMC_LPC_LA23_N"

LOC = "R27"; ## D24 on J63

LOC = "R28"; ## D23 on J63

NET "FMC LPC LA23 P"

LOC = "P32"; ## H29 on J63

NET "FMC LPC LA24 N"

NET "FMC_LPC_LA24_P"

LOC = "N32"; ## H28 on J63

NET "FMC LPC LA25 N"

LOC = "P30"; ## G28 on J63

NET "FMC LPC LA25 P"

LOC = "P31"; ## G27 on J63

NET "FMC LPC LA26 N"

LOC = "M32"; ## D27 on J63

NET "FMC LPC LA26 P"

LOC = "L33"; ## D26 on J63

NET "FMC_LPC_LA27_N"

LOC = "R32"; ## C27 on J63

NET "FMC LPC LA27 P"

LOC = "R31"; ## C26 on J63

LOC = "M33"; ## H32 on J63

NET "FMC LPC LA28 N"

LOC = "N33"; ## H31 on J63

NET "FMC LPC LA28 P"

NET "FMC_LPC_LA29_N"

LOC = "P34"; ## G31 on J63

LOC = "N34"; ## G30 on J63

NET "FMC_LPC_LA29_P"

NET "FMC LPC LA30 N"

LOC = "M27"; ## H35 on J63

NET "FMC_LPC_LA30_P"

LOC = "M26"; ## H34 on J63

LOC = "L31"; ## G34 on J63

NET "FMC LPC LA31 N"

LOC = "M31"; ## G33 on J63

NET "FMC_LPC_LA31_P"

LOC = "M25"; ## H38 on J63

NET "FMC_LPC_LA32_N"

NET "FMC LPC LA32 P"

LOC = "N25"; ## H37 on J63

NET "FMC LPC LA33 N"

LOC = "K31"; ## G37 on J63

NET "FMC LPC LA33 P"

LOC = "K32"; ## G36 on J63

NET "FMC_LPC_PRSNT_M2C_L"

LOC = "AD9"; ## H2 on J63

```