# L99LD02

# Automotive dual-phase boost DC/DC controller

# Features

- AEC-Q100 qualified

- General

- 32-bit ST SPI communication v 4.1

- Stand-alone operation supported

- QFN32L 5x5 with exposed pad

- Timeout watchdog and Limp Home function

- Boost section

- Wide input range: 3V to 28V operation

- Device supply option from boost output

- Adjustable boost output voltage up to 80V

- 10V Gate Driver supply for Standard-Level **MOSFETs**

- Internal 10V LDO regulator

- Fixed frequency architecture programmable by SPI

- Dither oscillator parameters as frequency modulation and deviation percentage programmable by SPI

- Peak current mode control with programmable Input Current Limitation

- Constant voltage regulation

- Adjustable Slope Compensation

- Soft start

- Multi-phase operation up to 4-phase supported

- SYNC I/O pin for multi-phase operation support

- Adjustable clock distribution and phase shift

# Datasheet - production data

- Programmable error amplifier gain

- Fully configurable in Limp Home

- Protection and diagnostic

- Boost functionality guaranteed in Cold Cranking

- Input overcurrent protection programmable by SPI

- Thermal warning

- Thermal shutdown

- Overvoltage protection (OVP)

# **Applications**

LED module applications.

# Description

The L99LD02 is a two-phase, constant frequency, current mode boost controller able to drive Nchannel power MOSFETs.

Multi-phase operation is supported by SYNC I/O pin, providing the phase shifted clock signal. The boost controllers of more devices can be stacked, in order to operate in multi-phase for high power applications. Multi-phase operation reduces system filtering capacitance and inductance requirements.

The operating frequency is configurable via SPI between 100kHz and 470kHz. Other features include an internal 10V LDO for the gate drivers, soft-start, device supply option from boost output and pre-configurable operation in Limp Home.

# Contents

| 1 | Intro | troduction |                                     |  |

|---|-------|------------|-------------------------------------|--|

|   | 1.1   | Typical    | application                         |  |

| 2 | Supp  | oly conc   | ept                                 |  |

| 3 | Boos  | st contro  | oller                               |  |

|   | 3.1   | Genera     | I description                       |  |

|   | 3.2   | Switchi    | ng frequency                        |  |

|   | 3.3   | Output     | voltage                             |  |

|   | 3.4   | Overvo     | Itage protection                    |  |

|   | 3.5   | Output     | failure protection                  |  |

|   | 3.6   | Soft sta   | rt                                  |  |

|   | 3.7   | Stability  | v – Error Amplifier characteristics |  |

|   | 3.8   | Operati    | on in multiphase interleaved mode   |  |

| 4 | Fund  | ctional d  | escription                          |  |

|   | 4.1   | Operati    | ng modes                            |  |

|   |       | 4.1.1      | Standby mode                        |  |

|   |       | 4.1.2      | Pre-standby mode                    |  |

|   |       | 4.1.3      | Reset mode                          |  |

|   |       | 4.1.4      | Limp Home / Stand-alone mode        |  |

|   |       | 4.1.5      | Active mode                         |  |

|   | 4.2   | Protecti   | ons and diagnostic                  |  |

|   |       | 4.2.1      | Temperature warning                 |  |

|   |       | 4.2.2      | Overcurrent                         |  |

|   |       | 4.2.3      | Over-temperature shutdown           |  |

|   |       | 4.2.4      | VS under voltage lockout            |  |

| 5 | Seria | al periph  | eral interface (ST SPI standard) 28 |  |

|   | 5.1   | Physica    | al layer - Functional description   |  |

|   | 5.2   | Physica    | al layer – protocol                 |  |

|   |       | 5.2.1      | SDI frame                           |  |

|   |       | 5.2.2      | SDO Frame                           |  |

|   |       |            |                                     |  |

| 9 | Order  | codes     |                                                      | 63 |

|---|--------|-----------|------------------------------------------------------|----|

|   |        | -         | _ 5x5 package information 6                          |    |

| 8 | Packa  | ge infoi  | rmation                                              | 61 |

|   |        | •         | _ 5x5 thermal data 6                                 |    |

| 7 | Packa  | ge and    | PCB thermal data 6                                   | 50 |

|   |        | 6.4.4     | SPI bus (CSN, SCK, SDI, SDO)                         | 58 |

|   |        | 6.4.3     | System Oscillator and Digital Timings                | 58 |

|   |        | 6.4.2     | Boost controller                                     | 53 |

|   |        | 6.4.1     | Supply                                               | 52 |

|   | 6.4    | Electrica | l characteristics                                    | 52 |

|   | 6.3    | Thermal   | data                                                 | 51 |

|   | 6.2    | ESD pro   | tection                                              | 51 |

|   | 6.1    | Absolute  | e maximum ratings                                    | 50 |

| 6 | Electr | ical spe  | cifications                                          | 50 |

|   |        | 5.7.4     | Customer test and trimming procedure description     | 48 |

|   |        |           | Customer trimming registers                          |    |

|   |        | 5.7.2     | Status Register description                          | 44 |

|   |        | 5.7.1     | Control Register                                     | 36 |

|   | 5.7    | Register  | description                                          | 36 |

|   | 5.6    | Timings   |                                                      | 36 |

|   |        | 5.5.2     | GSB and payload inconsistency                        | 36 |

|   |        | 5.5.1     | Register change during communication                 | 36 |

|   | 5.5    | Impleme   | ntation remarks                                      | 36 |

|   |        | 5.4.5     | Data stuck                                           | 35 |

|   |        |           | CSN timeout                                          |    |

|   |        |           | SCK phase (CPHA) check                               |    |

|   |        |           | SCK polarity (CPOL) check                            |    |

|   | -      |           | Clock monitor                                        |    |

|   |        |           | failure detection                                    |    |

|   |        |           | Device application registers                         |    |

|   |        |           | and data definition 3<br>Device Information Register |    |

|   |        |           |                                                      |    |

| Appendix A    | Glossary | 64 |

|---------------|----------|----|

| Revision hist | ory      | 65 |

# List of tables

| Table 1.  | Pin functionality                                   |    |

|-----------|-----------------------------------------------------|----|

| Table 2.  | Switching frequency configuration                   | 13 |

| Table 3.  | OTA gain configuration                              | 16 |

| Table 4.  | Clock distribution – MASTER (internal clock source) | 18 |

| Table 5.  | Clock distribution – SLAVE (external clock source)  | 18 |

| Table 6.  | Clock distribution - MASTER (internal clock source) | 20 |

| Table 7.  | Operating modes                                     | 22 |

| Table 8.  | Boost threshold for input current limitation        | 26 |

| Table 9.  | Command byte (8 bit)                                | 29 |

| Table 10. | Data byte 2                                         | 29 |

| Table 11. | Data byte 1                                         | 30 |

| Table 12. | Data byte 0                                         | 30 |

| Table 13. | Operation code definition                           | 30 |

| Table 14. | Global Status Byte                                  | 31 |

| Table 15. | Data byte2                                          | 31 |

| Table 16. | Data byte1                                          | 31 |

| Table 17. | Data byte0                                          | 31 |

| Table 18. | Global Status Byte                                  | 31 |

| Table 19. | Device information read access operating code       | 32 |

| Table 20. | RAM Memory Map                                      | 32 |

| Table 21. | ROM Memory Map                                      | 33 |

| Table 22. | CR#1: Control Register 1                            | 37 |

| Table 23. | CR#2: Control Register 2                            |    |

| Table 24. | CR#3: Control Register 3                            |    |

| Table 25. | CR#4: Control Register 4                            |    |

| Table 26. | SR#1: Status Register 1                             | 44 |

| Table 27. | CT: Ctm Trimming Register 1                         |    |

| Table 28. | CT: Ctm Trimming Register 2                         |    |

| Table 29. | Writing test conditions.                            |    |

| Table 30. | Absolute maximum ratings                            |    |

| Table 31. | ESD protection                                      | 51 |

| Table 32. | QFN 32L (5x5) thermal resistance                    |    |

| Table 33. | Thermal characteristics.                            |    |

| Table 34. | Supply                                              | 52 |

| Table 35. | Boost gate driver.                                  | 53 |

| Table 36. | Boost controller                                    |    |

| Table 37. | Boost controller reference voltage                  | 57 |

| Table 38. | Digital timings description                         |    |

| Table 39. | CŠN, SCK, SDI input                                 |    |

| Table 40. | SDO output                                          |    |

| Table 41. | SPI timing                                          |    |

| Table 42. | PCB proprieties.                                    |    |

| Table 43. | QFN-32L 5x5 package information                     |    |

| Table 44. | Device summary                                      |    |

| Table 45. | Glossary                                            |    |

| Table 46. | Document revision history                           |    |

# List of figures

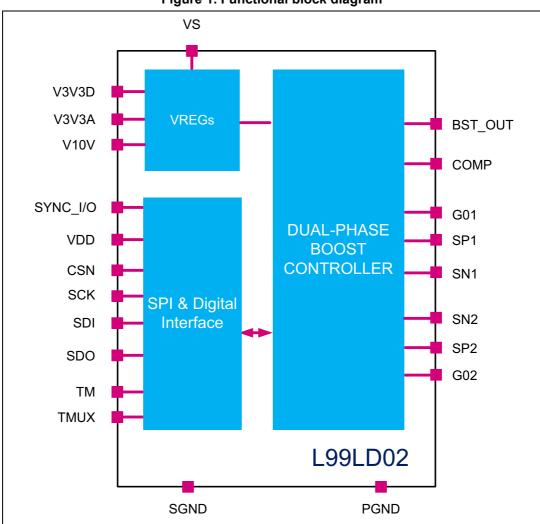

| Figure 1.  | Functional block diagram                                            | . 8 |

|------------|---------------------------------------------------------------------|-----|

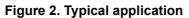

| Figure 2.  | Typical application                                                 | . 9 |

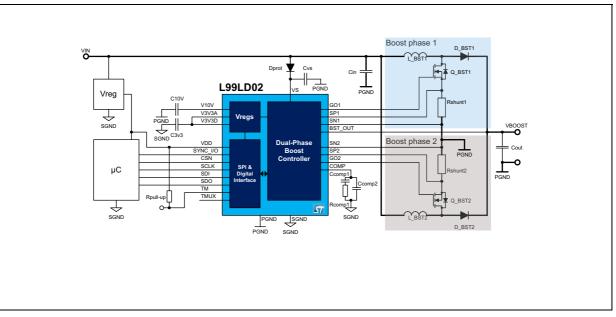

| Figure 3.  | QFN-32L connection diagram.                                         | . 9 |

| Figure 4.  | Resistor ladder for slope compensation and input current limitation | 15  |

| Figure 5.  | 1 or 2 phase configuration with single L99LD02 device               | 17  |

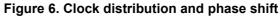

| Figure 6.  | Clock distribution and phase shift                                  | 17  |

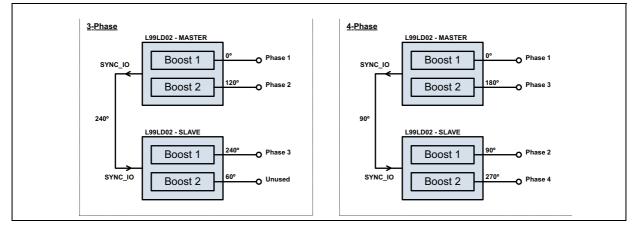

| Figure 7.  | Clock distribution scheme for 3 and 4 phase boost                   | 18  |

| Figure 8.  | 3 or 4 phase configuration with two L99LD02 devices                 | 19  |

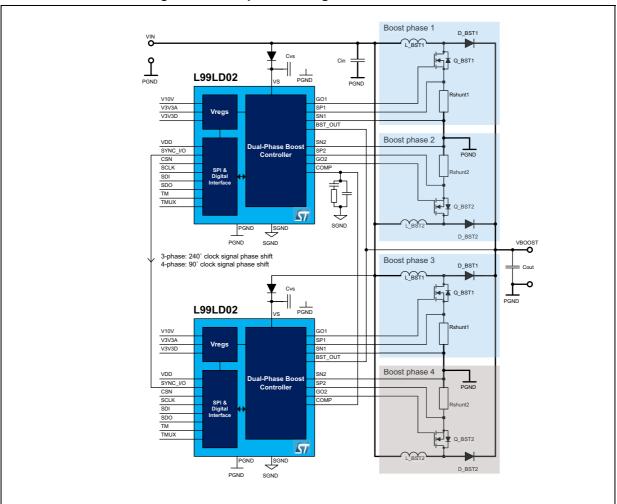

| Figure 9.  | Device state diagram                                                | 21  |

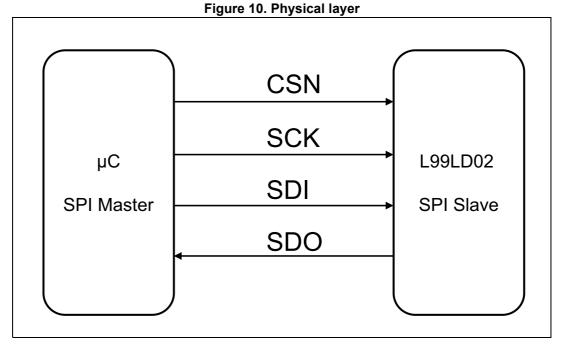

| Figure 10. | Physical layer                                                      | 28  |

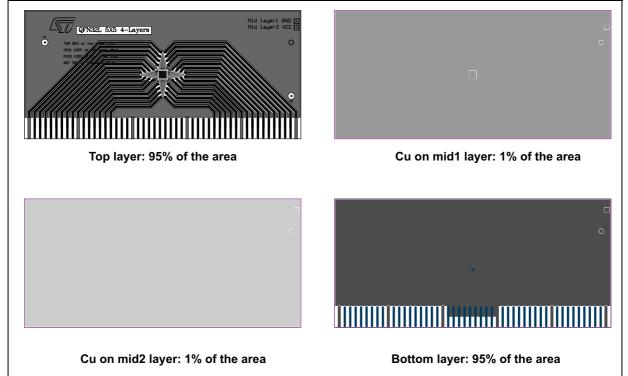

| Figure 11. | QFN-32L 5x5 on four-layers PCB.                                     | 60  |

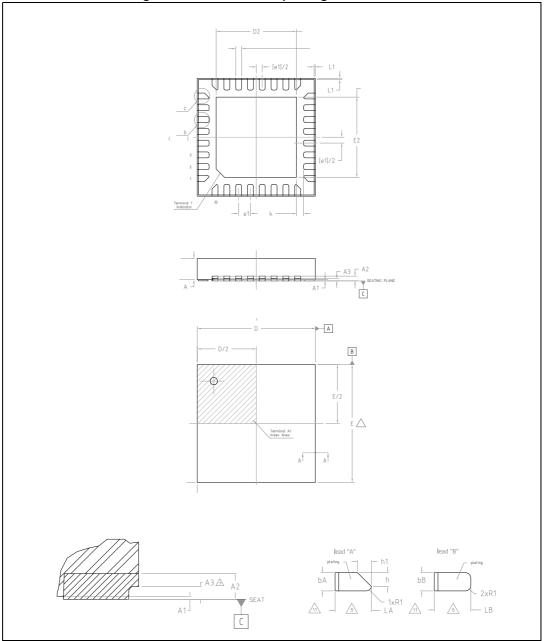

| Figure 12. | QFN-32L 5x5 package dimensions                                      | 61  |

# 1 Introduction

The L99LD02 is a dual-phase, constant frequency, current mode boost controller that drives N-channel power MOSFETs providing a regulated voltage on BST\_OUT pin.

The boost controllers of more devices can be stacked, in order to operate in multi-phase for high power applications. Multi-phase operation is supported by SYNC I/O pin, providing the phase shifted clock signal. Special care has been taken for the current balancing between the different phases and for the switching activity of the boost MOSFETs with proper phase shift.

The device offers a high level of flexibility, without any change of the external components, thanks to its programmability through the ST SPI interface. This feature supports generic platform approaches, which require a software configuration of several parameters. Moreover, this robust interface offers a detailed diagnostic of the device itself.

The L99LD02 features a timeout watchdog, a monitoring of the watchdog counter and a Limp Home function. The device is fully configurable in Limp Home through OTP bits, allowing stand-alone operation.

The L99LD02 integrates a 10 V LDO to supply the gate drivers for standard level MOSFETs and features a supply option from boost output to supply the device when battery level is not enough to guarantee fully Ron external MOSFETs and to fulfill cold cranking requirement.

The input of the boost stage must be connected to the battery voltage through a reverse polarity protection.

The output of the L99LD02 can reach up to 80 V. This allows system designers to drive LED strings up to 60 V.

# 1.1 Typical application

Figure 1. Functional block diagram

Figure 3. QFN-32L connection diagram

DS12448 Rev 3

### Table 1. Pin functionality

| Pin Number | Name                     | Function                                                                                                                                                             |  |

|------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 2          | VS                       | Input supply pin of the IC.<br>Connect to the battery voltage through a Schottky diode.                                                                              |  |

| 3          | ТМ                       | Internal Function. Drive this line from fail safe logic or directly with microcontroller I/O pin.<br>This pin can be used for stand-by mode activation in Limp Home. |  |

| 4          | COMP                     | Output of the error amplifier of the boost controller. Connect the compensation network between this pin and GND.                                                    |  |

| 5,6        | V3V3A, V3V3D<br>(Note 1) | Output of the 3.3 V regulated internal supply (logic supply).<br>Connect a low ESR capacitor (1uF) close to this pin.                                                |  |

| 7          | SGND                     | Signal Ground connection.                                                                                                                                            |  |

| 10         | SYNC_I/O                 | Boost synchronization Input / Output pin.<br>This pin generates the clock signal for synchronizing another L99LD02 in multi-<br>phase configuration.                 |  |

| 11         | CSN                      | Chip Select Not (active low) for SPI communication. It is the selection pin of the device. It is a CMOS compatible input.                                            |  |

| 12         | SDI                      | Serial Data Input for SPI communication. Data is transferred serially into the device on SCLK rising edge.                                                           |  |

| 13         | SCK                      | Serial Clock for SPI communication. It is a CMOS compatible input.                                                                                                   |  |

| 14         | SDO                      | Serial Data Output for SPI communication. Data is transferred serially out of the device on SCLK falling edge.                                                       |  |

| 15         | VDD                      | Connection to external 3.3V or 5V supplies voltage.<br>The external supply powers SPI interface and the I/O signal pins to the<br>microcontroller.                   |  |

| 18         | SP2                      | Positive connection to the boost shunt resistor 2, in series to the boost switching mosfet.                                                                          |  |

| 19         | SN2                      | Negative connection (Ground) to the boost shunt resistor 2, in series to the boost switching mosfet.                                                                 |  |

| 20         | TMUX                     | Internal function. Left open.                                                                                                                                        |  |

| 21         | G02                      | Output of the gate driver 2 for the external the boost switching mosfet.                                                                                             |  |

| 22         | PGND                     | Power Ground connection.                                                                                                                                             |  |

| 23         | G01                      | Output of the gate driver 1 for the external the boost switching mosfet.                                                                                             |  |

| 26         | V10V                     | Output of the 10V regulated internal supply (gate driver supply).<br>Connect low ESR capacitor (1uF typical) close to this pin.                                      |  |

| 27         | SN1                      | Negative connection (Ground) to the boost shunt resistor 1, in series to the boost switching mosfet.                                                                 |  |

| 28         | SP1                      | Positive connection to the boost shunt resistor 1, in series to the boost switching mosfet.                                                                          |  |

| Pin Number                                | Name    | Function                                                 |  |

|-------------------------------------------|---------|----------------------------------------------------------|--|

| 30                                        | BST_OUT | Boost output voltage pin. Optional supply pin of the IC. |  |

| 1, 8, 9, 16,<br>17, 24, 25,<br>29, 31, 32 | NC      | Not Connected                                            |  |

Table 1. Pin functionality (continued)

Note: At application level, V3V3A and V3V3D pins are connected together, then connected to a capacitor.

# 2 Supply concept

The L99LD02 supply range is from 3V up to 28V, which guarantees compatibility with 12V systems. The device is normally supplied from VS pin; when battery level is not enough to guarantee well driven external MOSFETs, the device supply is switched to BST\_OUT pin. The device supply is from:

- VS, in the range of Vs\_sw up to Vsmax;

- BST\_OUT when Vs < Vs\_sw and Bst\_out > Bst\_Out\_min (15V typical).

Vs\_sw is determined from minimum gate driver voltage (7V typical) and voltage drop between Vs and gate driver output. Vsmax is 40V to be compatible with 12V system load dump.

This supply concept guarantees boost functionality during cranking, according to ISO16750-2 and LV124. The L99LD02 output voltage regulation in cranking is ensured according to the following formula:

Bst\_Out = Vin \*  $\eta$  \* 1 / (Toff\_min \* Fsw)

where Vin is the minimum boost input voltage during cold cranking condition (3.2V),  $\eta$  is L99LD02 typical efficiency, Toff\_min is the minimum off time value specified for the full spec range, Fsw is the operative switching frequency of the device.

In cold cranking, boost operation and protection functions are kept. The output power is limited only by adjusted input current limit and converter Toff\_min, whilst, full functionality - without any limitation - is ensured from VS  $\geq$  Vs\_min (minimum operating supply voltage, 5.5V typical).

VS under-voltage shutdown function is implemented to avoid an operation of the external mosfet of the boost controller in linear mode, due to a too low gate driver supply. In case the VS falls below VS under-voltage threshold (Vs\_uv), while device is not supplied from BST\_OUT (BST\_OUT < BST\_OUT\_MIN), the device disables the boost operation. Configuration, operating mode and diagnostic data are kept down to POR.

# 3 Boost controller

## 3.1 General description

The L99LD02 device is able to work both with a microcontroller and without it (stand-alone operation).

The device integrates two boost controllers, based on a fixed frequency, peak current mode architecture. It can drive the gates of up to two external n-channel MOSFETs in order to step up the VS input voltage to a higher stabilized output voltage.

The L99LD02 integrates a 10V LDO to supply the gate drivers for standard level MOSFETs and features a device supply option from boost output.

This features is implemented in order to avoid any operation of the external MOSFETs of the boost controller in linear mode, due to a too low gate driver supply. On top of that, with supply option from boost output, the device fulfills cold cranking requirements.

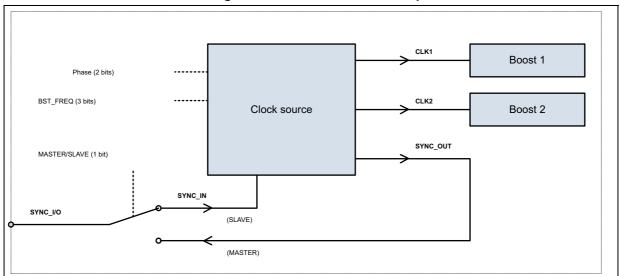

## 3.2 Switching frequency

The L99LD02 operates at a fixed frequency which can range from 100 kHz to 470 kHz. The switching frequency is configurable via SPI (see CR#3 Bit[7:5], BST\_FREQ in *Table 24: CR#3: Control Register 3*) or through dedicated OTPs (for stand-alone configuration).

Boost operative switching frequency value can be set according to *Table 2*:

| BITs [3÷0] | BST_FREQ [kHz] |

|------------|----------------|

| 000        | 101.01         |

| 001        | 151.52         |

| 010        | 196.08         |

| 011        | 256.41         |

| 100        | 303.03         |

| 101        | 333.33         |

| 110        | 416.67         |

| 111        | 476.19         |

Table 2. Switching frequency configuration

The L99LD02 features an internal dither oscillator. Frequency modulation as well as deviation percentage can be programmed through SPI (see CR#3 Bit[11:10] BST\_FDEV, Bit[9:8] BST\_FMOD in *Table 24: CR#3: Control Register 3*).

# 3.3 Output voltage

The boost output voltage (BST\_OUT) can vary in the range [14.7 $\div$ 80] V with a granularity of 7 bits.

DS12448 Rev 3

The voltage range and the granularity are defined to give flexibility because of internal output divider: the control loop regulates the output voltage on BST\_OUT pin looking to the internal feedback voltage.

Device output voltage is configurable via SPI (see CR#2 Bit[11:5], BST\_OUT in *Table 23: CR#2: Control Register 2*) or through dedicated OTPs (for stand-alone configuration).

## 3.4 Overvoltage protection

The peak current mode requires a minimum on-time, because of the noise generated right after the turn-on of the switching MOSFET. At light load (very low output current), this minimum on-time, in combination with the selected switching frequency is no longer able to regulate the output voltage to the requested voltage. The device enters in overvoltage protection (OVP), in order to prevent an excessive rise of the boost output voltage above the target voltage.

This mode is activated when the voltage on BST\_OUT pin is higher than the selected of a specified threshold value (VBST\_OUT\_OV\_ON).

The switching activity is resumed as soon as the voltage on BST\_OUT pin decreases to the selected one. In case of BST\_OUT voltage increases above VBST\_OUT\_OV\_ON, an output digital flag, called BST\_OVP, is set. As soon as the output voltage decreases down to programmed target value (BST\_OUT [xxxxx]), the bit is reset after t<sub>BST\_OVP\_RST</sub> delay time (10ms typical). This delay time is implemented in order to eliminate the diagnostic ambiguity (toggling of the OVP flag) during permanent no load or light load operation.

BST\_OVP bit is not set in case of boost disabled.

## 3.5 Output failure protection

The L99LD02 is protected in case of boost controller output voltage pin failure. More in detail, a specific bit, called BST\_OUT\_FAIL (see SR#1 Bit[6], BST\_OUT\_FAIL in *Table 26: SR#1: Status Register 1*), is set in case of output voltage pin (BST\_OUT) pin is left floating or shorted to ground.

This bit is set:

- If device is OFF, boost controllers do not start;

- If device is ON in

- single/dual phase configuration, boost controllers are immediately switched OFF;

- If device is ON in three/four phases configuration and it is in Active mode: both Master/Salve devices are switched off when the failure is recognized on Master side; only Slave device is switched off when the failure is recognized on Slave side while the Master is managed by the microcontroller;

- If device is ON in three/four phases configuration and it is in Limp Home: both Master/Salve devices are switched off when the failure is recognized on Master side; only Slave device is switched off when the failure is recognized on Slave side, while the Master is forced to work at minimum duty cycle.

The reset of BST\_OUT failure bit is demanded to the microcontroller (in Active mode) or to an auto-restart function (in Limp Home) that cyclically clears this bit with a period equal to  $t_{AUTORESTART}$ .

This bit is not set if BST\_DIS bit is set.

DS12448 Rev 3

## 3.6 Soft start

The L99LD02 features an internal soft start function, which gradually increases the boost current in 9 steps, in order to avoid a voltage overshoot of the boost output. The threshold of the current limitation reaches its nominal value after a specified soft start time ( $t_{SS}$ ).

A soft-start phase is initiated at the activation of the boost controller:

- after leaving standby mode;

- after deactivation of the boost controller due to a VS under voltage;

- after a previous deactivation of the boost by SPI (see CR#3 Bit[2:1], BST\_DIS in Table 24: CR#3: Control Register 3);

- after deactivation of the boost controllers due to a BST\_OUT\_FAIL;

- after deactivation of the boost controllers due to OVT.

# 3.7 Stability – Error Amplifier characteristics

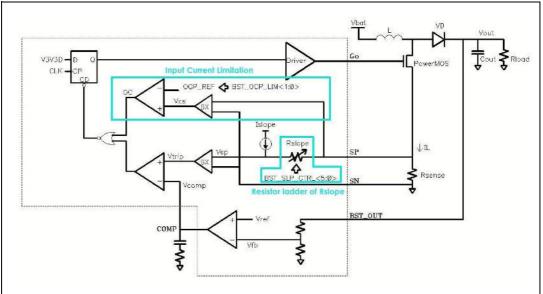

Slope compensation is needed to ensure loop stability with all possible values of duty cycle: D = TON / T (0 < D < 1) especially when duty cycle is greater than 0.5. The slope of the additional ramp is proportional to converter inductor current slope during the turn off phase. The L99LD02 generates an internal peak current value, I<sub>SLOPE</sub>, which is added to the positive sensing signal at the output of the OTA (see the following figure).

To avoid the use of external slope compensation resistor, thus limiting the coupling noise on the sense positive path, the compensation ramp slope of each boost controller can be configured by 6 bits (see Bit [23÷18], BST\_SLP\_CTRL, in *Table 23: CR#2: Control Register 2*) in the range [from 0.45 to 13.05] k $\Omega$  with a granularity step of 0.2 k $\Omega$ .

To keep the same compensation loop in multi-phase operation (same gain / phase-margin / band-width), without any hardware change, the OTA gain value can be configurable in 4 steps according to *Table 3*.

| BITs [1÷0] | BST_GM_OTA [µS] |

|------------|-----------------|

| 00         | 200             |

| 01         | 400             |

| 10         | 600             |

| 11         | 800             |

Both slope compensation and OTA gain are configurable via SPI (see CR#2 Bit[15:14], BST\_GM\_OTA in *Table 23: CR#2: Control Register 2*) or through dedicated OTPs (for stand-alone operation). Moreover, the OTA can be disabled through dedicated bit / OTP (see CR#2 Bit[17], BST\_DIS\_OTA in *Table 23: CR#2: Control Register 2*).

Homogeneous power losses distribution in multi-phases is guaranteed thanks to design specific measures ensuring the lowest spread for key-parameters like linear amplifier gain and offset ( $G_{LA}$  and  $G_{LA_OFFSET}$ ), slope compensation current ( $I_{SLOPE}$ ) and voltage on COMP pin ( $V_{COMP}$ ).

# 3.8 Operation in multiphase interleaved mode

The multiphase operation mode is needed in case of high output power requirement. The maximum output power per phase in front of LED applications is typically 35W considering a cost effective design. This limitation is mainly given by power losses and thermal constraints. By sharing the current between several phases, the conduction losses (which are proportional to the square of the conducted current) are reduced and the efficiency of the boost stage increases, in comparison to a single-phase. Another advantage of multiphase topology is higher effective switching frequency and lower ripple currents which significantly reduces the filtering effort on input and output side. In ideal case of 50% duty cycle in 2-phase mode (respectively 33.3% in 3-phase or 25% in 4-phase), the input ripple current is reduced down to zero.

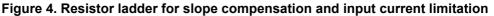

The L99LD02 can be configured in 1, 2, 3 or 4 phase mode. The 1 or 2 phase mode can be realized with one device as shown in *Figure 5: 1 or 2 phase configuration with single L99LD02 device*.

Figure 5. 1 or 2 phase configuration with single L99LD02 device

In case of 3 or 4 phase mode, two devices are needed with SYNC\_I/O, BST\_COMP and BST\_OUT pins connected together as shown in *Figure 8: 3 or 4 phase configuration with two L99LD02 devices*. One of the devices must be configured as a master and other device as a slave by a dedicated configuration bit.

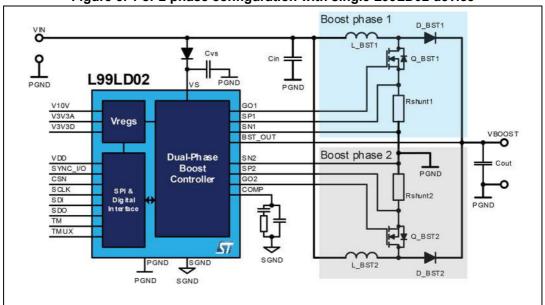

In master mode, an internal oscillator is used. The switching frequency is configurable via SPI by 3 bits. The clock signal is distributed in both boost channels and SYNC\_I/O pin (output) with configurable phase shift according to the desired number of phases – see *Table 4: Clock distribution – MASTER (internal clock source)*.

In slave mode, the device uses an external clock signal from SYNC\_I/O pin (input mode). This signal is used for boost channel 1 (no phase shift) and channel 2 ( $180^{\circ}$  phase shift) – see *Table 5*.

| Table 4. Clock distribution – MASTER (Internal Clock Source) |                       |         |         |

|--------------------------------------------------------------|-----------------------|---------|---------|

| MASTER                                                       | Phase config (2 bits) |         |         |

| Signal                                                       | 2 phase               | 3 phase | 4 phase |

| CLK1                                                         | 0°                    | 0°      | 0°      |

| CLK2                                                         | 180°                  | 120°    | 180°    |

| SYNC_OUT                                                     | 0°                    | 240°    | 90°     |

Table 4. Clock distribution – MASTER (internal clock source)

| Table 5. Clock distribution – SLAVE | (external clock source) |

|-------------------------------------|-------------------------|

|-------------------------------------|-------------------------|

| SLAVE   | Phase config (2 bits) |               |         |  |  |

|---------|-----------------------|---------------|---------|--|--|

| Signal  | 2 phase 3 phase 4     |               | 4 phase |  |  |

| SYNC_IN | 0°                    | 0°            | 0°      |  |  |

| CLK1    | 0°                    | 0°            | 0°      |  |  |

| CLK2    | 180°                  | 180° (unused) | 180°    |  |  |

### Figure 7. Clock distribution scheme for 3 and 4 phase boost

Figure 8. 3 or 4 phase configuration with two L99LD02 devices

For a proper current balancing between boost phases, identical external components (especially shunt resistors and inductors) must be used. In case of interconnection of two devices (3 or 4 phase systems), the following configuration must be applied:

| SPI configuration                                                                                                                      | Master device                                                                                               | Slave device                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MS (1 bit)                                                                                                                             | 0                                                                                                           | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BST_N_PHASE (2 bits)                                                                                                                   | 3 or 4 phase                                                                                                | Any value (this setting has no effect in slave mode)                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BST_GM_OTA (2 bits)<br>BST_GM_OTA (2 bits)<br>BST_GM_OTA (2 bits)<br>(see Section 3.7: Stability –<br>Error Amplifier characteristics) |                                                                                                             | Disabled<br>Enable is also allowed – then the<br>resulting Gm value is a sum of Gm<br>values of both devices. However, in<br>case the slave device is disabled<br>(e.g. due to lower output power<br>demand) the Gm of only master<br>device becomes too low with given<br>compensation network. This would<br>results in much lower regulation loop<br>bandwidth than it could be. Then,<br>another SPI command for increasing<br>master's Gm value might be<br>needed. |

| BST_SLP_CTRL (6 bits)                                                                                                                  | According to application<br>conditions<br>(see Section 3.7: Stability –<br>Error Amplifier characteristics) | Identical as master<br>(is a must for equal current<br>balancing)                                                                                                                                                                                                                                                                                                                                                                                                        |

| According to application<br>conditions<br>(see CR#2 Bit[13:12],<br>BST_OCP_LIM in Table 2:<br>CR#2: Control Register 2)                |                                                                                                             | Identical as master<br>(for consistent overcurrent<br>protection level)                                                                                                                                                                                                                                                                                                                                                                                                  |

| BST_OUT (7 bits)                                                                                                                       | According to requested output voltage                                                                       | Identical as master<br>(for consistent overvoltage<br>diagnostic feedback, power good<br>flag and correct output voltage in<br>case of slave's OTA kept enabled)                                                                                                                                                                                                                                                                                                         |

| BST_DIS (2 bit)                                                                                                                        | Phase 1, Phase 2 enabled<br>(see CR#3 Bit[2:1], BST_DIS<br>in Table 24: CR#3: Control<br>Register 3)        | 3-phase configuration: Phase 1<br>enabled, Phase 2 disabled<br>4-phase configuration: Phase 1,<br>Phase 2 enabled                                                                                                                                                                                                                                                                                                                                                        |

| Table 6. Clock distribution - MASTER | (internal clock source) |

|--------------------------------------|-------------------------|

| Table 0. Clock distribution - MASTER | (internal clock source) |

# 4 Functional description

# 4.1 Operating modes

Figure 9. Device state diagram

| Operating<br>mode   | Entering conditions                                                                                                                                                                                                                                                                                                                                                                                                                                     | Leaving condition                                                                                                                                         | Characteristics                                                                                                                 |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Standby<br>mode     | <ul> <li>By default, once the device is powered (VS present);</li> <li>CSN High for more than t<sub>STDBY</sub> when the device is in Pre-standby mode</li> </ul>                                                                                                                                                                                                                                                                                       | CSN pin Low for t > t <sub>WAKEUP</sub>                                                                                                                   | <ul> <li>V3V3 &lt; VPOR;</li> <li>VS and VDD low consumption;</li> <li>SPI inactive</li> </ul>                                  |

| Pre-standby<br>mode | <ul> <li>Under following condition, when device is in<br/>Active mode:</li> <li>Two consecutive SPI frames setting:<br/>UNLOCK = 1         <ul> <li>(EN,GOSTBY) = (0,1)</li> <li>Under following condition, when device is in<br/>Limp Home:</li> <li>Two consecutive SPI frames setting:<br/>UNLOCK = 1                  <ul></ul></li></ul></li></ul>                                                                                                 | Automatic transition to:<br>– Standby mode if CSN pin<br>High for t > t <sub>STDBY</sub><br>– Reset mode if CSN pin<br>Low for t > t <sub>PRE_STDBY</sub> | – V3V3>VPOR<br>– Boost disabled<br>– SPI active                                                                                 |

| Reset mode          | <ul> <li>By default, when device leaves Standby mode</li> <li>Under following condition, when device is in Active mode:</li> <li>VDD Under voltage</li> <li>WD failure;</li> <li>One SPI frame setting (EN,GOSTBY) = (0,0)</li> <li>Two consecutive SPI frames setting: UNLOCK = 1</li> <li>(EN,GOSTBY) = (1,1)</li> <li>Under following condition, when device is in Pre-standby mode:</li> <li>CSN pin low for t &gt;t<sub>PRE_STDBY</sub></li> </ul> | Automatic transition to Limp<br>Home after 400 ns                                                                                                         | <ul> <li>All registers reset to default values according to OTP settings</li> <li>V3V3&gt;VPOR</li> <li>SPI inactive</li> </ul> |

Table 7. Operating modes

| Operating<br>mode | Entering conditions                             | Leaving condition                                                                                                                                                                                                                                                                              | Characteristics                                                                                                               |

|-------------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Limp Home         | – 400 ns after Reset mode                       | <ul> <li>SPI sequence to enter<br/>Active mode:</li> <li>UNLOCK = 1</li> <li>(EN,GOSTBY) = (1,0)</li> <li>SPI sequence to enter<br/>Pre-Standby mode:</li> <li>UNLOCK = 1</li> <li>(EN,GOSTBY) = (1,0)</li> <li>OR</li> <li>TM = Low for t<sub>TM_LOW</sub></li> </ul>                         | <ul> <li>Boost enabled</li> <li>Device operation according to OTP settings</li> <li>SPI active</li> </ul>                     |

| Active mode       | SPI sequence:<br>UNLOCK = 1 (EN,GOSTBY) = (1,0) | <ul> <li>VDD under voltage</li> <li>WD failure</li> <li>SPI sequence</li> <li>(EN,GOSTBY) = (0,0)</li> <li>SPI sequence</li> <li>UNLOCK = 1</li> <li>(EN,GOSTBY) = (1,1)</li> <li>SPI sequence to enter</li> <li>Pre-Standby mode:</li> <li>UNLOCK = 1</li> <li>(EN,GOSTBY) = (0,1)</li> </ul> | <ul> <li>Boost enabled</li> <li>SPI is active</li> <li>Device operating according to SPI control register settings</li> </ul> |

| Table 7. | Operating r | nodes (con | tinued) |

|----------|-------------|------------|---------|

|----------|-------------|------------|---------|

### 4.1.1 Standby mode

The pre-requisites for this mode are:

- Device in power down

- Device in Pre-Standby mode

The device enters Standby mode under the following conditions:

- By default, once the device is powered (VS present);

- CSN High for more than t<sub>STDBY</sub>

The Standby mode characteristics are:

- V3V3 < VPOR

- VDD and VS low consumption

- SPI inactive

The device leaves this mode if:

• CSN Low for a time t > t<sub>WAKEUP</sub>

### 4.1.2 **Pre-standby mode**

The device enters Pre-standby mode under the following conditions:

• upon the two following consecutive SPI frames setting:

UNLOCK = 1

(see bit <1> on Table 22: CR#1: Control Register 1)

(EN,GOSTBY) = (0,1)

(see bit <3> and bit <2> on Table 23: CR#2: Control Register 2)

Or upon the condition of TM pin is low for more than a fixed time window ( $t_{TM LOW}$ ).

The Pre-standby mode characteristics are:

- V3V3 > VPOR

- Boost disabled

- SPI active

The device leaves automatically Pre-standby mode entering:

- Standby, if CSN high for a time t > t<sub>STDBY;</sub>

- Reset, if CSN Low for a time t > t<sub>PRE\_STDBY</sub>

### 4.1.3 Reset mode

The device enters Reset mode under the following conditions:

- By default, once the device leaves Standby mode;

- If in Active mode, when one of the following events occur:

- VDD under voltage;

- Watchdog failure

- One SPI frame setting (EN,GOSTBY) = (0,0)

- Two consecutive SPI frames setting

UNLOCK = 1

(EN,GOSTBY) = (1,1)

The Reset mode characteristics are:

- V3V3 > VPOR

- Control and status registers set to their default values (according to OTP settings)

- SPI inactive

The device leaves automatically Reset mode entering Limp Home after 400 ns (typical).

### 4.1.4 Limp Home / Stand-alone mode

The device enters Limp Home automatically 400 ns after Reset mode.

Limp Home characteristics are:

- Boost active

- Operation according to OTP settings

- SPI active:

- All SPI write operations must be allowed without any effects on the device behavior.

When the device leaves this mode, it can enter Standby or Active mode.

If the Microcontroller sends the following SPI frames sequence:

- The first SPI frame sets UNLOCK bit = 1 (see bit <1> on Table 22: CR#1: Control Register 1)

- The second consecutive SPI frame sets GO\_STBY bit = 1 and EN bit = 0, (see bit <3> and bit <2> on *Table 23: CR#2: Control Register 2*)

Or, if in stand-alone operation, upon the condition of TM pin is low for more than a fixed time window ( $t_{TM\ LOW}$ ), the device enters Pre-Standby mode.

Then, the device automatically enters:

- Standby, if CSN high for a time t > t<sub>STDBY;</sub>

- Reset, if CSN Low for a time t > t<sub>PRE\_STDBY</sub>;

If the Microcontroller sends to the device the sequence of the following SPI frames:

- The first SPI frame reads and clears the WD-Fail bit (see bit <14> on Table 26: SR#1: Status Register 1)

- The second SPI frame sets UNLOCK bit = 1 (see bit <1> on Table 22: CR#1: Control Register 1)

- The third consecutive SPI frame sets GOSTBY bit = 0 and EN bit = 1 (see bit <3> and bit <2> on *Table 23: CR#2: Control Register 2*)

The device enters Active mode.

In Limp Home, after setting bit 27 on GSB (FE1, functional error bit), an auto-restart procedure is implemented: every  $t_{AUTORESTART}$ , functional error bit eventually set is automatically cleared.

#### 4.1.5 Active mode

The device enters the Active mode if the Microcontroller sends the following SPI frames sequence:

- The first SPI frame reads and clears the WD-Fail bit (see bit <14> on Table 26: SR#1: Status Register 1)

- The second SPI frame sets UNLOCK bit = 1 (see bit <1> on Table 22: CR#1: Control Register 1)

- The third consecutive SPI frame sets GOSTBY bit = 0 and EN bit = 1 (see bit <3> and bit <2> on *Table 23: CR#2: Control Register 2*)

# 4.2 Protections and diagnostic

### 4.2.1 Temperature warning

The device integrates a temperature warning TW with two thresholds TW1 and TW2.

If the T<sub>j</sub> (junction temperature) of the boost controllers rises above TW1 or TW2, the status bit TWx (x=1 or x=2 stands for the TW1 or TW2) is set on the status registers (see bit <18> and bit <19> on *Table 26: SR#1: Status Register 1*). Thermal warning is also reported in the Global Status Byte register, and in particular, bit 25 (GW) is set.

If the Tj drops below the temperature warning reset threshold 1 (TW1-TW1\_HYS), respectively  $TW_2 - TW_2_HYS$ , the corresponding status bit is automatically reset. As long as the Tj does not exceed the over temperature shutdown, the device does not latch off the boost controllers, even if a temperature warning is detected.

Note that, powering the device via the BST\_OUT will produce an extra power dissipation which must be taken into account during the thermal design.

In case the device is supplied from BST\_OUT pin, a flag called BST\_OUT\_SUPPLY is provided to inform the application. If the junction temperature rises above TW (thermal warning) threshold, the application can decide to decrease power losses on gate driver V10V regulator (switching off 1 boost phase or decreasing boost switching frequency), minimizing the risk of undesired thermal shutdown.

### 4.2.2 Overcurrent

On top of the normal current regulation loop comparator, the L99LD02 integrates an additional comparator to clamp the maximum physical current that can flow in the booster input circuit while the MOSFET is driven. The aim is to protect all the external components involved (inductor from saturation, diode and MOSFET from overcurrent...).

The protection is active PWM cycle-by-cycle and switches off the MOSFET gate as the voltage drop across the shunt resistor reaches its maximum threshold (BST\_OCP\_LIM).

This threshold can be set by SPI / OTPs according to Table 8.

| BITs [1÷0] | BST_OCP_LIM [mV] |

|------------|------------------|

| 00         | 50               |

| 01         | 85               |

| 10         | 115              |

| 11         | 150              |

Table 8. Boost threshold for input current limitation

### 4.2.3 Over-temperature shutdown

If the junction temperature rises above the shutdown temperature TTSD, an overtemperature event (OVT) is detected. The boost controllers are switched off and the corresponding bit OVT is set in the status register (see bit <20> on *Table 26: SR#1: Status Register 1*). Over-temperature event is also reported in the Global Status Byte register and

in particular bit 27 FE1 is set. In normal mode the boost controllers are latched off, until the following conditions are fulfilled:

- TJX drops below the thermal shutdown reset threshold TTSD-TTSD\_HYS.

- Subsequently the microcontroller sends a read and clear command, in order to reset OVT bit.

In fail safe mode (Limp Home), the device applies an auto restart with a period equal to tAUTORESTART, provided that the TJX falls below TSD reset threshold (TTSD-TTSD\_HYS).

#### 4.2.4 VS under voltage lockout

Provided device is not supplied from BST\_OUT if the VS supply falls below Vs\_UV (VS under voltage threshold), the boost controllers will be deactivated, regardless of the SPI control register. This feature is implemented, in order to avoid an operation of the external mosfet of the boost controller in linear mode, due to a too low gate driver supply.

In this case, BST\_OUT\_SUPPLY bit is not set whilst VS\_UV\_FAIL bit is set (see bit <13> on Table 26: SR#1: Status Register 1)

# 5 Serial peripheral interface (ST SPI standard)

The ST-SPI is a standard used in ST Automotive ASSP devices. Therefore the here standardized SPI is described from SPI-Slave-Device point of view: a common structure of the communication frames and specific addresses for product and status information are defined.

The ST-SPI will allow usage of generic software to operate the devices while maintaining the required flexibility to adapt it to the individual functionality of a particular product. In addition to that, failsafe mechanisms are implemented to protect the communication from external influences and wrong or unwanted usage.

# 5.1 Physical layer - Functional description

This device features a 32-bit ST SPI in slave configuration for bi-directional communication with an external microcontroller. This device supports burst read access and shall be operated in the following mode: CPOL = 0 and CPHA = 0.

For this mode, input data is sampled on the rising edge of the clock signal SCK and output data is changed on the falling edge of SCK.

During standby mode, the SPI interface is deactivated.

Signal Description:

Chip Select Not (CSN)

The input pin is used to select the serial interface of this device. When CSN is high, the

output pin (SDO) will be in high-impedance state. In case CSN is stuck at GND, a

timeout is implemented which sets the SDO line back to high-impedance to release the

SPI network. A low signal activates the output driver and a serial communication can be started. The state during CSN = 0 is called a communication frame.

- Serial Data In (SDI)

The input pin is used to transfer data serially into the device. The data applied to SDI will be sampled on the rising edge of the SCK signal and shifted into an internal 32-bit shift register. On the rising edge of the CSN signal, the contents of the shift register will be transferred to the Data Input Register.

Only communication frames with 0 (read GSBN bit), 24 (standard communication frame), or 24 + (n \* 16) (burst read/write) clock pulses are accepted. All others will be ignored and a communication error will be reported with the next SPI command.

- Serial Data Out (SDO)

The data output driver is activated by a logic low level at the CSN input. After a falling edge of the CSN pin, the SDO pin will leave the tri-state condition and present the GSBN bit. At all following falling edges of the SCK signal, the following bits of the SPI frame are shifted out to the SDO pin.

- Serial Clock (SCK)

The SCK input is used to synchronize the input and output serial bit streams. The data input (SDI) is sampled on the rising edge of the SCK and the data output (SDO) will change with the falling edge of the SCK signal. The SPI can be driven with a SCK frequency up to 4 MHz.

# 5.2 Physical layer – protocol

#### 5.2.1 SDI frame

The data-in frame consists of 32 bits (OpCode + Address + Data).

The first two transmitted bits contain the Operation Code which represents the instruction to be performed. The following 6 bits represent the address on which the operation will be performed.

The subsequent 24 bits contain the payload data.

|      | Operating code |     |    |    | Add | ress |    |    |

|------|----------------|-----|----|----|-----|------|----|----|

| Bit  | 31             | 30  | 29 | 28 | 27  | 26   | 25 | 24 |

| Name | OC1            | OC0 | A5 | A4 | A3  | A2   | A1 | A0 |

Table 10. Data byte 2

Table 9. Command byte (8 bit)

|      |     |     |     | Data | byte 2 |     |     |     |

|------|-----|-----|-----|------|--------|-----|-----|-----|

| Bit  | 23  | 22  | 21  | 20   | 19     | 18  | 17  | 16  |

| Name | D23 | D22 | D21 | D20  | D19    | D18 | D17 | D16 |

| Table TT. Data byte T |             |     |     |     |     |     |    |    |

|-----------------------|-------------|-----|-----|-----|-----|-----|----|----|

|                       | Data byte 1 |     |     |     |     |     |    |    |

| Bit                   | 15          | 14  | 13  | 12  | 11  | 10  | 9  | 8  |

| Name                  | D15         | D14 | D13 | D12 | D11 | D10 | D9 | D8 |

#### Table 11. Data byte 1

#### Table 12. Data byte 0

|      | Data byte 0 |    |    |    |    |    |    |    |

|------|-------------|----|----|----|----|----|----|----|

| Bit  | 7           | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

| Name | D7          | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

#### Table 13. Operation code definition

| OC1 | 0C0 | Meaning                                |

|-----|-----|----------------------------------------|

| 0   | 0   | <write mode=""></write>                |

| 0   | 1   | <read mode=""></read>                  |

| 1   | 0   | <read and="" clear="" mode=""></read>  |

| 1   | 1   | <read device="" information=""></read> |

The operation code is used to distinguish between different access modes to the registers of the slave device.

The Write and Read Mode operations allow access to the RAM of the device.

The Read and Clear operation is used to read a status register and subsequently clears its content.

The Read Device Information allows access to the ROM area which contains device specific read-only data (like Device ID and SPI settings device related information) predefined by the ST SPI standard.

#### 5.2.2 SDO Frame

The Data-Out Frame consists of 32 bits (GSB + Data).

The first eight transmitted bits contain device-related status information and are latched into the shift register at the time of the Communication Start. These 8 bits are transmitted at every SPI transaction.

The subsequent bytes contain the payload data and are latched into the shift register with the eighth positive SCK edge. This could lead to an inconsistency of data between the GSB and Payload due to different shift register load times. Anyhow, no unwanted Status Register clear should appear, as status information should just be cleared with a dedicated bit clear after read.

|      | Global Status Byte |      |      |     |     |    |    |    |  |  |  |  |  |  |  |

|------|--------------------|------|------|-----|-----|----|----|----|--|--|--|--|--|--|--|

| Bit  | 31                 | 30   | 29   | 28  | 27  | 26 | 25 | 24 |  |  |  |  |  |  |  |

| Name | GSBN               | RSTB | SPIE | FE2 | FE1 | DE | GW | FS |  |  |  |  |  |  |  |

#### Table 14. Global Status Byte

|      | Data byte2 |     |     |     |     |     |     |     |  |  |  |  |  |

|------|------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|--|

| Bit  | 13         | 22  | 21  | 20  | 19  | 18  | 17  | 16  |  |  |  |  |  |

| Name | D23        | D22 | D21 | D20 | D19 | D18 | D17 | D16 |  |  |  |  |  |

#### Table 15. Data byte2

#### Table 16. Data byte1

|      | Data byte1 |     |     |     |     |     |    |    |  |  |  |  |  |

|------|------------|-----|-----|-----|-----|-----|----|----|--|--|--|--|--|

| Bit  | 15         | 14  | 13  | 12  | 11  | 10  | 9  | 8  |  |  |  |  |  |

| Name | D15        | D14 | D13 | D12 | D11 | D10 | D9 | D8 |  |  |  |  |  |

#### Table 17. Data byte0

|      | Data byte0 |    |    |    |    |    |    |    |  |  |  |  |

|------|------------|----|----|----|----|----|----|----|--|--|--|--|

| Bit  | 7          | 6  | 5  | 4  | 3  | 2  | 1  | 0  |  |  |  |  |

| Name | D7         | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |  |  |

The Global Status Byte is described here below.

The Payload (DATA Byte 0,1 & 2) is the data transferred from the slave device with every SPI communication to the microcontroller. The Payload always follows the OpCode and the Address bit of the actual shifted in data (In-Frame-Response).

#### Table 18. Global Status Byte

| Bit | Name | Description                                                                                                                                                                                  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31  | GSBN | Global Status Bit Not<br>This bit is a NOR combination of the remaining bits of this register:<br>RSTB nor SPIE nor FE2 nor FE1 nor DE nor GW nor FS                                         |

| 30  | RSTB | Reset Bit<br>The RSTB indicates a device reset. In case this bit is set, all internal <i>Control</i><br><i>Registers</i> are set to default and kept in that state until the bit is cleared. |

| 29  | SPIE | SPI Error<br>The SPIE is a logical OR combination of errors related to a wrong SPI<br>communication (SDI stuck, wrong number of clock, parity check error)                                   |

| 28  | FE2  | Functional Error 2<br>VS_UV_FAIL                                                                                                                                                             |

| 27  | FE1  | Functional Error 1<br>OVT or BST_OUT_FAIL                                                                                                                                                    |

| Bit | Name | Description                                              |

|-----|------|----------------------------------------------------------|

| 26  | DE   | Device error<br>N_PWR_GOOD or BST_OVP                    |

| 25  | GW   | Global warning:<br>TW1 or TW2                            |

| 24  | FS   | Fail safe:<br>If this bit is set, device is in Limp Home |

Table 18. Global Status Byte (continued)

# 5.3 Address and data definition

### 5.3.1 Device Information Register

The Device Information Register can be read by using OpCode '11'. After shifting out the GSB, the 8-bit wide payload will be transmitted. After shifting out the GSB followed by the 8-bit wide payload, a series of '0' is shifted out at the SDO pin.

| Operating code |     |  |  |  |  |  |  |  |

|----------------|-----|--|--|--|--|--|--|--|

| OC1            | 0C0 |  |  |  |  |  |  |  |

| 1              | 1   |  |  |  |  |  |  |  |

| Address | Name                       | Access                              | Content                                                                 |  |  |  |  |

|---------|----------------------------|-------------------------------------|-------------------------------------------------------------------------|--|--|--|--|

| 01h     | Control Register 1         | R/W                                 | CR#1: 1 <sup>st</sup> Control Register                                  |  |  |  |  |

| 02h     | Control Register 2         | R/W                                 | CR#2: 2 <sup>nd</sup> Control Register                                  |  |  |  |  |

| 03h     | Control Register 3         | R/W                                 | CR#3: 3 <sup>rd</sup> Control Register                                  |  |  |  |  |

| 04h     | Control Register 4         | R/W                                 | CR#4: 4 <sup>th</sup> Control Register                                  |  |  |  |  |

| 06h     | Status Register 1          | R/C                                 | SR#1: 1 <sup>st</sup> Status Register                                   |  |  |  |  |

| 3Eh     | Ctm Trimming<br>Register1  | R/W<br>(W only when EOT<br>bit = 0) | CT: Customer Trimming Register1                                         |  |  |  |  |

| 3Fh     | Ctm Trimming<br>Register2  | R/W<br>(W only when EOT<br>bit = 0) | CT: Customer Trimming Register2                                         |  |  |  |  |

| 3Fh     | Advanced<br>Operation Code | Clear                               | A R&C operation to this address causes a status registers to be cleared |  |  |  |  |

#### Table 20. RAM Memory Map

| Table 21. ROM Memory Map |                 |        |                  |                  |                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|--------------------------|-----------------|--------|------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Address                  | Name            | Access | Content<br>(hex) | Content<br>(bin) | Comments                                                                                                                                                                                                                               |  |  |  |  |  |  |

| 00h                      | Company Code    | R      | 00h              | 0000000b         | STMicroelectronics                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 01h                      | Device family   | R      | 02h              | 00000010b        | LED product family                                                                                                                                                                                                                     |  |  |  |  |  |  |

| 02h                      | Device N. 1     | R      | 55h              | 01010101b        | 'U' in ASCII                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 03h                      | Device N. 2     | R      | 42h              | 01000010b        | 'B' in ASCII                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 04h                      | Device N. 3     | R      | 42h              | 01000010b        | 'B' in ASCII                                                                                                                                                                                                                           |  |  |  |  |  |  |

| 05h                      | Device N. 4     | R      | 44h              | 01000100b        | 'D' in hex                                                                                                                                                                                                                             |  |  |  |  |  |  |

| 0Ah                      | Silicon version | R      | 01h              | 0000001b         | Second version                                                                                                                                                                                                                         |  |  |  |  |  |  |

| 10h                      | SPI Mode        | R      | 31h              | 00110001b        | Bit7 = 0, burst read is disabled<br>SPI data length = 32 bits<br>Bit6, DL2 = 0<br>Bit5, DL1 = 1<br>Bit4, DL0 = 1<br>Bit3, SPI8 =0 : 8 bit frame<br>option not available<br>Bit2 =0<br>Parity check is used<br>Bit1, S1=0<br>Bit0, S0=1 |  |  |  |  |  |  |

| 11h                      | WD Type 1       | R      | 4Ah              | 01001010b        | A WD is implemented<br>Bit7, WD1 =0<br>Bit6, WD0 =1<br>WD period 50ms = 10*5ms<br>-> WT[5:0] = 0xA<br>Bit5, WT5 = 0<br>Bit4, WT4 = 0<br>Bit3, WT3 = 1<br>Bit2, WT2 = 0<br>Bit1, WT1 = 1<br>Bit0, WT0 = 0                               |  |  |  |  |  |  |

| 13h                      | WD bit pos. 1   | R      | 44h              | 01000100b        | Bit7,WB1 = 0<br>Bit6,WB2 = 1<br>WBA[5-0], Bit[5-0] = address<br>of the config. register, where<br>the WD bit is located = 04d =<br>000100b                                                                                             |  |  |  |  |  |  |

Table 21. ROM Memory Map

| Address | Name                       | Access              | Content<br>(hex) | Content<br>(bin) | Comments                                                                                                                                                                                                                                                            |

|---------|----------------------------|---------------------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14h     | WD bit pos. 2              | R                   | D7h              | 11010111b        | Bit7,WB1 = 1<br>Bit6,WB0 = 1<br>Bit position of the WD bit<br>within the corresponding<br>configuration register<br>= 23d = 010111b                                                                                                                                 |

| 20h     | SPI CPHA Test              | SPI CPHA Test R 55h |                  | 01010101b        | Predefined by ST SPI V4.1, it<br>is used to verify that the SCK<br>Phase of the SPI master is set<br>correctly                                                                                                                                                      |

| 3Eh     | GSB Options                | R                   | 00h              | 0000000b         | All bits of GSB are used                                                                                                                                                                                                                                            |

| 3Fh     | Advanced<br>Operation Code | R OOb               |                  | 0000000b         | Access to this address<br>provokes a SW reset (all<br>control registers are set to<br>their default values; in<br>addition, all status registers<br>are cleared too).<br>NOTE: Data field should not<br>be "all ones", otherwise an<br>"SDI stuck at" error occurs. |

Table 21. ROM Memory Map (continued)

The Device Identification Registers represent a unique number identifying device partnumber.

By reading out the <SPI Mode> register, general information of SPI usage of the Device Application Registers can be read.

The SPI Burst Read bit indicates if a burst read operation is implemented.

The L99LD02 does not feature SPI Burst Read.

The SPI Data Length value indicates the length of the SCK count monitor which is running for all accesses to the Device Application Register. In case of a communication frame with an SCK count not equal to the reported one, this will lead to a SPI Error and the data will be rejected.

The default frame size of the L99LD02 is 32 bits, so the SPI Data Length bits are read as '011'.

For the L99LD02, a Data Consistency Check by parity check is implemented, therefore these bits are read as '01'. An odd parity bit is used and it is calculated over the complete communication frame.

The GSB Options byte indicates that device-specific status information is used instead of the predefined one. In case a bit of the GSB is not used, it has to be fixed to '0' value and is indicated by a logical '1' in the GSB Options byte.

#### L99LD02

### 5.3.2 Device application registers

The Device Application Registers are all registers accessible using OpCode '00', '01' and '10'.

An access to an unused address will not lead to any error. Any data read from an unused address is not defined.

# 5.4 Protocol failure detection

To realize a protocol which fulfills certain failsafe requirements, a basic set of failure detection mechanisms is implemented.

### 5.4.1 Clock monitor

During communication (CSN low to high phase) a clock monitor counts the valid SCK clock edges. If the SCK edges do not correlate with the SPI Data Length, an SPIE is reported with the next command and the current communication is rejected.

By accessing the Device Information Registers (OpCode = '11'), the Clock Monitor is set to a minimum of 16 SCK edges plus a multiple of 8 (e.g. 16, 24, 32).

Providing no SCK edge during a CSN low to high phase is not recognized as an SPIE.

### 5.4.2 SCK polarity (CPOL) check

To detect wrong polarity access on SCK, the internal clock monitor is used. Providing first a negative edge on SCK during communication (CSN low to high phase) or a positive edge at last will lead to an SPI Error being reported in the next communication and the current data is rejected.

### 5.4.3 SCK phase (CPHA) check

To verify that the SCK phase of the SPI master is set correctly a special Device Information Register is implemented. By reading this register the data must be 55H. In case AAH is read, the CPHA setting of the SPI master is wrong and a proper communication cannot be guaranteed.

### 5.4.4 CSN timeout

By pulling CSN low, the SDO is set active and leaves the tri-state condition. To ensure communication between other SPI devices within the same bus even in case of CSN stuck at low, a CSN timeout is implemented. By pulling CSN low, an internal timer is started. After the timer end is reached, the current communication is rejected and the SDO is set to tri-state condition. This error is not reported in any specific status register.

#### 5.4.5 Data stuck

SDI stuck at GND

As a command with all data bits set to '0' and OpCode '00' on address b'000000 cannot be distinguished from an SDI stuck-at-GND error, this command is not allowed. In case

a stuck-at-GND error is detected, the communication will be rejected and the SPIE will be set in the next communication cycle.

- SDI stuck at HIGH As a command with all data bits set to '1' and OpCode '11' on address b'111111 cannot be distinguished from an SDI stuck-at-HIGH error, this command is not allowed. In case a stuck-at-HIGH error is detected, the communication will be rejected and the SPIE will be set in the next communication cycle.

- SDO stuck SDO stuck-at-GND and stuck-at-HIGH errors have to be detected by the SPI master. As the definition of the GSB guarantees at least one bit toggle, a GSB with all bits set to '0' or with all bits set to '1' can be considered as an SDO stuck-at error.

# 5.5 Implementation remarks

### 5.5.1 Register change during communication

From an implementation point of view, it is guaranteed that no register change gets lost during communication. In case a register value was changed during a communication, it will be reported with the next communication frame.

### 5.5.2 GSB and payload inconsistency

Due to the internal implementation strategy, it may occur that data reported in the GSB does not match data reported in the payload in case the data was changed during GSB shift out. In this case, the payload data is the status quo, as it was loaded later into the SPI shift register.

# 5.6 Timings

All SPI related timings are defined in Section 6.4.4: SPI bus (CSN, SCK, SDI, SDO).

# 5.7 Register description

### 5.7.1 Control Register

#### CR#1: Control Register 1

| 23             | 22 | 21     | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10     | 9          | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|----|--------|----|----|----|----|----|----|----|----|----|----|--------|------------|---|---|---|---|---|---|---|---|---|

| CTM_CLK_EN     |    | Unused |    |    |    |    |    |    |    |    |    |    | NNLOCK | Parity bit |   |   |   |   |   |   |   |   |   |

| Address: 0x01h |    |        |    |    |    |    |    |    |    |    |    |    |        |            |   |   |   |   |   |   |   |   |   |

Type: R/W

36/66

| Bit  | Default | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     |