One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### Evaluating the ADuM4138 *i*Coupler, High-Voltage Isolated IGBT Gate Driver with Isolated Flyback Controller

### FEATURES

6 A peak drive output capability Output power device resistance <1 Ω Test infrastructure for SPI communication Miller clamp Desaturation detection Two overcurrent protection pins Two temperature sensor pins Fault reporting Two dummy loads

### **EVALUATION KIT CONTENTS**

EVAL-ADuM4138EBZ evaluation board

### **ADDITIONAL HARDWARE REQUIRED**

Variable power supply up to 20 V and up to 1 A USB-SDP-CABLEZ required for SPI communication

### SUPPORTED iCOUPLER MODELS

#### ADuM4138

### **GENERAL DESCRIPTION**

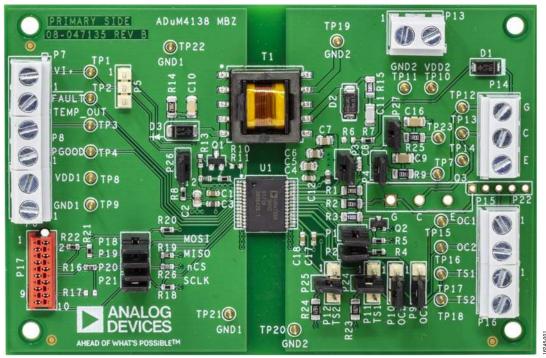

The EVAL-ADuM4138EBZ evaluation board demonstrates the advanced features of the ADuM4138 while maintaining flexibility in a testing environment. The EVAL-ADuM4138EBZ evaluation board layout delivers a circuit that is easy to manipulate via jumper pins. A more optimized layout is possible, which increases the performance of the system as a whole.

The evaluation board works with the USB-SDP-CABLEZ programming cable to access the secondary side electronically erasable programmable read-only memory (EEPROM), and also includes the option to drive the serial peripheral interface (SPI) bus with any other SPI compatible system. The USB-SDP-CABLEZ operates with a 3.3 V logic supply, while the ADuM4138 has an internal 5 V regulator. To allow for interfacing, a resistor divider on the MISO line is included in R21 and R22.

This user guide demonstrates how to use the included ADuM4138 evaluation software for accessing the user trim bits. This user guide shows how to simulate EEPROM settings, as well as program bits into nonvolatile memory.

### **EVALUATION BOARD PHOTOGRAPH**

Figure 1. EVAL-ADuM4138EBZ Evaluation Board

## TABLE OF CONTENTS

| Features                                 |

|------------------------------------------|

| Evaluation Kit Contents1                 |

| Additional Hardware Required 1           |

| Supported <i>i</i> Coupler Models1       |

| General Description 1                    |

| Evaluation Board Photograph1             |

| Revision History 2                       |

| Setting Up the Evaluation Board          |

| Load                                     |

| Power Connections                        |

| Input/Output Connections                 |

| Using SPI 3                              |

| Stock Configuration Fault Overides       |

| Miller Clamp Activation or Deactivation4 |

| GATE_SENSE Pin 4                         |

| Example Propagation Delay Testing 4      |

# EVAL-ADuM4138EBZ User Guide

| Register Descriptions                 | 5    |

|---------------------------------------|------|

| User Trim Register                    | 5    |

| Configuration Trim Register           | 5    |

| Control Register                      | 6    |

| Evaluation Software Description       | 8    |

| Evaluation Software Screenshot        | 8    |

| Software Installation Procedure       | 8    |

| Evaluation Software Example Operation | . 10 |

| When ADuM4138 is not Communicating    | . 10 |

| Example Read Commands                 | . 10 |

| Example EEPROM Write                  | . 11 |

| Evaluation Board Schematic            | . 16 |

| Ordering Information                  | . 17 |

| Bill of Materials                     | . 17 |

### **REVISION HISTORY**

12/2018—Revision 0: Initial Version

## SETTING UP THE EVALUATION BOARD

The EVAL-ADuM4138EBZ evaluation board comes ready to display VI+ to gate operation.

### LOAD

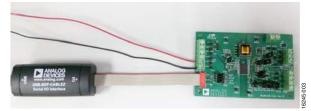

In the stock configuration, two parallel resistor capacitor (RC) loads, a 1  $\Omega$  resistor (R9 or R25) in series with a 100 nF capacitor (C9 or C16) can be jumped in via Jumper P4 and/or Jumper P27.

Figure 2. Simulated IGBT Gate Loads

Removing the P4 and P27 jumpers removes the RC load. Screw terminals and TO-264 through-holes are provided on the evaluation board as methods to connect other loads to the ADuM4138. TP7 and TP23 provide test points to show the simulated internal gate connection within an insulated gate bipolar transistor (IGBT) module that has an integrated 1  $\Omega$  series gate resistor. By jumping P4 or P27, a single RC load can remain.

### **POWER CONNECTIONS**

In the stock configuration, the only power connections required are the  $V_{DD1}$  pin and the GND<sub>1</sub> pin on the ADuM4138. Voltages between 6 V and 25 V are recommended for testing. DC current limits of approximately 1 A are also recommended for up to 20 kHz operation, although lower current limits are acceptable.

### **INPUT/OUTPUT CONNECTIONS**

The VI+ pin can be driven with any 5 V logic or 3.3 V logic push pull complementary metal-oxide semiconductor (CMOS) connection or with an adequate open-drain configuration if the correct pull-up resistor is used. It is recommended to drive the VI+ pin with a 50  $\Omega$  load capable source. If a jumper is in P26, the 50  $\Omega$  load is connected. (Note that the EVAL-ADuM4138EBZ comes configured with a jumper installed in P26.) R8 is a 0603 surface mount device (SMD) resistor that allows 50  $\Omega$  termination.

If a 50  $\Omega$  termination is not used, do not allow the VI+ pin to be driven by a high-Z signal. When not driven, the VI+ pin can be brought to a safe state by jumping Pin 2 and Pin 3 of Jumper P5, which shorts VI+ to GND<sub>1</sub>. If no 50  $\Omega$  termination is used, VI+ can be driven high by jumping Pin 1 and Pin 2 of Jumper P5. Do not jump Pin 1 and Pin 2 of P5 if the P26 jumper is set to have the 50  $\Omega$  termination load present. This configuration sinks the V5 low dropout (LDO) regulator on the primary side.

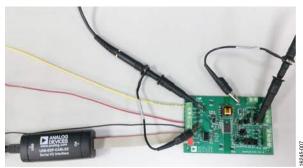

### USING SPI

The ADuM4138 evaluation board interfaces easily with the USB-SDP-CABLEZ cable. When using the SPI bus, place jumpers on P18, P19, P20, and P21. Connect the USB-SDP-CABLEZ to P17. The evaluation board has an indexing hole to ensure proper polarity. If the USB-SDP-CABLEZ system is to be used for SPI communication, refer to the Software Installation Procedure section for more information.

Alternately, any other SPI system can be tested on the evaluation board by connecting cables to the right side of the P18, P19, P20, and P21 jumpers. The pins of the evaluation board are labeled on the silkscreen.

When programming, it is recommended to have Pin 2 and Pin 3 of Jumper P5 shorted to prevent the VI+ pin from affecting the transfer of the gate drive signal. This configuration shorts VI+ to GND<sub>1</sub>.

Figure 3. EVAL-ADuM4138EBZ with USB-SDP-CABLEZ Connected

### STOCK CONFIGURATION FAULT OVERIDES

To present the EVAL-ADuM4138EBZ evaluation board with a simplified test platform, the evaluation board comes configured with fault mode overrides that normally do not exist in the application. These overrides can be removed to evaluate the fault modes, or the user can leave the overrides on the evaluation board to disable the fault condition and focus on other parts of the IC.

### **Desaturation Fault Override**

Jumping P3 shorts the desaturation detection blanking capacitor (C8) to the GND<sub>2</sub> pin, which blocks the desaturation fault from being detected. Removing the jumper on P3 allows the C8 capacitor to be charged via the precision internal 500  $\mu$ A current source if an active IGBT is not connected to the collector pins on the evaluation board. This configuration causes a desaturation fault approximately 6  $\mu$ s after the rising edge of an input signal on the VI+ pin.

### **Overcurrent Fault Overrides**

P9 and P10 provide a way to connect the OC1 pin and the OC2 pin either high or low. The default configuration is to tie the overcurrent pins low by connecting Pin 2 and Pin 3 of Jumper P9 and/or Jumper P10. This connects OC1 to GND<sub>1</sub> and OC2 to GND<sub>2</sub>. If the user want to force an overcurrent fault, connect Pin 1 and Pin 2 of either P9 or P10 to force the overcurrent fault to be read as soon as possible. This method is a simplified approach to seeing the overcurrent blanking time as set by the EEPROM registers.

### Temperature Sense Fault Override

Without remote temperature sensing resistors in place, the TS1 and TS2 pins float high, which produces a low temperature operation mode. To create a middle range voltage on the temperature sense pins, place an approximately 1.8 k $\Omega$  resistor on R23 or R24. These resistors can be removed by jumping P12 and P13 to different pin configurations, or the TS1 and TS2 pins can be fed by a voltage source. Jumper P11 and Jumper P12 are provided to allow the user to quickly tie Pin TS1 or Pin TS2 high or low, effectively railing these pins to make the ADuM4138 sense that the temperature sensor is experiencing a low or high temperature. A third option is to connect to the 1.8 k $\Omega$  resistors to obtain a midrange temperature simulation, as shown in Figure 6.

Figure 4. TS1 and TS2 Pins Jumped High (Low Temperature Simulation)

Figure 5. TS1 and TS2 Pins Jumped Low (High Temperature Simulation)

Figure 6. Midrange Temperature Sense Jumper Configuration

## EVAL-ADuM4138EBZ User Guide

### MILLER CLAMP ACTIVATION OR DEACTIVATION

In the stock configuration, P2 is jumpered. In this configuration, the Miller clamp is able to be operated. Removing the P2 jumper removes the pull-up resistor from the gate of the external Miller clamp metal-oxide semiconductor field effect transistor (MOSFET), which sends a low signal to the Miller clamp constantly, because the MILLER\_OUT pin is open-drain.

### **GATE\_SENSE PIN**

The P1 jumper allows access to connect and disconnect the GATE\_SENSE pin for manipulation testing. The left side of this pin is connected directly to the IC and the right side is connected to the available sensing node of an IGBT module. It is recommended always to leave the P1 jumper connected, unless a specific test is required, for example, testing the Miller clamp activation voltage.

### **EXAMPLE PROPAGATION DELAY TESTING**

From a stock configuration, an example propagation delay testing can be performed. Figure 7 shows one possible configuration. The VI+ pin is driven via a 5 V push-pull CMOS driver referenced to  $GND_1$ . Pin  $V_{DD1}$  is fed with 12 V referenced to  $GND_1$ . The E screw terminal is the emitter connection of the secondary side, which is also the  $GND_2$  pin. For this configuration, it is recommended to remove the USB-SDP-CABLEZ, as well as the P18, P19, P20, and P21 jumpers. If an SPI transmission occurs when the VI+ pin is brought high, the output is blocked. It is possible to perform a test with the USB-SDP-CABLEZ connected to the ADuM4138.

Measuring Test Point TP7 and/or Test Point TP23 simulates what an IGBT with a 1  $\Omega$  internal series gate resistance sees at its gate.

Adding or removing the P2 jumper affects the rising edge propagation delay, because the ADuM4138 senses when it is safe to turn on the main  $V_{OUT_ON}$  driver, based on the Miller MOSFET gate voltage. Do not allow the VI+ pin to be driven by a high-Z signal, which can happen on some function generator models when the output off button is pressed. If the function generator being used has a high-Z when turned off, it is recommended to leave P26 jumpered by placing a 50  $\Omega$  terminating resistor, R8, between VI+ and GND<sub>1</sub>.

Figure 7. Example Propagation Delay Test Setup

### **REGISTER DESCRIPTIONS** USER TRIM REGISTER

#### Table 1. Address 00-User Trim Register Map

| Bits    | Description                  |

|---------|------------------------------|

| [23:18] | TS2 offset                   |

| [17:12] | TS2 gain                     |

| [11:6]  | TS1 offset                   |

| [5:0]   | TS1 gain                     |

|         | [23:18]<br>[17:12]<br>[11:6] |

### OFFSET\_2[5:0]

Internal offset for the Temperature Sense Point 2, TS2, can be adjusted with the OFFSET\_2 field of the EEPROM. There are 6 bits of resolution available.

### GAIN\_2[5:0]

Internal gain for TS2 can be adjusted with the GAIN\_2 field of the EEPROM. 6 bits of resolution are available.

### OFFSET\_1[5:0]

Internal offset for TS1 can be adjusted with the OFFSET\_1 field of the EEPROM. There are 6 bits of resolution available.

### GAIN\_1[5:0]

Internal gain for TS1 can be adjusted with the GAIN\_1 field of the EEPROM. 6 bits of resolution are available.

### **CONFIGURATION TRIM REGISTER**

#### Table 2. Address 01—Configuration Trim Register Map

| Field        | Bits    | Description                                                    |

|--------------|---------|----------------------------------------------------------------|

| Reserved     | [23:17] | Reserved                                                       |

| OT_Fault_OP  | 16      | Overtemperature fault disable                                  |

| OT_fault_Sel | 15      | Overtemperature fault select                                   |

| OC_TIME_OP   | 14      | Disable two-level drive and timer<br>during overcurrent event  |

| OC_2Lev_OP   | 13      | Overcurrent two-level operation select                         |

| Low_T_OP     | 12      | Low temperature operation select                               |

| OC_Blank_OP  | 11      | Overcurrent blanking operation select                          |

| tblank       | [10:7]  | Overcurrent blanking time                                      |

| ECC_OFF_OP   | 6       | Enable soft shutdown with error<br>correcting code (ECC) fault |

| Flyback_V    | [5:2]   | Flyback output voltage setting                                 |

| T_ramp_OP    | 1       | Overcurrent temperature ramp enable                            |

| PWM_OSC      | 0       | Temperature reading output oscillator select                   |

### OT\_Fault\_OP

Set OT\_Fault\_OP to 1 to disable a fault for over temperature. If set to 0, the ADuM4138 issues a fault if the TS1 pin detects an overtemperature event.

### OT\_Fault\_Sel

OT\_Fault\_Sel selects between two overtemperature fault voltage thresholds. Selecting 0 sets the falling threshold to 1.64 V (typical) and the rising threshold to 1.68 V (typical). Setting the OT\_Fault\_SELF bit to 1 sets the falling threshold to 1.68 V (typical) and the rising threshold to 1.72 V (typical).

### OC\_TIME\_OP

Set OC\_TIME\_OP to 1 to disable two-level drive and timer during an overcurrent event. During an overcurrent event, the output enters soft shutdown immediately. Blanking is still available.

### OC\_2Lev\_OP

Set OC\_2Lev\_OP to 1 to disable two-level drive during an overcurrent event before a fault is registered. After the overcurrent detection time is complete, a fault is registered, and the output shuts down using the soft shutdown. If set to 0 during an overcurrent event, but before td\_OC, the two-level drive level is output to the gate.

### Low\_T\_OP

A special low temperature operation can be disabled in Bit 12 of the configuration trim register. If Low\_T\_OP is set to 0, when the sensed IGBT temperature is below  $-20^{\circ}$ C, the gate voltage rises to the two level plateau voltage during an on command. Hysteresis allows for operation up to  $-20^{\circ}$ C before the low temperature operation mode is left. If Low\_T\_OP is set to 1, all nonfault gate signals are at the VDD2 output voltage on an on signal.

### OC\_Blank\_OP

Set OC\_Blank\_OP to 1 to enable two-level drive during current blanking time. If OC\_Blank\_OP is set to 1, two-level drive is entered in the case of an overcurrent event during the tblank blanking time.

### tblank[3:0]

During the initial turn on of a gate, there can exist a large amount of noise caused by switching actions. To account for this, the overcurrent detection can be masked by setting different tblank values. During the masking time, overcurrent events are ignored.

### Table 3. td\_OC Blanking Times

| Table 5. td_OC Blankin | g Times            |

|------------------------|--------------------|

| tblank[10:7]           | Blanking time (μs) |

| 0000                   | 0                  |

| 0001                   | 0.4                |

| 0010                   | 0.6                |

| 0011                   | 0.8                |

| 0100                   | 1.0                |

| 0101                   | 1.2                |

| 0110                   | 1.6                |

| 0111                   | 2.0                |

| 1000                   | 2.4                |

| 1001                   | 2.8                |

| 1010                   | 3.2                |

| 1011                   | 3.6                |

| 1100                   | 4.0                |

| 1101                   | 4.4                |

| 1110                   | 4.8                |

| 1111                   | 6.0                |

### ECC\_OFF\_OP

If set to 1, when an ECC error is detected, the device enters a soft shutdown, and a fault is registered. This fault is registered whether a single or double ECC fault is detected. If set to 0, ECC faults are still set in the control register (Address 10), but the part continues to operate without shutting down.

### Flyback\_V[3:0]

The isolated flyback output voltage can be set by the Flyback\_V bits in the EEPROM. The default code is 0111 (16.00 V target). Table 4 shows the available output voltages.

#### Table 4. EEPROM Register Map

| Flyback_V[5:2] | VDD2 Voltage Setting (V) |

|----------------|--------------------------|

| 0000           | 14.25                    |

| 0001           | 14.50                    |

| 0010           | 14.75                    |

| 0011           | 15.00                    |

| 0100           | 15.25                    |

| 0101           | 15.50                    |

| 0110           | 15.75                    |

| 0111 (Default) | 16.00                    |

| 1000           | 16.25                    |

| 1001           | 16.50                    |

| 1010           | 16.75                    |

| 1011           | 17.00                    |

| 1100           | 17.25                    |

| 1101           | 17.50                    |

| 1110           | 17.75                    |

| 1111           | 20.00                    |

## EVAL-ADuM4138EBZ User Guide

### T\_Ramp\_OP

Set to 0 to allow the over current reference voltage to vary with temperature. The current reference varies by 10% across  $-40^{\circ}$ C to  $+175^{\circ}$ C. Set to 1 to have the overcurrent reference voltage set to 2 V (typical) regardless of sensed temperature.

#### PWM\_OSC

The PWM\_OSC bit controls whether the reported TEMP\_OUT pin pulse-width modulation (PWM) frequency is 10 kHz or 50 kHz. When PWM\_OSC is set to 0, the output frequency is 10 kHz (typical). When PWM\_OSC is set to 1, the PWM output frequency is 50 kHz (typical).

### **CONTROL REGISTER**

| Bits | Description                      |

|------|----------------------------------|

| 23:6 | Reserved                         |

| 5    | ECC Bank 2 double error detected |

| 4    | ECC Bank 2 single error detected |

| 3    | ECC Bank 1 double error detected |

| 2    | ECC Bank 1 single error detected |

| 1    | Program/busy bit                 |

| 0    | Simulate trim                    |

|      | 23:6<br>5<br>4<br>3<br>2<br>1    |

### ECC2\_DBL\_ERR

If two errors are detected in the EEPROM stored data, the ECC2\_DBL\_ERR bit is set to 1 when read. Two errors are detectable, but uncorrectable using the ECC employed by the ADuM4138. ECC2\_DBL\_ERR shows that a double error is detected in the memory banks representing trim performed on the parts outside of registers affected by the user trim address and the configuration trim address. A value of 0 means no error is detected.

### ECC2\_SNG\_ERR

If a single error is detected in the EEPROM stored data, the ECC2\_SNG\_ERR bit is set to 1 when read. A single error can be detected and corrected using the ECC employed by the ADuM4138. ECC2\_SNG\_ERR shows that a single error is detected in the memory banks representing trim performed on the parts outside of registers affected by the user trim address and the configuration trim address. A value of 0 means no error is detected.

### ECC1\_DBL\_ERR

If two errors are detected in the EEPROM stored data, the ECC1\_DBL\_ERR bit is set to 1 when read. Two errors are detectable, but uncorrectable using the ECC employed by the ADuM4138. ECC1\_DBL\_ERR shows that a double error is detected in the memory banks representing trim performed on the parts by the user trim address and the configuration trim address. A value of 0 means no error is detected.

### ECC1\_SNG\_ERR

If a single error is detected in the EEPROM stored data, the ECC1\_SNG\_ERR bit is set to 1 when read. A single error can be detected and corrected using the error correcting code employed by the ADuM4138. ECC1\_SNG\_ERR shows that a single error is detected in the memory banks representing trim performed on the parts by the user trim address and the configuration trim address. A value of 0 means no error is detected.

### Prog\_Busy

Set this bit high in order to program the EEPROM memory. When this bit is set to 1, the EEPROM begins to write to memory. The hardware sets this bit back to 0 to indicate that programming has occurred. The write sequence takes a maximum of 40 ms (maximum) to perform, but may write faster than 40 ms (maximum). If shorter wait times are desired, the Prog\_Busy bit can be read back multiple times during the writing time. If a 0 is read back after the user sets the bit to 1, the writing is complete.

### Sim\_Trim

If Sim\_Trim is set to 0, the user trim and configuration trim registers have no effect. Use this bit to simulate trim settings without writing to the registers.

## **EVALUATION SOFTWARE DESCRIPTION**

### **EVALUATION SOFTWARE SCREENSHOT**

| ADuM4138_eval_program_01        | vi                                                                                                                                                                                                | x |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| sclkFrequency<br>200000<br>STOP |                                                                                                                                                                                                   |   |

| Write/Read Addr:00              | OFFSET_2         GAIN_2         OFFSET_1         GAIN_1           b 000000         b 000000         b 000000         b 000000         b 000000           d ddr:00 Bits to Send         x 40000000 |   |

|                                 | Read Addr:00         Addr:00 Output         b 000000000000000000000000000000000000                                                                                                                |   |

| Write/Read Addr:01              | OT_Fault_OP OT_Fault_Sel OC_TIME_OP OC_2Lev_OP Low_T_OP OC_Blank_OP tBLANK                                                                                                                        | ] |

|                                 | ECC_OFF_OP Flyback_V T_ramp_OP PWM_OSC                                                                                                                                                            |   |

| Write/Read Addr:10              | Prog_Busy         Sim_Trim           0         0           0         0           Addr.10 Bits to Send         × 60000000                                                                          |   |

|                                 | Read Addr:10 Addr:10 Output 60010000000000000000000000000000000000                                                                                                                                |   |

|                                 | Sim_Tim<br>Prog_Busy<br>ECC1_DBL_ERR<br>ECC2_DBL_ERR<br>ECC2_DBL_ERR                                                                                                                              |   |

Figure 8. Evaluation Software Screenshot

### SOFTWARE INSTALLATION PROCEDURE

To use the USB-SDP-CABLEZ for SPI communication, a LabVIEW executable is available. The LabVIEW executable requires that the USB-SDP-CABLEZ drivers be installed, and that a LabVIEW runtime engine compatible with LabVIEW 2011 is available.

- 1. Install SDPdrivers.exe (available from Analog Devices).

- 2. Install LabVIEW Runtime Engine 2011 or later (available from National Instruments).

- 3. Double-click ADuM4138\_eval\_progam\_01.exe to run.

### STOP

Click **STOP** to halt the LabVIEW program. Alternate methods of stopping the program are to close the window, or force quit the program. All of these options set the  $\overline{CS}$  pin to an unknown state, so it is recommended to remove the USB-SDP-CABLEZ connection from the evaluation board before shutting the program down.

### Read Addr:00

Click **Read Addr:00** to see what the ADuM4138 has in the EEPROM at Address 00 (user trim bits). Clicking **Read Addr:00** sends two read commands. This is because of the way that the SPI setup operates. The second read command pushes the data loaded by the first read command to the MISO pin. The result of the second read appears in the **Addr:00 Output** field.

3245-008

### Read Addr:01

Click **Read Addr:01** to see what the ADuM4138 has in the EEPROM at Address 01 (configuration trim bits). Clicking **Read Addr:01** sends two read commands. This is because of the way that the SPI setup operates. The second read command pushes the data loaded by the first read command to the MISO pin. The result of the second read appears in the **Addr:01 Output** field.

### Read Addr:10

Click **Read Addr:10** to see what the ADuM4138 has in the EEPROM at Address 10 (control bits). Clicking **Read Addr:10** sends two read commands. This is because of the way that the SPI setup operates. The second read command pushes the data loaded by the first read command to the MISO pin. The result of the second read appears in the **Addr:10 Output** field.

### Write/Read Addr:00

Click **Write/Read Addr:00** to perform a single write comprised of the bit pattern set by the user in the **OFFSET\_2** field, the **GAIN\_2** field, the **OFFSET\_1** field, and the **GAIN\_1** field. After the single write, a single read is performed, allowing the user to verify that the sequence is sent. The result of this read is

sent to the **Addr:00 Output** field. If the Sim\_Trim bit at Address 10 is set to 1, the write affects the operation of the ADuM4138 with the new settings written by the user. The Sim\_Trim bit is set to 0 until the device is powered down, or until new settings are written.

### Write/Read Addr:01

Click **Write/Read Addr:01** to perform a single write comprised of the bit pattern set by the user in the OC\_2Lev\_OP field, the Low\_T\_OP field, the OC\_Blank\_OP field, the td\_OC field, the Flyback\_V field, the T\_ramp\_OP field, and the PWM\_OSC field. After the single write, a single read is performed, allowing the user to verify that the sequence is sent. The result of this read is sent to the Addr:01 Output field. If the Sim\_Trim bit at Address 10 is set to 1, the write affects the operation of the ADuM4138 with the new settings written by the user. The Sim\_Trim bit is set to 0 until the device is powered down, or until new settings are written.

### Write/Read Addr:10

Click **Write/Read Addr:10** to perform a single write comprised of the bit pattern set by the user in the **Prog Busy** field and the **Sim Trim** field. After the single write, a single read is performed, allowing the user to verify that the sequence is sent. The result of this read is sent to the **Addr:10 Output** field. If Sim\_Trim is set to 1, and then Prog\_Busy is set to 1, values written to the **ADuM4138** using **Write/Read Addr:00** and **Write/Read Addr:01** are written to EEPROM and are loaded on the next power up. These can be verified with an address read after a power up.

### sclkFrequency

This field is used to change the operating frequency of the SPI clocking. The field is set in hertz, and 200 kHz is the default and maximum value.

## **EVALUATION SOFTWARE EXAMPLE OPERATION**

These examples assume that the setup described in the Setting Up the Evaluation Board section is used.

### WHEN ADUM4138 IS NOT COMMUNICATING

If the ADuM4138 is not powered, and the USB-SDP-CABLEZ is plugged into the evaluation board, read commands usually report all 0s. By reading all registers, it is possible to see if the ADuM4138 is communicating properly, as the address bits are displayed on a read command. Additionally, with default settings, the Flyback\_V setting is 111 (see Figure 9).

### **EXAMPLE READ COMMANDS**

To perform a read command, first power up the ADuM4138. Then click the read button of the desired address to be read. If the ADuM4138 EEPROM has never been programmed, it is expected that all 0s except the address are returned, and a Flyback\_V setting of 111 in default configuration. Figure 10 shows **Read Addr:00**, **Read Addr:01**, and **Read Addr:10** clicked on a new ADuM4138.

| ADuM4138_eval_program_0:<br>sclkFrequency<br>200000 | 1.vi       |        |            |                      |                   |                     |                      |                             |                                         |                                         |   |

|-----------------------------------------------------|------------|--------|------------|----------------------|-------------------|---------------------|----------------------|-----------------------------|-----------------------------------------|-----------------------------------------|---|

| STOP<br>Write/Read Addr:00                          |            |        |            | OFFSET_2<br>6 000000 | GAIN_2<br>6000000 | OFFSET_<br>6 000000 |                      | 6 010000000<br>Addr:00 Bits |                                         | 00000000000000000000000000000000000000  |   |

|                                                     |            |        |            |                      | Read Ad           | dr:00               | Addr:00 Output       | 6 000000000                 | 000000000000000000000000000000000000000 | 000000000000000000000000000000000000000 | ] |

| Write/Read Addr:01                                  | ECC_OFF_OP | Enable | OC_TIME_OP | Enable               | Enable            | OC_Blank_C          | Ø 0 µs               | Addr:01 Bits                | to Send                                 | 0000000011100<br>× 5000001C             |   |

| Write/Read Addr:10                                  | ) Enable   | 16.00  | Enable     | 10 kHz               | Read A            |                     | Addr:01 Output       | €                           | 000000000000000000000000000000000000000 | 00000000000000000000000000000000000000  |   |

|                                                     |            |        |            | (                    | Read Ad           | idr:10              | Lange Addr:10 Output | ► 000000000                 |                                         |                                         | ] |

|                                                     |            |        |            |                      |                   |                     |                      |                             | ECC2_SNG_ERR<br>ECC2_DBL_ERR            | Sim_Trim<br>Prog_Busy<br>ECC1_SNG_ERR   |   |

Figure 9. All Zeros Show Communication is Not Occurring

| ADuM4138_eval_program_01.vi     |                             |                             |                                                                         |

|---------------------------------|-----------------------------|-----------------------------|-------------------------------------------------------------------------|

| sclkFrequency<br>200000<br>STOP |                             |                             |                                                                         |

| Write/Read Addr:00              | OFFSET_2                    | GAIN_2 OFFSET_1 GAIN_1      | 6 0100000000000000000000000000000000000                                 |

|                                 | [                           | Read Addr:00 Addr:00 Output | b 000000000000000000000000000000000000                                  |

| Write/Read Addr:01              |                             | Low_T_OP OC_Blank_OP tBLANK | b 0101000000000000000000000000011100<br>Addr:01 Bits to Send x 5000001C |

| ECC_OFF_OP                      | Flyback_V T_ramp_OP PWM_OSC | Read Addr:01 Addr:01 Output | ▶ 0001000000000000000000000000000000000                                 |

| Write/Read Addr:10              |                             | Prog_Busy Sim_Trim          | b 0110000000000000000000000000000000000                                 |

|                                 |                             | Read Addr:10 Addr:10 Output | • 001000000000000000000000000000000                                     |

|                                 |                             |                             | ERR R                                                                   |

Figure 10. Address Bits Are Being Read Back

### **EXAMPLE EEPROM WRITE**

To write data to the EEPROM, the Sim\_Trim bit must first be set. Set this bit by selecting 1 in the **Sim Trim** field, and clicking **Write/Read Addr:10**. This setting results in the **Sim\_Trim** green indicator lighting up (see Figure 11).

When the Sim\_Trim bit is set to 1, write commands to Address 00 or Address 01 affect the operation of the ADuM4138.

The next step to programming the EEPROM is to set the desired bits in Address 00 and Address 01. In this example, Bit 0 of the GAIN\_1 field is set to 1. When it is set to 1, clicking Write/Read Addr:00 results in the Addr:00 Output field showing that the value was written to the register. At this time,

the GAIN\_1 EEPROM register is not yet programmed. Note that **Sim\_Trim** is still 1 (see Figure 12).

6245-010

To write Address 00 data to EEPROM, set the **Prog Busy** field to 1, and click **Write/Read Addr:10** (see Figure 13).

The write/read button performs a write and then a read as normal. The **Prog\_Busy** green indicator is usually lit up. This state is because the read command occurs quickly after the write, and the Prog\_Busy bit in the ADuM4138 is 1 while the device is being programmed. Click **Read Addr:10** after this programming, and once the Prog\_Busy bit changes to 0, the EEPROM is programmed. The programming takes approximately 10 µs; therefore, a human user generally cannot click the read button fast enough to see a 1 in the **Prog Busy** field the second time, but an automated program might (see Figure 14). UG-1194

EVAL-ADuM4138EBZ User Guide

| ADuM4138_eval_program_0                          | 1.vi          |                                  |                                      |                                             |                                                                                  |                                                                                           |

|--------------------------------------------------|---------------|----------------------------------|--------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| clkFrequency                                     |               |                                  |                                      |                                             |                                                                                  | Ľ                                                                                         |

| 200000                                           |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

| STOP                                             |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

| Write/Read Addr:00                               |               |                                  | OFFSET                               | 2 GAIN_2 OF                                 | FSET_1 GAIN_1                                                                    |                                                                                           |

|                                                  |               |                                  | 6 00000C                             |                                             | 00000 600000                                                                     | b 0100000000000000000000000000000000000                                                   |

|                                                  |               |                                  |                                      |                                             |                                                                                  | Addr:00 Bits to Send ×40000000                                                            |

|                                                  |               |                                  |                                      | Deed Add-00                                 |                                                                                  | t b 00000000000000000000000000000000000                                                   |

|                                                  |               |                                  |                                      | Read Addr:00                                | Addr:00 Outpu                                                                    | [                                                                                         |

|                                                  |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

| Write/Read Addr:01                               | 3             | OT_Fault_Sel OC_TIME_(           |                                      |                                             | ank_OP tBLANK                                                                    |                                                                                           |

|                                                  | Enable        | 🕀 Enable 🕀 Enable                | Enable                               | 💮 Enable 💮 En                               | able 🕖 0 µs                                                                      | b 0101000000000000000000000011100<br>Addr:01 Bits to Send × 5000001C                      |

|                                                  | ECC_OFF_OP    | Flyback_V T_ramp_                | OP PWM_OSC                           |                                             |                                                                                  | Addrof bits to send                                                                       |

|                                                  | Enable        | () 16.00 () Enabl                |                                      | Read Addr:01                                | Addr:01 Outpu                                                                    | t b 00000000000000000000000000000000000                                                   |

|                                                  |               | a) a)                            | Ψ                                    |                                             |                                                                                  |                                                                                           |

| Write/Read Addr:10                               | 7             |                                  |                                      | Prog_Busy                                   | Sim_Trim                                                                         |                                                                                           |

|                                                  |               |                                  |                                      | 0                                           |                                                                                  | b 0110000000000000000000000000000000000                                                   |

|                                                  |               |                                  |                                      |                                             |                                                                                  | Addr:10 Bits to Send ×60000001                                                            |

|                                                  |               |                                  |                                      | <u></u>                                     |                                                                                  | ~~~                                                                                       |

|                                                  |               |                                  |                                      | Read Addr:10                                | Addr:10 Outpu                                                                    | t b 0110800000000000000000000000000000000                                                 |

|                                                  |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

|                                                  |               |                                  |                                      |                                             |                                                                                  | Nim_Trim<br>Prog_Busy<br>ECC1_SNG_ERF<br>ECC2_SNG_ERF<br>ECC2_DBL_ERR                     |

|                                                  |               |                                  |                                      |                                             |                                                                                  | m_Trim<br>rog_Busy<br>ccl_SNG_ERR<br>ccl_DBL_ERR<br>rc2_SNG_ERR<br>cc2_DBL_ERR            |

|                                                  |               |                                  |                                      |                                             |                                                                                  | ERR<br>ERR                                                                                |

|                                                  |               |                                  |                                      |                                             | 01:                                                                              |                                                                                           |

|                                                  |               | Figi                             | ure 11. Setti                        | ng the Sim_Trin                             | n Bit                                                                            |                                                                                           |

| ADuM4138_eval_program_0.                         | 1.vi          |                                  |                                      |                                             |                                                                                  |                                                                                           |

| clkFrequency                                     |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

|                                                  |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

|                                                  |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

| 200000<br>STOP                                   |               |                                  |                                      |                                             |                                                                                  |                                                                                           |

|                                                  | $\overline{}$ |                                  | OFFSET_                              | 2 GAIN_2 OF                                 | FSET_1 GAIN_1                                                                    | L 0100000000000000000000000000000000000                                                   |

| STOP                                             | >             |                                  | OFFSET_<br>6 000000                  | -                                           | FSET_1 GAIN_1<br>00000 b000001                                                   | b 0100000000000000000000000000000000000                                                   |

| STOP                                             | >             |                                  |                                      | -                                           |                                                                                  | b 0100000000000000000000000000000000000                                                   |

| STOP                                             | >             |                                  |                                      | -                                           | 00000 b 000001                                                                   | Addr:00 Bits to Send × 40000001                                                           |

| STOP                                             | >             |                                  |                                      | b 000000 b 0                                | 00000 b 000001                                                                   |                                                                                           |

| STOP                                             | >             |                                  | P 000000                             | b 000000 b 0                                | 00000 b 000001                                                                   | Addr:00 Bits to Send ×40000001                                                            |

| STOP<br>Write/Read Addr:00                       | 2             | OT_Fault_Sel OC_TIME_C           | 6 000000                             | Read Addr:00                                | 00000 b 000001                                                                   | Addr:00 Bits to Send ×40000001                                                            |

| STOP                                             | 2             | OT_Fault_Sel OC_TIME_<br>DEnable | 6 000000                             | b 000000 b 0                                | 00000 b 000001                                                                   | Addr:00 Bits to Send ×40000001                                                            |

| STOP<br>Write/Read Addr:00                       | Enable        | ) Enable                         | b 000000<br>DP OC_2Lev_O<br>Enable   | Read Addr:00<br>P Low_T_OP OC_BI            | 00000 b 000001                                                                   | Addr:00 Bits to Send ×40000001                                                            |

| STOP<br>Write/Read Addr:00                       | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | Read Addr:00<br>P Low_T_OP OC_BI            | 00000 b 000001<br>Addr:00 Output                                                 | Addr:00 Bits to Send         × 40000001           b 0100000000000000000000000000000000000 |

| STOP<br>Write/Read Addr:00                       | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | Read Addr:00<br>P Low_T_OP OC_BI<br>DEnable | 00000 b 000001<br>Addr:00 Output                                                 | Addr:00 Bits to Send ×40000001                                                            |

| STOP<br>Write/Read Addr:00                       | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | Addr:00 Output                                                                   | Addr:00 Bits to Send       × 40000001         b 0100000000000000000000000000000000000     |

| STOP<br>Write/Read Addr:00<br>Write/Read Addr:01 | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | 00000 b 000001<br>Addr:00 Output                                                 | Addr:00 Bits to Send       x 40000001         b 0100000000000000000000000000000000000     |

| STOP<br>Write/Read Addr:00<br>Write/Read Addr:01 | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | 00000 b 000001<br>Addr:00 Output<br>ank_OP tBLANK<br>able 0 μs<br>Addr:01 Output | Addr:00 Bits to Send       × 40000001         b 0100000000000000000000000000000000000     |

| STOP<br>Write/Read Addr:00<br>Write/Read Addr:01 | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | Addr:00 Outpur                                                                   | Addr:00 Bits to Send         × 40000001           b 0100000000000000000000000000000000000 |

| Write/Read Addr:00                               | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | Addr:00 Outpur                                                                   | Addr:00 Bits to Send       x 40000001         b 0100000000000000000000000000000000000     |

| STOP<br>Write/Read Addr:00<br>Write/Read Addr:01 | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | Addr:00 Outpur                                                                   | Addr:00 Bits to Send       × 40000001         b 0100000000000000000000000000000000000     |

| STOP<br>Write/Read Addr:00<br>Write/Read Addr:01 | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | Addr:00 Outpur                                                                   | Addr:00 Bits to Send       × 40000001         b 0100000000000000000000000000000000000     |

| STOP<br>Write/Read Addr:00<br>Write/Read Addr:01 | Enable        | Flyback_V T_ramp_                | DP OC_2Lev_O<br>Enable<br>OP PWM_OSC | P Low_T_OP OC_BI                            | Addr:00 Outpur                                                                   | Addr:00 Bits to Send         × 40000001           b 0100000000000000000000000000000000000 |

Figure 12. Writing Example Register Edit

| ADuM4138_eval_program_01<br>sclkFrequency<br>200000<br>STOP |          |                |                      |                    |                      |                    |                                         |                          |

|-------------------------------------------------------------|----------|----------------|----------------------|--------------------|----------------------|--------------------|-----------------------------------------|--------------------------|

| Write/Read Addr:00                                          |          |                | OFFSET_2<br>6 000000 | GAIN_2<br>6 000000 | OFFSET_1<br>6 000000 | GAIN_1<br>6 000001 | 6 0100000000000000000000000000000000000 | 00000000001<br>×40000001 |

|                                                             |          |                | Ì                    | Read Ad            | ldr:00               | Addr:00 Output     | b 0100000000000000000000000000000000000 | 00000000001              |

| Write/Read Addr:01                                          | ) Enable | ck_V T_ramp_OP |                      | Low_T_OP           | OC_Blank_OF          | () 0 µs            | b 0101000000000000000000000000000000000 | × 5000001C               |

| Write/Read Addr:10                                          | >        |                |                      | Prog               | g_Busy_Sim           | Trim               | 6 0110000000000000000000000000000000000 | 00000000011  ×60000003   |

|                                                             |          |                | (                    | Read Add           | <b>∟</b><br>dr.10 /  | Addr:10 Output     | b0110000000000000000000000000000000     |                          |

Figure 13. Programming EEPROM

| Frequency<br>1000<br>STOP |          |        |        |                      |                    |                      |                               |                                         |                                                                                             |

|---------------------------|----------|--------|--------|----------------------|--------------------|----------------------|-------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|

| Write/Read Addr:00        |          |        |        | OFFSET_2<br>6 000000 | GAIN_2<br>6 000000 | OFFSET_1<br>6 000000 | GAIN_1<br>6000001             | b 0100000000000000000000000000000000000 | 0000000000001<br>× 40000001                                                                 |

|                           |          |        |        | ĺ                    | Read A             | ddr:00               | Addr:00 Output                | b 0100000000000000000000000000000000000 | 000000000000000000000000000000000000000                                                     |

| Write/Read Addr:01        |          | Enable |        | OC_2Lev_OP           | Low_T_OP           | OC_Blank_O           | <sup>2</sup> tBLANK<br>θ θ μs | 6 0101000000000000000000000000000000000 | 0000000011100<br>×5000001C                                                                  |

| Write/Read Addr:10        | ) Enable | 16.00  | Enable | 10 kHz               | Read A             | g_Busy Sim           | _Trim                         | b 000000000000000000000000000000000000  | 1                                                                                           |

|                           |          |        |        | $\mathcal{C}$        | Read Ad            | )1<br>dr:10          | Add:10 Output                 | Addr:10 Bits to Send                    | × 60000003                                                                                  |

|                           |          |        |        |                      |                    |                      |                               |                                         | <ul> <li>Sim_Trim</li> <li>Prog_Busy</li> <li>ECC1_SNG_ERR</li> <li>ECC1_DBL_ERR</li> </ul> |

Figure 14. ADuM4138 Showing Programming Complete

# UG-1194

## UG-1194

After Prog\_Busy reads 0, the EEPROM is programmed. Verify this programming by powering down the ADuM4138 and clicking **Read Addr:00**. Expect to receive all 0s back, because the ADuM4138 is unpowered. This read is so that the next read is easier to see. The other read buttons can also be clicked, but it is not necessary. Figure 15 shows all read buttons clicked while the ADuM4138 is off. Now power up the ADuM4138, and click all the read buttons. It can then be seen that Bit 0 of GAIN\_1 survives a power-up, indicating that the EEPROM is programmed. The same steps can be performed with the GAIN\_1 field set to 0 to return the EEPROM to its original programmed state, if desired (see Figure 16).

| ADuM4138_eval_program_01       | vi         |                                                                |                      |                    |                      |                     |                                                                                       |

|--------------------------------|------------|----------------------------------------------------------------|----------------------|--------------------|----------------------|---------------------|---------------------------------------------------------------------------------------|

| clkFrequency<br>200000<br>STOP |            |                                                                |                      |                    |                      |                     |                                                                                       |

| Write/Read Addr:00             |            |                                                                | OFFSET_2<br>6 000000 | GAIN_2<br>6 000000 | OFFSET_1<br>6 000000 | GAIN_1<br>6 000000  | b 0100000000000000000000000000000000000                                               |

|                                |            |                                                                | Ĵ                    | Read Add           | Ir:00 A              | ⊥<br>Addr:00 Output | ► 000000000000000000000000000000000000                                                |

| Write/Read Addr:01             | 🖞 Enable 🖞 | T_Fault_Sel OC_TIME_OP<br>Enable Enable<br>Flyback_V T_ramp_OP | OC_2Lev_OP           |                    | OC_Blank_OP          | b tBLANK            | b 0101000000000000000000000000000000000                                               |

|                                |            | 16.00 DEnable                                                  | 10 kHz               | Read Add           | dr:01 A              | Addr:01 Output      | ► 000000000000000000000000000000000000                                                |

| Write/Read Addr:10             |            |                                                                |                      |                    | Busy Sim             |                     | b 0110000000000000000000000000000000000                                               |

|                                |            |                                                                | (                    | Read Add           | r:10 A               | Addr:10 Output      | A                                                                                     |

|                                |            |                                                                |                      |                    |                      |                     | Sim_Trim<br>Prog_Busy<br>ECC1_SNG_ERR<br>ECC2_SNG_ERR<br>ECC2_DBL_ERR<br>ECC2_DBL_ERR |

Figure 15. Unpowered Reads

| ADuM4138_eval_program_0        | Lvi                                                                                                     |

|--------------------------------|---------------------------------------------------------------------------------------------------------|

| clkFrequency<br>200000<br>STOP |                                                                                                         |

| Write/Read Addr:00             | OFFSET_2         GAIN_2         OFFSET_1         GAIN_1         b 0100000000000000000000000000000000000 |

|                                | Read Addr:00         Addr:00 Output         6000000000000000000000000000000000000                       |

| Write/Read Addr:01             | OT_Fault_OP OT_Fault_Sel OC_TIME_OP OC_2Lev_OP Low_T_OP OC_Blank_OP tBLANK                              |

|                                | ECC_OFF_OP Flyback_V T_ramp_OP PWM_OSC                                                                  |

| Write/Read Addr:10             | Prog_Busy         Sim_Trim         b 0110000000000000000000000000000000000                              |

|                                | Read Addr:10         Addr:10         Output         b 0010000000000000000000000000000000000             |

|                                | Sim_Trim<br>Prog_Busy<br>ECC_DBL_ERR<br>ECC2_DBL_ERR                                                    |

Figure 16. EEPROM Successfully Written

UG-1194

16245-017

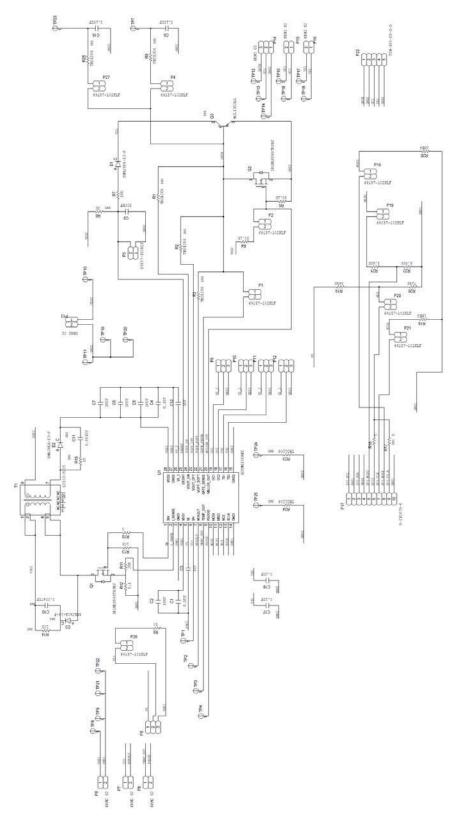

## **EVALUATION BOARD SCHEMATIC**

Figure 17. EVAL-ADuM4138EBZ Circuit Schematic

## **ORDERING INFORMATION**

### **BILL OF MATERIALS**

Table 6.

| Reference Designator | Description                                    | Part Number        | Supplier             |

|----------------------|------------------------------------------------|--------------------|----------------------|

| C1, C4, C17, C18     | 0.1 μF ceramic capacitor, 50 V, X7R 0603       | GRM188R71H104JA93D | Murata               |

| C10                  | 0.0047 μF ceramic capacitor, 50 V, X7R 1206    | CC1206KRX7R9BB472  | Yageo                |

| C11                  | 0.001 μF ceramic capacitor, 50 V, NP0 1206     | 12061A102JAT2A     | AVX                  |

| C2                   | 10 μF ceramic capacitor, 25 V, X5R 0805        | GRM21BR61E106KA73L | Murata               |

| C3, C12              | 1 μF ceramic capacitor, 25 V, X7R 0603         | GRM188R71A105KA61D | Murata               |

| C5, C6, C7           | 22 μF ceramic capacitor, 25 V, X5R 0805        | GRT21BR61E226ME13L | Murata               |

| C8                   | 300 pF ceramic capacitor, 50 V, C0G (NP0) 0603 | GRM1885C1H301JA01D | Murata               |

| C9, C16              | 0.1 μF ceramic capacitor, 25 V, X7R 1206       | CC1206KRX7R9BB104  | Yageo                |

| D1                   | Diode, ultrafast rectifier                     | US1M-E3/61T        | Vishay               |

| D2                   | Diode, SMT ultrafast power rectifier           | MURA140T3G         | Murata               |

| D3                   | Diode, ultrafast plastic rectifier, 1 A        | ES1D-E3/61T        | Vishay               |

| P17                  | 10-pin system demonstration platform (SDP)     | 8-215079-0         | TE Connectivity LTD  |

| P17 (alternate)      | WR-MM female connector                         | 690367181072       | Wurth Electronics    |

| Q1                   | Transistor, HEXFET power MOSFET                | IRLML0060TRPBF     | Infineon             |

| Q2                   | Transistor, N-channel HEXFET power MOSFET      | IRLML2030TRPBF     | Infineon             |

| R1                   | 2 Ω resistor, 1206                             | ERJ-8RQF2R0V       | Panasonic            |

| R10                  | 20 Ω resistor, 0603                            | P0603E20R0BBT      | Vishay               |

| R11                  | 20 kΩ resistor, 0603                           | ERJ-3EKF2002V      | Panasonic            |

| R12                  | 0.1 Ω resistor, 0603                           | ERJ-3RSFR10V       | Panasonic            |

| R13, R19             | 10 kΩ resistor, 0603                           | ERJ-3EKF1002V      | Panasonic            |

| R14                  | 20 kΩ resistor, 1206                           | ERJ-8ENF2002V      | Panasonic            |

| R15                  | 10 Ω resistor, 1206                            | ERJ-8ENF10R0V      | Panasonic            |

| R16                  | 0 Ω resistor, 0603                             | ERJ-3GEY0R00V      | Panasonic            |

| R18, R20             | 1 MΩ resistor, 0603                            | ERJ-3EKF1004V      | Panasonic            |

| R2, R9, R25          | 1 Ω resistor, 1206                             | ERJ-8RQF1R0V       | Panasonic            |

| R21                  | 3.48 kΩ resistor, 0603                         | ERJ-3EKF3481V      | Panasonic            |

| R22                  | 6.98 kΩ resistor, 0603                         | ERJ-3EKF6981V      | Panasonic            |

| R23, R24             | 1.82 kΩ resistor, 1206                         | RC1206FR-071K82L   | Yageo                |

| R26                  | 20 kΩ resistor, 0603                           | ERJ-3GEYJ203V      | Panasonic            |

| R3                   | 100 Ω resistor, 1206                           | ERJ-8ENF1000V      | Panasonic            |

| R4, R5               | 30.1 kΩ resistor, 0603                         | ERJ-3EKF3012V      | Panasonic            |

| R6, R17              | Not installed                                  | Not applicable     | Not applicable       |

| R7                   | 100 Ω resistor, 0603                           | ERJ-3EKF1000V      | Panasonic            |

| R8                   | 49.9 Ω resistor, 0603                          | ERJ-3EKF49R9V      | Panasonic            |

| T1                   | Sumida 13 μH primary 1:2 transformer           | 12322-T235         | Sumida               |

| U1                   | Isolated IGBT gate driver                      | ADuM4138BRWZ       | Analog Devices, Inc. |

## NOTES

#

ESD Caution

ESD (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer, all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS. ENDORSEMENTS. GUARANTEES. OR WARRANTIES, EXPRESS OR IMPLIED. RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2018 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. UG16245-0-12/18(0)

www.analog.com

Rev. 0 | Page 18 of 18