# Revision History 256M AS4C32M8SA 54-pin TSOPII PACKAGE

| Revision | Details               | Date      |

|----------|-----------------------|-----------|

| Rev 1.0  | Preliminary datasheet | Jun. 2017 |

Alliance Memory Inc. 511 Taylor Way, San Carlos, CA 94070 TEL: (650) 610-6800 FAX: (650) 620-9211 Alliance Memory Inc. reserves the right to change products or specification without notice

Confidential - 1 of 55 - Rev.1.0 June 2017

### 32M x 8 bit Synchronous DRAM (SDRAM)

Advance (Rev. 1.0, Jun. /2017)

#### **Features**

• Fast access time from clock: 5/5.4 ns

• Fast clock rate: 166/143 MHz

• Fully synchronous operation

• Internal pipelined architecture

• 8M word x 8-bit x 4-bank

• Programmable Mode registers

- CAS Latency: 2 or 3

- Burst Length: 1, 2, 4, 8, or full page

- Burst Type: Sequential or Interleaved

- Burst stop function

· Auto Refresh and Self Refresh

• 8192 refresh cycles/64ms

• CKE power down mode

• Single +3.3V ±0.3V power supply

Operating Temperature:

Commercial: T<sub>A</sub> = 0~70°C

Industrial: T<sub>A</sub> = -40~85°C

Interface: LVTTL

• 54-pin 400 mil plastic TSOP II package

- Pb free and Halogen free

#### Overview

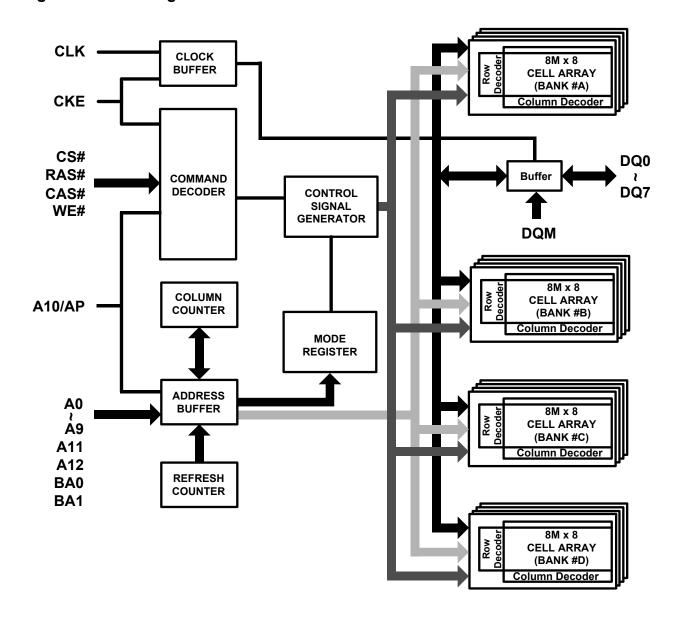

The AS4C32M8SA SDRAM is a high-speed CMOS synchronous DRAM containing 256 Mbits. It is internally configured as 4 Banks of 8M word x 8 DRAM with a synchronous interface (all signals are registered on the positive edge of the clock signal, CLK). Read and write accesses to the SDRAM are burst oriented; accesses start at a selected location and continue for a programmed number of locations in a programmed sequence. Accesses begin with the registration of a Bank Activate command which is then followed by a Read or Write command.

The AS4C32M8SA provides for programmable Read or Write burst lengths of 1, 2, 4, 8, or full page, with a burst termination option. An auto precharge function may be enabled to provide a self-timed row precharge that is initiated at the end of the burst sequence. The refresh functions, either Auto or Self Refresh are easy to use. By having a programmable mode register, the system can choose the most suitable modes to maximize its performance. These devices are well suited for applications requiring high memory bandwidth and particularly well suited to high performance PC applications.

**Table 1. Ordering Information**

| Part Number     | Org   | Temperature               | MaxClock (MHz) | Package       |  |

|-----------------|-------|---------------------------|----------------|---------------|--|

| AS4C32M8SA-7TCN | 32Mx8 | Commercial 0°C to +70°C   | 143 MHz        | 54-pin TSOPII |  |

| AS4C32M8SA-6TIN | 32Mx8 | Industrial -40°C to +85°C | 166 MHz        | 54-pin TSOPII |  |

**Table 2. Key Specifications**

|      | AS4C32M8SA                  | -6 | -7  | Unit |

|------|-----------------------------|----|-----|------|

| tCK3 | Clock Cycle time(min.)      | 6  | 7   | ns   |

| tAC3 | Access time from CLK (max.) | 5  | 5.4 | ns   |

| tRAS | Row Active time(min.)       | 42 | 42  | ns   |

| tRC  | Row Cycle time(min.)        | 60 | 63  | ns   |

**Figure 1. Pin Assignment (Top View)**

|      |    |    | ,    |

|------|----|----|------|

| VDD  | 10 | 54 | vss  |

| DQ0  | 2  | 53 | DQ7  |

| VDDQ | 3  | 52 | VSSQ |

| NC   | 4  | 51 | □ NC |

| DQ1  | 5  | 50 | DQ6  |

| VSSQ | 6  | 49 | VDDQ |

| NC   | 7  | 48 | NC   |

| DQ2  | 8  | 47 | DQ5  |

| VDDQ | 9  | 46 | VSSQ |

| NC   | 10 | 45 | NC   |

| DQ3  | 11 | 44 | DQ4  |

| VSSQ | 12 | 43 | VDDQ |

| NC   | 13 | 42 | NC   |

| VDD  | 14 | 41 | vss  |

| NC   | 15 | 40 | NC   |

| WE#  | 16 | 39 | DQM  |

| CAS# | 17 | 38 | CLK  |

| RAS# | 18 | 37 | CKE  |

| CS#  | 19 | 36 | A12  |

| ВА0  | 20 | 35 | A11  |

| BA1  | 21 | 34 | A9   |

| A10  | 22 | 33 | A8   |

| A0   | 23 | 32 | A7   |

| A1   | 24 | 31 | A6   |

| A2   | 25 | 30 | A5   |

| A3   | 26 | 29 | A4   |

| VDD  | 27 | 28 | vss  |

|      |    |    | J    |

Figure 2. Block Diagram

### **Pin Descriptions**

**Table 3. Pin Details**

| Symbol  | Type  | Description                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |  |  |  |  |

|---------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| CLK     | Input | the positive edge of CLK.                                                                                                                                                                                                                                                                                                                              | <b>Clock:</b> CLK is driven by the system clock. All SDRAM input signals are sampled on the positive edge of CLK. CLK also increments the internal burst counter and controls the output registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                 |  |  |  |  |

| CKE     | Input | CKE goes low synchronou inputs), the internal clock is output and burst address is are in the idle state, deactive Self Refresh modes. CKE Down and Self Refresh modes ame mode. The input buffer                                                                                                                                                      | Clock Enable: CKE activates (HIGH) and deactivates (LOW) the CLK signal. It CKE goes low synchronously with clock (set-up and hold time same as other inputs), the internal clock is suspended from the next clock cycle and the state of output and burst address is frozen as long as the CKE remains low. When all banks are in the idle state, deactivating the clock controls the entry to the Power Down and Self Refresh modes. CKE is synchronous except after the device enters Power Down and Self Refresh modes, where CKE becomes asynchronous until exiting the same mode. The input buffers, including CLK, are disabled during Power Down and Self Refresh modes, providing low standby power. |                                                                                                                                                 |  |  |  |  |

| BA0,BA1 | Input | Bank Activate: BA0, BA1 in                                                                                                                                                                                                                                                                                                                             | nput select the bank for oper                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ration.                                                                                                                                         |  |  |  |  |

|         |       | BA1                                                                                                                                                                                                                                                                                                                                                    | BA0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Select Bank                                                                                                                                     |  |  |  |  |

|         |       | 0                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BANK #A                                                                                                                                         |  |  |  |  |

|         |       | 0                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BANK #B                                                                                                                                         |  |  |  |  |

|         |       | 1                                                                                                                                                                                                                                                                                                                                                      | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BANK #C                                                                                                                                         |  |  |  |  |

|         |       | 1                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | BANK #D                                                                                                                                         |  |  |  |  |

| A0-A12  | Input | address A0-A12) and Readefining Auto Precharge) trespective bank. During a F                                                                                                                                                                                                                                                                           | d/Write command (column<br>to select one location out<br>Precharge command, A10 is<br>d (A10 = HIGH). The addr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ankActivate command (row<br>address A0-A9; with A10<br>of the 8M available in the<br>sampled to determine if all<br>ess inputs also provide the |  |  |  |  |

| CS#     | Input | command decoder. All com                                                                                                                                                                                                                                                                                                                               | mands are masked when (                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ables (sampled HIGH) the CS# is sampled HIGH. CS# ultiple banks. It is considered                                                               |  |  |  |  |

| RAS#    | Input | conjunction with the CAS# a CLK. When RAS# and CS either the BankActivate con WE# signal. When the WI selected and the bank designment were well asserted "LOW"                                                                                                                                                                                        | Row Address Strobe: The RAS# signal defines the operation commands in conjunction with the CAS# and WE# signals and is latched at the positive edges of CLK. When RAS# and CS# are asserted "LOW" and CAS# is asserted "HIGH" either the BankActivate command or the Precharge command is selected by the WE# signal. When the WE# is asserted "HIGH" the BankActivate command is selected and the bank designated by BA is turned on to the active state. When the WE# is asserted "LOW" the Precharge command is selected and the bank designated by BA is switched to the idle state after the precharge operation.                                                                                        |                                                                                                                                                 |  |  |  |  |

| CAS#    | Input | Column Address Strobe: The CAS# signal defines the operation commands in conjunction with the RAS# and WE# signals and is latched at the positive edges of CLK. When RAS# is held "HIGH" and CS# is asserted "LOW" the column access is started by asserting CAS# "LOW". Then, the Read or Write command is selected by asserting WE# "LOW" or "HIGH". |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                 |  |  |  |  |

| WE#     | Input | the RAS# and CAS# signal                                                                                                                                                                                                                                                                                                                               | Write Enable: The WE# signal defines the operation commands in conjunction with the RAS# and CAS# signals and is latched at the positive edges of CLK. The WE# input is used to select the BankActivate or Precharge command and Read or Write                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                 |  |  |  |  |

| DQM     | Input | Data Input/Output Mask: data in write mode.                                                                                                                                                                                                                                                                                                            | Controls output buffers in re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ead mode and masks Input                                                                                                                        |  |  |  |  |

| DQ0-DQ7          |        | <b>Data I/O:</b> The DQ0-7 input and output data are synchronized with the positive edges of CLK. The I/Os are maskabled during Reads and Writes. |

|------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| NC               | -      | No Connect: These pins should be left unconnected.                                                                                                |

| V <sub>DDQ</sub> | Suply  | <b>DQ Power:</b> Provide isolated power to DQs for improved noise immunity. (+3.3V $\pm$ 0.3V)                                                    |

| Vssq             | Supply | DQ Ground: Provide isolated ground to DQs for improved noise immunity. (0 V)                                                                      |

| V <sub>DD</sub>  | Supply | Power Supply: (+3.3V ±0.3V)                                                                                                                       |

| Vss              | Supply | Ground                                                                                                                                            |

Confidential - 6 of 55 - Rev.1.0 June 2017

### **Operation Mode**

Fully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 4 shows the truth table for the operation commands.

Table 4. Truth Table (Note (1), (2))

| Command                  | State                 | CKE <sub>n-1</sub> | CKEn     | DQM | BA0,1 | A10 | A0-9,11-12     | CS#   | RAS# | CAS#   | WE# |

|--------------------------|-----------------------|--------------------|----------|-----|-------|-----|----------------|-------|------|--------|-----|

| BankActivate             | Idle <sup>(3)</sup>   | Н                  | Х        | Х   | V     | R   | ow address     | L     | L    | Н      | Н   |

| BankPrecharge            | Any                   | Н                  | Х        | Х   | V     | L   | Х              | L     | L    | Н      | L   |

| PrechargeAll             | Any                   | Н                  | Х        | Х   | Х     | Н   | Х              | L     | L    | Н      | L   |

| Write                    | Active <sup>(3)</sup> | Н                  | Х        | V   | V     | L   | Column address | L     | Н    | L      | L   |

| Write and AutoPrecharge  | Active <sup>(3)</sup> | Н                  | Х        | V   | V     | Н   | (A0 ~ A9)      | L     | Н    | L      | L   |

| Read                     | Active <sup>(3)</sup> | Н                  | Х        | V   | V     | L   | Column address | L     | Н    | L      | Н   |

| Read and Autoprecharge   | Active <sup>(3)</sup> | Н                  | Х        | V   | V     | Н   | (A0 ~ A9)      | L     | Н    | L      | Н   |

| Mode Register Set        | Idle                  | Н                  | Х        | Х   |       | OP  | code           | L     | L    | L      | L   |

| No-Operation             | Any                   | Н                  | Х        | Х   | Х     | Х   | Х              | L     | Н    | Н      | Н   |

| Burst Stop               | Active <sup>(4)</sup> | Н                  | Х        | Х   | Х     | Х   | Х              | L     | Н    | Н      | L   |

| Device Deselect          | Any                   | Н                  | Х        | Х   | Х     | Х   | Х              | Н     | Х    | Х      | Х   |

| AutoRefresh              | Idle                  | Н                  | Н        | Х   | Х     | Х   | Х              | L     | L    | L      | Н   |

| SelfRefresh Entry        | Idle                  | Н                  | L        | Х   | Х     | Х   | Х              | L     | L    | L      | Н   |

| SelfRefresh Exit         | Idle<br>(SelfRefresh) | L                  | Н        | Х   | Х     | х   | х              | H     | X    | X<br>H | X   |

|                          |                       |                    |          |     |       |     |                | <br>H | X    | X      | Х   |

| Clock Suspend Mode Entry | Active                | Н                  | L        | Х   | Х     | Х   | X              | L     | V    | V      | V   |

| Power Down Mode Entry    | Any <sup>(5)</sup>    | Н                  | L        | Х   | Х     | Х   | Х              | Ι     | Х    | Х      | Х   |

| r ower bown wode Liftiy  | Ally                  | 11                 | <b>L</b> | ^   | ^     | ^   | ^              | L     | Н    | Н      | Н   |

| Clock Suspend Mode Exit  | Active                | L                  | Н        | Χ   | Х     | Χ   | X              | Χ     | Х    | Х      | Χ   |

| Power Down Mode Exit     | Any                   | L                  | Н        | Х   | Х     | Х   | Х              | Н     | Х    | Х      | Х   |

| TOWN DOWN WOOD LAIL      | (PowerDown)           | _                  | ''       |     |       | ^   | ^              | L     | Н    | Н      | Н   |

| Data Write/Output Enable | Active                | Н                  | Х        | L   | Х     | Χ   | Х              | Χ     | Х    | Х      | Χ   |

| Data Mask/Output Disable | Active                | Н                  | Χ        | Н   | Χ     | Χ   | X              | Χ     | Х    | Χ      | Χ   |

Note: 1. V=Valid, X=Don't Care, L=Low level, H=High level

2. CKE<sub>n</sub> signal is input level when commands are provided. CKE<sub>n-1</sub> signal is input level one clock cycle before the commands are provided.

- 3. These are states of bank designated by BA signal.

- 4. Device state is 1, 2, 4, 8, and full page burst operation.

- 5. Power Down Mode can not enter in the burst operation.

When this command is asserted in the burst cycle, device state is clock suspend mode.

#### **Commands**

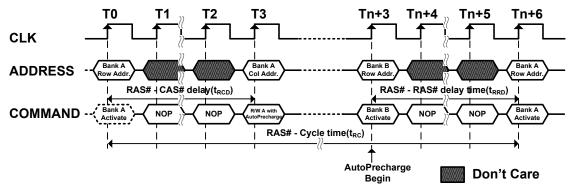

#### 1 BankActivate

(RAS# = "L", CAS# = "H", WE# = "H", BAs = Bank, A0-A12 = Row Address)

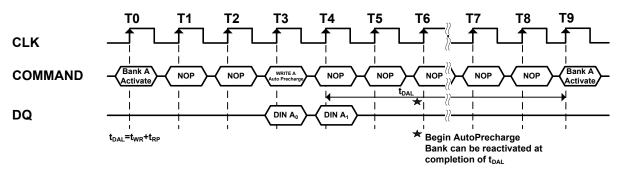

The BankActivate command activates the idle bank designated by the BA0, 1 signals. By latching the row address on A0 to A12 at the time of this command, the selected row access is initiated. The read or write operation in the same bank can occur after a time delay of trace (min.) from the time of bank activation. A subsequent BankActivate command to a different row in the same bank can only be issued after the previous active row has been precharged (refer to the following figure). The minimum time interval between successive BankActivate commands to the same bank is defined by trace (min.). The SDRAM has four internal banks on the same chip and shares part of the internal circuitry to reduce chip area; therefore it restricts the back-to-back activation of the two banks. trace (min.) specifies the minimum time required between activating different banks. After this command is used, the Write command and the Block Write command perform the no mask write operation.

Figure 3. BankActivate Command Cycle (Burst Length = n)

#### 2 BankPrecharge command

(RAS# = "L", CAS# = "H", WE# = "L", BAs = Bank, A10 = "L", A0-A9, A11 and A12 = Don't care)

The BankPrecharge command precharges the bank disignated by BA signal. The precharged bank is switched from the active state to the idle state. This command can be asserted anytime after trans(min.) is satisfied from the BankActivate command in the desired bank. The maximum time any bank can be active is specified by trans(max.). Therefore, the precharge function must be performed in any active bank within trans(max.). At the end of precharge, the precharged bank is still in the idle state and is ready to be activated again.

#### 3 PrechargeAll command

(RAS# = "L", CAS# = "H", WE# = "L", BAs = Don't care, A10 = "H", A0-A9, A11 and A12 = Don't care)

The PrechargeAll command precharges all banks simultaneously and can be issued even if all banks are not in the active state. All banks are then switched to the idle state.

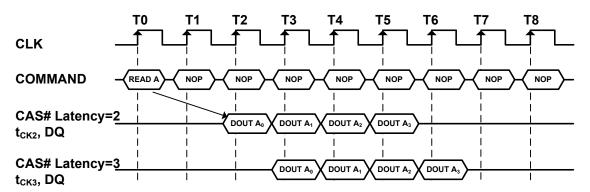

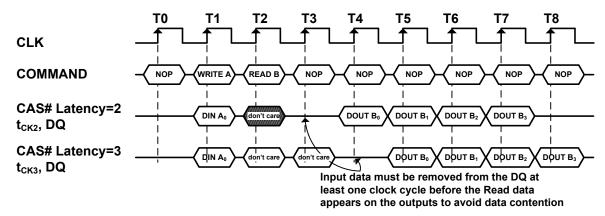

#### 4 Read command

(RAS# = "H", CAS# = "L", WE# = "H", BAs = Bank, A10 = "L", A0-A9 = Column Address)

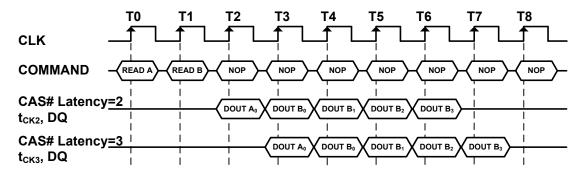

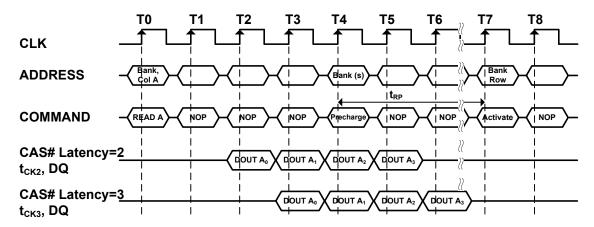

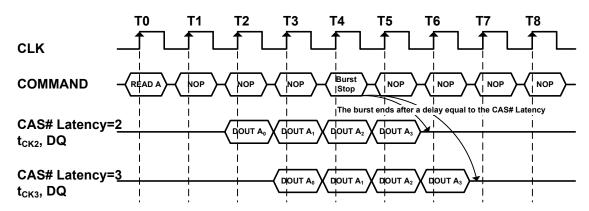

The Read command is used to read a burst of data on consecutive clock cycles from an active row in an active bank. The bank must be active for at least tRCD(min.) before the Read command is issued. During read bursts, the valid data-out element from the starting column address will be available following the CAS latency after the issue of the Read command. Each subsequent data-out element will be valid by the next positive clock edge (refer to the following figure). The DQs go into high-impedance at the end of the burst unless other command is initiated. The burst length, burst sequence, and CAS latency are determined by the mode register, which is already programmed. A full-page burst will continue until terminated (at the end of the page it will wrap to column 0 and continue).

Confidential - 8 of 55 - Rev.1.0 June 2017

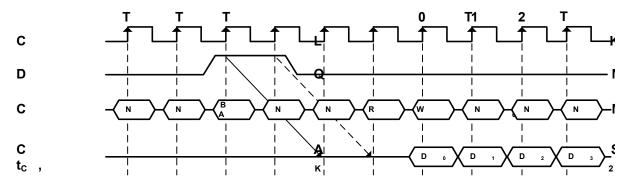

Figure 4. Burst Read Operation (Burst Length = 4, CAS# Latency = 2, 3)

The read data appears on the DQs subject to the values on the DQM inputs two clocks earlier (i.e. DQM latency is two clocks for output buffers). A read burst without the auto precharge function may be interrupted by a subsequent Read or Write command to the same bank or the other active bank before the end of the burst length. It may be interrupted by a BankPrecharge/ PrechargeAll command to the same bank too. The interrupt coming from the Read command can occur on any clock cycle following a previous Read command (refer to the following figure).

Figure 5. Read Interrupted by a Read (Burst Length = 4, CAS# Latency = 2, 3)

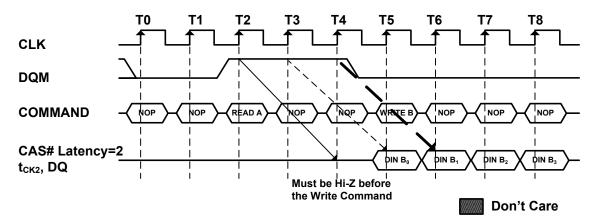

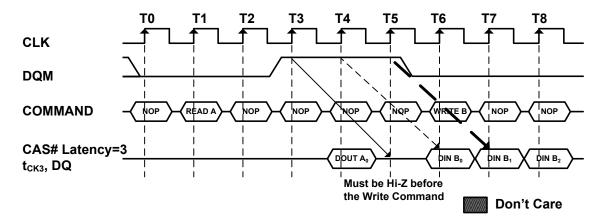

The DQM inputs are used to avoid I/O contention on the DQ pins when the interrupt comes from a Write command. The DQM must be asserted (HIGH) at least two clocks prior to the Write command to suppress data-out on the DQ pins. To guarantee the DQ pins against I/O contention, a single cycle with high-impedance on the DQ pins must occur between the last read data and the Write command (refer to the following three figures). If the data output of the burst read occurs at the second clock of the burst write, the DQM must be asserted (HIGH) at least one clock prior to the Write command to avoid internal bus contention.

Figure 6. Read to Write Interval (Burst Length ≥ 4, CAS# Latency = 2)

Confidential - 9 of 55 - Rev.1.0 June 2017

Figure 7. Read to Write Interval (Burst Length ≥ 4, CAS# Latency = 2)

Figure 8. Read to Write Interval (Burst Length ≥ 4, CAS# Latency = 3)

A read burst without the auto precharge function may be interrupted by a BankPrecharge/ PrechargeAll command to the same bank. The following figure shows the optimum time that Bank Precharge/ PrechargeAll command is issued in different CAS latency.

Figure 9. Read to Precharge (CAS# Latency = 2, 3)

Confidential - 10 of 55 - Rev.1.0 June 2017

#### 5 Read and AutoPrecharge command

(RAS# = "H", CAS# = "L", WE# = "H", BAs = Bank, A10 = "H", A0-A9 = Column Address)

The Read and AutoPrecharge command automatically performs the precharge operation after the read operation. Once this command is given, any subsequent command cannot occur within a time delay of  $\{t_{RP}(min.) + burst length\}$ . At full-page burst, only the read operation is performed in this command and the auto precharge function is ignored.

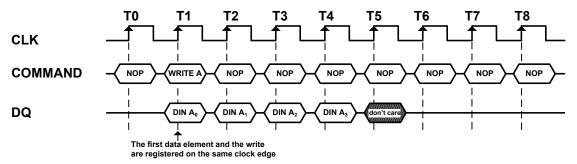

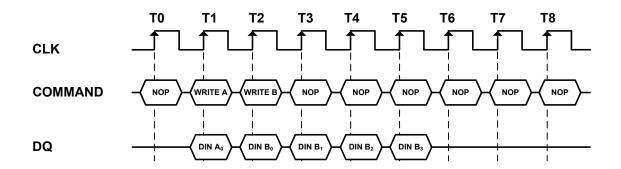

#### 6 Write command

(RAS# = "H", CAS# = "L", WE# = "L", BAs = Bank, A10 = "L", A0-A9 = Column Address)

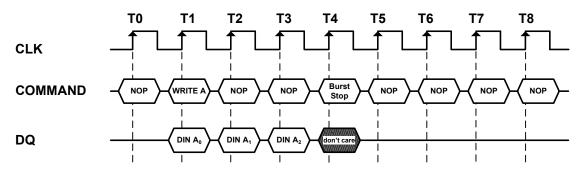

The Write command is used to write a burst of data on consecutive clock cycles from an active row in an active bank. The bank must be active for at least trace(min.) before the Write command is issued. During write bursts, the first valid data-in element will be registered coincident with the Write command. Subsequent data elements will be registered on each successive positive clock edge (refer to the following figure). The DQs remain with high-impedance at the end of the burst unless another command is initiated. The burst length and burst sequence are determined by the mode register, which is already programmed. A full-page burst will continue until terminated (at the end of the page it will wrap to column 0 and continue).

Figure 10. Burst Write Operation (Burst Length = 4)

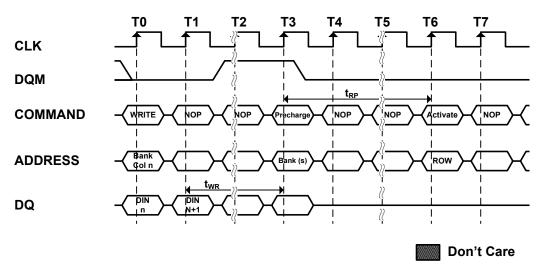

A write burst without the auto precharge function may be interrupted by a subsequent Write, BankPrecharge/PrechargeAll, or Read command before the end of the burst length. An interrupt coming from Write command can occur on any clock cycle following the previous Write command (refer to the following figure).

Figure 11. Write Interrupted by a Write (Burst Length = 4)

The Read command that interrupts a write burst without auto precharge function should be issued one cycle after the clock edge in which the last data-in element is registered. In order to avoid data contention, input data must be removed from the DQs at least one clock cycle before the first read data appears on the outputs (refer to the following figure). Once the Read command is registered, the data inputs will be ignored and writes will not be executed.

Confidential - 11 of 55 - Rev.1.0 June 2017

Figure 12. Write Interrupted by a Read (Burst Length = 4, CAS# Latency = 2, 3)

The BankPrecharge/PrechargeAll command that interrupts a write burst without the auto precharge function should be issued m cycles after the clock edge in which the last data-in element is registered, where m equals twR/tcK rounded up to the next whole number. In addition, the DQM signals must be used to mask input data, starting with the clock edge following the last data-in element and ending with the clock edge on which the BankPrecharge/PrechargeAll command is entered (refer to the following figure).

**Note:** The DQM can remain low in this example if the length of the write burst is 1 or 2.

Figure 13. Write to Precharge

7 Write and AutoPrecharge command

(RAS# = "H", CAS# = "L", WE# = "L", BAs = Bank, A10 = "H", A0-A9 = Column Address)

The Write and AutoPrecharge command performs the precharge operation automatically after the write operation. Once this command is given, any subsequent command can not occur within a time delay of {(burst length -1) +  $t_{WR}$  +  $t_{RP}$ (min.)}. At full-page burst, only the write operation is performed in this command and the auto precharge function is ignored.

Confidential - 12 of 55 - Rev.1.0 June 2017

Figure 14. Burst Write with Auto-Precharge (Burst Length = 2)

8 Mode Register Set command (RAS# = "L", CAS# = "L", WE# = "L", A0-A12 = Register Data)

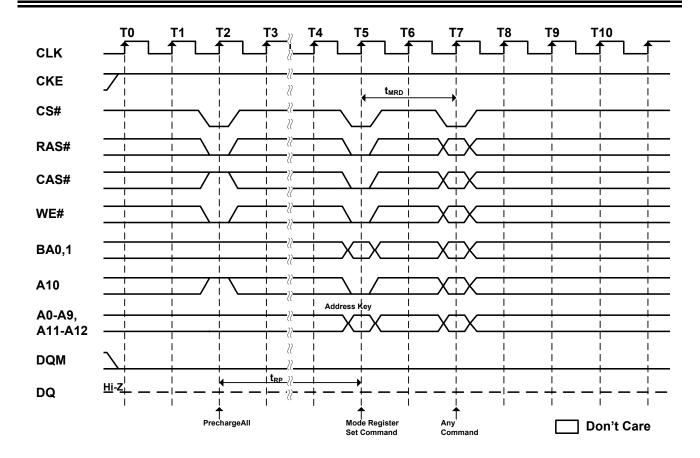

The mode register stores the data for controlling the various operating modes of SDRAM. The Mode Register Set command programs the values of CAS latency, Addressing Mode and Burst Length in the Mode register to make SDRAM useful for a variety of different applications. The default values of the Mode Register after power-up are undefined; therefore this command must be issued at the power-up sequence. The state of pins A0~ A12 in the same cycle is the data written to the mode register. Two clock cycles are required to complete the write in the mode register (refer to the following figure). The contents of the mode register can be changed using the same command and the clock cycle requirements during operation as long as all banks are in the idle state.

**Table 5. Mode Register Bitmap**

| BA1  | BA0   | A12     | A11    | A10               | A9   | A8       | A7     | A6       | A:   | 5    | A4      | A3     | A2              | A1       | A0      |

|------|-------|---------|--------|-------------------|------|----------|--------|----------|------|------|---------|--------|-----------------|----------|---------|

| RFU* | 0     |         | RFU*   |                   | WBL  | Test     | Mode   | CA       | S La | aten | су      | BT     | BT Burst Length |          | gth     |

|      |       | Ţ       |        | •                 |      | L        | 4      | <b>,</b> |      | _    |         | L      |                 | <b>→</b> |         |

| A9   | Write | Burst   | Length | n A               | 8 A7 | <b>'</b> | Test N | /lode    |      |      |         | A3     | Bu              | ırst Typ | е       |

| 0    |       | Burs    | t      | C                 | 0    |          | Norr   | nal      |      |      |         | 0      | Se              | equentia | al      |

| 1    | ,     | Single  | Bit    | 1                 | 0    | Ve       | ndor U | se Onl   | y    |      |         | 1      | In              | terleav  | е       |

|      |       |         |        | C                 | ) 1  | Ve       | ndor U | se Onl   | y    |      |         |        |                 |          |         |

|      |       |         |        | $\overline{\Box}$ |      |          |        |          |      |      |         |        | Ŧ               |          |         |

| A6   | A5    | A4      | CA     | S Late            | ncy  |          |        | A2       | Α    | .1   | A0      |        | Burs            | Lengtl   | h       |

| 0    | 0     | 0       | R      | eserve            | ed   |          |        | 0        | (    | )    | 0       |        |                 | 1        |         |

| 0    | 0     | 1       | R      | eserve            | ed   |          |        | 0        | (    | )    | 1       |        |                 | 2        |         |

| 0    | 1     | 0       | 2      | 2 clock           | s    |          |        | 0        | 1    | 1    | 0       |        |                 | 4        |         |

| 0    | 1     | 1       | 3      | 3 clock           | is   |          |        | 0        | 1    | 1    | 1       |        | 8               |          |         |

| 1    | 0     | 0       | R      | eserve            | ed   |          |        | 1        | 1    | 1    | 1       | Ful    | l Page          | (Seque   | ential) |

|      | All   | other F | Reserv | ed                | -    |          |        |          |      | Α    | ll othe | r Rese | erved           |          |         |

\*Note: RFU (Reserved for future use) should stay "0" during MRS cycle.

Figure 15. Mode Register Set Cycle

• Burst Length Field (A2~A0)

This field specifies the data length of column access using the A2 $\sim$ A0 pins and selects the Burst Length to be 2, 4, 8, or full page.

Table 6. Burst Length Field

| A2 | A1      | A0 | Burst Length |

|----|---------|----|--------------|

| 0  | 0       | 0  | 1            |

| 0  | 0       | 1  | 2            |

| 0  | 1       | 0  | 4            |

| 0  | 1       | 1  | 8            |

| 1  | 0       | 0  | Reserved     |

| 1  | 0       | 1  | Reserved     |

| 1  | 1       | 0  | Reserved     |

| 1  | 1       | 1  | Full Page    |

|    | 11 1001 |    |              |

Full Page Length: 1024

#### • Burst Type Field (A3)

The Addressing Mode can be one of two modes, Interleave Mode or Sequential Mode. Sequential Mode supports burst length of 1, 2, 4, 8, or full page, but Interleave Mode only supports burst length of 4 and 8.

Table 7. Addressing Mode Select Field

| A3 | Burst Type |

|----|------------|

| 0  | Sequential |

| 1  | Interleave |

• Burst Definition, Addressing Sequence of Sequential and Interleave Mode

Table 8. Burst Definition

| Burst Length | Start Address |         | ess  | Sequential                                 | Interleave             |  |

|--------------|---------------|---------|------|--------------------------------------------|------------------------|--|

| Burst Length | A2            | A1      | A0   | Sequential                                 | interleave             |  |

| 2            | Χ             | X       | 0    | 0, 1                                       | 0, 1                   |  |

| 2            | X             | X       | 1    | 1, 0                                       | 1, 0                   |  |

|              | Χ             | 0       | 0    | 0, 1, 2, 3                                 | 0, 1, 2, 3             |  |

| 4            | Х             | 0       | 1    | 1, 2, 3, 0                                 | 1, 0, 3, 2             |  |

| 4            | Х             | 1       | 0    | 2, 3, 0, 1                                 | 2, 3, 0, 1             |  |

|              | X             | 1       | 1    | 3, 0, 1, 2                                 | 3, 2, 1, 0             |  |

|              | 0             | 0       | 0    | 0, 1, 2, 3, 4, 5, 6, 7                     | 0, 1, 2, 3, 4, 5, 6, 7 |  |

|              | 0             | 0       | 1    | 1, 2, 3, 4, 5, 6, 7, 0                     | 1, 0, 3, 2, 5, 4, 7, 6 |  |

|              | 0             | 1       | 0    | 2, 3, 4, 5, 6, 7, 0, 1                     | 2, 3, 0, 1, 6, 7, 4, 5 |  |

| 8            | 0             | 1       | 1    | 3, 4, 5, 6, 7, 0, 1, 2                     | 3, 2, 1, 0, 7, 6, 5, 4 |  |

| 0            | 1             | 0       | 0    | 4, 5, 6, 7, 0, 1, 2, 3                     | 4, 5, 6, 7, 0, 1, 2, 3 |  |

|              | 1             | 0       | 1    | 5, 6, 7, 0, 1, 2, 3, 4                     | 5, 4, 7, 6, 1, 0, 3, 2 |  |

|              | 1             | 1       | 0    | 6, 7, 0, 1, 2, 3, 4, 5                     | 6, 7, 4, 5, 2, 3, 0, 1 |  |

|              | 1             | 1       | 1    | 7, 0, 1, 2, 3, 4, 5, 6                     | 7, 6, 5, 4, 3, 2, 1, 0 |  |

| Full page    | locatio       | n = 0-1 | 1023 | n, n+1, n+2, n+3,1023,<br>0, 1, 2, n-1, n, | Not Support            |  |

#### CAS Latency Field (A6~A4)

This field specifies the number of clock cycles from the assertion of the Read command to the first read data. The minimum whole value of CAS Latency depends on the frequency of CLK. The minimum whole value satisfying the following formula must be programmed into this field.

tcac(min) ≤ CAS Latency X tck

Table 9. CAS Latency

| 4.0 | ۸.5 | A 4 | 0.4.0.1. = 4.= = = = |

|-----|-----|-----|----------------------|

| A6  | A5  | A4  | CAS Latency          |

| 0   | 0   | 0   | Reserved             |

| 0   | 0   | 1   | Reserved             |

| 0   | 1   | 0   | 2 clocks             |

| 0   | 1   | 1   | 3 clocks             |

| 1   | Х   | Х   | Reserved             |

Confidential - 15 of 55 - Rev.1.0 June 2017

#### • Test Mode field (A8~A7)

These two bits are used to enter the test mode and must be programmed to "00" in normal operation.

Table 10. Test Mode

| A8 | A7 | Test Mode       |

|----|----|-----------------|

| 0  | 0  | normal mode     |

| 0  | 1  | Vendor Use Only |

| 1  | Х  | Vendor Use Only |

### • Write Burst Length (A9)

This bit is used to select the write burst length. When the A9 bit is "0", the Burst-Read-Burst-Write mode is selected. When the A9 bit is "1", the Burst-Read-Single-Write mode is selected.

Table 11. Write Burst Length

| A9 | Write Burst Length      |  |  |  |

|----|-------------------------|--|--|--|

| 0  | Burst-Read-Burst-Write  |  |  |  |

| 1  | Burst-Read-Single-Write |  |  |  |

Note: A10 and BA0, 1 should stay "L" during mode set cycle.

#### 9 No-Operation command

(RAS# = "H", CAS# = "H", WE# = "H")

The No-Operation command is used to perform a NOP to the SDRAM which is selected (CS# is Low). This prevents unwanted commands from being registered during idle or wait states.

#### 10 Burst Stop command

(RAS# = "H", CAS# = "H", WE# = "L")

The Burst Stop command is used to terminate either fixed-length or full-page bursts. This command is only effective in a read/write burst without the auto precharge function. The terminated read burst ends after a delay equal to the CAS latency (refer to the following figure). The termination of a write burst is shown in the following figure.

Figure 16. Termination of a Burst Read Operation (Burst Length>4, CAS# Latency = 2, 3)

Confidential - 16 of 55 - Rev.1.0 June 2017

Figure 17. Termination of a Burst Write Operation (Burst Length = X)

#### 11 Device Deselect command (CS# = "H")

The Device Deselect command disables the command decoder so that the RAS#, CAS#, WE# and Address inputs are ignored, regardless of whether the CLK is enabled. This command is similar to the No Operation command.

#### 12 AutoRefresh command

(RAS# = "L", CAS# = "L", WE# = "H", CKE = "H", A0-A12 = Don't care)

The AutoRefresh command is used during normal operation of the SDRAM and is analogous to CAS#-before-RAS# (CBR) Refresh in conventional DRAMs. This command is non-persistent, so it must be issued each time a refresh is required. The addressing is generated by the internal refresh controller. This makes the address bits a "don't care" during an AutoRefresh command. The internal refresh counter increments automatically on every auto refresh cycle to all of the rows. The refresh operation must be performed 8192 times within 64ms. The time required to complete the auto refresh operation is specified by tRc(min.). To provide the AutoRefresh command, all banks need to be in the idle state and the device must not be in power down mode (CKE is high in the previous cycle). This command must be followed by NOPs until the auto refresh operation is completed. The precharge time requirement, tRP(min), must be met before successive auto refresh operations are performed.

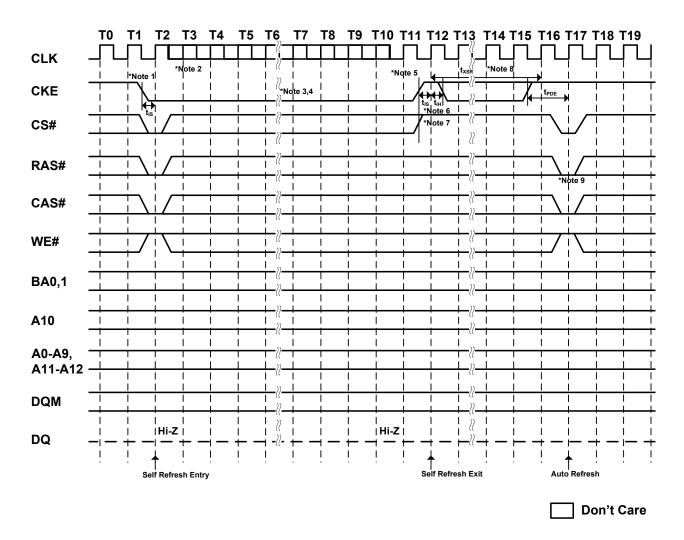

#### 13 SelfRefresh Entry command

(RAS# = "L", CAS# = "L", WE# = "H", CKE = "L", A0-A12 = Don't care)

The SelfRefresh is another refresh mode available in the SDRAM. It is the preferred refresh mode for data retention and low power operation. Once the SelfRefresh command is registered, all the inputs to the SDRAM become "don't care" with the exception of CKE, which must remain LOW. The refresh addressing and timing is internally generated to reduce power consumption. The SDRAM may remain in SelfRefresh mode for an indefinite period. The SelfRefresh mode is exited by restarting the external clock and then asserting HIGH on CKE (SelfRefresh Exit command).

#### 14 SelfRefresh Exit command

This command is used to exit from the SelfRefresh mode. Once this command is registered, NOP or Device Deselect commands must be issued for  $t_{\rm XSR}(min.)$  because time is required for the completion of any bank currently being internally refreshed. If auto refresh cycles in bursts are performed during normal operation, a burst of 8192 auto refresh cycles should be completed just prior to entering and just after exiting the SelfRefresh mode.

#### 15 Clock Suspend Mode Entry / PowerDown Mode Entry command (CKE = "L")

When the SDRAM is operating the burst cycle, the internal CLK is suspended (masked) from the subsequent cycle by issuing this command (asserting CKE "LOW"). The device operation is held intact while CLK is suspended. On the other hand, when all banks are in the idle state, this command performs entry into the PowerDown mode. All input and output buffers (except the CKE buffer) are turned off in the PowerDown mode. The device may not remain in the Clock Suspend or PowerDown state longer than the refresh period (64ms) since the command does not perform any refresh operations.

Confidential - 17 of 55 - Rev.1.0 June 2017

16 Clock Suspend Mode Exit / PowerDown Mode Exit command (CKE= "H")

When the internal CLK has been suspended, the operation of the internal CLK is reinitiated from the subsequent cycle by providing this command (asserting CKE "HIGH", the command should be NOP or deselect). When the device is in the PowerDown mode, the device exits this mode and all disabled buffers are turned on to the active state.  $t_{\text{PDE}}$  (min.) is required when the device exits from the PowerDown mode. Any subsequent commands can be issued after one clock cycle from the end of this command.

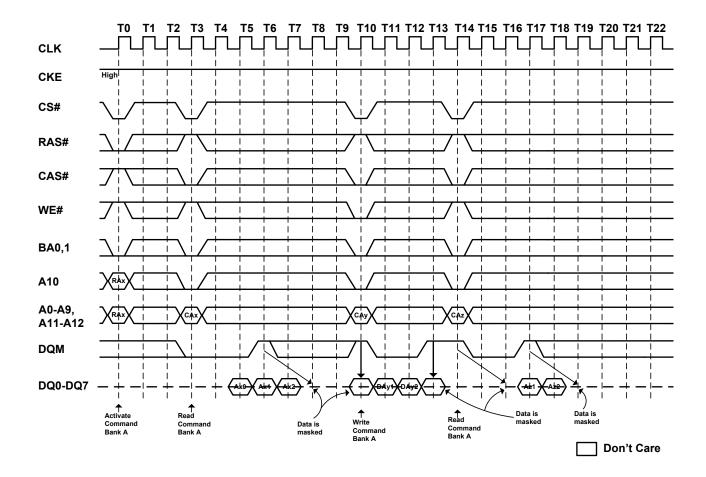

17 Data Write / Output Enable, Data Mask / Output Disable command (DQM = "L", "H")

During a write cycle, the DQM signal functions as a Data Mask and can control every word of the input data. During a read cycle, the DQM functions as the controller of output buffers. DQM is also used for device selection, byte selection and bus control in a memory system.

Confidential - 18 of 55 - Rev.1.0 June 2017

**Table 12. Absolute Maximum Rating**

| Symbol           | ltem                               | Values     | Unit | Note |

|------------------|------------------------------------|------------|------|------|

| VIN, VOUT        | Input, Output Voltage              | -1.0 ~ 4.6 | V    | 1    |

| $V_{DD},V_{DDQ}$ | Power Supply Voltage               | -1.0 ~ 4.6 | V    | 1    |

| TA               | Operating Temperature-Commercial   | 0 ~ 70     | °C   | 1    |

| IA               | Operating Temperature-Industrial   | -40 ~ 85   | °C   | 1    |

| Tstg             | Storage Temperature                | -55 ~ 150  | °C   | 1    |

| TSOLDER          | Soldering Temperature (10 seconds) | 260        | °C   | 1    |

| PD               | Power Dissipation                  | 1          | W    | 1    |

| los              | Short Circuit Output Current       | 50         | mA   | 1    |

Table 13. Recommended D.C. Operating Conditions ( $V_{DD} = 3.3V \pm 0.3V$ )

| Symbol    | Parameter                                                                             | Min. | Тур. | Max.                  | Unit | Note |

|-----------|---------------------------------------------------------------------------------------|------|------|-----------------------|------|------|

| $V_{DD}$  | Power Supply Voltage                                                                  | 3.0  | 3.3  | 3.6                   | >    | 2    |

| $V_{DDQ}$ | Power Supply Voltage(for I/O Buffer)                                                  | 3.0  | 3.3  | 3.6                   | >    | 2    |

| VIH       | LVTTL Input High Voltage                                                              | 2.0  | -    | V <sub>DDQ</sub> +0.3 | >    | 2    |

| VIL       | LVTTL Input Low Voltage                                                               | -0.3 | -    | 0.8                   | >    | 2    |

| lı∟       | Input Leakage Current ( $0V \le VIN \le VDD$ , All other pins not under test = $0V$ ) | -10  | -    | 10                    | μΑ   |      |

| loz       | Output Leakage Current Output disable, $0V \le V_{OUT} \le V_{DDQ}$ )                 | -10  | -    | 10                    | μА   |      |

| Vон       | LVTTL Output "H" Level Voltage ( Iout = -2mA )                                        | 2.4  | _    | -                     | >    |      |

| Vol       | LVTTL Output "L" Level Voltage ( Iouт = 2mA )                                         | 1    | -    | 0.4                   | ٧    |      |

**NOTE:** These parameters are testing under the following conditions.

Operating temperature - Commercial:  $T_A$ = 0~70 °C Operating temperature - Industrial:  $T_A$ = -40~85 °C

Table 14. Capacitance (VDD = 3.3V, TA = 25°C)

| Symbol           | Parameter                | Min. | Max. | Unit |

|------------------|--------------------------|------|------|------|

| Cı               | Input Capacitance        | 2    | 4    | pF   |

| C <sub>I/O</sub> | Input/Output Capacitance | 4    | 6    | pF   |

Note: These parameters are periodically sampled and are not 100% tested.

### Table 15. D.C. Characteristics ( $V_{DD} = 3.3V \pm 0.3V$ )

| Description/Test condition                                                                                                                               | Symbol             | -6 | -7  | Unit | Note  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|-----|------|-------|

| 2 coorphicity root contained                                                                                                                             | ,                  | Ма | ax. |      | 11010 |

| Operating Current tRc≥ tRc(min), Outputs Open, One bank active                                                                                           | I <sub>DD1</sub>   | 60 | 55  |      | 3     |

| Precharge Standby Current in non-power down mode $t_{CK} = 15ns$ , $CS\# \ge V_{IH}(min)$ , $CKE \ge V_{IH}$ Input signals are changed every 2clks       | I <sub>DD2N</sub>  | 30 | 30  |      |       |

| Precharge Standby Current in non-power down mode $t_{CK} = \infty, \ CLK \le V_{IL}(max), \ CKE \ge V_{IH}$                                              | I <sub>DD2NS</sub> | 18 | 18  |      |       |

| Precharge Standby Current in power down mode $t_{CK} = 15ns$ , $CKE \le V_{IL}(max)$                                                                     | I <sub>DD2P</sub>  | 2  | 2   |      |       |

| Precharge Standby Current in power down mode $t_{CK} = \infty$ , $CKE \le V_{IL}(max)$                                                                   | I <sub>DD2PS</sub> | 2  | 2   | mA   |       |

| Active Standby Current in non-power down mode tcκ = 15ns, CKE ≥ V <sub>IH</sub> (min), CS# ≥ V <sub>IH</sub> (min) Input signals are changed every 2clks | IDD3N              | 40 | 40  | IIIA |       |

| Active Standby Current in non-power down mode $CKE \geq V_{IH}(min), \ CLK \leq V_{IL}(max), \ tcK = \infty$                                             | Iddans             | 40 | 40  |      |       |

| Operating Current (Burst mode) tcκ =tcκ(min), Outputs Open, Multi-bank interleave                                                                        | I <sub>DD4</sub>   | 62 | 60  |      | 3, 4  |

| Refresh Current<br>t <sub>RC</sub> ≥ t <sub>RC</sub> (min)                                                                                               | I <sub>DD5</sub>   | 80 | 75  |      | 3     |

| Self Refresh Current CKE $\leq 0.2V$ ; for other inputs V $_{IH}\!\geq\!V_{DD}$ - $0.2V,V_{IL}\leq0.2V$                                                  | I <sub>DD6</sub>   | 2  | 2   |      |       |

**NOTE:** These parameters are testing under the following conditions.

Operating temperature - Commercial:  $T_A$ = 0~70 °C Operating temperature - Industrial:  $T_A$ = -40~85 °C

# Table 16. Electrical Characteristics and Recommended A.C. Operating Conditions ( $V_{DD} = 3.3V \pm 0.3V$ ) (Note: 5, 6, 7, 8)

|        | ol A.C. Parameter                                    |           | -6      |      | -7      |      | Unit | Nata |

|--------|------------------------------------------------------|-----------|---------|------|---------|------|------|------|

| Symbol |                                                      |           | Min.    | Max. | Min.    | Max. | Unit | Note |

| trc    | Row cycle time (same bank)                           |           | 60      | -    | 63      | -    |      |      |

| trfc   | Refresh cycle time                                   |           | 60      | -    | 63      | -    |      |      |

| trcd   | RAS# to CAS# delay (same bank)                       |           | 18      | -    | 21      | -    |      |      |

| trp    | Precharge to refresh/row activate (same bank)        | command   | 18      | -    | 21      | -    |      |      |

| trrd   | Row activate to row activate delay (different banks) |           | 12      | -    | 14      | -    |      |      |

| tmrd   | Mode register set cycle time                         |           | 12      | -    | 14      | -    |      |      |

| tras   | Row activate to precharge time (sa                   | ame bank) | 42      | 120K | 42      | 120K |      |      |

| twr    | Write recovery time                                  |           | 12      | -    | 14      | -    |      |      |

|        | Clock cycle time                                     | CL* = 2   | 10      | -    | 10      | -    |      |      |

| tck CI |                                                      | CL* = 3   | 6       | -    | 7       | -    | ns S | 9    |

| tсн    | Clock high time                                      |           | 2       | -    | 2.5     | -    |      | 10   |

| tcL    | Clock low time                                       |           | 2       | -    | 2.5     | -    |      | 10   |

| tac    | Access time from CLK                                 | CL* = 2   | -       | 6    | -       | 6    |      | 10   |

| IAC    | (positive edge)                                      | CL* = 3   | -       | 5    | -       | 5.4  |      | 10   |

| tон    | Data output hold time                                |           | 2.5     | -    | 2.5     | -    |      | 9    |

| tız    | Data output low impedance                            |           | 0       | -    | 0       | -    |      |      |

| tHZ    | Data output high impedance                           |           | -       | 5    | -       | 5.4  |      | 8    |

| tıs    | Data/Address/Control Input set-up time               |           | 1.5     | -    | 1.5     | -    |      | 10   |

| tıн    | Data/Address/Control Input hold time                 |           | 0.8     | -    | 0.8     | -    |      | 10   |

| tpde   | Power Down Exit set-up time                          |           | tıs+tcĸ | -    | tıs₊tcĸ | -    |      |      |

| trefi  | Average Refresh interval time                        |           | -       | 7.8  | -       | 7.8  | μs   |      |

| txsr   | Exit Self-Refresh to any Command                     |           | trc+tis | -    | trc+tis | -    | ns   |      |

<sup>\*</sup> CL is CAS Latency.

#### Note:

- 1. Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Absolute maximum DC requirements contain stress ratings only. Functional operation at the absolute maximum limits is not implied or guaranteed. Extended exposure to maximum ratings may affect device reliability.

- 2. All voltages are referenced to Vss. Overshoot V<sub>IH</sub> (Max) = 4.6V for pulse width ≤ 3ns. Undershoot V<sub>IL</sub> (Min) = -1.0V for pulse width ≤ 3ns.

- 3. These parameters depend on the cycle rate and these values are measured by the cycle rate under the minimum value of tck and tRc. Input signals are changed one time during every 2 tck.

- 4. These parameters depend on the output loading. Specified values are obtained with the output open.

- 5. Power-up sequence is described in Note 11.

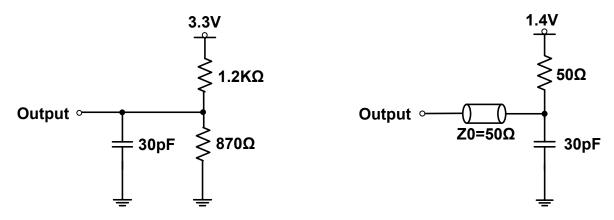

- 6. A.C. Test Conditions

- 7. These parameters are testing under the following conditions.

Operating temperature - Commercial:  $T_A$ = 0~70 °C Operating temperature - Industrial:  $T_A$ = -40~85 °C

#### Table 17. LVTTL Interface

| Reference Level of Output Signals                | 1.4V / 1.4V                            |

|--------------------------------------------------|----------------------------------------|

| Output Load                                      | Reference to the Under Output Load (B) |

| Input Signal Levels                              | 2.4V / 0.4V                            |

| Transition Time (Rise and Fall) of Input Signals | 1ns                                    |

| Reference Level of Input Signals                 | 1.4V                                   |

Figure 18.1 LVTTL D.C. Test Load (A)

Figure 18.2 LVTTL A.C. Test Load (B)

- 7. Transition times are measured between  $V_{IH}$  and  $V_{IL}$ . Transition (rise and fall) of input signals are in a fixed slope (1 ns).

- 8. thz defines the time in which the outputs achieve the open circuit condition and are not at reference levels.

- 9. If clock rising time is longer than 1 ns, (t<sub>R</sub> / 2 -0.5) ns should be added to the parameter.

- 10. Assumed input rise and fall time  $t_T$  ( $t_R \& t_F$ ) = 1 ns

If  $t_R$  or  $t_F$  is longer than 1 ns, transient time compensation should be considered, i.e., [(tr + tf)/2 - 1] ns should be added to the parameter.

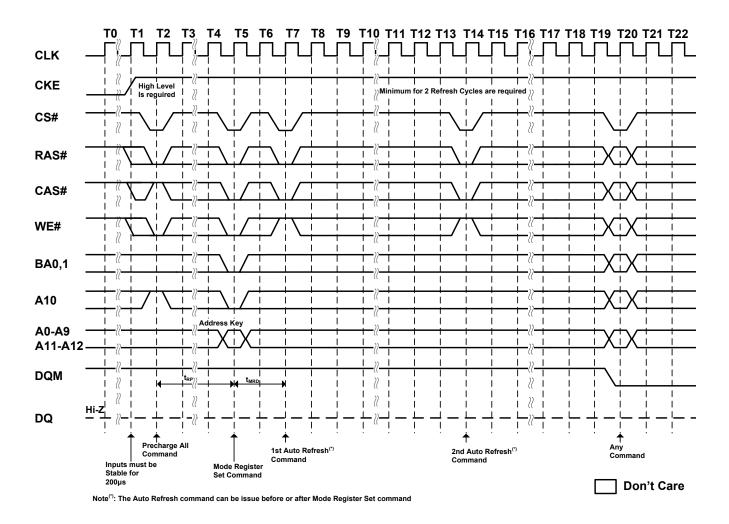

#### 11. Power up Sequence

Power up must be performed in the following sequence.

- 1) Power must be applied to V<sub>DD</sub> and V<sub>DDQ</sub> (simultaneously) when CKE= "LOW", DQM= "HIGH" and all input signals are held "NOP" state.

- 2) Start clock and maintain stable condition for minimum 200  $\mu$ s, then bring CKE "HIGH" and, it is recommended that DQM is held "HIGH" ( $V_{DD}$  levels) to ensure DQ output is in high impedance.

- 3) All banks must be precharged.

- 4) Mode Register Set command must be asserted to initialize the Mode register.

- 5) A minimum of 2 Auto-Refresh dummy cycles must be required to stabilize the internal circuitry of the device.

- \* The Auto Refresh command can be issue before or after Mode Register Set command

### **Timing Waveforms**

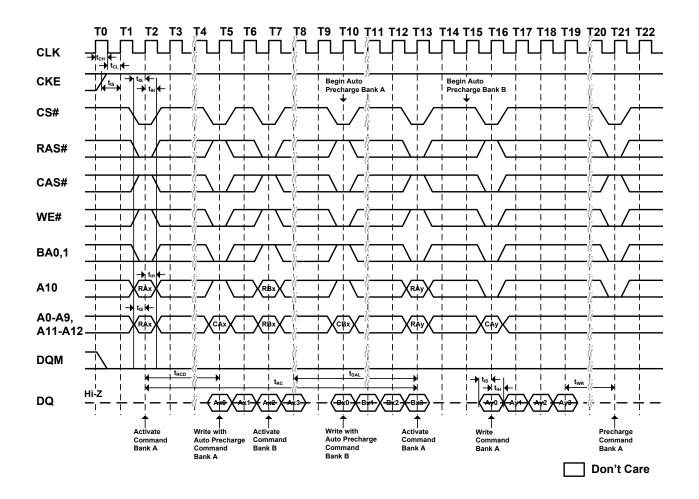

Figure 19. AC Parameters for Write Timing (Burst Length=4)

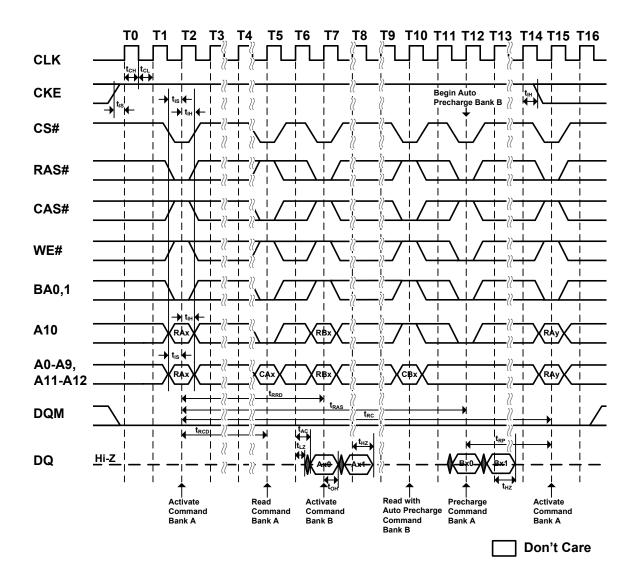

Figure 20. AC Parameters for Read Timing (Burst Length=2, CAS# Latency=2)

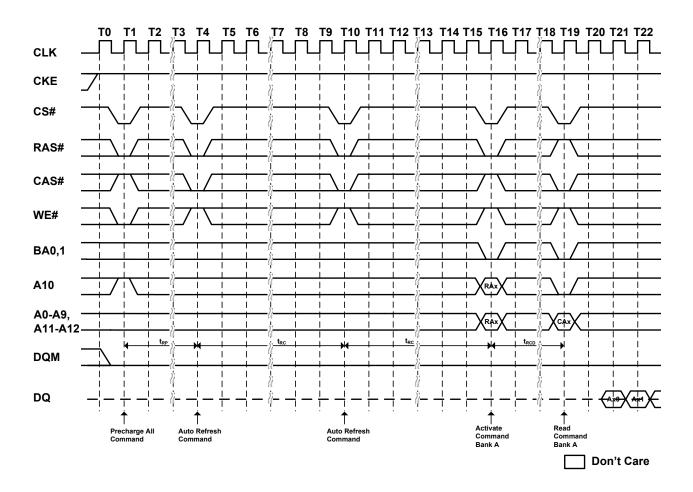

Figure 21. Auto Refresh (Burst Length=4, CAS# Latency=2)

Figure 22. Power on Sequence and Auto Refresh

Figure 23. Self Refresh Entry & Exit Cycle

#### Note: To Enter SelfRefresh Mode

- 1. CS#, RAS# & CAS# with CKE should be low at the same clock cycle.

- 2. After 1 clock cycle, all the inputs including the system clock can be don't care except for CKE.

- 3. The device remains in SelfRefresh mode as long as CKE stays "low".

- 4. Once the device enters SelfRefresh mode, minimum t<sub>RAS</sub> is required before exit from SelfRefresh.

#### To Exit SelfRefresh Mode

- 5. System clock restart and be stable before returning CKE high.

- 6. Enable CKE and CKE should be set high for valid setup time and hold time.

- 7. CS# starts from high.

- 8. Minimum txsR is required after CKE going high to complete SelfRefresh exit.

- 9. 8192 cycles of burst AutoRefresh is required before SelfRefresh entry and after SelfRefresh exit if the system uses burst refresh.

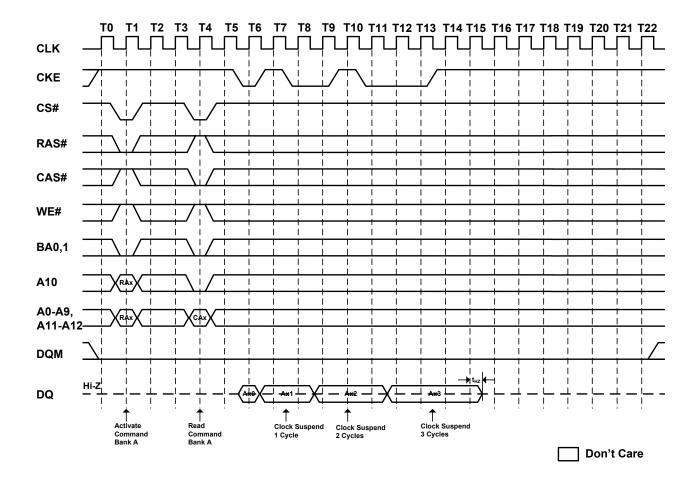

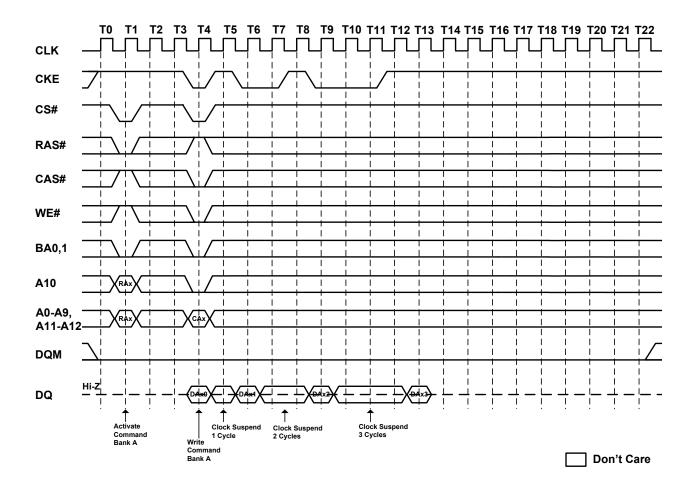

Figure 24.1. Clock Suspension During Burst Read (Using CKE)

(Burst Length=4, CAS# Latency=2)

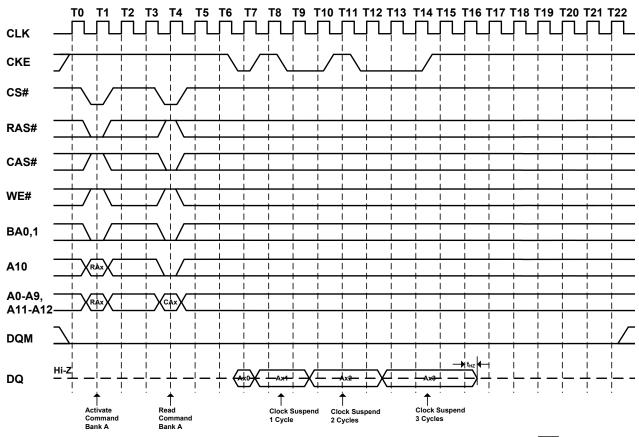

Figure 24.2. Clock Suspension During Burst Read (Using CKE) (Burst Length=4, CAS# Latency=3)

Don't Care

Figure 25. Clock Suspension During Burst Write (Using CKE) (Burst Length=4)

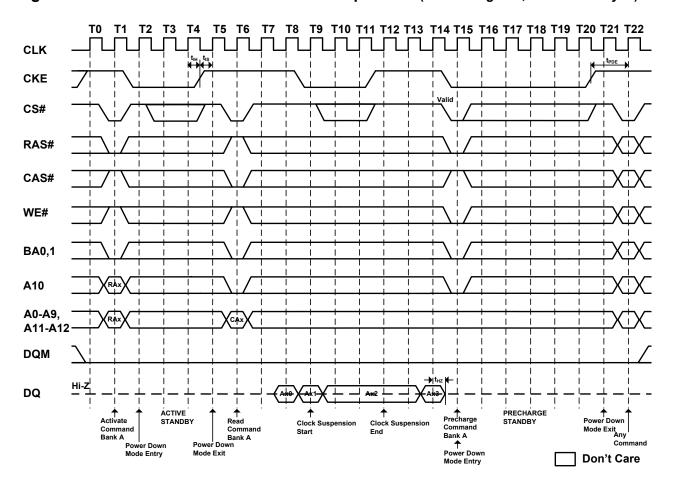

Figure 26. Power Down Mode and Clock Suspension (Burst Length=4, CAS# Latency=2)

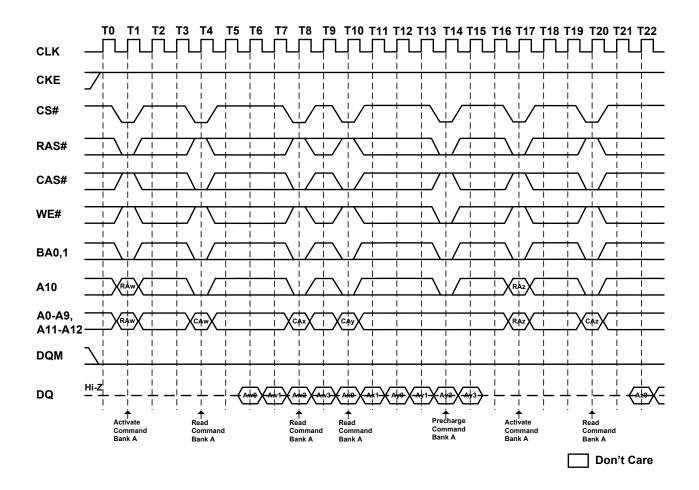

Figure 27.1. Random Column Read (Page within same Bank) (Burst Length=4, CAS# Latency=2)

Figure 27.2. Random Column Read (Page within same Bank) (Burst Length=4, CAS# Latency=3)

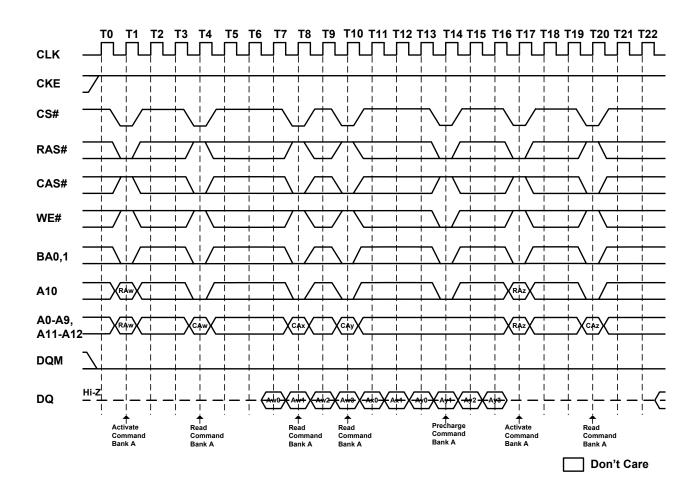

Figure 28. Random Column Write (Page within same Bank) (Burst Length=4)

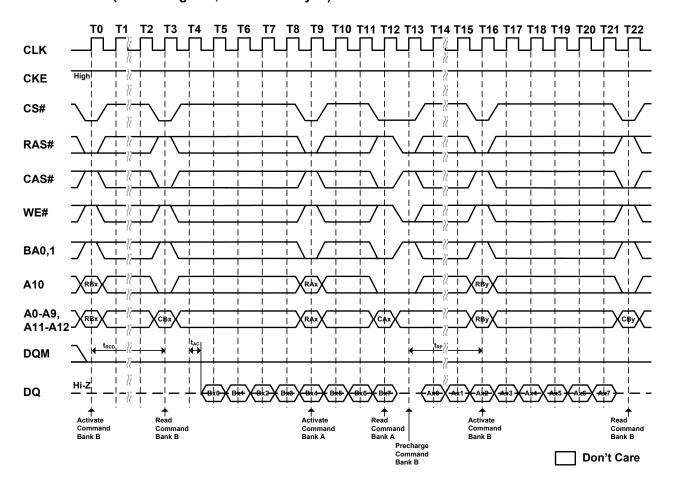

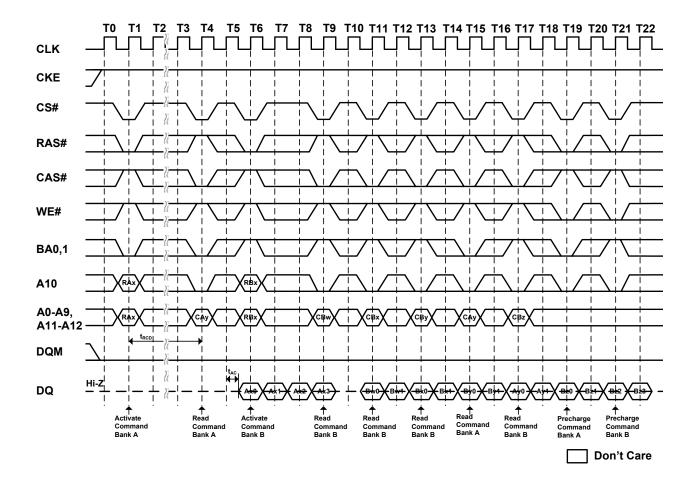

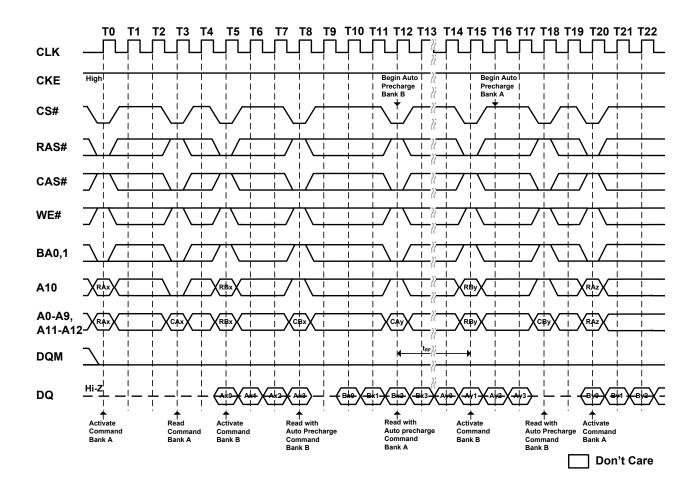

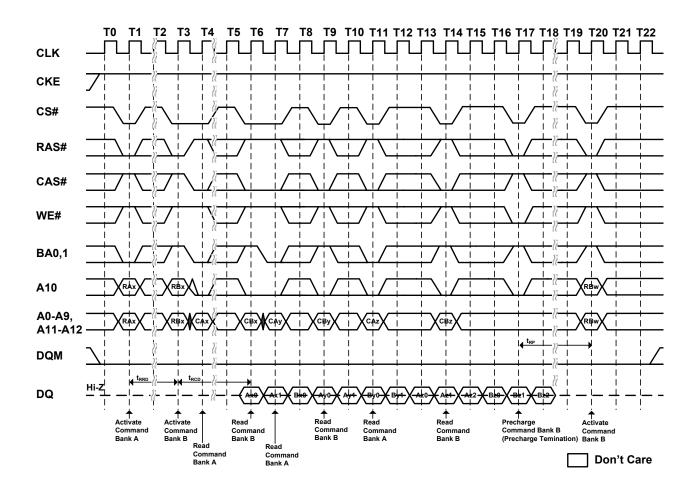

Figure 29.1. Random Row Read (Interleaving Banks)

(Burst Length=8, CAS# Latency=2)

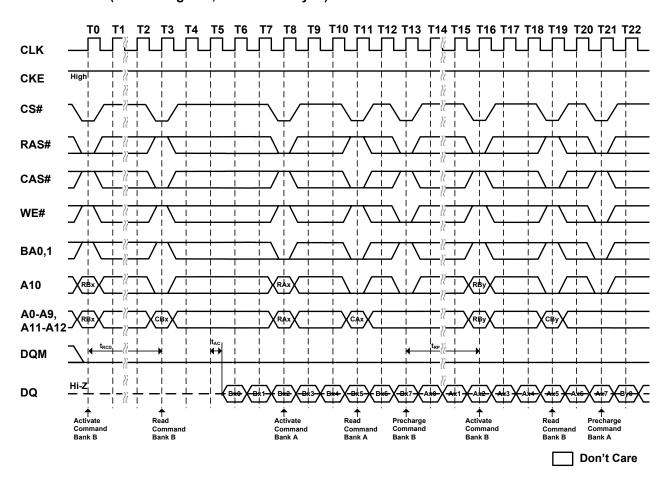

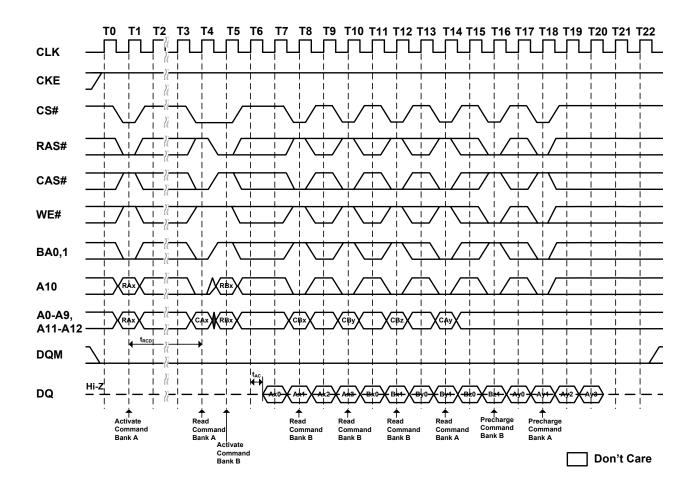

Figure 29.2. Random Row Read (Interleaving Banks)

(Burst Length=8, CAS# Latency=3)

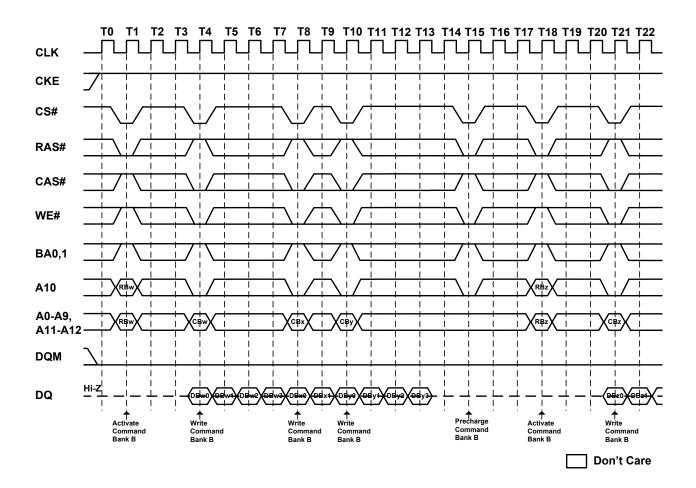

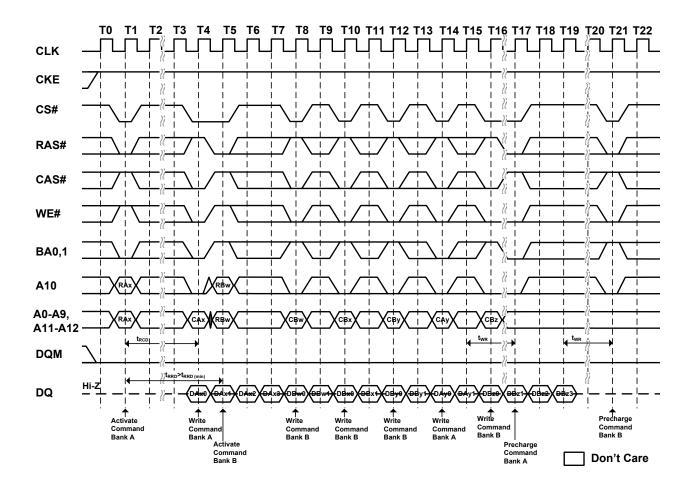

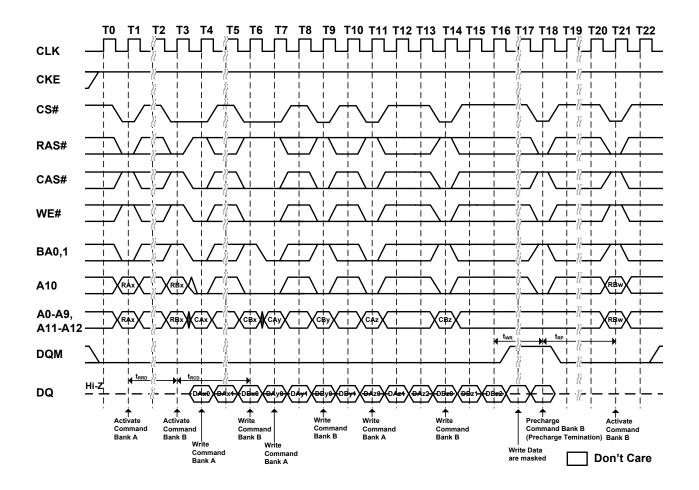

Figure 30. Random Row Write (Interleaving Banks)

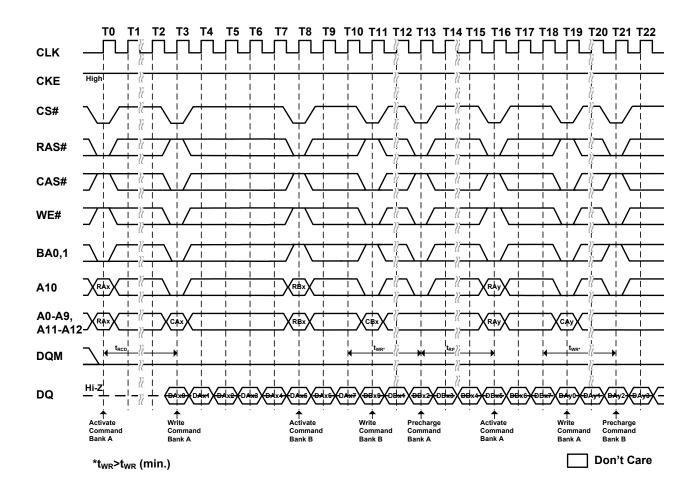

(Burst Length=8)

Figure 31.1. Read and Write Cycle (Burst Length=4, CAS# Latency=2)

Figure 31.2. Read and Write Cycle (Burst Length=4, CAS# Latency=3)

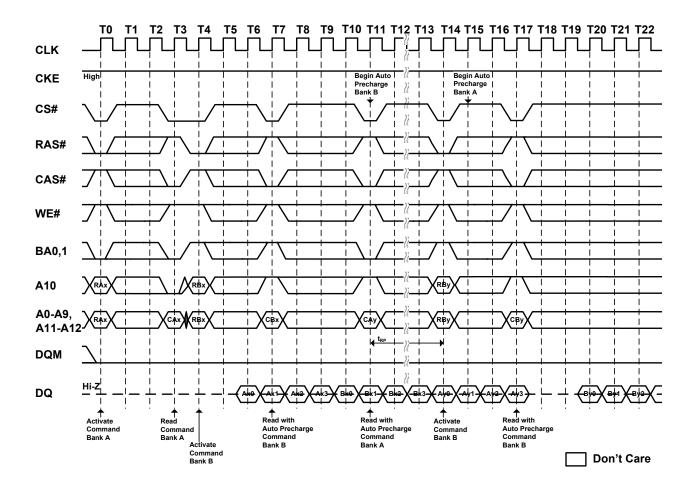

Figure 32.1. Interleaving Column Read Cycle (Burst Length=4, CAS# Latency=2)

Figure 32.2. Interleaved Column Read Cycle (Burst Length=4, CAS# Latency=3)

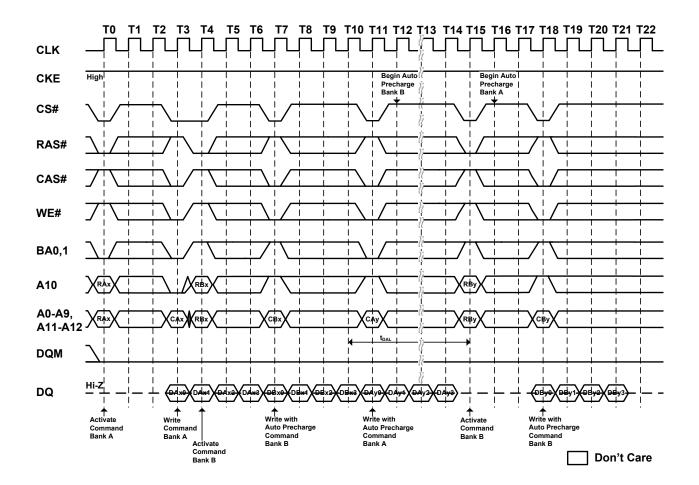

Figure 33. Interleaved Column Write Cycle (Burst Length=4)

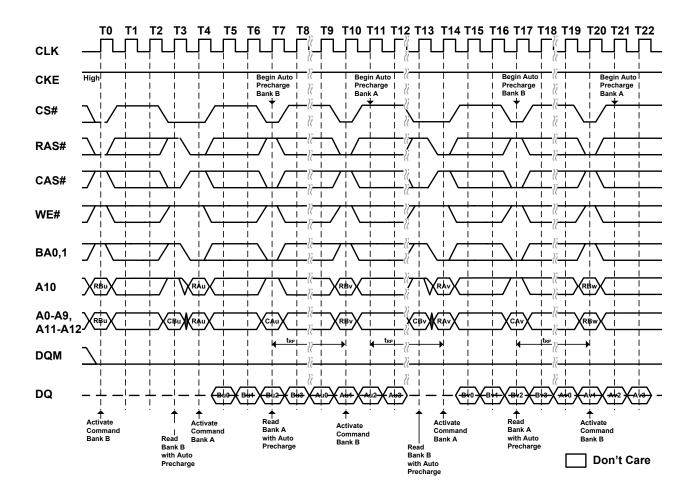

Figure 34.1. Auto Precharge after Read Burst (Burst Length=4, CAS# Latency=2)

Figure 34.2. Auto Precharge after Read Burst (Burst Length=4, CAS# Latency=3)

Figure 35. Auto Precharge after Write Burst (Burst Length=4)

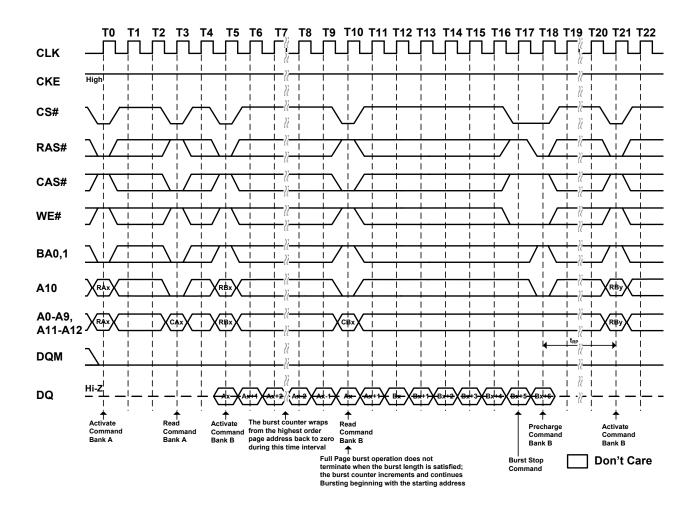

Figure 36.1. Full Page Read Cycle (Burst Length=Full Page, CAS# Latency=2)

Figure 36.2. Full Page Read Cycle (Burst Length=Full Page, CAS# Latency=3)

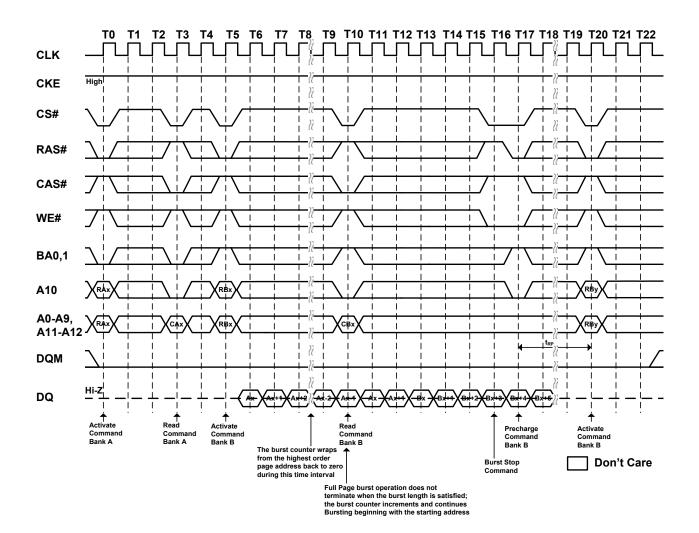

Figure 37. Full Page Write Cycle (Burst Length=Full Page)

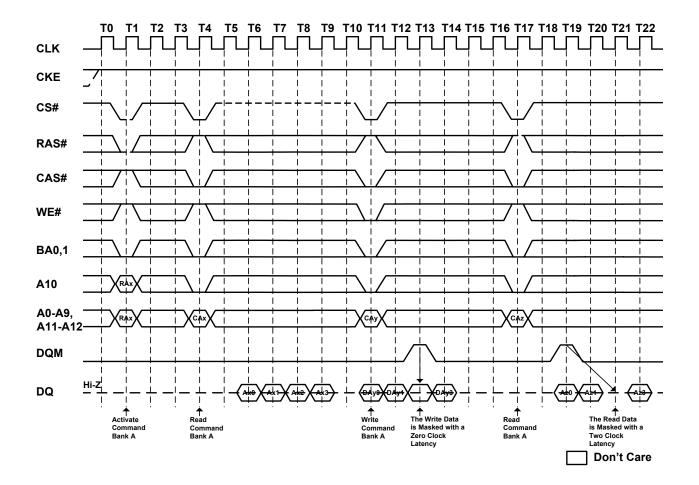

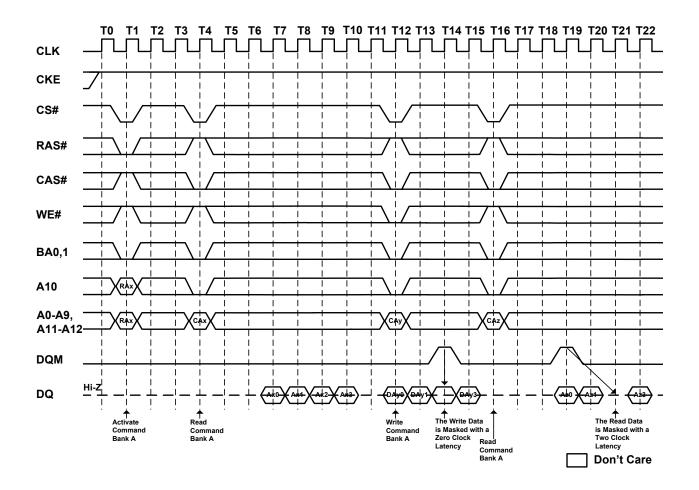

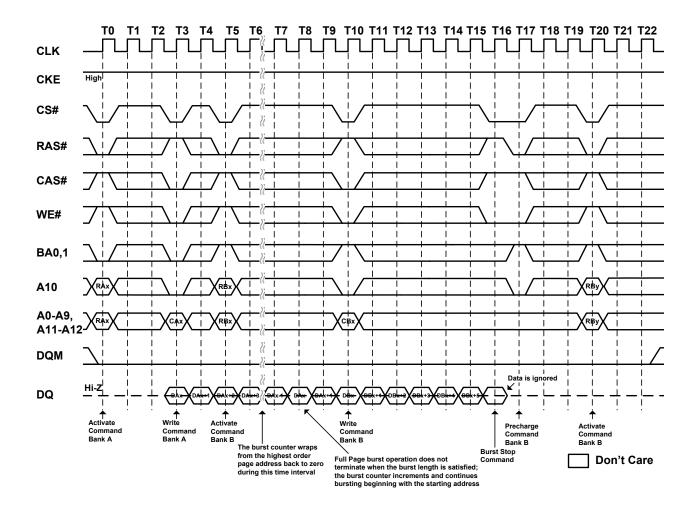

Figure 38. Byte Read and Write Operation (Burst Length=4, CAS# Latency=2)

Figure 39. Random Row Read (Interleaving Banks)

(Burst Length=4, CAS# Latency=2)

Figure 40. Full Page Random Column Read (Burst Length=Full Page, CAS# Latency=2)

Figure 41. Full Page Random Column Write (Burst Length=Full Page)

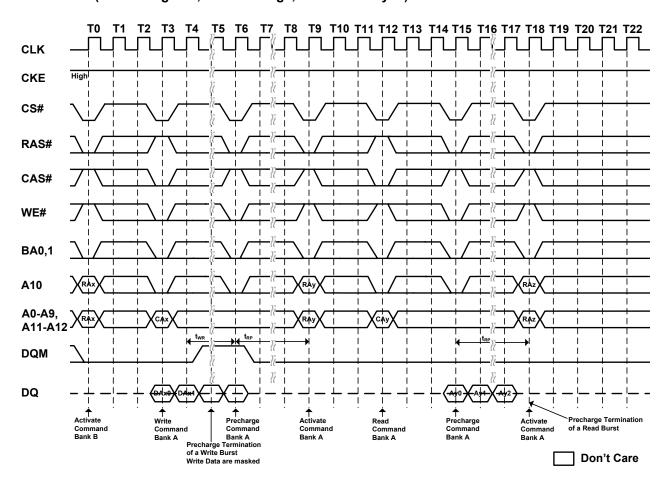

Figure 42. Precharge Termination of a Burst (Burst Length=4, 8 or Full Page, CAS# Latency=3)

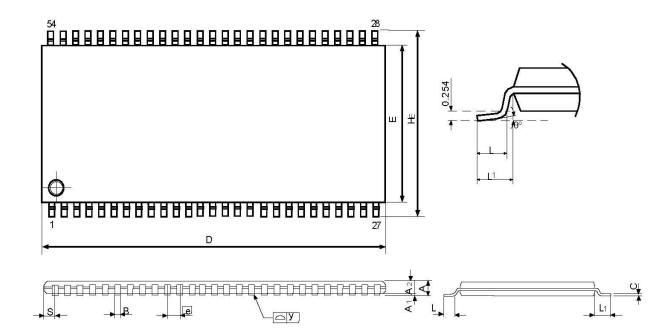

Figure 43. 54 Pin TSOP II Package Outline Drawing Information

| Symbol | Dimension in inch |       |       | Dimension in mm |       |       |

|--------|-------------------|-------|-------|-----------------|-------|-------|

|        | Min               | Nom   | Max   | Min             | Nom   | Max   |

| Α      |                   |       | 0.047 |                 |       | 1.2   |

| A1     | 0.002             |       | 0.008 | 0.05            |       | 0.2   |

| A2     | 0.035             | 0.039 | 0.043 | 0.9             | 1.0   | 1.1   |

| В      | 0.01              | 0.014 | 0.018 | 0.25            | 0.35  | 0.45  |

| С      | 0.004             | 0.006 | 0.008 | 0.12            | 0.165 | 0.21  |

| D      | 0.87              | 0.875 | 0.88  | 22.09           | 22.22 | 22.35 |

| E      | 0.395             | 0.400 | 0.405 | 10.03           | 10.16 | 10.29 |

| е      |                   | 0.031 |       |                 | 0.8   |       |

| HE     | 0.455             | 0.463 | 0.471 | 11.56           | 11.76 | 11.96 |

| L      | 0.016             | 0.02  | 0.024 | 0.4             | 0.5   | 0.6   |

| L1     |                   | 0.032 |       |                 | 0.84  |       |

| S      |                   | 0.028 |       |                 | 0.71  |       |

| У      |                   |       | 0.004 |                 |       | 0.1   |

| θ      | 0°                |       | 8°    | 0°              |       | 8°    |

Confidential - 54 of 55 - Rev.1.0 June 2017

#### PART NUMBERING SYSTEM

| AS4C | 32M8SA                           | 6/7                  | T          | C/I                                                            | N                                   | XX                                   |

|------|----------------------------------|----------------------|------------|----------------------------------------------------------------|-------------------------------------|--------------------------------------|

| DRAM | 32M8=32Mx8<br>S=SDRAM<br>A=A die | 6=166MHz<br>7=143MHz | T = TSOPII | C=Commercial<br>0°C to +70°C<br>I=Industrial<br>-40°C to +85°C | Indicates Pb<br>and<br>Halogen Free | Packing Type<br>None:Tray<br>TR:Reel |

Alliance Memory, Inc. 511 Taylor Way, San Carlos, CA 94070 Tel: 650-610-6800 Fax: 650-620-9211

www.alliancememory.com

Copyright © Alliance Memory All Rights Reserved

© Copyright 2007 Alliance Memory, Inc. All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development. significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against all claims arising from such use.