UCD9081

SLVS813C -JUNE 2008-REVISED NOVEMBER 2016

# UCD9081 8-Channel Power Supply Sequencer and Monitor With Error Logging

### 1 Features

- Single Supply Voltage: 3.3 V

- Low Power Consumption: 3-mA Nominal Supply Current

- Sequences and Monitors Eight Voltage Rails

- Rail Voltages Sampled With 3.2-mV Resolution

- Internal or External Voltage Reference

- Four Configurable Digital Outputs for Power-On-Reset and Other Functions

- Configurable Digital Output Polarity

- Flexible Rail Sequencing Based on Timeline (ms), Parent Rail Regulation Window, or Parent Rail Achieving Defined Threshold

- Independent Under- and Overvoltage Thresholds Per Rail

- Configurable Regulation Expiration Times Per Rail

- Flexible Alarm Processing: Ignore, Log Only, Retry n Times, Retry Continuously, Sequence, Parent Rail Can Shutdown Child Rails

- Alarm Conditions Logged With Timestamp: Underand Overvoltage Glitch, Sustained Under- and Overvoltage, Rail Did Not Start

- On-Chip Flash for Storing User Data

- Error Logging to Flash for System Failure Analysis

- I<sup>2</sup>C<sup>™</sup> Interface for Configuration and Monitoring

- Microsoft Windows™ GUI for Configuration and Monitoring

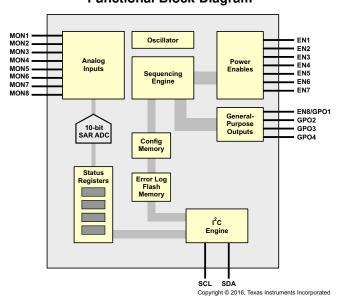

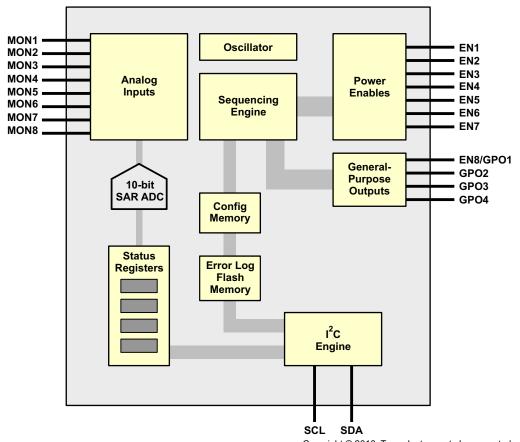

## **Functional Block Diagram**

## 2 Applications

- Telecommunications Switches

- Servers

- · Networking Equipment

- Test Equipment

- Industrial

- Any System Requiring Sequencing of Multiple Voltage Rails

## 3 Description

The UCD9081 power-supply sequencer controls the enable sequence of up to eight independent voltage rails and provides four general-purpose digital outputs (GPO). The device operates from a 3.3-V supply, provides 3.2-mV resolution of voltage rails, and requires no external memory or clock. The UCD9081 monitors the voltage rails independently and has a high degree of rail sequence and alarm response options. The sequencing of rails can be based on timed events or on timed events in conjunction with other rails achieving regulation or a voltage threshold. In addition, each rail is monitored for undervoltage and overvoltage glitches and thresholds. Each rail the UCD9081 monitors can be configured to shut down a user-defined set of other rails and GPOs, and alarm conditions are monitored on a per-rail basis.

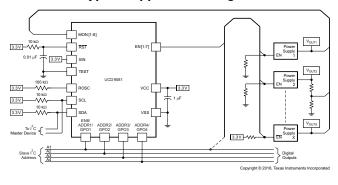

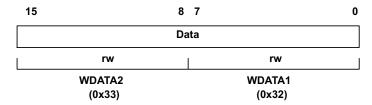

Figure 20 shows the UCD9081 power-supply sequencer in a typical application.

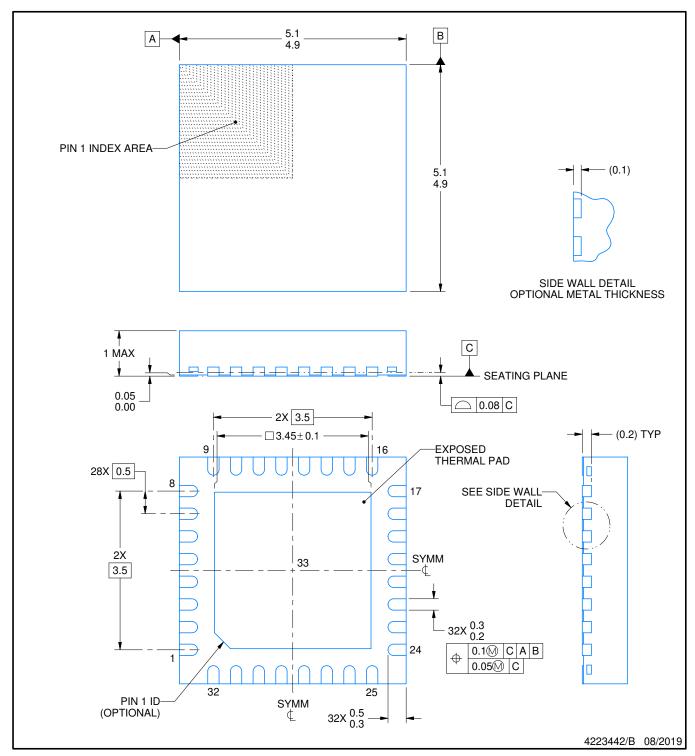

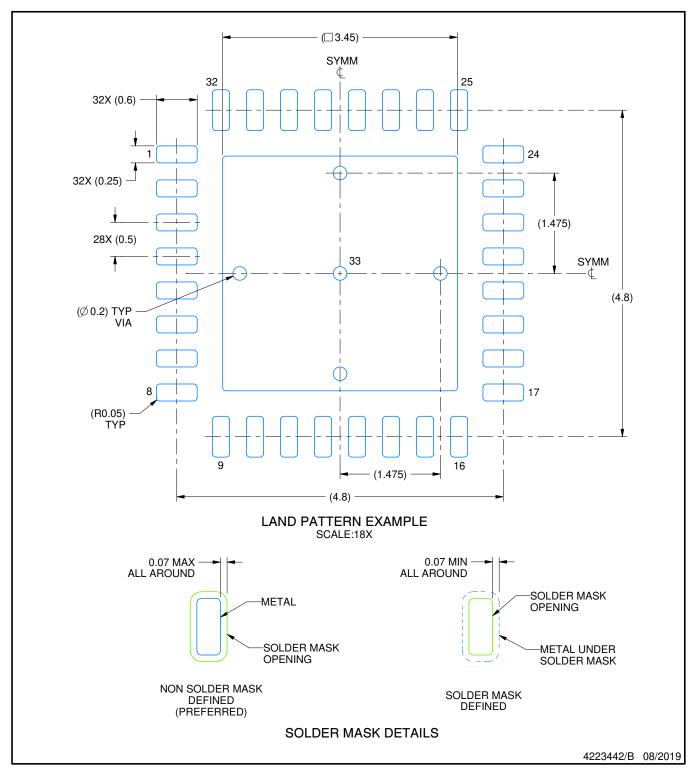

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| UCD9081     | VQFN (32) | 5.00 mm × 5.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

#### **Typical Application Diagram**

Page

## **Table of Contents**

| 1 | Features 1                                          |    | 8.5 Programming                                      | 1    |

|---|-----------------------------------------------------|----|------------------------------------------------------|------|

| 2 | Applications 1                                      |    | 8.6 Register Maps                                    | 18   |

| 3 | Description 1                                       | 9  | Application and Implementation                       | . 24 |

| 4 | Revision History2                                   |    | 9.1 Application Information                          | . 24 |

| 5 | Pin Configuration and Functions3                    |    | 9.2 Typical Application                              | . 2  |

| 6 | Specifications5                                     | 10 | Power Supply Recommendations                         | . 28 |

| • | 6.1 Absolute Maximum Ratings                        | 11 | Layout                                               | . 28 |

|   | 6.2 Recommended Operating Conditions                |    | 11.1 Layout Guidelines                               | 28   |

|   | 6.3 Thermal Information                             |    | 11.2 Layout Example                                  | 28   |

|   | 6.4 Electrical Characteristics                      | 12 | Device and Documentation Support                     | . 29 |

|   | 6.5 Timing Requirements: I <sup>2</sup> C Interface |    | 12.1 Documentation Support                           | 2    |

|   | 6.6 Typical Characteristics                         |    | 12.2 Receiving Notification of Documentation Updates | s 2  |

| 7 | Parameter Measurement Information 8                 |    | 12.3 Community Resources                             | 29   |

| 8 | Detailed Description9                               |    | 12.4 Trademarks                                      | 29   |

| • | 8.1 Overview                                        |    | 12.5 Electrostatic Discharge Caution                 | 2    |

|   | 8.2 Functional Block Diagram9                       |    | 12.6 Glossary                                        | . 29 |

|   | 8.3 Feature Description                             | 13 | Mechanical, Packaging, and Orderable Information     | 20   |

|   | 8.4 Device Functional Modes11                       |    |                                                      | . 2  |

# 4 Revision History

Changes from Revision B (December 2010) to Revision C

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| •        | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section | 1         |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| •        | Deleted Ordering Information table; see POA at the end of the data sheet                                                                                                                                                                                                            | 1         |

| •        | Added Thermal Information table                                                                                                                                                                                                                                                     | 5         |

| •        | Moved Timing Parameters for PC Interface table and PC Timing diagram to Specifications                                                                                                                                                                                              | 6         |

| •        | Moved content in Monitoring the UCD9081 to Register Maps                                                                                                                                                                                                                            | 18        |

|          | hanges from Revision A (September 2008) to Revision B  Added Note 1 to the PIN FUNCTIONS table                                                                                                                                                                                      | Page<br>3 |

| •        |                                                                                                                                                                                                                                                                                     |           |

| •        | Added Note regarding state of enable and digital I/O pins when the device contains factory configuration                                                                                                                                                                            |           |

| <u>.</u> | Added a reference to the UCD9081 Programming Guide                                                                                                                                                                                                                                  | 16        |

| C        | hanges from Original (June 2008) to Revision A                                                                                                                                                                                                                                      | Page      |

| •        | Changed the data sheet from Product Preview to Production; multiple changes throughout                                                                                                                                                                                              | 1         |

| •        | Changed first RAIL voltage equation From: × V <sub>REF</sub> To: × V <sub>R+</sub>                                                                                                                                                                                                  | 19        |

Product Folder Links: UCD9081

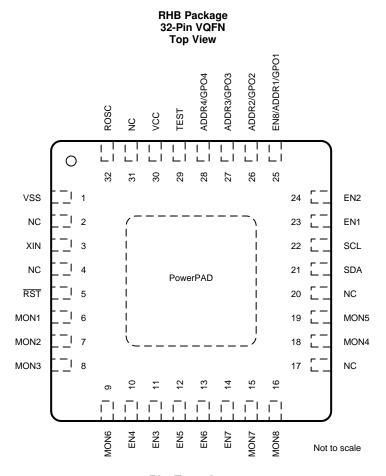

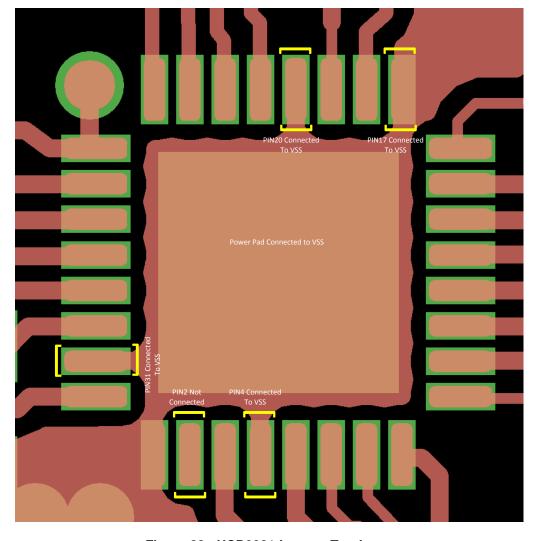

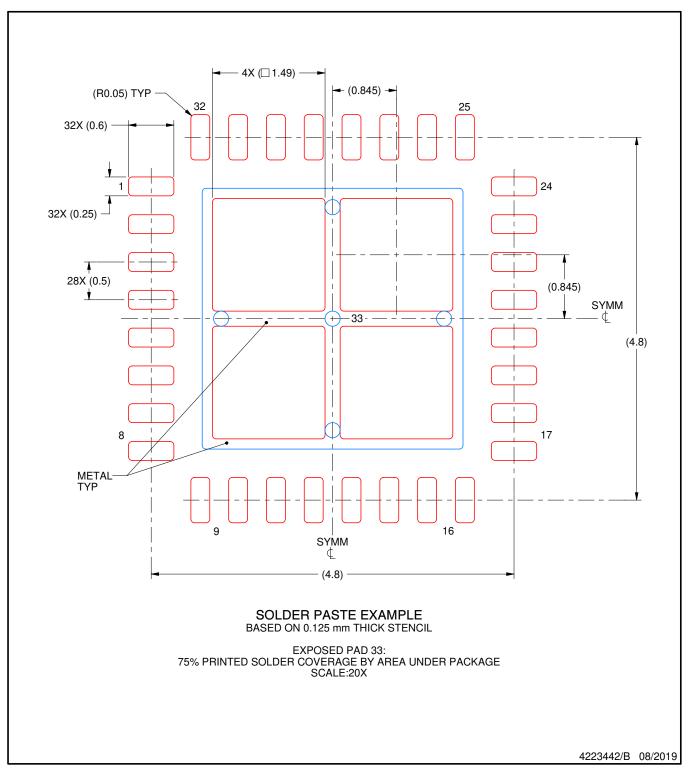

# 5 Pin Configuration and Functions

**Pin Functions**

| PIN <sup>(1)</sup> |     | 1/0 | DECODIDATION                                                                                                |  |  |

|--------------------|-----|-----|-------------------------------------------------------------------------------------------------------------|--|--|

| NAME               | NO. | I/O | DESCRIPTION                                                                                                 |  |  |

| ADDR2/GPO2         | 26  | I/O | I <sup>2</sup> C address select 2, general-purpose digital output 2                                         |  |  |

| ADDR3/GPO3         | 27  | I/O | I <sup>2</sup> C address select 3, general-purpose digital output 3                                         |  |  |

| ADDR4/GPO4         | 28  | I/O | I <sup>2</sup> C address select 4, general-purpose digital output 4                                         |  |  |

| EN1                | 23  | I/O | Voltage rail 1 enable (digital output)                                                                      |  |  |

| EN2                | 24  | I/O | Voltage rail 2 enable (digital output)                                                                      |  |  |

| EN3                | 11  | I/O | Voltage rail 3 enable (digital output)                                                                      |  |  |

| EN4                | 10  | I/O | Voltage rail 4 enable (digital output)                                                                      |  |  |

| EN5                | 12  | I/O | Voltage rail 5 enable (digital output)                                                                      |  |  |

| EN6                | 13  | I/O | Voltage rail 6 enable (digital output)                                                                      |  |  |

| EN7                | 14  | I/O | Voltage rail 7 enable (digital output)                                                                      |  |  |

| EN8/ADDR1/<br>GPO1 | 25  | I/O | Voltage rail 8 enable (digital output), I <sup>2</sup> C address select 1, general-purpose digital output 1 |  |  |

| MON1               | 6   | ı   | Analog input for voltage rail 1                                                                             |  |  |

| MON2               | 7   | I   | Analog input for voltage rail 2                                                                             |  |  |

| MON3               | 8   | I   | Analog input for voltage rail 3                                                                             |  |  |

| MON4               | 18  | 1   | Analog input for voltage rail 4                                                                             |  |  |

<sup>(1)</sup> Enable and GPIO pins are in high-impedance state when a device is received from factory and during the first configuration programming done by customer.

# Pin Functions (continued)

| PIN <sup>(</sup> | N <sup>(1)</sup> |     | DECORPORTION                                                                                                                                          |  |

|------------------|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME             | NO.              | I/O | DESCRIPTION                                                                                                                                           |  |

| MON5             | 19               | 1   | Analog input for voltage rail 5                                                                                                                       |  |

| MON6             | 9                | - 1 | Analog input for voltage rail 6                                                                                                                       |  |

| MON7             | 15               | - 1 | Analog input for voltage rail 7                                                                                                                       |  |

| MON8             | 16               | - 1 | Analog input for voltage rail 8                                                                                                                       |  |

| NC               | 2                | _   | Do not connect                                                                                                                                        |  |

| NC               | 4, 17,<br>20, 31 | _   | Recommended to connect to V <sub>SS</sub> , pin is not connected internally                                                                           |  |

| ROSC             | 32               | _   | Internal oscillator frequency adjust. Must use 100-k $\Omega$ pullup to $V_{CC}$ for minimum drift and maximum frequency when sampling voltage rails. |  |

| RST              | 5                | - 1 | Reset input                                                                                                                                           |  |

| SCL              | 22               | I/O | I <sup>2</sup> C clock. Must pull up to 3.3 V.                                                                                                        |  |

| SDA              | 21               | I/O | I <sup>2</sup> C data. Must pull up to 3.3 V.                                                                                                         |  |

| TEST             | 29               | - 1 | Connect to V <sub>SS</sub>                                                                                                                            |  |

| V <sub>CC</sub>  | 30               | _   | Supply voltage                                                                                                                                        |  |

| $V_{SS}$         | 1                | _   | Ground reference                                                                                                                                      |  |

| XIN              | 3                | _   | Connect to V <sub>CC</sub>                                                                                                                            |  |

| PowerPAD™        | _                | _   | Package pad. Recommended to connect to V <sub>SS</sub> .                                                                                              |  |

## 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                         | MIN  | MAX            | UNIT |

|---------------------------------------------------------|------|----------------|------|

| Voltage applied from V <sub>CC</sub> to V <sub>SS</sub> | -0.3 | 4.1            | V    |

| Voltage applied to any pin <sup>(2)</sup>               | -0.3 | $V_{CC} + 0.3$ | V    |

| ESD diode current at any device terminal                |      | ±2             | mA   |

| Storage temperature, T <sub>stq</sub>                   | -40  | 85             | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages referenced to V<sub>SS</sub>.

## 6.2 Recommended Operating Conditions

|                |                                                           | MIN | NOM | MAX | UNIT |

|----------------|-----------------------------------------------------------|-----|-----|-----|------|

| $V_{CC}$       | Supply voltage during operation and configuration changes | 3   | 3.3 | 3.6 | V    |

| T <sub>A</sub> | Operating free-air temperature                            | -40 |     | 85  | °C   |

#### 6.3 Thermal Information

|                        |                                              | UCD9081    |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | RHB (VQFN) | UNIT |

|                        |                                              | 32 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 32.1       | °C/W |

| R <sub>0</sub> JC(top) | Junction-to-case (top) thermal resistance    | 18.1       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6          | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.2        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 5.9        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.2        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

#### 6.4 Electrical Characteristics

These specifications are over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                                                                | PARAMETER                              | TEST CONDITIONS                                                         | MIN                   | TYP | MAX                   | UNIT |

|----------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| SUPPLY C                                                       | CURRENT                                |                                                                         |                       |     |                       |      |

| Is                                                             | Supply current into V <sub>CC</sub>    | T <sub>A</sub> = 25°C, excluding external current                       |                       | 3   | 4                     | mA   |

| I <sub>C</sub>                                                 | Supply current during configuration    | V <sub>CC</sub> = 3.6 V                                                 |                       | 3   | 7                     | mA   |

| STANDAR                                                        | ID INPUTS (RST, TEST)                  |                                                                         |                       |     |                       |      |

| V <sub>IL</sub>                                                | Low-level input voltage                | V <sub>CC</sub> = 3 V                                                   | V <sub>SS</sub>       |     | V <sub>SS</sub> + 0.6 | V    |

| V <sub>IH</sub>                                                | High-level input voltage               | V <sub>CC</sub> = 3 V                                                   | 0.8 × V <sub>CC</sub> |     | V <sub>CC</sub>       | ٧    |

| SCHMITT TRIGGER INPUTS (SDA, SCL, EN[17], EN8/ADDR1, ADDR[24]) |                                        |                                                                         |                       |     |                       |      |

| V <sub>IT+</sub>                                               | Positive-going input threshold voltage | V <sub>CC</sub> = 3 V                                                   | 1.5                   |     | 1.9                   | V    |

| $V_{IT-}$                                                      | Negative-going input threshold voltage | V <sub>CC</sub> = 3 V                                                   | 0.9                   |     | 1.3                   | V    |

| $V_{hys}$                                                      | Input voltage hysteresis               | $V_{CC} = 3 \text{ V}, V_{IT+} - V_{IT-}$                               | 0.5                   |     | 1                     | V    |

| I <sub>lkg</sub>                                               | High-impedance leakage current         |                                                                         |                       |     | ±50                   | nA   |

| ANALOG I                                                       | INPUTS (MONx, ROSC)                    |                                                                         | •                     |     | '                     |      |

| V <sub>CC</sub>                                                | Analog supply voltage                  | V <sub>SS</sub> = 0 V                                                   | 3                     |     | 3.6                   | ٧    |

|                                                                |                                        | Internal voltage reference selected                                     | 0                     |     | 2.5                   |      |

| V <sub>MON&lt;18&gt;</sub>                                     | Analog input voltage                   | External voltage reference selected (V <sub>CC</sub> used as reference) | 0                     |     | V <sub>CC</sub>       | V    |

## **Electrical Characteristics (continued)**

These specifications are over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                                  | PARAMETER                                             | TEST CO                                                               | ONDITIONS                                              | MIN                    | TYP                        | MAX                    | UNIT   |

|----------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------|------------------------|----------------------------|------------------------|--------|

| C <sub>I</sub> <sup>(1)</sup>    | Input capacitance                                     | Only one terminal car<br>(MON1 to MON8)                               | n be selected at a time                                |                        |                            | 27                     | pF     |

| R <sub>I</sub> <sup>(1)</sup>    | Input MUX ON resistance                               | $0 \text{ V} \leq V_{MONx} \leq V_{CC}, \text{ V}$                    | <sub>CC</sub> = 3 V                                    |                        |                            | 2000                   | Ω      |

| I <sub>lkg</sub>                 | High-impedance leakage current                        | MON1 to MON8                                                          |                                                        |                        |                            | ±50                    | nA     |

| V <sub>REF+</sub>                | Positive internal reference voltage                   | Internal voltage refere                                               | ence selected,                                         | 2.35                   | 2.5                        | 2.65                   | ٧      |

| V                                | ADO total consultinated consu                         | V 0.V                                                                 | V <sub>R+</sub> = 2.5 V<br>(internal reference)        |                        |                            | ±12.2                  |        |

| V <sub>TUE</sub>                 | ADC total unadjusted error                            | V <sub>CC</sub> = 3 V                                                 | V <sub>R+</sub> = V <sub>CC</sub> (external reference) |                        |                            | ±14.7                  | mV     |

| T <sub>REF+</sub> <sup>(1)</sup> | Temperature coefficient of internal voltage reference | I <sub>(VREF+)</sub> is a constant of mA ≤ I <sub>(VREF+)</sub> ≤ 1 m |                                                        |                        |                            | ±100                   | ppm/°C |

| MISCELLA                         | NEOUS                                                 |                                                                       |                                                        |                        |                            |                        |        |

| T <sub>retention</sub>           | Retention of configuration parameters                 | T <sub>J</sub> = 25°C                                                 |                                                        | 100                    |                            |                        | Years  |

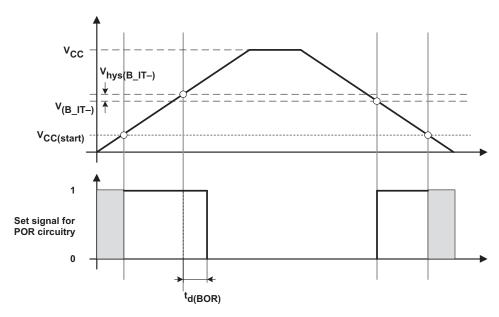

| POR, BRO                         | WNOUT, RESET <sup>(2)(3)</sup>                        |                                                                       |                                                        |                        |                            |                        |        |

| t <sub>d(BOR)</sub>              | Brownout                                              |                                                                       |                                                        |                        |                            | 2000                   | μs     |

| V <sub>CC(start)</sub>           | Brownout                                              | dV <sub>CC</sub> /dt ≤ 3 V/s                                          |                                                        |                        | 0.7 × V <sub>(B_IT-)</sub> |                        | V      |

| V <sub>(B_IT-)</sub>             | Brownout                                              | dV <sub>CC</sub> /dt ≤ 3 V/s                                          |                                                        |                        |                            | 1.71                   | V      |

| V <sub>hys(B_IT-)</sub>          | Brownout                                              | dV <sub>CC</sub> /dt ≤ 3 V/s                                          |                                                        | 70                     | 130                        | 180                    | mV     |

| t <sub>(reset)</sub>             | Brownout                                              | Pulse length required reset internally, V <sub>CC</sub> =             | at RST pin to accept<br>3 V                            | 2                      |                            |                        | μs     |

| DIGITAL O                        | OUTPUTS (EN8/GPO1, GPO[24], EN[17],                   | SDA, SCL)                                                             |                                                        |                        |                            |                        |        |

| V                                | I Bala lavral autorituralta ar-                       | $I_{OH}$ max = -1.5 mA <sup>(4)</sup> ,                               | V <sub>CC</sub> = 3 V                                  | V <sub>CC</sub> - 0.25 |                            | V <sub>CC</sub>        | V      |

| V <sub>OH</sub>                  | High-level output voltage                             | $I_{OH}$ max = -6 mA <sup>(5)</sup> , V                               | <sub>CC</sub> = 3 V                                    | V <sub>CC</sub> - 0.6  |                            | V <sub>CC</sub>        | V      |

| V                                | Law lavel output voltage                              | $I_{OL}$ max = 1.5 mA <sup>(4)</sup> , V                              | / <sub>CC</sub> = 3 V                                  | V <sub>SS</sub>        |                            | V <sub>SS</sub> + 0.25 | V      |

| V <sub>OL</sub>                  | Low-level output voltage                              | $I_{OL}$ max = 6 mA <sup>(5)</sup> , $V_{C}$                          | <sub>C</sub> = 3 V                                     | V <sub>SS</sub>        |                            | $V_{SS} + 0.6$         | V      |

| I <sub>lkg</sub>                 | High-impedance leakage current                        | V <sub>CC</sub> = 3 V                                                 |                                                        |                        |                            | ±50                    | nA     |

- Not production tested. Limits verified by design.

- The current consumption of the brown-out module is already included in the  $I_{CC}$  current consumption data.

- During power up, device initialization starts following a period of  $t_{d(BOR)}$  after  $V_{CC} = V_{(B\_IT-)} + V_{hys(B\_IT-)}$ . The maximum total current,  $I_{OH}$  max and  $I_{OL}$  max, for all outputs combined, must not exceed ±12 mA to hold the maximum voltage drop specified.

- The maximum total current, I<sub>OH</sub>max and I<sub>OL</sub>max, for all outputs combined, must not exceed ±48 mA to hold the maximum voltage drop

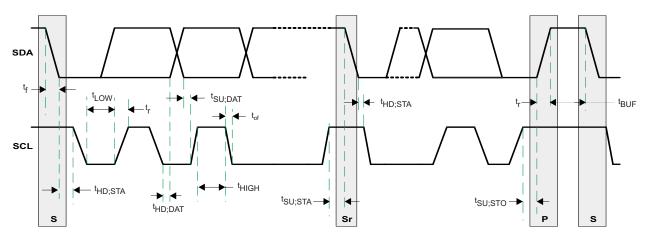

## 6.5 Timing Requirements: I<sup>2</sup>C Interface

|                     |                                                                                                                     | MIN  | MAX                 | UNIT |

|---------------------|---------------------------------------------------------------------------------------------------------------------|------|---------------------|------|

| t <sub>ofof</sub>   | Output fall time from V <sub>OH</sub> to V <sub>OL</sub> <sup>(1)</sup> with a bus capacitance from 10 pF to 400 pF |      | 250 <sup>(2)</sup>  | ns   |

| Cı                  | Capacitance for each pin                                                                                            |      | 10                  | pF   |

| f <sub>SCL</sub>    | SCL clock frequency                                                                                                 | 10   | 100                 | kHz  |

| t <sub>HD;STA</sub> | Repeated hold time START condition (after this period, the first clock pulse is generated)                          | 4    |                     | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                                                                                      | 0(3) | 3.45 <sup>(4)</sup> | μs   |

| $t_{LOW}$           | LOW period of the SCL clock                                                                                         | 4.7  |                     | μs   |

| t <sub>HIGH</sub>   | HIGH period of the SCL clock                                                                                        | 4    |                     | μs   |

| t <sub>SU;STA</sub> | Setup time for repeated start condition                                                                             | 4.7  |                     | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                                                                                     | 250  |                     | ns   |

- See Electrical Characteristics

- The maximum t<sub>f</sub> for the SDA and SCL bus lines (300 ns) is longer than the specified maximum t<sub>of</sub> for the output stages (250 ns). This allows series protection resistors,  $R_s$ , to be connected between the SDA/SCL pins and the SDA/SCL bus lines without exceeding the maximum specified tf.

- A device must internally provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL.

- The maximum t<sub>HD:DAT</sub> must only be met if the device does not stretch the LOW period (t<sub>LOW</sub>) of the SCL signal. (4)

# Timing Requirements: I<sup>2</sup>C Interface (continued)

|                     |                                                                                 | MIN                   | MAX  | UNIT |

|---------------------|---------------------------------------------------------------------------------|-----------------------|------|------|

| t <sub>r</sub>      | Rise time of both SDA and SCL signals                                           |                       | 1000 | ns   |

| t <sub>f</sub>      | Fall time of both SDA and SCL signals                                           |                       | 300  | ns   |

| t <sub>SU;STO</sub> | Setup time for STOP condition                                                   | 4                     |      | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition                                | 4.7                   |      | μs   |

| C <sub>(b)</sub>    | Capacitive load for each bus line                                               |                       | 400  | pF   |

| V <sub>nL</sub>     | Noise margin at the LOW level for each connected device (including hysteresis)  | 0.1 × V <sub>DD</sub> |      | V    |

| V <sub>nH</sub>     | Noise margin at the HIGH level for each connected device (including hysteresis) | $0.2 \times V_{DD}$   |      | V    |

Figure 1. Timing Diagram for I<sup>2</sup>C Interface

## 6.6 Typical Characteristics

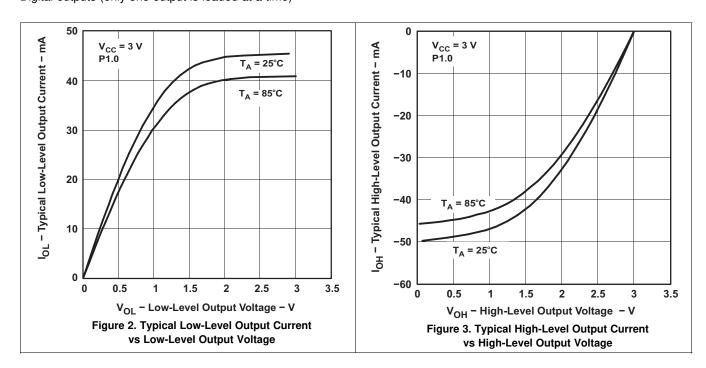

Digital outputs (only one output is loaded at a time)

Product Folder Links: UCD9081

Submit Documentation Feedback

# TEXAS INSTRUMENTS

## 7 Parameter Measurement Information

Figure 4. POR/Brownout Reset (BOR) vs Supply Voltage

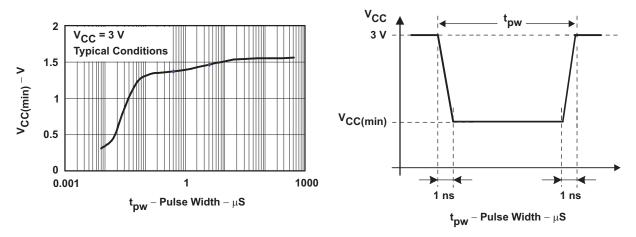

Figure 5.  $V_{CC(min)}$  Level With a Square Voltage Drop to Generate a POR/Brownout Signal

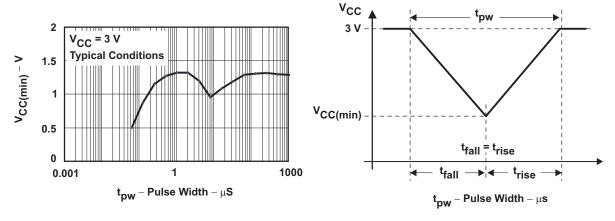

Figure 6. V<sub>CC(min)</sub> Level With a Triangle Voltage Drop to Generate a POR/Brownout Signal

## 8 Detailed Description

#### 8.1 Overview

Electronic systems that include CPU, DSP, microcontroller, FPGA, ASIC, and so forth, can have multiple voltage rails and require certain power on and off sequences to function correctly. The UCD9081 device can control up to 8 voltage rails and ensure correct power sequences during normal condition and fault conditions.

In addition to sequencing, UCD9081 can continuously monitor rail voltages, fault conditions, and report the system health information to a I<sup>2</sup>C host, improving the long-term reliability of the system.

Also, UCD9081 can protect electronic systems by responding to power system faults. The fault responses are conveniently configured by users through PC-based GUI. Fault events are stored in on-chip nonvolatile flash memory to assist failure analysis.

The UCD9081 can control up to four general-purpose digital outputs through the same sequencing mechanisms as the power supply enables, which can be used for digital signals for other devices.

## 8.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

## 8.3 Feature Description

#### 8.3.1 Rail Configuration

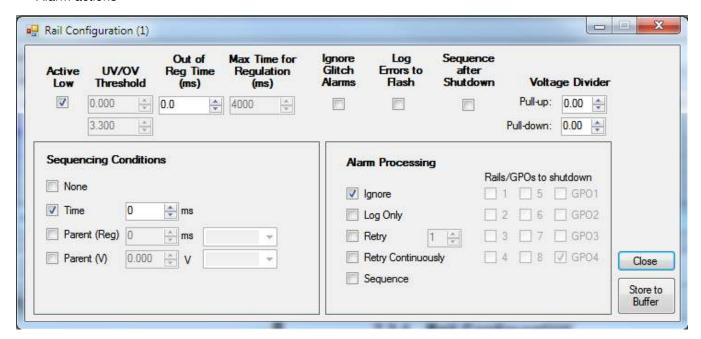

A rail includes voltage monitoring pin, a power-supply enable. UCD9081 can support up to 8 rails. Once the assigned rail is selected, other key monitoring and sequencing criteria are selected for each rail from rail configuration:

- Enable pin polarity

- Undervoltage (UV) and overvoltage (OV) fault limits

- Maximum time allowed before an alarm is declared

- Maximum time allowed achieving regulation (voltage between UV or OV range)

- · Masks glitches from error log windows

- · Log errors to flash

- · Sequence after shutdown

- Voltage divider

- · Sequence conditions selections

- · Alarm actions

Figure 7. GUI Rail Configuration

#### 8.3.2 Graphical User Interface (GUI)

UCD9081 designer is provided for device configuration. This PC-based graphical user interface (GUI) offers an intuitive I<sup>2</sup>C interface to the device. It allows the design engineer to configure the system operating parameters for the application without directly using I<sup>2</sup>C commands, store the configuration to on-chip nonvolatile memory, and observe system status (voltage, and so forth). The UCD9081 GUI can be downloaded from www.ti.com in the product folder.

#### 8.4 Device Functional Modes

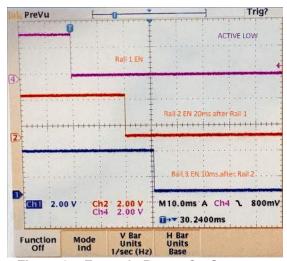

#### 8.4.1 Power Supply Sequencing

The UCD9081 can be configured to sequence power supply rails using the enable signals (ENx) or the general-purpose outputs (GPOx) in one of four ways:

- 1. A rail can be configured to not be sequenced

- 2. Using a delay time after UCD9081 RESET. The enable or GPO is asserted after UCD9081 RESET plus the user specified delay

- Using a delay time after another (parent) rail has achieved regulation (V<sub>RAIL</sub> is within specified under- and overvoltage settings). The enable or GPO is asserted after the (parent) rail is in regulation plus the user specified delay.

- 4. Using a (parent) rail voltage. The enable or GPO is asserted after the (parent) rail voltage is greater than or equal to the user specified voltage.

## 8.4.2 Power-Supply Enables

The UCD9081 can sequence and enable or disable up to eight power supplies through the ENx (EN1 to EN8) signals. These signals can be configured active-high or active-low, supporting power supplies with either polarity.

EN8 can also be configured as a GPO (GPO1). EN8/ADDR1/GPO1 is also used for  $I^2C$  address selection (ADDR1).

While the UCD9081 is in RESET, the enable signals are in a high-impedance state. The enable signals must be pulled up or down on the board according to the desired default power-supply state (enabled or disabled).

## 8.4.3 General-Purpose Outputs

The UCD9081 can control up to four general-purpose digital outputs through the same sequencing mechanisms as the power supply enables. These general-purpose outputs (GPO1–GPO4) can be used for digital signals such as resets or status inputs to other devices. These signals are multiplexed with other functions (primarily I<sup>2</sup>C address selection). See *Pin Configuration and Functions* to ensure that these signals are used properly by the application. The GPO1 signal is also multiplexed with EN8.

#### 8.4.4 Device Reset

UCD9081 RESET occurs due to one of the following conditions:

- External RST pin is asserted

- Power is applied to the device (power-on-reset) or power is cycled

- A sequence event occurs as a result of a configured rail alarm event

- RESTART command is issued over the I<sup>2</sup>C bus

During RESET, the following takes place:

- · All ENx and GPOx pins are placed in a high-impedance state

- · All internal timers are reset to zero

- The I<sup>2</sup>C address pins (ADDR1-ADDR4) are sampled and the device address is assigned accordingly

- · All ENx and GPOx pins are driven to their inactive levels

- The UCD9081 runs a checksum function to validate its memory contents

- If there are no errors, the device starts sequencing according to the current sequencer configuration

During this time, the UCD9081 does not respond to host requests made over the I<sup>2</sup>C bus.

To ensure the integrity of data within the device, the device runs a checksum function during RESET. If the configuration parameters of the device are valid, the UCD9081 begins operating according to the current sequencer configuration. If the configuration parameters are invalid, the UCD9081 overwrites the current configuration parameters with the last known good configuration and the device begins operating with these parameters. This can cause a delay in the RESET time. To establish a copy of the valid configuration, UCD9081 RESET time is delayed the first time a new configuration is loaded.

## **Device Functional Modes (continued)**

#### 8.4.5 Voltage Reference

The analog to digital converter in the UCD9081 has a selectable voltage reference,  $V_{R+}$ . The voltage reference can either be an internally generated 2.5-V reference or an external reference derived from  $V_{CC}$ . The external reference is recommended for those systems requiring more accurate voltage readings. See *Estimating UCD9081 Reporting Accuracy Over Variations in ADC Voltage Reference* for information on calculating the accuracy of each reference.

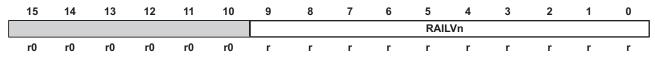

#### 8.4.6 Voltage Monitoring

The UCD9081 can monitor eight voltage rails through the MONx terminals of the device (MON1 to MON8). The UCD9081 samples these eight input channels and uses the selected reference to convert the voltages to digital values. These values are accessible through the I<sup>2</sup>C interface. When monitoring a voltage rail that has a nominal voltage larger than the selected reference, a resistor divider network is typically used. The design must ensure that the source impedance of the resistor network is chosen properly to maintain the accuracy of the analog to digital conversion. For more details, see *Application Information*.

The UCD9081 allows the user to independently specify the following for each monitored rail:

- · overvoltage (OV) threshold

- · undervoltage (UV) threshold

- out of regulation time or glitch width (OORW)

- · maximum time for regulation (MTFR)

The MTFR is used to determine whether or not a rail starts successfully after being enabled.

The UCD9081 also has the ability to ignore glitches. Glitches are fault conditions that last less than the specified OORW for that rail. Ignoring glitches may be useful in the case where the power supply is known to be noisy but still operates well. Ignoring glitches does not affect the monitoring capability of the UCD9081 with respect to detecting sustained UV or OV faults. It simply prevents the UCD9081 from logging glitch faults to the error log.

#### 8.4.7 Rail Shutdown

Rail (or GPO) shutdown is the act of setting the ENx (or GPOx) pin to a state which disables the associated power supply output. A rail can shutdown for one of the following reasons:

- · A fault condition on the rail itself

- · A fault condition on a parent rail resulting in a shutdown

- An I<sup>2</sup>C shutdown command

Each rail and GPO can be independently configured to shutdown according to a user-specified time delay from 0 ms to 4095 ms. This is referred to as the system shutdown configuration.

#### 8.4.8 Alarm Processing

Each rail can be independently configured to respond to an alarm or fault in a variety of ways. A fault can be an UV condition, OV condition, or a rail that did not start (MTFR exceeded before UV threshold achieved). The options for alarm processing are as follows:

- Ignore

- · Log only

- Retry n times (n = 0,1,2,3,4)

- Retry continuously

- Sequence (immediately)

- Sequence after shutdown

In addition to these options, a rail can be independently configured to log errors to FLASH to aid in failure analysis. For more details, see *Error Logging*.

#### **Device Functional Modes (continued)**

#### 8.4.8.1 Ignore

The UCD9081 can be configured to ignore all alarms on the rail. This is the recommended option for all unused power supply rails on the UCD9081.

#### 8.4.8.2 Log Only

The UCD9081 can be configured to log a fault and take no additional action. For more information, see *Error Logging*.

#### 8.4.8.3 Retry n Times

The UCD9081 can be configured to attempt to restart a rail up to n times (n = 0,1,2,3, or 4) in response to a sustained fault condition. With this option, the user can also specify which rails and GPOs are dependent upon the configured rail. When a sustained fault is detected, the faulty rail is disabled and re-enabled the desired number of times. The rail remains enabled for the specified MTFR before attempting another retry. If the rail does not achieve regulation after the desired number of retries, all user-specified dependent rails and GPOs are shutdown according to the times specified in the system shutdown configuration. If any of the dependent rails have other rails or GPOs marked as dependents, those dependent rails or GPOs are also forced to shutdown regardless of their alarm processing configurations.

## 8.4.8.4 Retry Continuously

The UCD9081 can be configured to continuously attempt to restart a faulty rail. When the UCD9081 detects a sustained fault condition on the configured rail, the rail is disabled and then re-enabled. The rail remains enabled for the specified MTFR. The retry process repeats for this rail until it properly achieves regulation.

#### 8.4.8.5 Sequence

The UCD9081 can be configured to sequence the entire system in response to a sustained fault condition. When the UCD9081 detects a fault on the configured rail, all rails and GPOs are shutdown immediately and UCD9081 RESET occurs (see *Device Reset*). For this configuration, a shutdown according to the delay times specified by the system shutdown configuration does not occur prior to UCD9081 RESET.

#### 8.4.8.6 Sequence After Shutdown

Sequence after shutdown is an option that can be used in conjunction with *Retry n Times*. When a fault occurs on the configured rail, this option forces a UCD9081 RESET to occur after the procedure outlined in *Retry n Times* takes place. If a rail is configured for sequence after shutdown and is forced to shutdown due to a fault on a parent rail, a sequence after shutdown takes place.

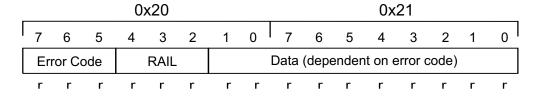

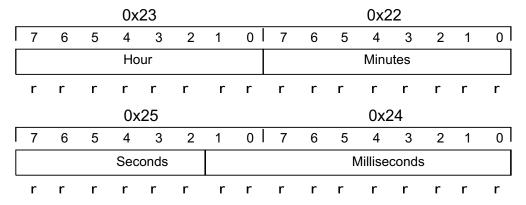

#### 8.4.9 Error Logging

The UCD9081 is capable of logging errors in two ways. The first method uses an eight-deep FIFO located in volatile memory (SRAM) of the UCD9081. Error conditions are posted to the ERROR registers according to the configuration for that rail. The UCD9081 logs the type of error, the time (from Reset) when the error occurred, the rail number, and the rail voltage. If the user has specified *ignore glitches* as an option for the faulty rail, glitches are not posted to the error log. If the user has specified *lgnore* as the alarm response for the faulty rail, no errors are posted to the error log for that rail. All other alarm responses result in the error condition being logged. Due to the unknown latency of the host extracting data from the FIFO, the UCD9081 only posts to the FIFO is if it has room to write. There is no impact to the monitoring operation of the UCD9081 if this FIFO is full and cannot be written.

The second method of error logging uses the non-volatile memory (FLASH) of the UCD9081. Similar to the error log in SRAM, faults are posted for all rails that have the appropriate alarm processing options selected. In this case, errors are posted to both the SRAM log and the FLASH log. The UCD9081 is capable of recording up to eight entries in the flash error log. Again, the UCD9081 only posts to the log if there is room to write. There is no impact to the monitoring operation of the UCD9081 if the error log is full and cannot be written.

## **Device Functional Modes (continued)**

To provide flexibility for a variety of systems, the UCD9081 has two modes for non-volatile error logging. The first mode configures the UCD9081 to hold in RESET when entries are present in the FLASH error log. This is advantageous in systems where a master I<sup>2</sup>C device is available to read the error log following a critical system failure. When configured for this mode, the UCD9081 checks for a non-empty FLASH error log during RESET. If there are entries in the FLASH error log, the device waits for a host to clear the error log before sequencing the device. For information on clearing the FLASH error log, see the section on *Resetting the Flash Error Log*.

The second mode allows the UCD9081 to sequence (following a RESET of the device) regardless of whether or not there are entries present in the FLASH error log. This is useful in systems with no master I<sup>2</sup>C device, or where power cycles are common and not due to system failure.

For information on reading the error logs in each mode, see *Register Maps*.

#### 8.4.10 Brownout

The brownout circuit is implemented to provide the proper internal reset signal to the device during power on and power off.

#### 8.5 Programming

#### 8.5.1 I<sup>2</sup>C Interface

The UCD9081 power-supply sequencer has a 100 kHz, slave mode I<sup>2</sup>C interface for communication with an I<sup>2</sup>C master. The I<sup>2</sup>C master uses this interface to configure and monitor the UCD9081. The master must support clock stretching to properly communicate with the UCD9081.

#### 8.5.2 Configuring and Monitoring the UCD9081

The UCD9081 supports both configuration and monitoring using its I<sup>2</sup>C slave interface. A Microsoft Windows™ GUI is available for configuring and monitoring the UCD9081. This GUI can be downloaded from the TI website at www.ti.com.

For monitoring the sequencer, an I<sup>2</sup>C memory map allows an I<sup>2</sup>C host to perform memory-mapped reads (and in some cases writes) to obtain status information from the UCD9081. For instance, all rails can report their voltage through the I<sup>2</sup>C memory map. For information on which parameters are available through the I<sup>2</sup>C memory map, see *Register Maps*.

To change configuration parameters of the sequencer, a different mechanism is used. The entire set of configuration parameters must be written at one time to the device as one large transaction over the I<sup>2</sup>C interface. This ensures that the configuration of the device is consistent at any given time. The process for configuring the UCD9081 is described in *Configuring the UCD9081*.

The UCD9081 is compatible with 3.3-V IO ports of microcontrollers, TMS320™ DSP family as well as ASICs. The UCD9081 is available in a plastic 32-pin VQFN package (RHB).

#### 8.5.3 Resetting the Flash Error Log

The UCD9081 can be configured to log errors on a critical voltage rail to internal FLASH memory. This mechanism permits the error log to be read after the device has been reset, or if a loss of power causes non-volatile memory to be cleared. As outlined in *Error Logging*, there are two modes for using this feature.

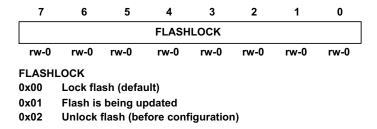

The first mode holds the UCD9081 in RESET (following a RESET of the device) if entries are present in the FLASH error log. This allows the user to successfully read and clear the FLASH error log before sequencing the system. When using this mode, the UCD9081 does not sequence until the FLASH error log is cleared. To clear the FLASH error log and sequence the device, perform the following steps:

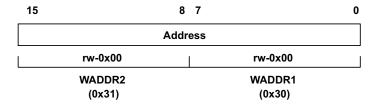

- Write FLASHLOCK register to a value of 0x02

- Write WADDR register to a value of 0x1000

- Write WDATA register to a value of 0xBADC

- Write WADDR register to a value of 0x107E

- Write WDATA register to a value of 0xBADC

- Write FLASHLOCK register to a value of 0x00

## **Programming (continued)**

Write RESTART register to a value of 0x00

The second mode allows the UCD9081 to sequence (following a RESET of the device) regardless of whether or not there are entries present in the FLASH error log. When using this mode, the user still may wish to clear the FLASH error logs some time after RESET. To do this, perform the following steps:

- Write FLASHLOCK register to a value of 0x02

- Write WADDR register to a value of 0x1000

- Write WDATA register to a value of 0xBADC

- Write WADDR register to a value of 0x107E

- Write WDATA register to a value of 0xBADC

- Write FLASHLOCK register to a value of 0x00

Clearing the FLASH error log during run-time causes a delay in monitoring.

## 8.5.4 Configuring the UCD9081

The UCD9081 has many different configurable parameters such as sequencing options, alarm processing options, and rail dependencies. A Microsoft Windows™ GUI is available for selecting and generating the necessary configuration parameters. The UCD9081 GUI can be downloaded from www.ti.com in the product folder. See *UCD9081 EVM User's Guide* (SLVU249) for details on installing and using the GUI. Once the user-specific configuration parameters are selected, the GUI generates a hex file that can be loaded into the flash memory of the UCD9081 through the I²C interface.

The enable and digital I/O pins of the UCD9081 are in a high impedance state when the device is not configured (Texas instruments delivers the device in this state).

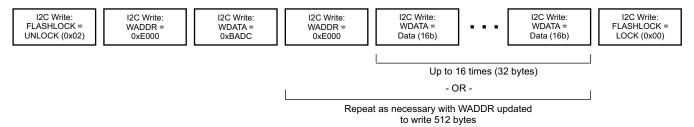

To download the configuration parameters generated by the GUI into the UCD9081, a contiguous block of configuration information is sent to the device through the I<sup>2</sup>C interface. This block is 512 bytes long and starts at address 0xE000.

This 512-byte block of configuration information is sent to the device in multiple segments. The segment size can range from 2 to 32 bytes at one time, and must be a multiple of 2 bytes. That is, a master can send 256 2-byte segments or 32 16-byte segments, and so on. All the segments must be sent back-to-back in the proper sequence, and this operation must be completed by sending the last segment so that the last byte of the 512-byte block is written. If this is not done, the UCD9081 is in an unknown state and does not function as designed.

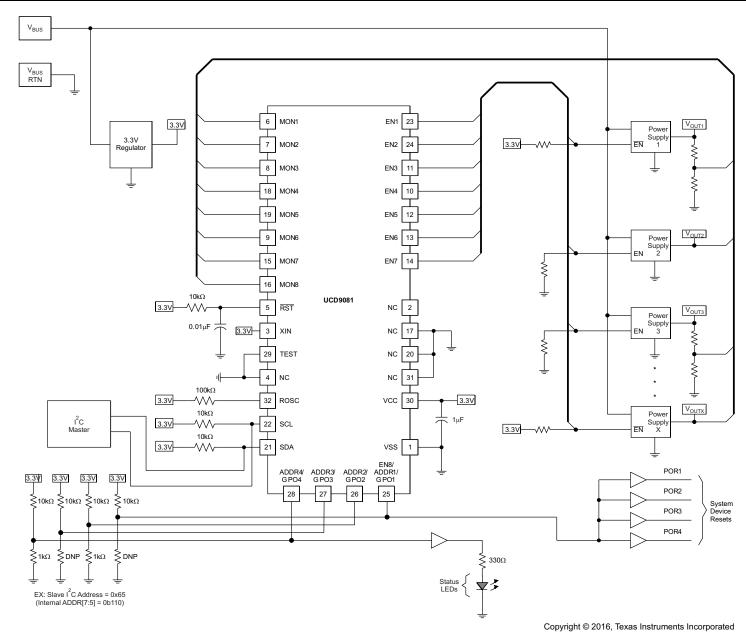

The process for sending the configuration information to the UCD9081 is as shown in Figure 8.

Figure 8. Configuration Information

## **Programming (continued)**

As shown in Figure 8, the process for updating the configuration of the UCD9081 is as follows:

- 1. Unlock flash memory by writing the value 0x02 to the FLASHLOCK register

- 2. Write the address of the configuration section of memory (WADDR = 0xE000)

- 3. Write the constant 0xBADC to update memory (WDATA = 0xBADC)

- 4. Write the address of the configuration section of memory again (WADDR = 0xE000)

- 5. Write the data (WDATA = <varies>). Repeat steps 4 and 5 as necessary, depending on the data segment size used, to write 512 bytes. Increment the address as necessary.

- 6. Lock flash memory after the last byte of the last segment is written by writing the value 0x00 to the FLASHLOCK register

At the conclusion of this process, the configuration of the UCD9081 is updated with the configuration changes, as represented by the values from the data segments. See *UCD9081 Programming Guide* (SLVA275) for more details on programming the UCD9081.

#### 8.5.5 User Data

User data (128 bytes) can be stored in the UCD9081 FLASH memory at location 0x1080 to 0x10FF. Writes to the User Data section of memory are performed as follows:

- 1. Unlock flash memory by writing the value 0x02 to the FLASHLOCK register

- 2. Write the address of the USER DATA section of memory (WADDR = 0x1080)

- 3. Write the constant 0xBADC to update memory (WDATA = 0xBADC)

- 4. Write the address of the USER DATA section of memory again (WADDR = 0x1080)

- 5. Write the data (WDATA = <varies>). Repeat steps 4 and 5 as necessary depending on the data segment size used. Increment the address as necessary.

- 6. Lock flash memory after the last byte of the last segment is written by writing the value 0x00 to the FLASHLOCK register

To read the User Data section of memory, follow the procedure for reading memory outlined in WADDR and WDATA.

#### 8.5.6 I<sup>2</sup>C Address Selection

The UCD9081 supports 7-bit I<sup>2</sup>C addressing. The UCD9081 selects an I<sup>2</sup>C address by sampling the logic level of the four digital inputs to the device (ADDR1–ADDR4) during the RESET interval. When the UCD9081 is released from RESET, the ADDRx logic levels are latched and the I<sup>2</sup>C address is assigned as shown in *Figure 9*.

| A7 _ 1 | A6 = 1 | Λ5 – O | A4 = ADDR4/GPO4     | A3 = ADDB3/GPO3    | A2 = ADDR2/GPO2 | A1 = FN8/ADDR1/GPO1 |

|--------|--------|--------|---------------------|--------------------|-----------------|---------------------|

|        |        |        | A4 = A1111B4/(3PC)4 | Aa = AIJIJBa/UzPUa |                 |                     |

## Figure 9. $I^2C$ Address = 0x60-0x6F

External pullup or pulldown resistors are required to configure the  $I^2C$  address; the UCD9081 does not have internal bias resistors. The 7-bit  $I^2C$  address refers to the address bits only, not the read/write bit in the first byte of the  $I^2C$  protocol. The base  $I^2C$  address is 0x60 and the  $I^2C$  general call address (0x00) is not supported.

After the initialization process of the UCD9081 is complete, these four pins can be used for general-purpose outputs.

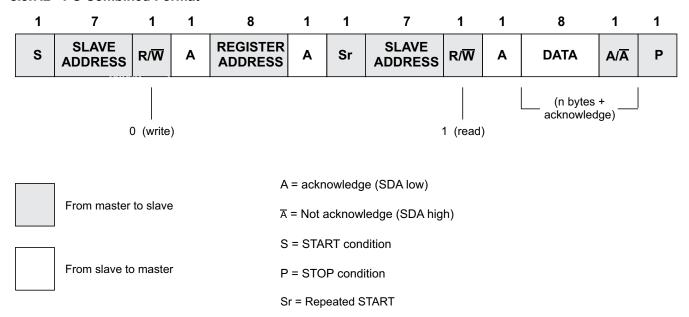

#### 8.5.7 I<sup>2</sup>C Transactions

The UCD9081 can be configured and monitored through I<sup>2</sup>C memory-mapped registers. Registers that are configurable (can be written) through an I<sup>2</sup>C write operation are implemented using an I<sup>2</sup>C unidirectional data transfer, from the master to slave, with a stop bit between transactions.

#### 8.5.7.1 PC Unidirectional Transfer

Figure 10. I<sup>2</sup>C Register Access With START or STOP

Registers that can be read are implemented using an  $I^2C$  read operation, which can use the  $I^2C$  combined format that changes data direction during the transaction. This transaction uses an  $I^2C$  repeated START during the direction change.

#### 8.5.7.2 PC Combined Format

Figure 11. I<sup>2</sup>C Register Access With Repeated START

The UCD9081 also supports a feature that auto-increments the register address pointer for increased efficiency when accessing sequential blocks of data. It is not necessary to issue separate I<sup>2</sup>C transactions.

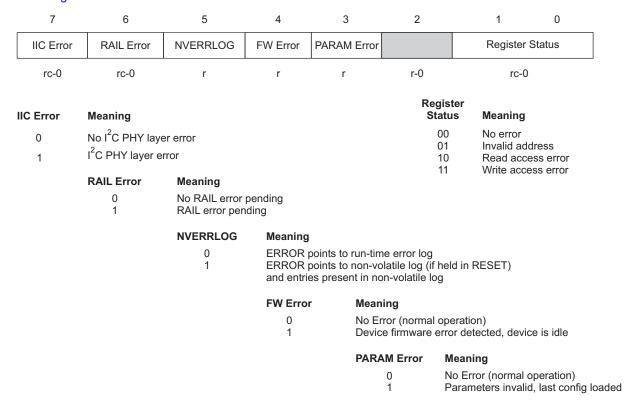

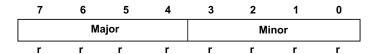

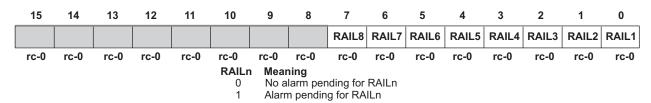

## 8.6 Register Maps

The UCD9081 allows all monitoring of the system through the I<sup>2</sup>C interface on the device. The following is the memory map of the supported registers in the system. The detail of each of these registers is given in the next section as well.

The UCD9081 supports functionality to increment the I<sup>2</sup>C register address value automatically when a register is being accessed to more efficiently access blocks of like registers. Table 1 also shows the amount that the register address is incremented for each register access.

**Table 1. Register Access Adjustment**

| REGISTER NAME ADDRESS ACCESS ADJUSTMENT AFTER ACCESS |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|                                                      |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|                                                      |                                                                                           | +1 (0x01)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                                                      |                                                                                           | +1 (0x02)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                                                      |                                                                                           | +1 (0x03)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                                                      |                                                                                           | +1 (0x04)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                                                      |                                                                                           | +1 (0x05)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

|                                                      | r                                                                                         | +1 (0x06)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x06                                                 | r                                                                                         | +1 (0x07)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x07                                                 | r                                                                                         | +1 (0x08)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x08                                                 | r                                                                                         | +1 (0x09)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x09                                                 | r                                                                                         | +1 (0x0A)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x0A                                                 | r                                                                                         | +1 (0x0B)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x0B                                                 | r                                                                                         | +1 (0x0C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x0C                                                 | r                                                                                         | +1 (0x0D)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x0D                                                 | r                                                                                         | +1 (0x0E)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |

| 0x0E                                                 | r                                                                                         | +1 (0x0F)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |  |  |