### ISL76534

Ultra-Low Power 14-Channel Programmable Gamma Buffer with Integrated EEPROM

FN8866 Rev 0.00 July 27, 2016

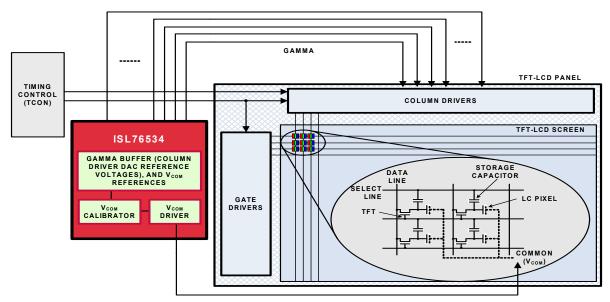

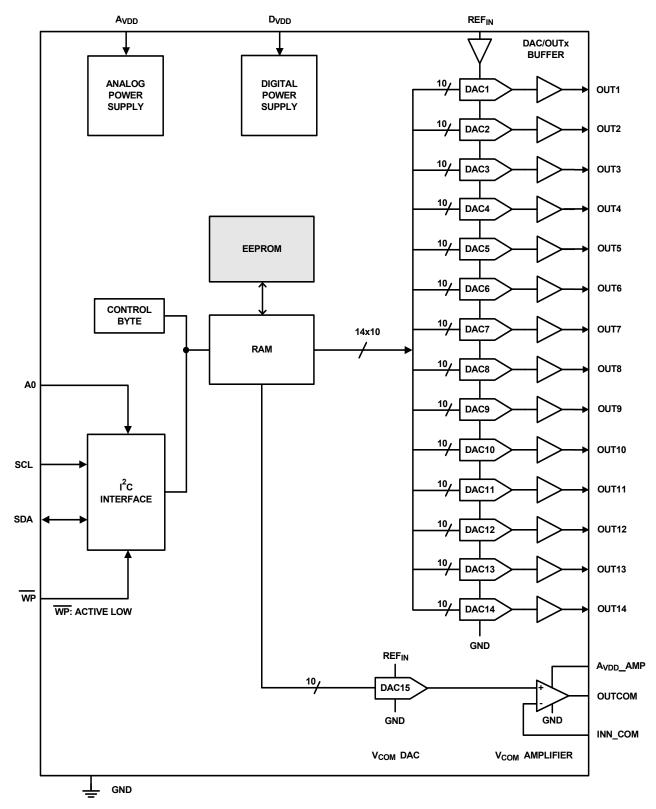

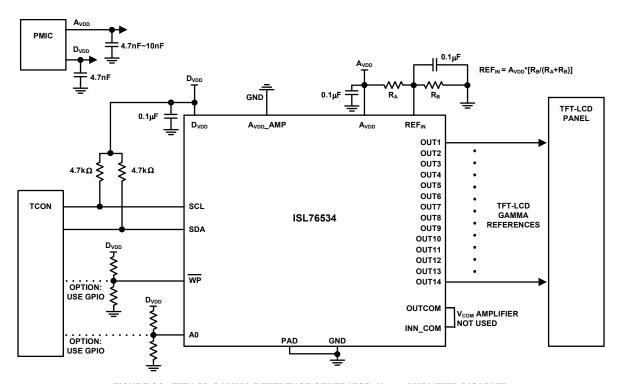

The ISL76534 is a programmable gamma buffer for TFT-LCDs featuring ultra-low power operation. The ISL76534 contains an I $^2$ C programmable, 10-bit, 14-channel gamma reference voltage generator with buffered outputs, a 10-bit programmable  $V_{COM}$  calibrator, a high output current  $V_{COM}$  amplifier, and internal EEPROM to store all reference voltage data. The EEPROM features an endurance of 10,000 write cycles and a data retention of 20 years at 105  $^\circ$ C.

Combining gamma and  $V_{COM}$  reference voltage generators with low power operation and EEPROM, the ISL76534 provides a complete reference voltage solution ideal for TFT-LCD displays.

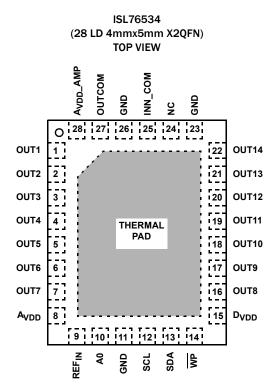

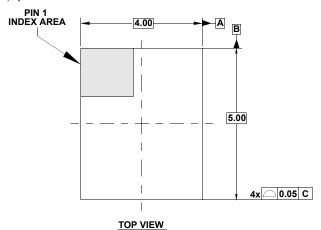

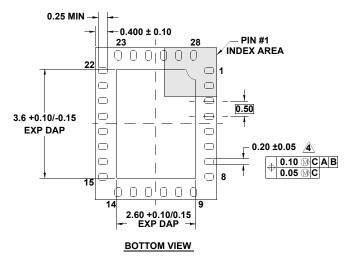

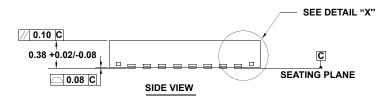

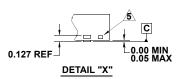

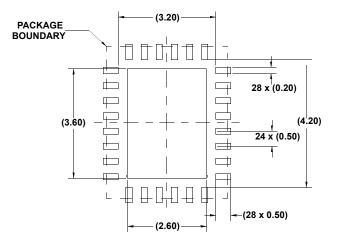

The ISL76534 is available in a super thin (height = 0.4mm maximum) 28 Ld 4mmx5mm X2QFN thermally enhanced package. The device is specified for operation across the ambient temperature - $40^{\circ}$ C to + $105^{\circ}$ C.

### **Applications**

- · Automotive infotainment display

- Automotive Center Information Display (CID)

- · Automotive smart mirrors

- Automotive instrument cluster display

- · Automotive TFT-LCD display

### **Features**

- 14-channel gamma references, 10-bit resolution with buffered outputs

- 1-channel V<sub>COM</sub> calibrator with 10-bit resolution

- High output current V<sub>COM</sub> amplifier

- Ultra-low power operation, ideal for automotive displays:

Typical quiescent power, 12mW at 8V AVDD

- EEPROM data retention: 20 years at 105°C

- EEPROM endurance: 10,000 write cycles

- Read/write capable over 2.25V to 3.6V D<sub>VDD</sub> range

- 6.3V to 19V analog supply operating range

- 2.25V to 3.6V digital supply operating range

- Power Supply Rejection Ratio (PSRR): 75dB typical

- 28 Ld 4mmx5mm super thin X2QFN package

- · Pb-free (RoHS compliant)

- AEC-Q100 qualified

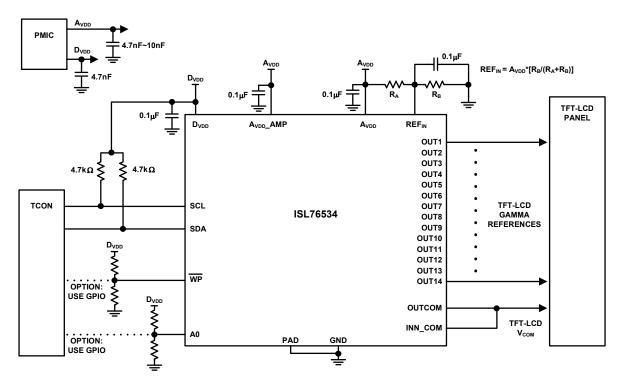

FIGURE 1. TYPICAL APPLICATION: TFT-LCD GAMMA REFERENCE VOLTAGE GENERATOR

# **Table of Contents**

| Block Diagram                                                | 3    |

|--------------------------------------------------------------|------|

| Ordering Information                                         | 4    |

| Pin Configuration                                            | 4    |

| Pin Descriptions                                             | 4    |

| Absolute Maximum Ratings                                     | е    |

| Thermal Information                                          |      |

| Recommended Operating Conditions                             |      |

| Electrical Specifications                                    |      |

| Typical Performance Curves                                   |      |

| •                                                            |      |

| General Description                                          |      |

| I <sup>2</sup> C Digital Interface                           |      |

| Data ValiditySTART and STOP Condition                        |      |

| Byte Format                                                  |      |

| Acknowledge (ACK)                                            | . 12 |

| Not Acknowledge (NACK)                                       |      |

| Device Address and R/W Bit                                   |      |

| Application Information                                      |      |

| ISL76534 Communication Protocol                              |      |

| Write Operation                                              |      |

| Write Timing Diagrams                                        |      |

|                                                              |      |

| Read Operation                                               |      |

| Read Timing Diagram                                          |      |

| Data Word (WRITE/READ)  DAC Transfer Function of OUT1-OUT14. |      |

| DAC Output Accuracy                                          |      |

| DAC Reference Voltage                                        |      |

| DAC Channel Outputs                                          |      |

| VCOM Amplifier                                               |      |

| Write Protection (WP)                                        |      |

| Writing to the EEPROM                                        |      |

| Recalling The EEPROM                                         |      |

| UVLO and Output Enable.                                      |      |

| Power Sequencing                                             | . 21 |

| Thermal Shutdown                                             |      |

| Power Dissipation                                            |      |

| General PowerPAD Design Considerations                       |      |

| Typical Applications                                         |      |

| Revision History                                             |      |

|                                                              | _ 23 |

|                                                              |      |

| About Intersil                                               | . 23 |

### **Block Diagram**

FIGURE 2. BLOCK DIAGRAM

### **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3) | PART<br>MARKING  | TEMP. RANGE<br>(°C) | PACKAGE<br>(RoHS COMPLIANT) | PKG.<br>DWG. # |

|--------------------------------|------------------|---------------------|-----------------------------|----------------|

| ISL76534ARXZ                   | 76534 ARXZ       | -40 to +105         | 28 Ld X2QFN                 | L28.4x5D       |

| ISL76534EVAL1Z                 | Evaluation Board |                     |                             |                |

#### NOTES:

- 1. Add "-T13" suffix for 6k unit or "-T7A" suffix for 250 unit Tape and Reel options. Please refer to TB347 for details on reel specifications.

- These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu-Ag plate

- e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL

classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL76534. For more information on MSL please see tech brief TB363.

### **Pin Configuration**

Note: Thermal pad is electrically connected to GND

### **Pin Descriptions**

| PIN#                                                     | PIN NAME          | PIN TYPE      | PIN FUNCTION                                                                                                                                                                                                                                                    | EQUIVALENT<br>CIRCUIT |

|----------------------------------------------------------|-------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

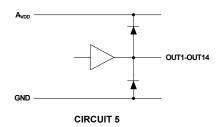

| 1, 2, 3, 4, 5,<br>6, 7, 16, 17,<br>18, 19, 20,<br>21, 22 | OUTx              | Analog Output | 10-bit Programmable DAC outputs                                                                                                                                                                                                                                 | 5                     |

| 8                                                        | A <sub>VDD</sub>  | Analog Power  | Analog power supply. Include a bulk $4.7\mu F$ capacitor, and a local $0.1\mu F$ ceramic bypass capacitor to the system ground. Place the $0.1\mu F$ as close to the pin as possible; the bulk capacitor may be placed farther away from the IC.                | 1                     |

| 9                                                        | REF <sub>IN</sub> | Analog Input  | High-impedance, buffered reference voltage input for 10-bit DACs. Include a local 0.1μF ceramic bypass capacitor to the system ground; place as close to the pin as possible.                                                                                   | 4                     |

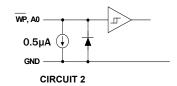

| 10                                                       | AO                | Digital Input | Determines the device's 7-bit I <sup>2</sup> C device address:  0: Device Address = 0x74 (this is the default setting if pin is left floating)  1: Device Address = 0x75 (pull-up pin externally)  Note: pin has an internal pull-down to GND of 10MΩ (typical) | 2                     |

# Pin Descriptions (Continued)

| PIN#       | PIN NAME              | PIN TYPE      | PIN FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                        | EQUIVALENT<br>CIRCUIT |

|------------|-----------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 11, 23, 26 | GND                   | Power         | Ground                                                                                                                                                                                                                                                                                                                                                                                                                              |                       |

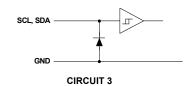

| 12         | SCL                   | Digital Input | I <sup>2</sup> C clock (high impedance input)                                                                                                                                                                                                                                                                                                                                                                                       | 3                     |

| 13         | SDA                   | Digital I/O   | I <sup>2</sup> C data (high impedance input/open-drain output)                                                                                                                                                                                                                                                                                                                                                                      | 3                     |

| 14         | WP                    | Digital Input | I <sup>2</sup> C Write Protection, active low:  0: Prevent I <sup>2</sup> C data writes to internal DAC registers and EEPROM (this is the default setting if pin is left floating)  1: Allow I <sup>2</sup> C data writes to internal DAC registers and EEPROM (pull-up pin externally)  Note: pin has an internal pull-down to GND of 10MΩ (typical)                                                                               | 2                     |

| 15         | D <sub>VDD</sub>      | Digital Power | Digital power supply. Include a local $0.1\mu F$ ceramic bypass capacitor to the system ground; place as close to the pin as possible.                                                                                                                                                                                                                                                                                              | 1                     |

| 24         | NC                    |               | Not Connected Internally. Acceptable to leave pin floating.                                                                                                                                                                                                                                                                                                                                                                         |                       |

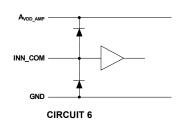

| 25         | INN_COM               | Analog Input  | V <sub>COM</sub> amplifier inverting input                                                                                                                                                                                                                                                                                                                                                                                          | 6                     |

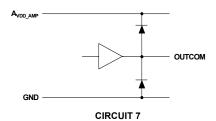

| 27         | оитсом                | Analog Output | V <sub>COM</sub> amplifier output                                                                                                                                                                                                                                                                                                                                                                                                   | 7                     |

| 28         | A <sub>VDD</sub> _AMP | Analog Power  | Analog power supply for $V_{COM}$ amplifier. It is acceptable that $A_{VDD}$ _AMP is tied to $A_{VDD}$ , or set to a lower voltage: $A_{VDD}$ _AMP $\leq A_{VDD}$ . Include a bulk 4.7 $\mu$ F capacitor (or share with the $A_{VDD}$ bulk), and a local $0.1\mu$ F ceramic bypass capacitor to the system ground. Place the $0.1\mu$ F as close to the pin as possible; the bulk capacitor may be placed farther away from the IC. | 1                     |

| -          | THERMAL PAD           | GND           | Thermal pad. Electrically connected to GND (pins 11, 23, 26). Connect to ground plane on PCB to maximize thermal performance.                                                                                                                                                                                                                                                                                                       |                       |

$\mathbf{D}_{\text{VDD}}$

### **Absolute Maximum Ratings** (T<sub>A</sub> = +25°C)

| Supply Voltage                                 |                  |

|------------------------------------------------|------------------|

| Between A <sub>VDD</sub> and GND               | +21V             |

| A <sub>VDD</sub> _AMP to GND                   |                  |

| Between D <sub>VDD</sub> and GND               |                  |

| Maximum Output Voltage                         |                  |

| [OUT1-OUT14]                                   | A <sub>VDD</sub> |

| OUTCOM                                         | AVDD AMP         |

| SDA                                            |                  |

| Maximum Input Voltage                          |                  |

| REF <sub>IN</sub>                              | A <sub>VDD</sub> |

| INN_COM                                        |                  |

| SCL, SDA, AO, WP                               | +4.5V            |

| Maximum Continuous Output Current per Channel  |                  |

| OUT1-OUT14                                     | ±60mA            |

| OUTCOM                                         | ±100mA           |

| Maximum Total Output Current                   |                  |

| OUT1-OUT14                                     | ±250mA           |

| ESD Ratings                                    |                  |

| Human Body Model (Tested per AEC-Q100-002)     | 3kV              |

| Machine Model (Tested per AEC-Q100-003)        | 250V             |

| Charged Device Model (Tested per AEC-Q100-011) | 2kV              |

| Latch-up (Tested per AEC-Q100-004)             | 100mA            |

|                                                |                  |

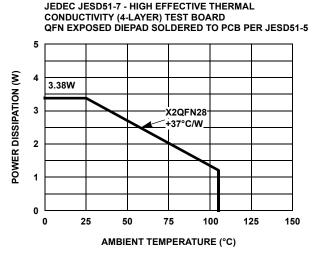

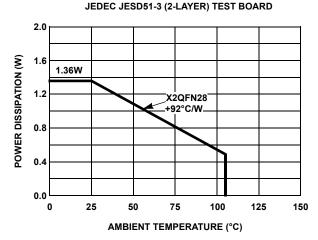

### **Thermal Information**

| Thermal Resistance (Typical) | $\theta_{JA}$ (°C/W) | $\theta_{JC}(^{\circ}C/W)$ |

|------------------------------|----------------------|----------------------------|

| 28 Ld X2QFN (Notes 4, 5)     | 37                   | 1.5                        |

| Power Dissipation            |                      | See page 21                |

| Maximum Die Temperature      |                      | +150°C                     |

| Storage Temperature          | 6!                   | 5°C to +150°C              |

| Pb-free Reflow Profile       |                      | see <u>TB493</u>           |

### **Recommended Operating Conditions**

| Operating Range                                |

|------------------------------------------------|

| A <sub>VDD</sub> 6.3V to 19                    |

| A <sub>VDD</sub> _AMP 4.5V to A <sub>VD</sub>  |

| D <sub>VDD</sub>                               |

| Reference Voltage Range                        |

| REF <sub>IN</sub> to GND 5V to A <sub>VD</sub> |

| Ambient Operating Temperature                  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{\mbox{\scriptsize JC}},$  the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications**  $A_{VDD} = A_{VDD}$  AMP = 15V,  $D_{VDD} = 3.3$ V,  $REF_{IN} = 14.75$ V,  $T_A = +25$ °C, unless otherwise specified. **Boldface limits** apply across the operating temperature range, -40°C to +105°C.

| PARAMETER                                      | SYMBOL TEST CONDITIONS |                                                                                                     | MIN<br>( <u>Note 6</u> )  | TYP                       | MAX<br>( <u>Note 6</u> ) | UNIT |

|------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------|---------------------------|---------------------------|--------------------------|------|

| SUPPLY                                         |                        |                                                                                                     |                           |                           |                          |      |

| Analog Supply Voltage                          | A <sub>VDD</sub>       |                                                                                                     | 6.3                       |                           | 19                       | ٧    |

| Analog Supply Voltage for V <sub>COM</sub> Amp | A <sub>VDD</sub> _AMP  |                                                                                                     | 4.5                       |                           | A <sub>VDD</sub>         | ٧    |

| Digital Supply Voltage                         | D <sub>VDD</sub>       |                                                                                                     | 2.25                      |                           | 3.6                      | ٧    |

| Analog Supply Current                          | I <sub>AVDD</sub>      | A <sub>VDD</sub> = 8V, no load                                                                      |                           | 1.00                      | 1.8                      | mA   |

|                                                |                        | A <sub>VDD</sub> _AMP = 8V, no load                                                                 |                           | 0.40                      | 0.75                     | mA   |

|                                                |                        | A <sub>VDD</sub> = 15V, no load                                                                     |                           | 1.30                      | 2.5                      | mA   |

|                                                |                        | A <sub>VDD</sub> _AMP = 15V, no load                                                                |                           | 0.60                      | 1.2                      | mA   |

| Digital Supply Current                         | I <sub>DVDD</sub>      |                                                                                                     |                           | 190                       | 330                      | μΑ   |

| DAC High Reference Voltage                     | V <sub>REFIN</sub>     |                                                                                                     |                           |                           | A <sub>VDD</sub>         | ٧    |

| Undervoltage Lockout for A <sub>VDD</sub>      | UVLO                   | A <sub>VDD</sub> rising - OUTCOM, OUTx enabled                                                      | 3.9                       | 4.3                       | 4.5                      | ٧    |

|                                                |                        | A <sub>VDD</sub> falling - OUTCOM, OUTx disabled                                                    | 3.7                       | 4.0                       | 4.3                      | ٧    |

|                                                |                        | Hysteresis                                                                                          | 200                       | 330                       | 500                      | m۷   |

| ANALOG                                         | •                      |                                                                                                     |                           |                           |                          |      |

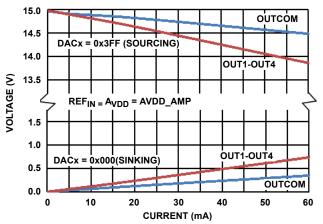

| Highest Output Voltage for OUT1-OUT14          | V <sub>OH</sub>        | REF <sub>IN</sub> = A <sub>VDD</sub> , DAC = 1023,<br>I <sub>LOAD</sub> = +5mA                      | REF <sub>IN</sub> - 0.150 | REF <sub>IN</sub> - 0.100 |                          | V    |

| Highest Output Voltage for OUTCOM              |                        | REF <sub>IN</sub> = A <sub>VDD</sub> , DAC = 1023, A <sub>V</sub> = +1,<br>I <sub>LOAD</sub> = +5mA | REF <sub>IN</sub> - 0.100 | REF <sub>IN</sub> - 0.050 |                          | V    |

| Lowest Output Voltage for<br>OUT1-OUT14        | V <sub>OL</sub>        | DAC = 0, I <sub>LOAD</sub> = -5mA                                                                   |                           | GND + 0.085               | GND + 0.150              | V    |

| Lowest Output Voltage for OUTCOM               |                        | DAC = 0, A <sub>V</sub> = +1, I <sub>LOAD</sub> = -5mA                                              |                           | GND + 0.050               | GND + 0.100              | V    |

**Electrical Specifications**  $A_{VDD} = A_{VDD}$  AMP = 15V,  $D_{VDD} = 3.3$ V,  $REF_{IN} = 14.75$ V,  $T_A = +25$ °C, unless otherwise specified. **Boldface limits** apply across the operating temperature range, -40°C to +105°C. (Continued)

| PARAMETER                                                | SYMBOL                    | TEST CONDITIONS                                                                                                                 | MIN<br>( <u>Note 6</u> ) | TYP  | MAX<br>( <u>Note 6</u> ) | UNIT  |

|----------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|--------------------------|-------|

| Power Supply Rejection Ratio                             | PSRR                      | OUT1-OUT14: OUTx = 0.5*A <sub>VDD</sub><br>A <sub>VDD</sub> varied from 14V to 16V                                              | 55                       | 75   |                          | dB    |

|                                                          |                           | OUTCOM: OUTCOM = 0.5*A <sub>VDD</sub><br>A <sub>VDD</sub> _AMP varied from 14V to 16V                                           | 50                       | 70   |                          | dB    |

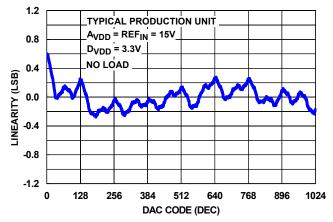

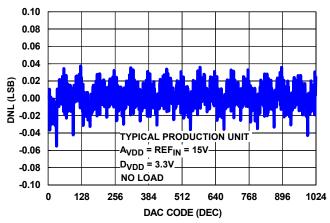

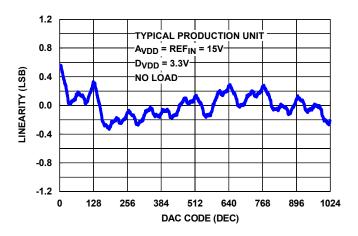

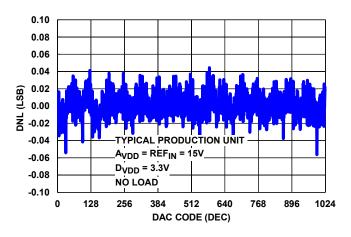

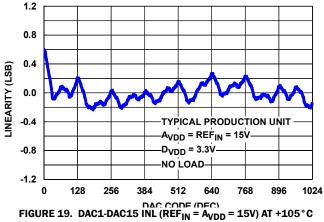

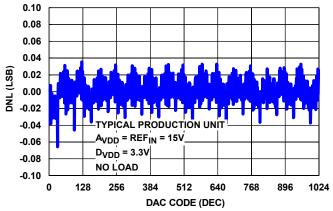

| DAC Integral Non-Linearity                               | INL                       | DAC1 through DAC14                                                                                                              | -2                       | 0    | 2                        | LSB   |

|                                                          |                           | DAC15 (OUTCOM)                                                                                                                  | -2                       | 0    | 2                        | LSB   |

| Input Leakage Current of REF <sub>IN</sub>               | I <sub>L_REF</sub>        | REF <sub>IN</sub> = 0.5*A <sub>VDD</sub>                                                                                        | -1                       | 0    | 1                        | μΑ    |

| Input Leakage Current of V <sub>COM</sub><br>Amplifier   | I <sub>L_INN</sub>        | V <sub>COM</sub> Amplifier: INN = 0.5*A <sub>VDD</sub>                                                                          | -1                       | 0    | 1                        | μΑ    |

| Short-Circuit Current                                    | I <sub>SC</sub>           | OUT1-OUT14: OUTx = $V_{OH}$ , OUTx short to GND (source) through $10\Omega$                                                     | 170                      | 230  | 400                      | mA    |

|                                                          |                           | OUT1-OUT14: OUTx = $V_{OL}$ , OUTx short to $A_{VDD}$ (sink) through $10\Omega$                                                 | 150                      | 200  | 400                      | mA    |

|                                                          |                           | $V_{COM}$ Amplifier (OUTCOM):<br>OUTx = 0.5*A <sub>VDD</sub> _AMP, short to GND<br>(source) through 10 $\Omega$                 | 400                      | 530  | 700                      | mA    |

|                                                          |                           | $V_{COM}$ Amplifier (OUTCOM):<br>OUTx = 0.5*A <sub>VDD</sub> _AMP, short to<br>A <sub>VDD</sub> _AMP (sink) through 10 $\Omega$ | 450                      | 570  | 750                      | mA    |

| Load Regulation                                          | REG                       | OUT1-OUT14: I <sub>LOAD</sub> = ±5mA step                                                                                       | 0                        | 1.5  | 5                        | mV/mA |

|                                                          |                           | OUTCOM: I <sub>LOAD</sub> = ±5mA step                                                                                           | 0                        | 1.5  | 5                        | mV/mA |

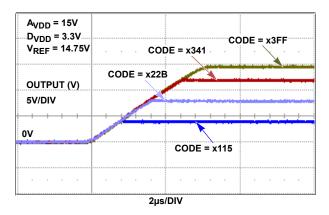

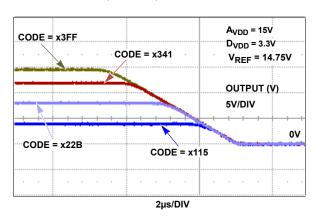

| Slew Rate                                                | SR                        | OUT1-OUT14: Full-scale DAC code change                                                                                          | 2                        | 5    | 40                       | V/µs  |

|                                                          |                           | $V_{COM}$ amplifier: $A_V = -1$ ,<br>$0.5V \le OUTx \le 5.5V$ , $C_L = 10pF$ to GND                                             | 4                        | 10   | 40                       | V/µs  |

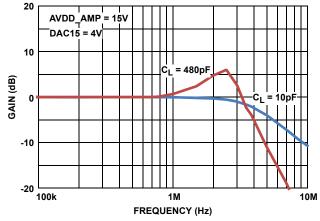

| V <sub>COM</sub> Amplifier Bandwidth                     | BW                        | $A_V = -1$ , $OUTx = 4V$ ,<br>$R_L = 10k\Omega \mid \mid C_L = 10pF \text{ to GND}$                                             |                          | 5    |                          | MHz   |

| Time to Load EEPROM Data to DAC<br>Registers at Power-ON | t <sub>Data_loading</sub> | Start of EEPROM loading to when OUTx is enabled, (Note 7)                                                                       |                          | 6    |                          | ms    |

| DIGITAL                                                  |                           |                                                                                                                                 | · ·                      |      |                          |       |

| Logic '1' Input Voltage                                  | V <sub>IH</sub>           | SCL, SDA, A0, WP                                                                                                                | 0.8*D <sub>VDD</sub>     |      |                          | V     |

| Logic 'O' Input Voltage                                  | $V_{IL}$                  | SCL, SDA, A0, WP                                                                                                                |                          |      | 0.2 * D <sub>VDD</sub>   | ٧     |

| I <sup>2</sup> C SCL Clock Frequency                     | f <sub>CLK</sub>          | ( <u>Note 8</u> )                                                                                                               |                          |      | 400                      | kHz   |

| Input Leakage Current                                    | IL                        | SCL, SDA, A0, WP: at GND                                                                                                        | -1                       | 0    | 1                        | μΑ    |

|                                                          |                           | SCL, SDA: at D <sub>VDD</sub>                                                                                                   | -1                       | 0    | 1                        | μA    |

|                                                          |                           | A0, WP: at D <sub>VDD</sub>                                                                                                     | 0.10                     | 0.55 | 1                        | μA    |

### NOTES:

- 6. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

- 7. The " $t_{\mbox{\scriptsize Data\_loading}}$  " parameter is determined by IC design, and simulation.

- 8. For more detailed information regarding I<sup>2</sup>C timing characteristics, refer to <u>Table 1</u> on <u>page 13</u>.

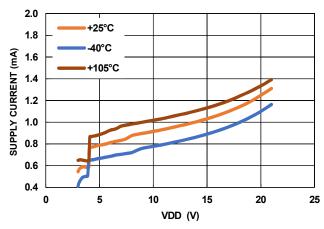

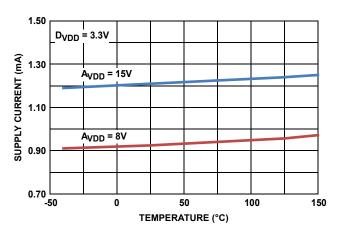

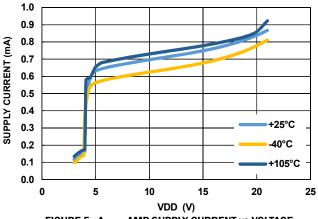

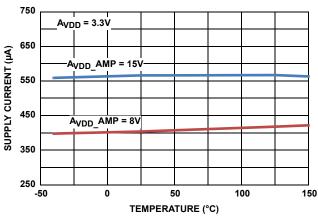

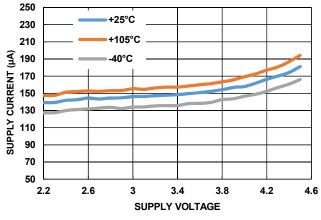

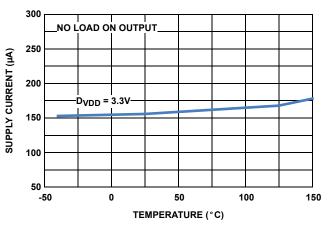

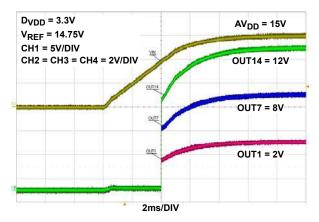

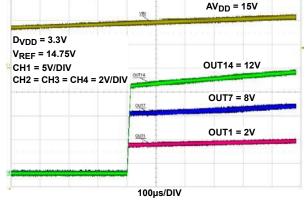

# Typical Performance Curves T<sub>A</sub> = +25 °C, unless otherwise specified.

FIGURE 3. A<sub>VDD</sub> SUPPLY CURRENT vs VOLTAGE

FIGURE 4. A<sub>VDD</sub> SUPPLY CURRENT vs TEMPERATURE

FIGURE 5. AVDD\_AMP SUPPLY CURRENT vs VOLTAGE

FIGURE 6. A<sub>VDD</sub>\_AMP SUPPLY CURRENT vs TEMPERATURE

FIGURE 7. D<sub>VDD</sub> SUPPLY CURRENT vs VOLTAGE

FIGURE 8. D<sub>VDD</sub> SUPPLY CURRENT vs TEMPERATURE

# Typical Performance Curves T<sub>A</sub> = +25 °C, unless otherwise specified. (Continued)

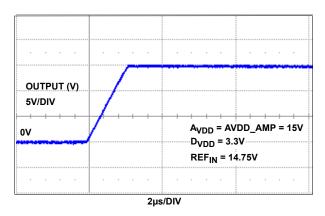

FIGURE 9. OUT1-OUT14 POSITIVE SLEW RATE (DAC CODE CHANGE)

FIGURE 10. OUT1-OUT14 NEGATIVE SLEW RATE (DAC CODE CHANGE)

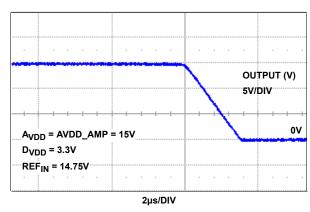

FIGURE 11.  $V_{\text{COM}}$  amplifier positive slew rate

FIGURE 12.  $V_{COM}$  AMPLIFIER NEGATIVE SLEW RATE

FIGURE 13. V<sub>COM</sub> AMPLIFIER BANDWIDTH vs CAPACITIVE LOADING

FIGURE 14. OUT1-OUT14 AND OUTCOM OUTPUT VOLTAGE vs OUTPUT CURRENT ( $V_{OH}$  AND  $V_{OL}$ )

# Typical Performance Curves T<sub>A</sub> = +25 °C, unless otherwise specified. (Continued)

FIGURE 15. DAC1-DAC15 INL (REF $_{IN}$  = A $_{VDD}$  = 15V) AT +25 °C

FIGURE 16. DAC1-DAC15 DNL (REF<sub>IN</sub> = A<sub>VDD</sub> = 15V) AT +25°C

FIGURE 17. DAC1-DAC15 TYPICAL INL (REF $_{

m IN}$  = A $_{

m VDD}$  = 15V) AT -40 °C

FIGURE 18. DAC1-DAC15 TYPICAL DNL (REF $_{

m IN}$  = A $_{

m VDD}$  = 15V) AT -40 ° C

FIGURE 20. DAC1-DAC15 DNL (REF $_{

m IN}$  = A $_{

m VDD}$  = 15V) AT +105  $^{\circ}$  C

# Typical Performance Curves T<sub>A</sub> = +25 °C, unless otherwise specified. (Continued)

FIGURE 21. OUT1-OUT7-OUT14 AT POWER-ON

FIGURE 22. OUT1-OUT7-OUT14 AT POWER-ON (ZOOMED IN)

FIGURE 23. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE (4-LAYER BOARD)

FIGURE 24. PACKAGE POWER DISSIPATION VS AMBIENT TEMPERATURE (2-LAYER BOARD)

### **General Description**

The Voltage/Transmission (V/T) transfer curve or gamma curve of LCD panels require adjustment to achieve the desired optimal visual response (often called gamma correction).

The ISL76534 has a total of 15 channels (14xgamma channels +  $1\text{xV}_{COM\ channel}$ ) independent, programmable reference voltage outputs whose output voltage can be set with 10-bit resolution. The ISL76534 has integrated EEPROM to store all gamma and  $V_{COM}$  data.

In addition to the 14-channel gamma DACs, the ISL76534 provides a  $V_{COM}$  calibrator DAC with 10-bit resolution and a high output current operational amplifier to drive the  $V_{COM}$  voltage also required by the LCD panel.

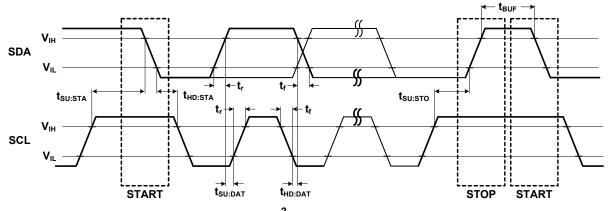

## I<sup>2</sup>C Digital Interface

The ISL76534 uses a standard I<sup>2</sup>C interface bus for communication. The two-wire interface links a master(s) and uniquely addressable slave devices. The master generates clock signals and is responsible for initiating data transfers. The serial clock is on the SCL line and the serial data (bidirectional) is on the SDA line. The ISL76534 supports clock rates up to 400kHz (fast-mode), and is backwards compatible with standard 100kHz clock rates (standard-mode).

The SDA and SCL lines must be HIGH when the bus if free - not in use. An external pull-up resistor (typically 2.2k $\Omega$  to 4.7k $\Omega$ ) or current source is required for SDA and SCL.

The ISL76534 meets standard I<sup>2</sup>C timing specifications; see Figure 25 and Table 1, which show the standard timing definitions and specifications for I<sup>2</sup>C communication.

### **Data Validity**

The data on the SDA line must be stable (clearly defined as HIGH or LOW) during the HIGH period of the clock signal. The state of the SDA line can only change when the SCL line is low (except to create a START or STOP condition). See timing specifications on Table 1 on page 13.

The voltage levels used to indicate a logical '0' (LOW) and logical '1' (HIGH) are determined by the  $V_{IL}$  and  $V_{IH}$  thresholds, respectively; see the "Electrical Specifications" table on page 6.

### **START and STOP Condition**

All I<sup>2</sup>C communication begins with a START condition, indicating the beginning of a transaction, and ends with a STOP condition, signaling the end of the transaction.

A START condition is signified by a HIGH to LOW transition on the Serial Data line (SDA) while the Serial Clock Line (SCL) is HIGH. A STOP condition is signified by a LOW to HIGH transition on the SDA line while SCL is HIGH. See timing specifications in Table 1.

The master always initiates START and STOP conditions. After a START condition, the bus is considered "busy." After a STOP condition, the bus is considered "free." The ISL76534 also supports repeated STARTs, where the bus will remain busy for continued transaction(s).

### **Byte Format**

Every byte on the SDA must be 8 bits in length. After every byte of data sent by the transmitter, there must be an acknowledge bit (from the receiver) to signify that the previous 8 bits were transferred successfully. Data is always transferred on the SDA with the Most Significant Bit (MSB) first. If the data is larger than 8 bits then it can be separated into multiple 8-bit bytes. See "Data Word (WRITE/READ)" on page 19.

### **Acknowledge (ACK)**

Each 8-bit data transfer is followed by an Acknowledge (ACK) bit from the receiver. The Acknowledge bit signifies that the previous 8 bits of data was transferred successfully (master-slave or slave-master).

When the master sends data to the slave (e.g. during a WRITE transaction), after the 8<sup>th</sup> bit of a data byte is transmitted, the master tri-states the SDA line during the 9<sup>th</sup> clock. The slave device acknowledges that it received all 8 bits by pulling down the SDA line, generating an ACK bit.

When the master receives data from the slave (e.g. during a data READ transaction), after the 8<sup>th</sup> bit is transmitted, the slave tri-states the SDA line during the 9<sup>th</sup> clock. The master acknowledges that it received all 8 bits by pulling down the SDA line, generating an ACK bit.

FIGURE 25. I<sup>2</sup>C TIMING DEFINITIONS

| TADIE 1 | 12C TIMING | CHARACTERISTICS |

|---------|------------|-----------------|

|         |            |                 |

|                                                  |                     | FAST-MC                | DDE | STANDARI | D-MODE |      |

|--------------------------------------------------|---------------------|------------------------|-----|----------|--------|------|

| PARAMETER                                        | SYMBOL              | MIN                    | MAX | MIN      | MAX    | UNIT |

| SCL Clock Frequency                              | f <sub>SCL</sub>    | 0                      | 400 | 0        | 100    | kHz  |

| Set-Up Time for a START Condition                | t <sub>SU:STA</sub> | 0.6                    |     | 4.7      |        | μs   |

| Hold Time for a START Condition                  | thd:STA             | 0.6                    |     | 4.0      |        | μs   |

| Set-Up Time for a STOP Condition                 | tsu:sto             | 0.6                    |     | 4.0      |        | μs   |

| Bus Free Time between a STOP and START Condition | t <sub>BUF</sub>    | 1.3                    |     | 4.7      |        | μs   |

| Data Set-Up Time                                 | t <sub>SU:DAT</sub> | 100                    |     | 250      |        | ns   |

| Data Hold Time                                   | t <sub>HD:DAT</sub> | 0                      |     | 0        |        | μs   |

| Rise Time of SDA and SCL (Note 9)                | t <sub>r</sub>      | 20 + 0.1C <sub>b</sub> | 300 |          | 1000   | ns   |

| Fall Time of SDA and SCL (Note 9)                | t <sub>f</sub>      | 20 + 0.1C <sub>b</sub> | 300 |          | 300    | ns   |

NOTE:

9. C<sub>b</sub> = total capacitance of one bus line in pF

### **Not Acknowledge (NACK)**

A Not Acknowledge (NACK) is generated when the receiver does not pull down the SDA line during the acknowledge clock (i.e., SDA line remains HIGH during the 9<sup>th</sup> clock). This indicates to the master that it can generate a STOP condition to end the transaction and free the bus.

A NACK can be generated for various reasons, for example:

- After an I<sup>2</sup>C device address is transmitted, there is NO receiver with that address on the bus to respond.

- The receiver is busy performing an internal operation (e.g. reset, recall, etc.), and cannot respond.

- The master (acting as a receiver) needs to indicate the end of a transfer with the slave (acting as a transmitter).

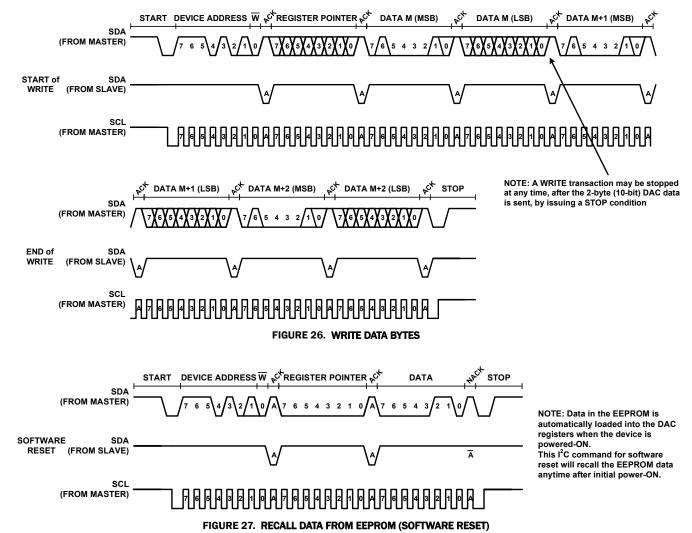

### Device Address and $R/\overline{W}$ Bit

Data transfers follow the format shown in Figures 26 through 27. After a valid START condition, the first byte sent in a transaction contains the 7-bit device (slave) Address plus a direction ( $R/\overline{W}$ ) bit. The Device Address identifies which device (of up to 127 devices on the  $I^2C$  bus) the master wishes to communicate with.

After a START condition, the ISL76534 monitors the first 8 bits (Device Address byte) and checks for it is 7-bit Device Address in the MSBs. If it recognizes the correct Device Address it will ACK, and becomes ready for further communication. If it does not see it is Device Address, it will sit idle until another START condition is issued on the bus.

To access the ISL76534 DACs, the Device Addresses allowed are 0x74 hex (1110100x), or 0x75 hex (1110101x). The first 6 bits (b<sub>7</sub> to b<sub>2</sub>, MSBs) of the 7-bit device address have been factory programmed and are always 111010. Only the least significant bit of the Device Address (bit b<sub>1</sub>, LSB) is allowed to change. The value of the LSB (bit b<sub>1</sub>) is set by the hardware "A0" pin. When A0 = HIGH, the device will only respond to a Device Address of 0x75. When A0 = LOW, the device will only respond to a Device Address of 0x74. This allows for two ISL76534 devices to be used on the same I $^2$ C bus, each with a different Device Address.

Note: The eighth bit of the Device Address byte (bit  $b_0$ ) indicates the direction of transfer, READ or WRITE (R/ $\overline{W}$ ). A "0" indicates a WRITE operation- the master will transmit data to the ISL76534 (receiver). A "1" indicates a Read operation- the master will receive data from the ISL76534 (transmitter).

### **Application Information**

### **ISL76534 Communication Protocol**

The ISL76534 allows the user to sequentially read or write all the registers with a single multi-byte I<sup>2</sup>C READ or WRITE operation ("Burst Mode").

The ISL76534 also allows the user to READ or WRITE to a specific register only (or a specific range of registers), using Register Pointer addressing ("Register Mode"). With Register Mode, a specific  $V_{COM}$  value, Gamma DAC value or range of values may be read or written without having to read or write the other registers.

### **Register Description and Pointer**

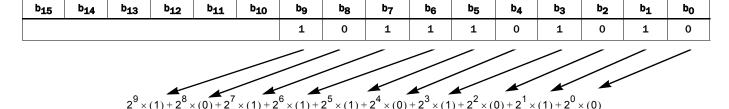

Table 2 contains a detailed register description. All registers contain 10 bits, which span over two data bytes (16 bits) and the data is latched-in after the 16<sup>th</sup> bit (LSB) is received. The only exception is the Control Register, where the data is latched in after the first 8 bits are received.

Reading/writing always begins at location specified by the Register Pointer. The Register Pointer automatically increments by 0x01 with every two bytes transferred. For example, when using Register Pointer 0x01 to address DAC1 (MSB and LSB), the device automatically increments the pointer to 0x02, 0x03... after every two data bytes are received. This enables Burst Mode operation where only the first Register Pointer for a given sequence of registers is needed.

To address separate or non-sequential register locations, a full I<sup>2</sup>C START, Device Address, Register Pointer, Data..., STOP sequence must be used to address each register location; see "WRITE TRANSACTION" on page 15.

The Control Register is located at Register Pointer 0x00, while the 10-bit DAC data is at Register Pointers 0x01 though 0x0F.

### **TABLE 2. REGISTER DESCRIPTION**

| REGISTER<br>POINTER | REGISTER                                                                               | BIT(S) | FUNCTION NAME              | DESCRIPTION                                                                                                                                                                                          |

|---------------------|----------------------------------------------------------------------------------------|--------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00                | Control Byte                                                                           | 15:14  | Reserved                   | Set to 0                                                                                                                                                                                             |

|                     | (data latched in after each byte, b[15:8] and b[7:0], is received by I <sup>2</sup> C) | 13:12  | Reserved                   | Set to 0                                                                                                                                                                                             |

|                     |                                                                                        | 11     | Output Enable (active low) | 0: Outputs Enabled, default at power-ON 1: Outputs Disabled                                                                                                                                          |

|                     |                                                                                        |        | Recall EEPROM              | 00: Normal Operation 11: When Register Pointer 0x00 = 0x06; "Software Reset." Recalls stored EEPROM data to DAC registers. Device will NACK during the 9th SCL pulse when a Reset command is issued. |

|                     |                                                                                        | 8:0    | Reserved                   | Set to 0                                                                                                                                                                                             |

| 0x01 ~ 0x0F         | Gamma Data                                                                             | 15     | Reserved                   | Set to 0                                                                                                                                                                                             |

|                     |                                                                                        | 14     | Write EEPROM               | 0: Write data to DAC only 1: Write data to DAC and EEPROM                                                                                                                                            |

|                     |                                                                                        | 13:10  | Reserved                   | Set to 0                                                                                                                                                                                             |

|                     |                                                                                        | 9:0    | DAC data                   | 10-bit data for DACs 1 through 15                                                                                                                                                                    |

| 0x10 ~ 0xFF         | Reserved                                                                               | 15:0   | Reserved                   | Do not write data to these registers                                                                                                                                                                 |

#### NOTES:

- 10. Any Register Pointers not indicated in <a href="Table 2">Table 2</a> are Reserved Registers, and should not be used.

- 11. A write to an EEPROM register can take up to 35ms to complete. To avoid errors and ensure correct EEPROM data, any writes to EEPROM registers should be spaced at least 35ms apart. For more information, refer to "Writing to the EEPROM" on page 20.

# **Write Operation**

Table 3 describes a write operation and Figures 26 and 27 shows the write timing diagram.

**TABLE 3. WRITE TRANSACTION**

| I <sup>2</sup> C DATA<br>FROM MASTER | I <sup>2</sup> C DATA<br>FROM ISL76534 | NOTES                                                                                                                                                                                                                                                                                                                                                                           |

|--------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START                                |                                        | I <sup>2</sup> C START Signal                                                                                                                                                                                                                                                                                                                                                   |

| OxE8 or OxEA                         | ACK                                    | Send Device Address + $R/\overline{W}$ bit (depends on the state of A0 pin) 1110100 + 0, if A0 = LOW 1110101 + 0, if A0 = HIGH                                                                                                                                                                                                                                                  |

| Register Pointer                     | ACK                                    | Register Pointer indicating starting register location to write to. Register Pointer = 0x00 for Control Byte Register Pointer = 0x01 for DAC 1 MSB/LSB data Register Pointer = 0x02 for DAC 2 MSB/LSB data Register Pointer = 0x0E for DAC 14 MSB/LSB data Register Pointer = 0x0F for DAC 15 MSB/LSB data For more information on the Register Pointer see Table 2 on page 14. |

| Byte 1                               | ACK                                    | If Register Pointer = 0x00, Byte 1 is the Control Byte. When Register Pointer = 0x00 and Byte 1 = 0x06, data is recalled from EEPROM and written into the DAC registers (RAM).  If Register Pointer = 0x01 or more, Byte 1 is the MSB byte of the DAC word                                                                                                                      |

| Byte 2                               | ACK                                    | If Register Pointer = 0x00, Byte 2 is a null byte and will be ignored If Register Pointer = 0x01 or more, Byte 2 is the LSB of the DAC word                                                                                                                                                                                                                                     |

| Byte 3                               | ACK                                    | MSB of DAC (1 + Register Pointer). Ex) Register Pointer = 0x00, MSB of DAC1                                                                                                                                                                                                                                                                                                     |

| Byte 4                               | ACK                                    | LSB of DAC (1 + Register Pointer). Ex) Register Pointer = 0x00, LSB of DAC1                                                                                                                                                                                                                                                                                                     |

| Byte 5                               | ACK                                    | MSB of DAC (2 + Register Pointer)                                                                                                                                                                                                                                                                                                                                               |

| Byte 6                               | ACK                                    | LSB of DAC (2 + Register Pointer)                                                                                                                                                                                                                                                                                                                                               |

|                                      |                                        | The WRITE operation can be stopped at any time after a register has been written. The DAC channel output is updated after ALL 10-bit channel data is received.                                                                                                                                                                                                                  |

| STOP                                 |                                        | I <sup>2</sup> C STOP Signal                                                                                                                                                                                                                                                                                                                                                    |

### **Write Timing Diagrams**

# **Read Operation**

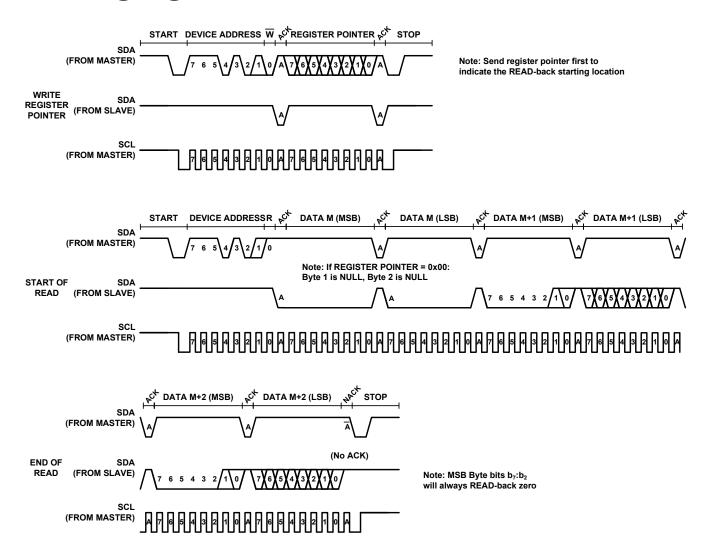

$\underline{\textbf{Table 4}} \ \text{describes a Read operation and } \underline{\textbf{Figure 28}} \ \text{shows the} \\ \textbf{read timing diagram}.$

**TABLE 4. READ TRANSACTION**

| I <sup>2</sup> C DATA<br>FROM MASTER | I <sup>2</sup> C DATA<br>FROM ISL76534   | NOTES                                                                                                                                                                                                                                                                                                                                                                                  |  |

|--------------------------------------|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| START                                |                                          | I <sup>2</sup> C START Signal                                                                                                                                                                                                                                                                                                                                                          |  |

| OxE8 or OxEA                         | ACK                                      | Send Device Address + $R/\overline{W}$ Bit (depends on the state of AO pin)<br>1110100 + 0, if AO = LOW<br>1110101 + 0, if AO = HIGH                                                                                                                                                                                                                                                   |  |

| Register Pointer                     | ACK                                      | Register Pointer indicating starting register location to write to.  Register Pointer = 0x00 for Control Byte  Register Pointer = 0x01 for DAC 1 MSB/LSB data  Register Pointer = 0x02 for DAC 2 MSB/LSB data   Register Pointer = 0x0E for DAC 14 MSB/LSB data  Register Pointer = 0x0F for DAC 15 MSB/LSB data  For more information on the Register Pointer see Table 2 on page 14. |  |

| STOP                                 |                                          | I <sup>2</sup> C STOP signal                                                                                                                                                                                                                                                                                                                                                           |  |

| START                                |                                          | I <sup>2</sup> C START signal                                                                                                                                                                                                                                                                                                                                                          |  |

| 0xE9                                 | ACK                                      | Send Device Address + R/W Bit 1110100 + 1                                                                                                                                                                                                                                                                                                                                              |  |

| OxE9 or OxEB                         | ACK                                      | Send Device Address + $R/\overline{W}$ Bit (depends on the state of A0 pin)<br>1110100 + 1, if A0 = LOW<br>1110101 + 1, if A0 = HIGH                                                                                                                                                                                                                                                   |  |

| ACK                                  | Byte 1                                   | If Register Pointer = 0x00, Byte 1 is a Null Byte If Register Pointer = 0x01 or more, Byte 1 is the MSB byte of the DAC word                                                                                                                                                                                                                                                           |  |

| ACK                                  | Byte 2                                   | If Register Pointer = 0x00, Byte 2 is a Null Byte If Register Pointer = 0x01 or more, Byte 2 is the LSB byte of the DAC word                                                                                                                                                                                                                                                           |  |

| ACK                                  | Byte 3                                   | MSB of DAC (1 + Register Pointer). Ex) Register Pointer = 0x00, MSB of DAC1                                                                                                                                                                                                                                                                                                            |  |

| ACK                                  | Byte 4                                   | LSB of DAC (1 + Register Pointer). Ex) Register Pointer = 0x00, LSB of DAC1                                                                                                                                                                                                                                                                                                            |  |

| ACK                                  | Byte 5 MSB of DAC (2 + Register Pointer) |                                                                                                                                                                                                                                                                                                                                                                                        |  |

| ACK                                  | Byte 6                                   | Byte 6 LSB of DAC (2 + Register Pointer)                                                                                                                                                                                                                                                                                                                                               |  |

|                                      |                                          | The READ operation can be stopped at any time after a register has been read                                                                                                                                                                                                                                                                                                           |  |

| NAK                                  | DAC 15 LSB                               | 8 LSBs of DAC 15's 10-bit value: dddd dddd                                                                                                                                                                                                                                                                                                                                             |  |

| STOP                                 |                                          | I <sup>2</sup> C STOP Signal                                                                                                                                                                                                                                                                                                                                                           |  |

### **Read Timing Diagram**

NOTE: The READ operation can be stopped at any time after the DAC register data has been read by sending a STOP condition.

#### FIGURE 28. READ TIMING DIAGRAM

### TABLE 5. DAC CALCULATION

### Data Word (WRITE/READ)

Data Words contain the data written or read from the 10-bit DACs. Each 10-bit DAC data is transmitted in one word (e.g. two bytes, 16-bits), as shown in Table 5. Bits  $[b_9:b_0]$  represent the 10-bit data. Bits  $[b_{15}:b_{10}]$  are "do not cares" and will default to zero when reading data, however, when writing data bit  $b_{14}$  indicates the type of write. If  $b_{14}$  = '0': WRITE data to the DAC register; if  $b_{14}$  = '1': WRITE data to the DAC and EEPROM (program).

For any DAC, the first data byte of the word is called the Upper Byte (or MSB), and the two LSBs of this byte represent the MSBs of the 10-bit data, [b<sub>9</sub>:b<sub>8</sub>]. The second data byte of the word, or Lower Byte (LSB), contains the remaining 8-bits (LSBs) of the 10-bit DAC data, [b<sub>7</sub>:b<sub>0</sub>]. These data words provide the DAC values that ultimately determine the output voltages of the ISL76534.

Refer to <u>Table 2</u> for more information about the byte structure, and refer to the following sections for information about the expected DAC output voltage.

### **DAC Transfer Function of OUT1-OUT14**

Equation 1 shows the transfer function for each 10-bit DAC channel (expected output voltage). The transfer function relates the REF<sub>IN</sub> voltage and a DAC\_CODE to a DAC output voltage, "V<sub>OUT</sub>." The DAC\_CODE is the decimal value of the 10-bit data written to a given DAC channel.

$$V_{OUT} = REF_{IN} \times \frac{DAC\_CODE}{1024}$$

(EQ. 1)

DAC\_CODE: 0 ~ 1023

Example calculation to find the expected VOUT:

$$A_{VDD} = 15V$$

REF<sub>IN</sub> = 14.75V

$1LSB = \frac{14.75V}{1024} = 14.40mV$

$V_{OUT} = 14.40mV \times DAC\_CODE$

$V_{OUT}(DAC\_CODE = 512) = 14.40mV \times 512 = 7.375V$

### **DAC Output Accuracy**

The relationship between the actual/measured DAC output voltage and the expected voltage is the "Output Accuracy" (OUT<sub>AC</sub>). <u>Equation 2</u> shows how to determine output accuracy:

$$OUT_{AC} = V_{OUT(expected)} - V_{OUT(measured)}$$

(EQ. 2)

The ISL76534 features are very good and have consistent output accuracy across all DAC codes and REF<sub>IN</sub> voltages, ±15mV (typical). Some competitor devices have diverging accuracy performance near the high rail and have significantly larger output accuracy variances compared to ISL76534.

The output accuracy performance of the ISL76534 provides highly accurate reference voltages ideal for TFT-LCD applications. This is important in TFT-LCD applications that require the DACs/EEPROM to be programmed with the same digital codes (e.g. gamma references determined from gamma calibration) on a production line, and especially when using reflected code

gamma calibration methods. Ensuring accurate gamma references is also important for optimizing pixel/panel reliability.

### **DAC Reference Voltage**

The REF $_{\text{IN}}$  pin is the reference voltage input for the 10-bit DACs. It is a high impedance input. The voltage can be set using an external resistor divider, regulated voltage, or tied directly to the A $_{\text{VDD}}$  power rail. The REF $_{\text{IN}}$  pin should always be well bypassed to minimize noise, and provide the best DAC performance. Use a 0.1 $\mu$ F ceramic capacitor (to GND), placed as close to the pin as possible.

See example of the typical application circuits in <u>Figures 30</u> and <u>31</u>.

### **DAC Channel Outputs**

The DAC output buffers are optimized to drive rail-to-rail for optimal flexibility. Generally, in a TFT-LCD half of the required gamma reference voltages will lie between  $V_{COM}$  and  $A_{VDD}$  (or  $REF_{IN}$ ), and the other half will lie between  $V_{COM}$  and GND. For maximum flexibility, all ISL76534 outputs (OUT1-OUT14) can drive to within 100mV of  $REF_{IN}$  ( $A_{VDD}=REF_{IN}$ ) and to within 85mV of GND (with  $\pm 5$ mA load). See "Electrical Specifications" table on page 6 for more details about output channel capabilities.

Each DAC is updated as soon as the entire 10-bit value for that DAC is received via  $I^2$ C. DAC data is latched, and the respective DAC responds, on the falling edge of the 8th SCL clock (which corresponds to the DAC LSB data bit, bit  $b_0$ ).

### **V<sub>COM</sub>** Amplifier

The ISL76534  $V_{COM}$  amplifier is capable of rail-to-rail output swings and the ability to drive highly capacitive loads. It can source/sink up to 100mA of continuous current and over 500mA of peak current. The output capability of the  $V_{COM}$  amplifier is described in detail in "Electrical Specifications" table on page 6.

The  $V_{COM}$  amplifier is powered from a separate power supply than the rest of the IC, called  $A_{VDD}$ \_AMP. This allows  $A_{VDD}$ \_AMP to be set at a voltage lower than AVDD, to save system power. Though it is acceptable to set  $A_{VDD}$ \_AMP =  $A_{VDD}$ .

A<sub>VDD</sub>\_AMP is not required for the rest of the IC to operate, so if an application is not utilizing the V<sub>COM</sub> Amplifier in the ISL76534 (OUTCOM), then A<sub>VDD</sub>\_AMP can be tied to GND to disable the function and save IC and system power. If A<sub>VDD</sub>\_AMP is powered but not connected in the application, then the V<sub>COM</sub> amplifier should be set in a buffer (A<sub>V</sub> = +1) configuration (INN\_COM tied to OUTCOM). See example typical application circuits in Figures 30 and 31.

The device offers access to the inverting pin of the amplifier, INN\_COM, which enables various types of circuit configurations depending on the requirements of the TFT-LCD panel architecture. Most common applications either buffer the amplifier for direct driving and response (INN\_COM tied to OUTCOM), or they may utilize feedback from the TFT-LCD panel as an input to the INN\_COM pin.

### **Output Stability**

The ISL76534 outputs are designed to drive capacitive loads, such as in TFT-LCD panel. However, purely capacitive loads should not exceed 1nF without appropriate external load isolation and/or amplifier compensation.

As load capacitance increases, the -3dB bandwidth will decrease and peaking can occur. Depending on the application, it may be necessary to reduce peaking and improve device stability. To do this, a snubber circuit (compensation) or a series resistor (isolation) may be added to the output of the ISL76534.

A snubber is a shunt load consisting of a resistor in series with a capacitor. An optimized snubber can improve the phase margin and the stability of the ISL76534 by adding a zero in the loop response. The advantage of a snubber circuit is that it does not draw any DC load current or reduce the gain.

Another method to reduce peaking is to add a series output resistor (typically between  $1\Omega$  to  $10\Omega$ ). Depending on the capacitive loading, a small value resistor may be the most appropriate choice to minimize any reduction in gain.

### Write Protection (WP)

The ISL76534 has an I $^2$ C write protection ( $\overline{WP}$ ) pin.  $\overline{WP}$  is a logic level input pin and is active low.

- WP = 0 (LOW): Protected, device ignores I<sup>2</sup>C data writes to the internal DAC registers and EEPROM

- WP = 1 (HIGH): Not Protected, device allows I<sup>2</sup>C data writes to the internal DAC registers and EEPROM

Whether  $\overline{WP}$  is set HIGH or LOW, the device will ACK to proper I<sup>2</sup>C commands, however, when  $\overline{WP}$  = LOW the device internally ignores the data bytes.

The logic state of  $\overline{\text{WP}}$  can be changed during device operation. However,  $\overline{\text{WP}}$  should not be changed during the EEPROM write procedure time.

### **Writing to the EEPROM**

During an  $I^2C$  transaction, setting bit  $b_{14}$  of a Data Word HIGH indicates to the device that the data in that same Data Word should be written to both the DAC and EEPROM. The EEPROM programming cycle for the appropriate channel(s) is started as soon as a subsequent STOP command is issued on the  $I^2C$  bus.

After the STOP condition is issued, it takes up to 35ms (maximum) for a single EEPROM Register Write, and 420ms (maximum) to write all registers to EEPROM. To ensure EEPROM data validity, wait at least 35ms between single EEPROM Register Writes, and before sending any other  $\rm I^2C$  commands. When writing all registers to EEPROM, wait at least 420ms before sending any other  $\rm I^2C$  commands. During the EEPROM programming cycle time, the device's  $\rm I^2C$  bus is internally busy and will NACK  $\rm I^2C$  commands.

Note, the normal DAC writes (bit  $b_{14} = '0'$ ) can be written to as quickly as the  $I^2C$  bus can support.

#### **OUT1-OUT14 AND OUTCOM BEHAVIOR**

During the EEPROM writing/programming cycle the ISL76534 gamma outputs (OUT1-OUT14) and V<sub>COM</sub> amplifier output (OUTCOM) remain enabled.

### **Recalling The EEPROM**

There are two ways to initiate a recall of the stored EEPROM data:

- Automatic recall Power cycle (or power-ON) the device

- Manual recall Perform a "software reset" using I<sup>2</sup>C

The recall operation will overwrite all current DAC register values with the values stored in EEPROM.

#### **AUTOMATIC RECALL**

When the device is powered-ON, the ISL76534 automatically recalls the EEPROM data and loads it into the DAC registers (RAM) after D<sub>VDD</sub> reaches ~2.2V. The time for the EEPROM recall to complete is the "t<sub>Data\_loading</sub>" time and is 6ms (typical) by design. This operation restores all DAC registers to the values stored in EEPROM.

#### **MANUAL RECALL**

A recall can be initiated by performing a software reset using I<sup>2</sup>C. A software reset is done by writing data 0x06 to Register Pointer 0x00 (Control Byte), and then on the falling edge of 8<sup>th</sup> SCL clock (of the Control Byte), the recall operation will be started. The device will then issue a NACK on the 9<sup>th</sup> SCL clock.

Recalling the ISL76534 EEPROM data to the output DACs takes 6ms typical) to complete. During the EEPROM recall time (power-ON or during a software reset), OUT1-OUT14 and OUTCOM will be set to high impedance and the device will NACK to any I<sup>2</sup>C commands. Once the EEPROM recall is complete OUT1-OUT14 and OUTCOM will enable simultaneously and the outputs will slew to the correct level. If some or all of the outputs (OUT1-OUT14, OUTCOM) need to be defined (not high impedance) during this delay time, an external resistor divider may be used to set a "coarse" voltage until the DAC outputs are enabled.

Note, the ISL76534 EEPROM values are pre-programmed to the default values explained in the <u>"DEFAULT EEPROM VALUES"</u> section

#### **EEPROM Default Values**

The ISL76534 has factory programmed (default) EEPROM values for the output channels, which will be recalled from EEPROM and loaded to the DAC registers at initial power-ON. The default EEPROM values are shown in <u>Table 6</u>.

**TABLE 6. DEFAULT EEPROM VALUES**

| DAC #   | CHANNEL | CODE (hex) | EXPECTED OUTPUT<br>VOLTAGE (V) |

|---------|---------|------------|--------------------------------|

| DAC1-14 | OUT1-14 | 0x000      | GND                            |

| DAC15   | оитсом  | 0x200      | REF <sub>IN</sub> /2           |

### **UVLO and Output Enable**

The ISL76534 includes an Undervoltage Lock-Out (UVLO) for  $A_{VDD}$ . At power-ON the output drivers, OUTx and OUTCOM, are initially in a high impedance (disabled) state,  $A_{VDD}$  < UVLO.

The OUT1-OUT14 outputs are ENABLED when the internal EEPROM recall has been completed (see "Recalling The EEPROM" on page 20), and  $A_{VDD}$  rises above 4.5V (maximum). Although OUTCOM is powered from  $A_{VDD}$ AMP, it is internally linked to the  $A_{VDD}$  UVLO function. The OUTCOM will be enabled when  $A_{VDD}$  and  $A_{VDD}$ AMP rise above 4.5V (maximum).

The OUT1-OUT14 and OUTCOM outputs are DISABLED if  $A_{VDD}$  falls below 3.5V (minimum).

### **Power Sequencing**

The ISL76534 has no restrictions on power supply sequencing of  $A_{VDD}$  and  $D_{VDD}$ .  $A_{VDD}$ \_AMP should not exceed  $A_{VDD}$ .  $A_{VDD}$ \_AMP can also be set to GND to disable the function.

The DAC reference, REF $_{IN}$ , voltage should not exceed  $A_{VDD}$ . This ensures the ESD protection diodes from REF $_{IN}$  to  $A_{VDD}$  do not become forward biased. If REF $_{IN}$  does exceed  $A_{VDD}$ , then the current flow through the ESD diode should not exceed 10mA.

#### Thermal Shutdown

The ISL76534 features thermal shutdown, which protects the device from damage due to overheating. When the junction (die) temperature rises to 160°C (typical) all outputs, OUTx and OUTCOM, are disabled (high-impedance). When the die temperature cools by 20°C (typical) all outputs are re-enabled.

### **Power Dissipation**

With high short-circuit and continuous output current capability for each channel, it is possible to exceed the +150°C absolute maximum junction (die) temperature. Therefore, it is important to calculate the maximum junction temperature for the application to determine if load or circuit conditions need to be modified to keep the device in a safe operating region.

The maximum power dissipation allowed in a package is determined according to <a href="Equation 3">Equation 3</a>:

$$P_{DMAX} = \frac{T_{JMAX} - T_{AMAX}}{\Theta_{JA}}$$

(EQ. 3)

#### Where:

- T<sub>JMAX</sub> = Maximum junction temperature

- T<sub>AMAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- P<sub>DMAX</sub> = Maximum power dissipation in the package

For more details on the allowable package power dissipation, refer to <u>Figures 23</u> and <u>24</u>.

# Power Supply Bypassing and Printed Circuit Board Layout

Good Printed Circuit Board (PCB) layout is necessary for optimum performance. The following are recommendations to achieve optimum high frequency performance from your PCB.

- To optimize thermal performance, solder the ISL76534's

exposed thermal pad to GND. PCB vias should be placed below

the device's exposed thermal pad and connected to GND to

transfer heat away from the device (see "General PowerPAD

Design Considerations"). If the thermal pad is not connected to

GND then it should be electrically isolated.

- Maximize use of AC decoupled PCB layers. All signal I/O lines should be routed over continuous ground planes (i.e., no split planes or PCB gaps under these lines). Avoid vias in the signal I/O lines.

- When testing, use good quality connectors and cables, match cable types and keep cable lengths to a minimum.