## Description

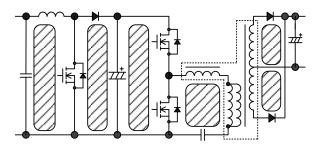

The MD6752 is a fully digital-controlled power supply IC, which incorporates a bridgeless PFC control circuit and an LLC current-resonant circuit. The PFC circuit, driven by continuous conduction mode (CCM), is controlled with frequencies suitable for applied input voltages and loads. The IC incorporates current mode for controlling constant voltages in the LLC stage and a floating drive circuit that drives an external high-side power MOSFET, in addition to functionally-rich protections. These digitally controlled strategies allow application-specific optimal settings. Compared to conventional analog control circuits, the IC can achieve more cost-effective, high-efficient, yet low-noise power systems with fewer external components.

## Features

- Fully Digital-controlled PFC and LLC Current-resonant Circuits

- Soft Start

- Bridgeless PFC Circuit

- Continuous Conduction Mode (CCM) PFC Control

- Current Mode LLC Control

- Protections Include:

- AC Power Supply Input Undervoltage Lockout

- AC Power Supply Input Off-state Detection

- PFC Output Undervoltage Protection (PFC\_UVP)

- PFC Output Overvoltage Protection (PFC\_OVP)

- PFC Overcurrent Protection (PFC\_OCP)

- PFC Overload Protection (PFC\_OLP)

- LLC High-side Driver Undervoltage Lockout (VB\_UVLO)

- LLC Overcurrent Protection (LLC\_OCP)

- LLC Overload Protection (LLC\_OLP)

- VCC Pin Overvoltage Protection (VCC\_OVP)

- Thermal Shutdown (TSD)

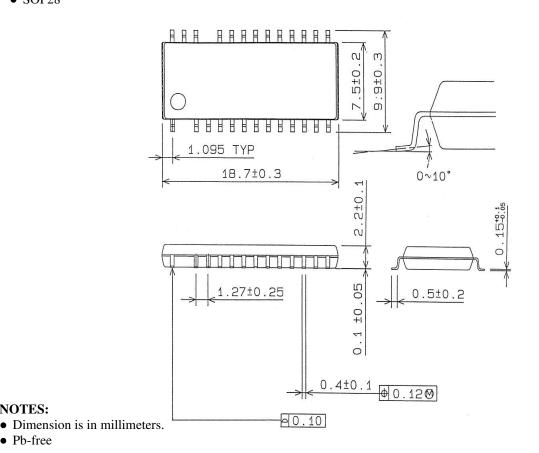

## Package

SOP28

Not to scale

## Applications

For devices requiring high power supplies such as:

- Audiovisual Equipment

- Office Automation Equipment (e.g., Server, Multifunction Printer)

- Industrial Equipment

- Communication Equipment

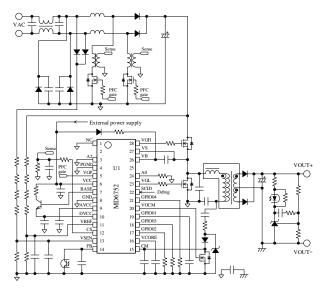

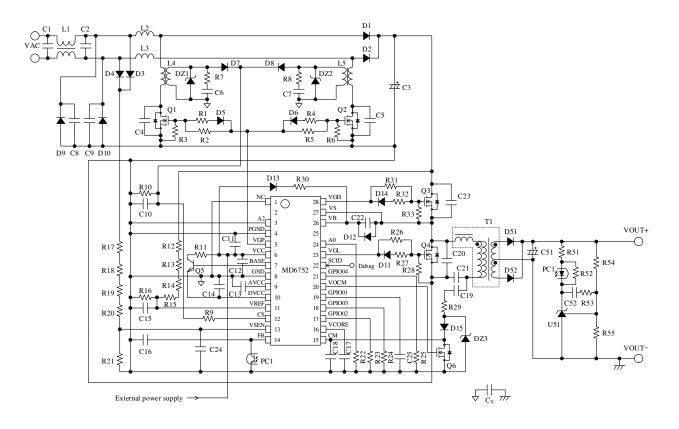

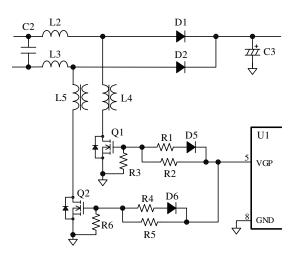

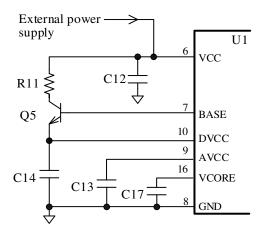

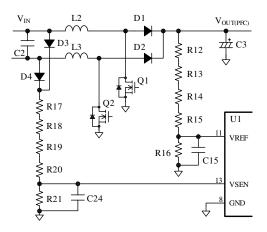

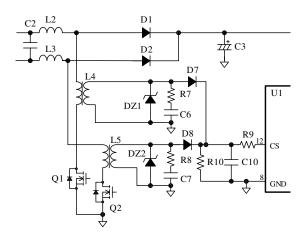

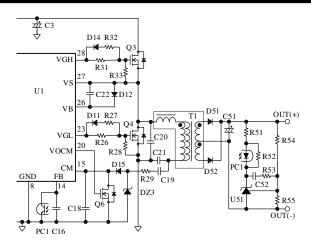

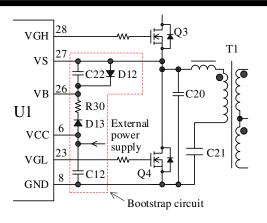

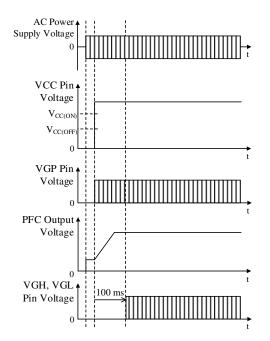

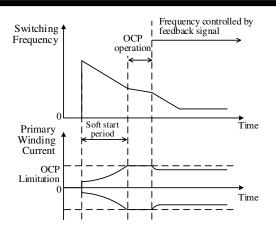

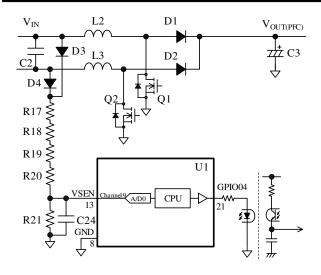

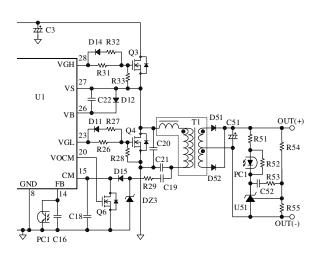

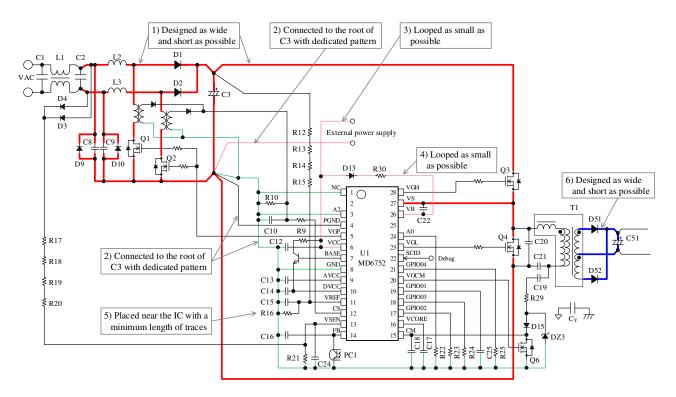

## **Typical Application**

# Contents

| Description  |                                                   | 1         |

|--------------|---------------------------------------------------|-----------|

| Contents     |                                                   | 2         |

| 1. Absolute  | e Maximum Ratings                                 | 4         |

| 2. Electrica | al Characteristics                                | 5         |

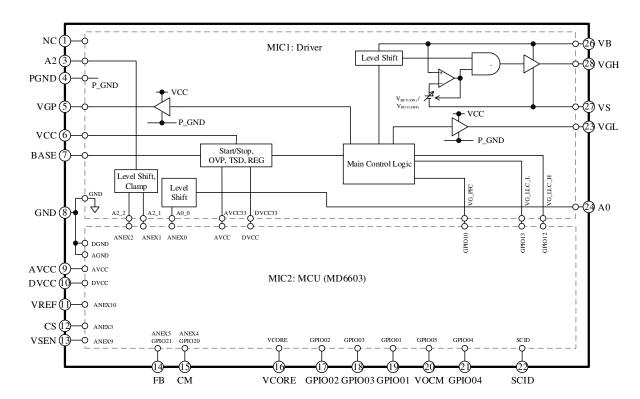

| 3. Block D   | iagram                                            | 9         |

|              | figuration Definitions                            |           |

|              | Application                                       |           |

| • •          | Dimensions                                        |           |

| •            | g Diagram                                         |           |

|              | onal Description                                  |           |

| 8.1. Gei     | neral Description                                 | 13        |

| 8.2 Pin      | Descriptions                                      | 13        |

| 8.2.1.       | A0                                                |           |

| 8.2.2.       | A2                                                |           |

| 8.2.3.       | GND and PGND                                      | -         |

| 8.2.4.       | VGP                                               |           |

| 8.2.5.       | VCC                                               | -         |

| 8.2.6.       | DVCC and BASE                                     | 14        |

| 8.2.7.       | AVCC                                              | 14        |

| 8.2.8.       | VREF                                              | 14        |

| 8.2.9.       | CS                                                | 15        |

| 8.2.10.      | VSEN                                              |           |

| 8.2.11.      | FB                                                |           |

| 8.2.12.      |                                                   |           |

| 8.2.13.      | VCORE                                             |           |

| 8.2.14.      | GPIO01 to GPIO04                                  |           |

| 8.2.15.      | VOCM                                              |           |

| 8.2.16.      |                                                   |           |

|              | VGL and VGH                                       |           |

|              | VB and VS                                         |           |

|              | rtup Operation                                    |           |

|              | t Start Function                                  | 17        |

|              | Power Supply Input Undervoltage Lockout,          |           |

| AC           | Power Supply Input Off-state Detection Function   | 17        |

|              | C Pin Overvoltage Protection                      |           |

| 8.7. PF      | C Overcurrent Protection, PFC Overload Protection | 18        |

| 8.8. PF      | C Undervoltage Protection                         | 19        |

| 8.9. PF      | C Constant Voltage Control                        | 19        |

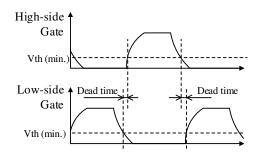

|              | C Dead Time                                       | 20        |

|              | C High-side Driver Undervoltage Lockout           |           |

| 8 13 LL      | C Overcurrent Protection, LLC Overload Protection | 21        |

|              | ermal Shutdown                                    |           |

|              |                                                   |           |

|              | Components                                        |           |

|              | onant Transformer                                 |           |

|              | uctor in PFC Stage                                |           |

|              | ver MOSFET                                        |           |

|              | C Boost Diode (D1, D2)                            |           |

|              | ut Filter                                         |           |

| 9.6. Out     | put Capacitor (C51)                               | <i>11</i> |

| 9.7. Current-resonant Capacitor (C21) | 22 |

|---------------------------------------|----|

| 10. PCB Pattern Layout                | 22 |

| Important Notes                       | 24 |

## 1. Absolute Maximum Ratings

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out of the IC (sourcing) is negative current (–). Unless specifically noted,  $T_A = 25$  °C. Surge withstand capability (HBM) of the MD6752 is guaranteed up to 2000 V. Note that the following pins are guaranteed to withstand surges up to 1000 V: 26, 27, 28.

| Parameter                          | Symbol                 | Pin   | Rating                                            | Unit |

|------------------------------------|------------------------|-------|---------------------------------------------------|------|

| A0 Pin Voltage                     | V <sub>A0</sub>        | 24-8  | -6.0 to 6.0                                       | V    |

| A2 Pin Voltage                     | V <sub>A2</sub>        | 3-8   | -6.0 to 6.0                                       | V    |

| PGND Pin Voltage                   | V <sub>PGND</sub>      | 4-8   | -0.3 to 0.3                                       | V    |

| VGP Pin Voltage                    | V <sub>GP</sub>        | 5-8   | -0.3 to V <sub>CC</sub> + 0.3                     | V    |

| VGP Pin Voltage (tw $\leq$ 50 ns)  | V <sub>GP(PULSE)</sub> | 5-8   | -1.5                                              | V    |

| VCC Pin Voltage                    | Vcc                    | 6–8   | -0.3 to 20                                        | V    |

| BASE Pin Voltage                   | VBASE                  | 7–8   | -0.3 to 6.0                                       | V    |

| AVCC Pin Voltage <sup>(1)(2)</sup> | VAVCC                  | 9–8   | -0.3 to 3.6                                       | V    |

| DVCC Pin Voltage <sup>(2)</sup>    | V <sub>DVCC</sub>      | 10-8  | -0.3 to 3.6                                       | V    |

| VREF Pin Voltage <sup>(3)</sup>    | V <sub>REF</sub>       | 11-8  | -0.3 to V <sub>DVCC</sub> + 0.3 and $-0.3$ to 3.6 | V    |

| CS Pin Voltage <sup>(3)</sup>      | V <sub>CS</sub>        | 12-8  | -0.3 to V <sub>DVCC</sub> + 0.3 and $-0.3$ to 3.6 | V    |

| VSEN Pin Voltage                   | V <sub>SEN</sub>       | 13–8  | -0.3 to V <sub>DVCC</sub> + 0.3 and $-0.3$ to 3.6 | V    |

| FB Pin Voltage                     | V <sub>FB</sub>        | 14–8  | -0.3 to V <sub>DVCC</sub> + 0.3 and $-0.3$ to 3.6 | V    |

| CM Pin Voltage                     | V <sub>CM</sub>        | 15-8  | -0.3 to V <sub>DVCC</sub> + 0.3 and $-0.3$ to 3.6 | V    |

| VCORE Pin Voltage <sup>(4)</sup>   | VCORE                  | 16–8  | $-0.3$ to $2.0^{(5)}$                             | V    |

| GPIO02 Pin Voltage <sup>(6)</sup>  | V <sub>GPIO02</sub>    | 17–8  | -0.3 to 5.5                                       | V    |

| GPIO02 Pin Current <sup>(6)</sup>  | I <sub>GPIO02</sub>    | 17–8  | -4.0 to4.0                                        | mA   |

| GPIO03 Pin Voltage <sup>(6)</sup>  | V <sub>GPIO03</sub>    | 18-8  | -0.3 to 5.5                                       | V    |

| GPIO03 Pin Current <sup>(6)</sup>  | I <sub>GPIO03</sub>    | 18-8  | -4.0 to 4.0                                       | mA   |

| GPIO01 Pin Voltage <sup>(6)</sup>  | V <sub>GPIO01</sub>    | 19–8  | -0.3 to 5.5                                       | V    |

| GPIO01 Pin Current <sup>(6)</sup>  | I <sub>GPIO01</sub>    | 19–8  | -4.0 to 4.0                                       | mA   |

| VOCM Pin Voltage                   | Vocm                   | 20-8  | -0.3 to 5.5                                       | V    |

| VOCM Pin Current                   | Ivocm                  | 20-8  | -4.0 to 4.0                                       | mA   |

| GPIO04 Pin Voltage <sup>(6)</sup>  | V <sub>GPIO04</sub>    | 21-8  | -0.3 to 5.5                                       | V    |

| GPIO04 Pin Current <sup>(6)</sup>  | I <sub>GPIO04</sub>    | 21-8  | -4.0 to 4.0                                       | mA   |

| SCID Pin Voltage                   | VSCID                  | 22-8  | -0.3 to 5.5                                       | V    |

| VGL Pin Voltage                    | V <sub>GL</sub>        | 23-8  | -0.3 to V <sub>CC</sub> + 0.3                     | V    |

| VB–VS Pin Voltage                  | V <sub>BS</sub>        | 26–27 | -0.3 to 20.0                                      | V    |

| VS Pin Voltage                     | Vs                     | 27–8  | -1 to 600                                         | V    |

| VGH Pin Voltage                    | $V_{GH}$               | 28-8  | $V_{\rm S} - 0.3$ to $V_{\rm B} + 0.3$            | V    |

| Operating Ambient Temperature      | Тор                    | —     | -40 to 85                                         | °C   |

| Storage Temperature                | Tstg                   | —     | -40 to 125                                        | °C   |

| Junction Temperature               | TJ                     |       | 125                                               | °C   |

<sup>(1)</sup> The AVCC pin is the 3.3 V power supply output pin dedicated for the internal LSI chip. Do not apply external voltage to this pin.

<sup>&</sup>lt;sup>(2)</sup> Electric potential difference between the AVCC and DVCC pins should be maintained within  $\pm 0.3$  V (t > 1 ms).

<sup>&</sup>lt;sup>(3)</sup> Refers to an analog input pin for 3.3 V systems.

<sup>&</sup>lt;sup>(4)</sup> The VCORE pin is the 1.8 V power supply output pin dedicated for digital circuits of the internal LSI chip. Do not apply external voltage to this pin.

<sup>&</sup>lt;sup>(5)</sup> Should be rated from -0.3 V to 2.4 V when t < 1 ms (e.g., at startup).

<sup>&</sup>lt;sup>(6)</sup> Refers to a digital output pin for 3.3 V systems.

## 2. Electrical Characteristics

Current polarities are defined as follows: current going into the IC (sinking) is positive current (+); current coming out of the IC (sourcing) is negative current (–).

Unless specifically noted,  $T_A = 25$  °C,  $V_{CC} = 17$  V.

The checkmark in the Chg. column indicates that the item is dedicated GUI-changeable. In addition, the characteristic value in this column is a reference value.

| Parameter                                                         | Symbol                 | Conditions                                      | Pin  | Min.  | Тур.  | Max.  | Unit | Chg. |

|-------------------------------------------------------------------|------------------------|-------------------------------------------------|------|-------|-------|-------|------|------|

| Startup Circuit, Circuit Current                                  |                        |                                                 |      |       |       |       |      |      |

| Operation Start Voltage                                           | V <sub>CC(ON)</sub>    |                                                 | 6–8  | 13.0  | 14.0  | 15.0  | V    |      |

| Operation Stop Voltage <sup>(1)</sup>                             | $V_{CC(OFF)}$          |                                                 | 6–8  | 7.4   | 8.3   | 9.2   | V    |      |

| Circuit Current in Operation                                      | ICC(ON)                |                                                 | 6–8  |       | 1.8   | 4.0   | mA   |      |

| Circuit Current in Non-<br>operation                              | Icc(off)               | V <sub>CC</sub> = 11 V                          | 6–8  |       | 0.5   | 1.0   | mA   |      |

| VCC Pin Protection Release<br>Threshold Voltage <sup>(1)</sup>    | $V_{CC(P.OFF)}$        |                                                 | 6–8  | 7.4   | 8.3   | 9.2   | V    |      |

| Circuit Current in Protection<br>Operation                        | $I_{CC(P)}$            | V <sub>CC</sub> = 10 V                          | 6–8  |       | 0.5   | 1.0   | mA   |      |

| VCORE Pin Supply Voltage                                          | V <sub>CORE</sub>      |                                                 | 16–8 | 1.72  | 1.80  | 1.88  | V    |      |

| SCID Pin High Level Detection Voltage <sup>(2)</sup>              | $V_{SCID\_IH}$         |                                                 | 22–8 | 2.0   |       |       | V    |      |

| SCID Pin Low Level Detection<br>Voltage <sup>(2)</sup>            | $V_{SCID\_IL}$         |                                                 | 22–8 |       |       | 0.8   | V    |      |

| 3.3 V Analog Internal Regulator                                   | V <sub>AVCC</sub>      |                                                 | 9–8  | 3.233 | 3.300 | 3.366 | V    |      |

| 3.3 V Digital Internal Regulator                                  | V <sub>DVCC</sub>      |                                                 | 10-8 | 3.135 | 3.300 | 3.465 | V    |      |

| External Transistor Drive<br>Voltage for DVCC Pin                 | VBASE                  | $I_{BASE} = -1 mA$                              | 7–8  | 3.6   |       | 4.4   | V    |      |

| VSEN Pin Input UVP<br>Threshold Voltage                           | V <sub>SEN(OFF)</sub>  |                                                 | 13–8 | 0.43  | 0.47  | 0.51  | V    | 1    |

| VSEN Pin Input UVP Release<br>Voltage                             | $V_{SEN(ON)}$          |                                                 | 13–8 | 0.52  | 0.56  | 0.60  | V    | 1    |

| VSEN Pin AC Input Voltage<br>Off-state Detection Voltage          | $V_{SEN(AC\_OFF)}$     |                                                 | 13–8 | 0.16  | 0.19  | 0.22  | V    | 1    |

| Delay Time of VSEN Pin Input<br>UVP Detection                     | t <sub>VSEN(OFF)</sub> |                                                 | 13–8 | 9.5   | 10.0  | 10.5  | ms   | 1    |

| Delay Time of VSEN Pin AC<br>Input Voltage Off-state<br>Detection | tvsen(ac_off)          |                                                 | 13–8 | 21.8  | 23.0  | 24.2  | ms   | 1    |

| PFC Stage                                                         |                        | -                                               |      |       |       |       |      |      |

| PFC Drive Current (Source)                                        | $I_{GP(SRC)}$          | $V_{CC} = 17 \text{ V},$ $V_{GP} = 0 \text{ V}$ | 5–4  |       | -500  |       | mA   |      |

| PFC Drive Current (Sink)                                          | $I_{GP(SNK)}$          | $V_{CC} = 17 V,$<br>$V_{GP} = 17 V$             | 5–4  | —     | 1     | _     | А    |      |

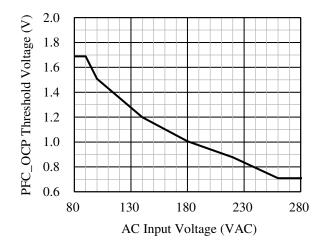

| CS Pin OCP Threshold Voltage<br>(Low)                             | V <sub>CS(LO)</sub>    | $V_{IN} = 90 \text{ VAC}$                       | 12–8 | 1.60  | 1.69  | 1.78  | V    | 1    |

$^{(1)} V_{CC \ (OFF)} = V_{CC \ (P.OFF)}$

<sup>(2)</sup> Guaranteed by design.

## MD6752

| Parameter                                                                                | Symbol                       | Conditions                                                                                                             | Pin          | Min.  | Тур.                       | Max.  | Unit  | Chg.     |

|------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------|-------|----------------------------|-------|-------|----------|

| CS Pin OCP Threshold Voltage<br>(High)                                                   | V <sub>CS(HI)</sub>          | V <sub>IN</sub> = 260 VAC                                                                                              | 12-8         | 0.65  | 0.71                       | 0.77  | v     | <i>v</i> |

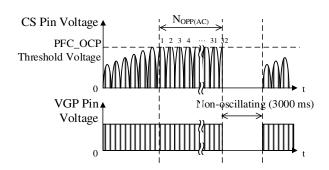

| Number of OVP Operation<br>Times                                                         | N <sub>OPP(AC)</sub>         |                                                                                                                        | 5-8          |       | 32                         |       | Times | 1        |

| VREF Pin Threshold Voltage<br>for PFC Output Control                                     | V <sub>REF</sub>             |                                                                                                                        | 11-8         | 2.009 | 2.096                      | 2.183 | v     | 1        |

| Maximum PFC Oscillation<br>Frequency                                                     | f <sub>MAX_PFC</sub>         |                                                                                                                        | 5–8          | 190   | 200                        | 210   | kHz   | 1        |

| Minimum PFC On-time                                                                      | t <sub>ON(MIN)_PFC</sub>     |                                                                                                                        | 5-8          | 0.28  | 0.30                       | 0.32  | μs    | 1        |

| Minimum PFC Off-time                                                                     | toff(MIN)_PFC                |                                                                                                                        | 5-8          | 0.28  | 0.30                       | 0.32  | μs    | 1        |

| Maximum PFC On-time                                                                      | t <sub>ON(MAX)_PFC</sub>     |                                                                                                                        | 5-8          | 20.8  | 21.9                       | 23.0  | μs    | 1        |

| Maximum PFC Off-time                                                                     | t <sub>OFF(MAX)_PFC</sub>    |                                                                                                                        | 5-8          | 14.2  | 14.9                       | 15.7  | μs    | 1        |

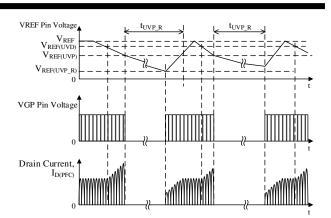

| VREF Pin PFC_UVP Start<br>Voltage                                                        | V <sub>REF(UVD)</sub>        |                                                                                                                        | 11-8         |       | V <sub>REF</sub> -<br>0.08 |       | v     |          |

| VERF Pin PFC_UVP<br>Oscillation Stop Voltage                                             | V <sub>REF(UVP)</sub>        |                                                                                                                        | 11-8         | 1.05  | 1.10                       | 1.15  | v     | 1        |

| VREF Pin PFC_UVP Release<br>Voltage                                                      | V <sub>REF(UVP_R)</sub>      |                                                                                                                        | 11-8         | 0.51  | 0.55                       | 0.59  | V     | 1        |

| PFC_UVP Recovery Delay<br>Time                                                           | t <sub>(UVP_R)</sub>         |                                                                                                                        | _            | 778   | 819                        | 860   | ms    | 1        |

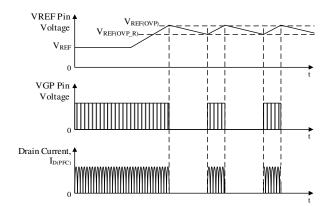

| VREF Pin PFC_OVP Start<br>Voltage                                                        | V <sub>REF(OVD)</sub>        |                                                                                                                        | 11-8         |       | V <sub>REF</sub> +<br>0.08 |       | v     |          |

| VREF Pin PFC_OVP<br>Oscillation Stop Voltage                                             | V <sub>REF(OVP)</sub>        |                                                                                                                        | 11-8         | 2.14  | 2.23                       | 2.33  | v     | 1        |

| VREF Pin PFC_OVP<br>Oscillation Stop Release<br>Voltage                                  | V <sub>REF(OVP_R)</sub>      |                                                                                                                        | 11-8         | 2.09  | 2.18                       | 2.27  | V     | 1        |

| LLC Stage                                                                                |                              |                                                                                                                        |              |       |                            |       |       |          |

| Maximum FB Pin Source<br>Current                                                         | I <sub>FB(MAX)</sub>         | $V_{FB} = 0 V$                                                                                                         | 14–8         | -440  | -330                       | -250  | μΑ    |          |

| High-side Driver Operation<br>Start Voltage                                              | V <sub>BUV(ON)</sub>         |                                                                                                                        | 26–27        | 5.8   | 6.8                        | 7.8   | v     |          |

| High-side Driver Operation<br>Stop Voltage                                               | V <sub>BUV(OFF)</sub>        |                                                                                                                        | 26–27        | 5.4   | 6.4                        | 7.4   | v     |          |

| LLC Drive Current (Source)                                                               | $I_{GL(SRC)} \\ I_{GH(SRC)}$ | $\label{eq:VCC} \begin{array}{l} V_{CC} = 17 \ V, \\ V_B = 17 \ V, \\ V_{GL} = 17 \ V, \\ V_{GH} = 17 \ V \end{array}$ | 23–4<br>28–8 |       | -300                       |       | mA    |          |

| LLC Drive Current (Sink)                                                                 | $I_{GL(SNK)} \\ I_{GH(SNK)}$ | $V_{CC} = 17 V, V_{B} = 17 V, V_{GL} = 0 V, V_{GH} = 0 V$                                                              | 23–4<br>28–8 | _     | 550                        | _     | mA    |          |

| VREF Pin LLC Operation Start<br>Voltage                                                  | $V_{REF(LLC\_ON)}$           |                                                                                                                        | 11-8         | 1.85  | 1.93                       | 2.01  | V     | 1        |

| VREF Pin LLC Operation Stop<br>Voltage                                                   | $V_{REF(LLC\_OFF)}$          |                                                                                                                        | 11-8         | 1.26  | 1.32                       | 1.39  | v     | 1        |

| LLC Maximum Oscillation<br>Frequency during Soft Start<br>Operation                      | $f_{MAX\_LLC(SS)}$           |                                                                                                                        | 23–4<br>28–8 | 385   | 405                        | 426   | kHz   | 1        |

| Current Mode Operation Start<br>LLC Oscillation Frequency<br>during Soft Start Operation | f <sub>LLC(CM)</sub>         |                                                                                                                        | 23–4<br>28–8 | 190   | 200                        | 210   | kHz   | 1        |

| Lowest LLC Oscillation<br>Frequency                                                      | f <sub>MIN_LLC</sub>         |                                                                                                                        | 23–4<br>28–8 | 55.7  | 58.6                       | 61.5  | kHz   | 1        |

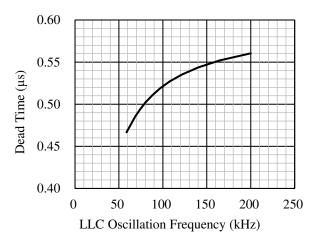

| Highest LLC Oscillation $f_{MAX, JLC}$ $23.4 \\ 28-8$ 190       200       210       kHz $\checkmark$ Minimum LLC Dead Time $t_{4MMN}$ $23.4 \\ 28-8$ 0.44       0.47       0.49 $\mu$ s $\checkmark$ Maximum LLC Dead Time $t_{4MMN}$ $23.4 \\ 28-8$ 0.53       0.56       0.59 $\mu$ s $\checkmark$ Maximum LLC Dead Time $t_{4MMN}$ $23.4 \\ 28-8$ 0.53       0.56       0.59 $\mu$ s $\checkmark$ Current Mode Control       Winimum CM Pin Voltage       VCMUV.MN0       15-8       1.90       2.00       2.10       V $\checkmark$ Maximum CM Pin Voltage       VCMUV.MN0       15-8       2.66       2.78       2.91       V $\checkmark$ OLP Operation Start FB Pin       VGMUV.MN0       15-8       2.66       2.78       2.91       V $\checkmark$ OLP Delay Time 1       toLP1       15-8       2.85       3.00       3.12       V $\checkmark$ OLP Delay Time 2       toLP2       15-8       0.1       0.2       0.3       ms $\checkmark$ OLP Delay Time 1       toLP1       15-8       2850       3000       3150       ms $\checkmark$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                           |                         |                          | 1    |       |       |       | 1    |      |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------|--------------------------|------|-------|-------|-------|------|------|

| Frequency         IAAX_JIC $28-8$ 190 $200$ $210$ $KHZ$ $\checkmark$ Minimum LLC Dead Time $t_{6MIN}$ ) $23-4$ $0.44$ $0.47$ $0.49$ $\mu$ s $\checkmark$ Maximum LLC Dead Time $t_{6MIN}$ ) $23-4$ $0.53$ $0.56$ $0.59$ $\mu$ s $\checkmark$ Minimum CM Pin Voltage         VCMMAN)         15-8 $0.06$ $0.10$ $0.15$ V $\checkmark$ Current Mode Control         VCMMAN)         15-8 $1.90$ $2.00$ $2.10$ V $\checkmark$ Current Mode Control         VCMUV_MIN)         15-8 $2.66$ $2.78$ $2.91$ V $\checkmark$ OLP Operation Start FB Pin         VFBIOLP         14-8 $2.89$ $3.00$ $3.12$ V $\checkmark$ OLP Delay Time 1         tot.r1 $15-8$ $4.7$ $5.0$ $5.3$ ms $\checkmark$ OLP Delay Time 1         tot.r1 $15-8$ $2850$ $3000$ $3150$ ms $\checkmark$ OLP Delay Time 1         tot.r1 $5.2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Parameter                                                                 | Symbol                  | Conditions               | Pin  | Min.  | Тур.  | Max.  | Unit | Chg. |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Highest LLC Oscillation<br>Frequency                                      | $f_{MAX\_LLC}$          |                          |      | 190   | 200   | 210   | kHz  | 1    |

| Maximum LLC Dead Time $L_{(IMAX)}$ $23 \cdot 4 \\ 28 \cdot 8$ $0.53$ $0.56$ $0.59$ $\mu s$ $\checkmark$ Current Mode Control $V_{CM(MIN)}$ $15 - 8$ $0.06$ $0.10$ $0.15$ $\vee$ $\checkmark$ Current Mode Control         Maximum CM Pin Voltage $V_{CM(UV,MIN)}$ $15 - 8$ $1.90$ $2.00$ $2.10$ $\vee$ $\checkmark$ Maximum CM Pin Voltage $V_{CM(UV,MIN)}$ $15 - 8$ $2.66$ $2.78$ $2.91$ $\vee$ $\checkmark$ Maximum CM Pin Voltage $V_{CM(UV,MIN)}$ $14 - 8$ $2.89$ $3.00$ $3.12$ $\vee$ $\checkmark$ OLP Operation Start FB Pin $\nabla_{FB(OLP)}$ $14 - 8$ $2.89$ $3.00$ $3.12$ $\vee$ $\checkmark$ OLP Delay Time 1         toter $15 - 8$ $0.1$ $0.2$ $0.3$ ms $\checkmark$ VCC Pin OVP Threshold $V_{CG(OVP)}$ $6 - 8$ $18.1$ $19.0$ $19.7$ $\vee$ AO Pin OPeration Stop $V_{A0}$ $24 - 8$ $1.18$ $1.25$ $1.32$ $\vee$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Minimum LLC Dead Time                                                     | t <sub>d(MIN)</sub>     |                          |      | 0.44  | 0.47  | 0.49  | μs   | 1    |

| Carrent Mode Control<br>Minimum CM Pin Voltage $V_{CM(MN)}$ 15-8         0.06         0.10         0.15         V $\checkmark$ Minimum CM Pin Voltage<br>Current Mode Control<br>Maximum CM Pin Voltage<br>during LLC Undervoltage<br>OLP Operation Start FB Pin<br>VEMUV_MIN         15-8         1.90         2.00         2.10         V $\checkmark$ OLP Operation Start FB Pin<br>Voltage         V <sub>CMUV_MIN</sub> 15-8         2.66         2.78         2.91         V $\checkmark$ OLP Delay Time 1         toLP 1         15-8         4.7         5.0         5.3         ms $\checkmark$ OLP Delay Time 1         toLP 2         15-8         0.1         0.2         0.3         ms $\checkmark$ OVersoltage Protection (OVP)         VCC:0VP         6-8         18.1         19.0         19.7         V $\checkmark$ VCC Pin OVP Threshold         VC:0VP         6-8         18.1         19.0         19.7         V $\checkmark$ AO Pin Operation Stop<br>Threshold Voltage         V <sub>A0</sub> 24-8         1.18         1.25         1.32         V $\checkmark$ AO Pin Offset Voltage <sup>(4)</sup> V <sub>A0</sub> V         24-8         -         1.06         -         N         C                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Maximum LLC Dead Time                                                     | $t_{d(MAX)}$            |                          | 23–4 | 0.53  | 0.56  | 0.59  | μs   | 1    |

| Current Mode Control<br>Maximum CM Pin Voltage $V_{CM(MAX)}$ 15-8         1.90         2.00         2.10         V $\checkmark$ Maximum CM Pin Voltage<br>during LLC Undervoltage $V_{CM(UV,MIN)}$ 15-8         2.66         2.78         2.91         V $\checkmark$ OLP Operation Start FB Pin<br>Voltage $V_{FR(OLP)}$ 14-8         2.89         3.00         3.12         V $\checkmark$ OLP Delay Time 1         toLP1         15-8         4.7         5.0         5.3         ms $\checkmark$ OLP Delay Time 2         toLP2         15-8         0.1         0.2         0.3         ms $\checkmark$ Protection Recovery Time         tAR         15-8         2850         3000         3150         ms $\checkmark$ Protection Recovery Time         tAR         15-8         18.1         19.0         19.7         V         External Shutdown           AO Pin Operation Stop<br>Threshold Voltage         VA0         24-8         1.18         1.25         1.32         V $\checkmark$ AO Pin Offset Voltage <sup>(3)</sup> VA00         24-8         -         1000         -         ms $\checkmark$ AO Pin Offset Voltage <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Current Mode Control<br>Minimum CM Pin Voltage                            | V <sub>CM(MIN)</sub>    |                          |      | 0.06  | 0.10  | 0.15  | v    | 1    |

| Current Mode Control<br>Maximum CM Pin Voltage $V_{CMUV,MIN}$ 15-8         2.66         2.78         2.91         V $\checkmark$ Maximum CM Pin Voltage $V_{EMOLP}$ 14-8         2.89         3.00         3.12         V $\checkmark$ OLP Operation Start FB Pin<br>Voltage $V_{EMOLP}$ 15-8         4.7         5.0         5.3         ms $\checkmark$ OLP Delay Time 1 $to(LP)$ 15-8         0.1         0.2         0.3         ms $\checkmark$ OLP Delay Time 2 $to(LP)$ 15-8         0.1         0.2         0.3         ms $\checkmark$ Protection Recovery Time $t_{AR}$ 15-8         2850         300         3150         ms $\checkmark$ OVEr Oldage Protection (OVP)         24-8         1.18         1.25         1.32         V $\checkmark$ AO Pin Operation Stop $V_{A0}$ 24-8         -         1.65         -         V $\vee$ AO Pin Offset Voltage <sup>(3)</sup> $V_{A0} = 0$ 3-8         -         0.66         -         V $\vee$ Digital Pull-up Resistor $V_{A0} = 0$ 3-8         -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Current Mode Control                                                      | V <sub>CM(MAX)</sub>    |                          | 15-8 | 1.90  | 2.00  | 2.10  | v    | 1    |

| Voltage         VFB(OLP)         14-8         2.89         3.00         3.12         V         V           OLP Delay Time 1         toLP1         15-8         4.7         5.0         5.3         ms         ✓           OLP Delay Time 2         toLP2         15-8         0.1         0.2         0.3         ms         ✓           Protection Recovery Time         toLP2         15-8         0.1         0.2         0.3         ms         ✓           Overvoltage Protection (OVP)         V         5-8         2850         3000         3150         ms         ✓           VCC Pin OVP Threshold Voccovp         6-8         18.1         19.0         19.7         V         ✓           A0 Pin Operation Stop Threshold Voltage         VA0         24-8         1.18         1.25         1.32         V         ✓           A0 Pin Offset Voltage <sup>(5)</sup> VA0         24-8         -         1000         -         ms         ✓           A0 Pin Offset Voltage <sup>(6)</sup> VA0(OFS)         VA0 = 0 V         24-8         -         1.65         -         V           Digital General-purpose I/O         5.0         V         -         -         0.6         -         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Current Mode Control<br>Maximum CM Pin Voltage<br>during LLC Undervoltage | V <sub>CM(UV_MIN)</sub> |                          | 15-8 | 2.66  | 2.78  | 2.91  | V    | 1    |

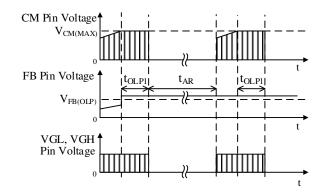

| OLP Delay Time 1 $t_{OLP1}$ 15-8         4.7         5.0         5.3         ms $\checkmark$ OLP Delay Time 2 $t_{OLP2}$ 15-8         0.1         0.2         0.3         ms $\checkmark$ Protection Recovery Time $t_{AR}$ 15-8         2850         3000         3150         ms $\checkmark$ Overvoltage Protection (OVP) $L_{AR}$ 6-8         18.1         19.0         19.7 $\vee$ $\checkmark$ AD Pin Operation Stop $V_{A0}$ 24-8         1.18         1.25         1.32 $\vee$ $\checkmark$ AO Pin Operation Stop $V_{A0}$ 24-8 $$ 1000 $$ ms $\checkmark$ AO Pin Offset Voltage <sup>(3)</sup> $V_{A0(OFS)}$ $V_{a0} = 0$ 24-8 $$ 1.65 $$ $\vee$ Digital General-purpose I/O $Z_{4-8}$ $$ $1.65$ $$ $\vee$ $$ A2 Pin Offset Voltage <sup>(4)</sup> $V_{A2(OFS)}$ $V_{A2} = 0$ $3-8$ $$ $0.6$ $$ $\vee$ $-$ GPIO Pin High Level Detection $V_{H}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | OLP Operation Start FB Pin<br>Voltage                                     | V <sub>FB(OLP)</sub>    |                          | 14-8 | 2.89  | 3.00  | 3.12  | V    | 1    |

| Normal         Image of the second system         Image of the second system <thimage of="" second="" system<="" th="" the="">         Image of the second</thimage> | OLP Delay Time 1                                                          | t <sub>OLP1</sub>       |                          | 15-8 | 4.7   | 5.0   | 5.3   | ms   | 1    |

| Overvoltage Protection (OVP)         V         6-8         18.1         19.0         19.7         V           VCC Pin OVP Threshold<br>Voltage         V <sub>CC(OVP)</sub> 6-8         18.1         19.0         19.7         V           External Shutdown         A0 Pin Operation Stop<br>Threshold Voltage         V <sub>A0</sub> 24-8         1.18         1.25         1.32         V         ✓           A0 Pin Operation Delay Time         t <sub>A0</sub> 24-8         —         1000         —         ms         ✓           A0 Pin Offset Voltage <sup>(3)</sup> V <sub>A0</sub> (OFS)         V <sub>A0</sub> = 0 V         24-8         —         1.65         —         V           Digital General-purpose I/O          A2 Pin Offset Voltage <sup>(4)</sup> V <sub>A2(OFS)</sub> V <sub>A2</sub> = 0 V         3-8         —         0.66         —         V           GPIO Pin High Level Detection<br>Voltage         V <sub>IL</sub> (5)         2.0         —         —         V         GPIO Pin Low Level Detection         VIL         (5)         2.0         60         100         kΩ           Oligital Pull-up Resistor         RPUP         (5)         20         60         100         kΩ         P           Input Leakage Current         IL         V <sub>SEN = 0</sub> V                                                                                                                                                                                                                                                                                                                                                                                | OLP Delay Time 2                                                          | t <sub>OLP2</sub>       |                          | 15-8 | 0.1   | 0.2   | 0.3   | ms   | 1    |

| VCC Pin OVP Threshold<br>Voltage       V <sub>CC(OVP)</sub> 6-8       18.1       19.0       19.7       V         External Shutdown       A0 Pin Operation Stop<br>Threshold Voltage       VA0       24-8       1.18       1.25       1.32       V       ✓         A0 Pin Operation Stop<br>Threshold Voltage       VA0       24-8       -       1000       -       ms       ✓         A0 Pin Protection Delay Time       tA0       24-8       -       1.65       -       V       ✓         Digital General-purpose I/O       VA0(OFS)       VA2 = 0 V       3-8       -       0.6       -       V       ✓         A2 Pin Offset Voltage <sup>(4)</sup> VA2(OFS)       VA2 = 0 V       3-8       -       0.6       -       V       ✓         GPIO Pin High Level Detection<br>Voltage       VII.       (5)       2.0       -       -       V       ✓         Oydtage       VII.       (5)       2.0       60       100       kΩ       ×         Digital Pull-up Resistor       RPUP       (5)       20       60       100       kΩ       ×         Input Leakage Current       IL       VREF = 0 V       13-8       -2       ±1       2       µA       ×         <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Protection Recovery Time                                                  | t <sub>AR</sub>         |                          | 15-8 | 2850  | 3000  | 3150  | ms   | 1    |

| Voltage         VCC(OVP)         6-8         18.1         19.0         19.7         V           External Shutdown         A0 Pin Operation Stop<br>Threshold Voltage         VA0         24-8         1.18         1.25         1.32         V         ✓           A0 Pin Operation Delay Time $t_{A0}$ 24-8          1000          ms         ✓           A0 Pin Offset Voltage <sup>(3)</sup> VA0(OFS)         VA0 = 0 V         24-8          1.65          V           Digital General-purpose I/O         Xa2 = 0 V         3-8          0.6          V           A2 Pin Offset Voltage <sup>(4)</sup> VA2(OFS)         VA2 = 0 V         3-8          0.6          V           GPIO Pin High Level Detection<br>Voltage         V <sub>H</sub> (5)         2.0           V         -           GPIO Pin Low Level Detection<br>Voltage         V <sub>IL</sub> (5)         2.0         60         100         kΩ         -           Ingital Pull-up Resistor         RPUP         15-8         7.9         10.0         12.4         kΩ           Input Leakage Current         IL         VREF = 0 V<br>VSEN = 0 V         13-8         -2<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Overvoltage Protection (OVP)                                              |                         | -                        |      |       |       |       |      |      |

| A0 Pin Operation Stop<br>Threshold Voltage $V_{A0}$ 24-8       1.18       1.25       1.32       V       ✓         A0 Pin Protection Delay Time       tao       24-8       -       1000       -       ms       ✓         A0 Pin Offset Voltage <sup>(3)</sup> $V_{A0(OFS)}$ $V_{A0} = 0$ 24-8       -       1.65       -       V         Digital General-purpose I/O         A2 Pin Offset Voltage <sup>(4)</sup> $V_{A2(OFS)}$ $V_{A2} = 0$ 3-8       -       0.6       -       V         GPIO Pin High Level Detection<br>Voltage $V_{H}$ (5)       2.0       -       -       V         GPIO Pin Low Level Detection<br>Voltage $V_{IL}$ (5)       -       -       0.8       V         Digital Pull-up Resistor $R_{PUP}$ (5)       20       60       100       kΩ         Analog Pull-up Resistor<br>(FB, CM) $R_{PUP2}$ $I_{4-8}^{14-8}$ 7.9       10.0       12.4       kΩ         GPIO Pin High Level Output<br>Voltage $V_{OH4}$ $I_{OH} = -4$ mA       (5)       2.4       -       -       V         GPIO Pin Low Level Output<br>Voltage $V_{OL4}$ $I_{OH} = 4$ mA       (5)       2.4       -       -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VCC Pin OVP Threshold<br>Voltage                                          | V <sub>CC(OVP)</sub>    |                          | 6–8  | 18.1  | 19.0  | 19.7  | V    |      |

| Threshold Voltage       VA0 $24-8$ 1.18       1.23       1.32       V       V         A0 Pin Protection Delay Time       ta0 $24-8$ -       1000       -       ms       ✓         A0 Pin Offset Voltage <sup>(3)</sup> VA0(OFS)       Va0 = 0 V $24-8$ -       1.65       -       V         Digital General-purpose I/O         A2 Pin Offset Voltage <sup>(4)</sup> VA2(OFS)       VA2 = 0 V $3-8$ -       0.6       -       V         GPIO Pin High Level Detection       VIH       (5) $2.0$ -       -       V       GPIO Pin Low Level Detection       VIL       (5) $2.0$ -       -       V       GPIO Pin Low Level Detection       VIL       (5) $2.0$ -       -       V $V$ Digital Pull-up Resistor       RPUP       (5)       20       60       100       k $\Omega$ $A$ Analog Pull-up Resistor       RPUP $11-8$ 7.9       10.0       12.4 $k\Omega$ Input Leakage Current       IL       VREF = 0 V $13-8$ -2 $\pm 1$ 2 $\mu A$ GPIO Pin High Level Output       VOH4       IOH = -4 mA       (5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | External Shutdown                                                         |                         |                          | •    |       |       |       |      |      |

| A0 Pin Protection Delay Time $t_{A0}$ $24-8$ $1000$ ms $\checkmark$ A0 Pin Offset Voltage <sup>(3)</sup> $V_{A0(OFS)}$ $V_{A0} = 0$ V $24-8$ $1.65$ V         Digital General-purpose I/O         A2 Pin Offset Voltage <sup>(4)</sup> $V_{A2(OFS)}$ $V_{A2} = 0$ V $3-8$ $0.6$ V         GPIO Pin High Level Detection VIH $V_{A2(OFS)}$ $V_{A2} = 0$ V $3-8$ $0.6$ V         GPIO Pin High Level Detection VIH $V_{A2} = 0$ V $3-8$ $0.6$ V         Oditage $V_{HH}$ $(5)$ $2.0$ V         GPIO Pin Low Level Detection VIL $V_{IL}$ $(5)$ $2.0$ $60$ $100$ $k\Omega$ Analog Pull-up Resistor $R_{PUP}$ $15-8$ $7.9$ $10.0$ $12.4$ $k\Omega$ $k\Omega$ Input Leakage Current $I_L$ $V_{REF} = 0$ V $11-8$ $-2$ $\pm 11$ $2$ $\mu A$ GPIO Pin High Level Output $V_{OH4}$ $I_{OH} = -4$ mA $(5)$ $2.4$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A0 Pin Operation Stop<br>Threshold Voltage                                | $V_{A0}$                |                          | 24–8 | 1.18  | 1.25  | 1.32  | V    | 1    |

| Digital General-purpose I/O           A2 Pin Offset Voltage <sup>(4)</sup> $V_{A2(OFS)}$ $V_{A2} = 0$ V $3-8$ $0.6$ V           GPIO Pin High Level Detection<br>Voltage $V_{IH}$ (5) $2.0$ V           GPIO Pin Low Level Detection<br>Voltage $V_{IL}$ (5) $$ $$ $V$ Digital Pull-up Resistor $R_{PUP}$ (5) $20$ $60$ $100$ $k\Omega$ Analog Pull-up Resistor $R_{PUP2}$ $14-8$ $7.9$ $10.0$ $12.4$ $k\Omega$ Input Leakage Current         IL $V_{REF} = 0$ V<br>$V_{SEN} = 0$ V $11-8$ $-2$ $\pm 1$ $2$ $\mu A$ GPIO Pin High Level Output<br>Voltage $V_{OH4}$ $I_{OH} = -4$ mA $(5)$ $2.4$ $$ $V$ GPIO Pin Low Level Output<br>Voltage $V_{OL4}$ $I_{OH} = 4$ mA $(5)$ $$ $0.4$ $V$ GPIO Pin Low Level Output<br>Voltage $V_{OL4}$ $I_{OH} = 4$ mA $(5)$ $$ $0.4$ $V$ Clock Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | A0 Pin Protection Delay Time                                              | tA0                     |                          | 24-8 | _     | 1000  |       | ms   | 1    |

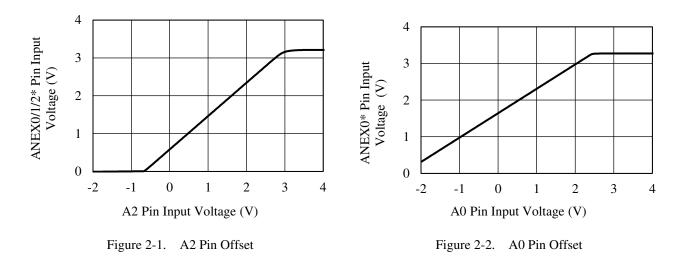

| A2 Pin Offset Voltage <sup>(4)</sup> $V_{A2(OFS)}$ $V_{A2} = 0$ V $3-8$ $0.6$ V           GPIO Pin High Level Detection<br>Voltage $V_{IH}$ (5) $2.0$ V           GPIO Pin Low Level Detection<br>Voltage $V_{IL}$ (5) $2.0$ V           Digital Pull-up Resistor $R_{PUP}$ (5) $20$ $60$ $100$ $k\Omega$ Analog Pull-up Resistor $R_{PUP}$ (5) $20$ $60$ $100$ $k\Omega$ Input Leakage Current $I_L$ $V_{REF} = 0$ V<br>$V_{SEN} = 0$ V $11-8$<br>$13-8$ $-2$ $\pm 1$ $2$ $\mu A$ GPIO Pin High Level Output<br>Voltage $V_{OH4}$ $I_{OH} = -4$ mA $(5)$ $2.4$ V           GPIO Pin Low Level Output<br>Voltage $V_{OL4}$ $I_{OH} = 4$ mA $(5)$ $$ $0.4$ V           GPIO Pin Low Level Output<br>Voltage $V_{OL4}$ $I_{OH} = 4$ mA $(5)$ $$ $$ $0.4$ V           Clock Operation $F_{IRC}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | A0 Pin Offset Voltage <sup>(3)</sup>                                      | V <sub>A0(OFS)</sub>    | $V_{A0} = 0 V$           | 24-8 | _     | 1.65  | _     | V    |      |

| GPIO Pin High Level Detection<br>Voltage         V <sub>IH</sub> (5)         2.0           V           GPIO Pin Low Level Detection<br>Voltage         V <sub>IL</sub> (5)           0.8         V           Digital Pull-up Resistor         R <sub>PUP</sub> (5)         20         60         100         kΩ           Analog Pull-up Resistor<br>(FB, CM)         R <sub>PUP2</sub> $14-8$<br>15-8         7.9         10.0         12.4         kΩ           Input Leakage Current         IL         V <sub>REF</sub> = 0 V<br>V <sub>SEN</sub> = 0 V $11-8$<br>$13-8$ -2         ±1         2 $\mu A$ GPIO Pin High Level Output<br>Voltage         VoH4         IoH = -4 mA         (5)         2.4          -V         V           GPIO Pin Low Level Output<br>Voltage         VoL4         IoH = 4 mA         (5)          0.4         V           GPIO Pin Low Level Output<br>Voltage         ToL4         IoH = 4 mA         (5)          0.4         V           Clock Operation         finc          11.64         12.00         12.18         MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Digital General-purpose I/O                                               |                         |                          |      |       |       |       |      | •    |

| GPIO Pin High Level Detection<br>Voltage $V_{\rm IH}$ (5) $2.0$ $$ $V$ GPIO Pin Low Level Detection<br>Voltage $V_{\rm IL}$ (5) $$ $$ $0.8$ $V$ Digital Pull-up ResistorRPUP(5) $20$ $60$ $100$ $k\Omega$ Analog Pull-up Resistor<br>(FB, CM)RPUP2 $14-8$<br>$15-8$ $7.9$ $10.0$ $12.4$ $k\Omega$ Input Leakage CurrentIL $V_{\rm REF} = 0$ V<br>$V_{\rm SEN} = 0$ V $11-8$<br>$13-8$ $-2$ $\pm 1$ $2$ $\mu A$ GPIO Pin High Level Output<br>VoltageVoH4IoH = $-4$ mA(5) $2.4$ $$ $$ VGPIO Pin Low Level Output<br>VoltageVoL4IoH = $4$ mA(5) $$ $0.4$ VInternal IRC Oscillation<br>Frequencyfirc $$ $11.64$ $12.00$ $12.18$ MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | A2 Pin Offset Voltage <sup>(4)</sup>                                      | V <sub>A2(OFS)</sub>    | $V_{A2} = 0 V$           | 3–8  |       | 0.6   |       | V    |      |

| GPIO Pin Low Level Detection<br>Voltage $V_{IL}$ (5)         0.8       V         Digital Pull-up Resistor       RPUP       (5)       20       60       100       k $\Omega$ Analog Pull-up Resistor<br>(FB, CM)       RPUP2 $14-8$ 7.9       10.0       12.4       k $\Omega$ Input Leakage Current       IL       VREF = 0 V<br>VSEN = 0 V $11-8$ -2 $\pm 1$ 2 $\mu A$ GPIO Pin High Level Output<br>Voltage       VOH4       IOH = -4 mA       (5)       2.4         V         GPIO Pin Low Level Output<br>Voltage       VOL4       IOH = 4 mA       (5)         0.4       V         Internal IRC Oscillation<br>Frequency       fIRC        11.64       12.00       12.18       MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GPIO Pin High Level Detection<br>Voltage                                  |                         |                          | (5)  | 2.0   |       |       | v    |      |

| Digital Pull-up Resistor         RPUP         (5)         20         60         100 $k\Omega$ Analog Pull-up Resistor<br>(FB, CM)         RPUP2 $14-8$ 7.9         10.0         12.4 $k\Omega$ Input Leakage Current         IL $V_{REF} = 0 V$ $11-8$ $-2$ $\pm 1$ 2 $\mu A$ GPIO Pin High Level Output<br>Voltage         VOH4         IOH = $-4 \text{ mA}$ (5) $2.4$ $$ V           GPIO Pin Low Level Output<br>Voltage         VOL4         IOH = $4 \text{ mA}$ (5) $$ $0.4$ V           GPIO Pin Low Level Output<br>Voltage         VOL4         IOH = $4 \text{ mA}$ (5) $$ $0.4$ V           Internal IRC Oscillation<br>Frequency         firc $$ $11.64$ $12.00$ $12.18$ MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | GPIO Pin Low Level Detection                                              | VIL                     |                          | (5)  |       |       | 0.8   | v    |      |

| (FB, CM)       RPUP2       15-8       7.9       10.0       12.4       RS2         Input Leakage Current       IL $V_{REF} = 0 V$ $11-8$ $-2$ $\pm 1$ 2 $\mu A$ GPIO Pin High Level Output $V_{OH4}$ $I_{OH} = -4 \text{ mA}$ (5) $2.4$ $$ $V$ GPIO Pin Low Level Output $V_{OL4}$ $I_{OH} = 4 \text{ mA}$ (5) $$ $0.4$ $V$ GPIO Pin Low Level Output $V_{OL4}$ $I_{OH} = 4 \text{ mA}$ (5) $$ $$ $0.4$ $V$ GORG Operation       Internal IRC Oscillation $f_{IRC}$ $$ $11.64$ $12.00$ $12.18$ MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Digital Pull-up Resistor                                                  | Rpup                    |                          | (5)  | 20    | 60    | 100   | kΩ   |      |

| Input Leakage CurrentIL $V_{REF} = 0 V_{VSEN} = 0 V$ $11-8_{13-8}$ $-2$ $\pm 1$ $2$ $\mu A$ GPIO Pin High Level Output<br>Voltage $V_{OH4}$ $I_{OH} = -4 mA$ $^{(5)}$ $2.4$ $$ $$ $V$ GPIO Pin Low Level Output<br>Voltage $V_{OL4}$ $I_{OH} = 4 mA$ $^{(5)}$ $$ $$ $0.4$ $V$ <b>Clock Operation</b> Internal IRC Oscillation<br>Frequency $f_{IRC}$ $$ $11.64$ $12.00$ $12.18$ MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog Pull-up Resistor<br>(FB, CM)                                       | R <sub>PUP2</sub>       |                          |      | 7.9   | 10.0  | 12.4  | kΩ   |      |

| VoltageVoH4IoH = -4 mA(b) $2.4$ VGPIO Pin Low Level OutputVoL4IoH = 4 mA(b) $2.4$ VVoltageVoL4IoH = 4 mA(b)0.4VClock OperationInternal IRC Oscillationfirc11.6412.0012.18MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Input Leakage Current                                                     | $I_L$                   |                          | 11-8 | -2    | ±1    | 2     | μΑ   |      |

| GPIO Pin Low Level Output<br>Voltage $V_{0L4}$ $I_{OH} = 4 \text{ mA}$ $^{(5)}$ $  0.4$ VClock OperationInternal IRC Oscillation<br>Frequency $f_{IRC}$ $ 11.64$ $12.00$ $12.18$ MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | GPIO Pin High Level Output<br>Voltage                                     | V <sub>OH4</sub>        | $I_{OH} = -4 \text{ mA}$ |      | 2.4   |       |       | V    |      |

| Clock OperationInternal IRC OscillationFrequencyfIRC—11.6412.0012.18MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GPIO Pin Low Level Output<br>Voltage                                      | Vol4                    | $I_{OH} = 4 \text{ mA}$  | (5)  |       |       | 0.4   | V    |      |

| Frequency IIRC — 11.64 12.00 12.18 MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Clock Operation                                                           |                         |                          |      |       |       |       |      |      |