October 1987 Revised April 2002

# CD4049UBC • CD4050BC Hex Inverting Buffer • Hex Non-Inverting Buffer

### **General Description**

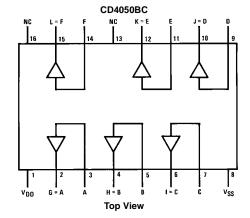

The CD4049UBC and CD4050BC hex buffers are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. These devices feature logic level conversion using only one supply voltage (V $_{\rm DD}$ ). The input signal high level (V $_{\rm IH}$ ) can exceed the V $_{\rm DD}$  supply voltage when these devices are used for logic level conversions. These devices are intended for use as hex buffers, CMOS to DTL/TTL converters, or as CMOS current drivers, and at V $_{\rm DD}=5.0$ V, they can drive directly two DTL/TTL loads over the full operating temperature range.

#### **Features**

- Wide supply voltage range: 3.0V to 15V

- Direct drive to 2 TTL loads at 5.0V over full temperature range

- High source and sink current capability

- $\blacksquare$  Special input protection permits input voltages greater than  $V_{DD}$

#### **Applications**

- · CMOS hex inverter/buffer

- · CMOS to DTL/TTL hex converter

- · CMOS current "sink" or "source" driver

- CMOS HIGH-to-LOW logic level converter

# **Ordering Code:**

| Order Number | Package Number | Package Description                                                          |

|--------------|----------------|------------------------------------------------------------------------------|

| CD4049UBCM   | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| CD4049UBCN   | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |

| CD4050BCM    | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |

| CD4050BCN    | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |

Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code.

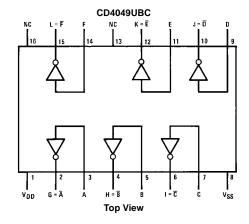

#### **Connection Diagrams**

Pin Assignments for DIP

# **Absolute Maximum Ratings**(Note 1)

(Note 2)

$\begin{tabular}{ll} Supply Voltage (V_{DD}) & -0.5V to +18V \\ Input Voltage (V_{IN}) & -0.5V to +18V \\ Voltage at Any Output Pin (V_{OUT}) & -0.5V to V_{DD} + 0.5V \\ \end{tabular}$

Storage Temperature Range (T<sub>S</sub>)

-65°C to +150°C

Power Dissipation (P<sub>D</sub>)

Dual-In-Line

700 mW

Small Outline

500 mW

Lead Temperature  $(T_L)$

(Soldering, 10 seconds) 260°C

# Recommended Operating Conditions (Note 2)

$\begin{aligned} & \text{Supply Voltage (V}_{\text{DD}}) & 3\text{V to 15V} \\ & \text{Input Voltage (V}_{\text{IN}}) & 0\text{V to 15V} \\ & \text{Voltage at Any Output Pin (V}_{\text{OUT}}) & 0 \text{ to V}_{\text{DD}} \end{aligned}$

Operating Temperature Range (T<sub>A</sub>)

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed; they are not meant to imply that the devices should be operated at these limits. The table of "Recommended Operating Conditions" and "Electrical Characteristics" provides conditions for actual device operation.

Note 2: V<sub>SS</sub> = 0V unless otherwise specified.

#### **DC Electrical Characteristics** (Note 3)

| Symbol          | Parameter                    | Conditions                      | -5    | –55°C |       | +25°C             |      |       | +125°C |       |  |

|-----------------|------------------------------|---------------------------------|-------|-------|-------|-------------------|------|-------|--------|-------|--|

| Syllibol        | Farameter                    | Conditions                      | Min   | Max   | Min   | Тур               | Max  | Min   | Max    | Units |  |

| I <sub>DD</sub> | Quiescent Device Current     | $V_{DD} = 5V$                   |       | 1.0   |       | 0.01              | 1.0  |       | 30     |       |  |

|                 |                              | $V_{DD} = 10V$                  |       | 2.0   |       | 0.01              | 2.0  |       | 60     | μΑ    |  |

|                 |                              | $V_{DD} = 15V$                  |       | 4.0   |       | 0.03              | 4.0  |       | 120    |       |  |

| V <sub>OL</sub> | LOW Level Output Voltage     | $V_{IH} = V_{DD}, V_{IL} = 0V,$ |       |       |       |                   |      |       |        |       |  |

|                 |                              | $ I_O  < 1 \mu A$               |       |       |       |                   |      |       |        |       |  |

|                 |                              | $V_{DD} = 5V$                   |       | 0.05  |       | 0                 | 0.05 |       | 0.05   |       |  |

|                 |                              | $V_{DD} = 10V$                  |       | 0.05  |       | 0                 | 0.05 |       | 0.05   | V     |  |

|                 |                              | $V_{DD} = 15V$                  |       | 0.05  |       | 0                 | 0.05 |       | 0.05   |       |  |

| V <sub>OH</sub> | HIGH Level Output Voltage    | $V_{IH} = V_{DD}, V_{IL} = 0V,$ |       |       |       |                   |      |       |        |       |  |

|                 |                              | $ I_O  < 1 \mu A$               |       |       |       |                   |      |       |        |       |  |

|                 |                              | $V_{DD} = 5V$                   | 4.95  |       | 4.95  | 5                 |      | 4.95  |        |       |  |

|                 |                              | $V_{DD} = 10V$                  | 9.95  |       | 9.95  | 10                |      | 9.95  |        | V     |  |

|                 |                              | $V_{DD} = 15V$                  | 14.95 |       | 14.95 | 15                |      | 14.95 |        |       |  |

| V <sub>IL</sub> | LOW Level Input Voltage      | I <sub>O</sub>   < 1 μA         |       |       |       |                   |      |       |        |       |  |

|                 | (CD4050BC Only)              | $V_{DD} = 5V, V_{O} = 0.5V$     |       | 1.5   |       | 2.25              | 1.5  |       | 1.5    |       |  |

|                 |                              | $V_{DD} = 10V, V_{O} = 1V$      |       | 3.0   |       | 4.5               | 3.0  |       | 3.0    | V     |  |

|                 |                              | $V_{DD} = 15V, V_{O} = 1.5V$    |       | 4.0   |       | 6.75              | 4.0  |       | 4.0    |       |  |

| V <sub>IL</sub> | LOW Level Input Voltage      | $ I_O  < 1 \mu A$               |       |       |       |                   |      |       |        |       |  |

| (               | (CD4049UBC Only)             | $V_{DD} = 5V, V_{O} = 4.5V$     |       | 1.0   |       | 1.5               | 1.0  |       | 1.0    |       |  |

|                 |                              | $V_{DD} = 10V, V_{O} = 9V$      |       | 2.0   |       | 2.5               | 2.0  |       | 2.0    | V     |  |

|                 |                              | $V_{DD} = 15V, V_{O} = 13.5V$   |       | 3.0   |       | 3.5               | 3.0  |       | 3.0    |       |  |

| V <sub>IH</sub> | HIGH Level Input Voltage     | $ I_O  < 1 \mu A$               |       |       |       |                   |      |       |        |       |  |

|                 | (CD4050BC Only)              | $V_{DD} = 5V, V_{O} = 4.5V$     | 3.5   |       | 3.5   | 2.75              |      | 3.5   |        |       |  |

|                 |                              | $V_{DD} = 10V, V_{O} = 9V$      | 7.0   |       | 7.0   | 5.5               |      | 7.0   |        | V     |  |

|                 |                              | $V_{DD} = 15V, V_{O} = 13.5V$   | 11.0  |       | 11.0  | 8.25              |      | 11.0  |        |       |  |

| V <sub>IH</sub> | HIGH Level Input Voltage     | I <sub>O</sub>   < 1 μA         |       |       |       |                   |      |       |        |       |  |

|                 | (CD4049UBC Only)             | $V_{DD} = 5V, V_{O} = 0.5V$     | 4.0   |       | 4.0   | 3.5               |      | 4.0   |        |       |  |

|                 |                              | $V_{DD} = 10V, V_{O} = 1V$      | 8.0   |       | 8.0   | 7.5               |      | 8.0   |        | V     |  |

|                 |                              | $V_{DD} = 15V, V_{O} = 1.5V$    | 12.0  |       | 12.0  | 11.5              |      | 12.0  |        |       |  |

| I <sub>OL</sub> | LOW Level Output Current     | $V_{IH} = V_{DD}, V_{IL} = 0V$  |       |       |       |                   |      |       |        |       |  |

|                 | (Note 4)                     | $V_{DD} = 5V, V_{O} = 0.4V$     | 5.6   |       | 4.6   | 5                 |      | 3.2   |        |       |  |

|                 |                              | $V_{DD} = 10V, V_{O} = 0.5V$    | 12    |       | 9.8   | 12                |      | 6.8   |        | mA    |  |

|                 |                              | $V_{DD} = 15V, V_{O} = 1.5V$    | 35    |       | 29    | 40                |      | 20    |        |       |  |

| Он              | HIGH Level Output Current    | $V_{IH} = V_{DD}, V_{IL} = 0V$  |       |       |       |                   |      |       |        | 1     |  |

|                 | (Note 4)                     | $V_{DD} = 5V, V_{O} = 4.6V$     | -1.3  |       | -1.1  | -1.6              |      | -0.72 |        |       |  |

|                 |                              | $V_{DD} = 10V, V_{O} = 9.5V$    | -2.6  |       | -2.2  | -3.6              |      | -1.5  |        | mA    |  |

|                 |                              | $V_{DD} = 15V, V_{O} = 13.5V$   | -8.0  |       | -7.2  | -12               |      | -5    |        |       |  |

| I <sub>IN</sub> | Input Current                | $V_{DD} = 15V, V_{IN} = 0V$     |       | -0.1  |       | -10 <sup>-5</sup> | -0.1 |       | -1.0   | ^     |  |

|                 | $V_{DD} = 15V, V_{IN} = 15V$ |                                 |       | 0.1   |       | 10 <sup>-5</sup>  | 0.1  |       | 1.0    | μA    |  |

## DC Electrical Characteristics (Continued)

Note 4: These are peak output current capabilities. Continuous output current is rated at 12 mA maximum. The output current should not be allowed to exceed this value for extended periods of time. I<sub>OL</sub> and I<sub>OH</sub> are tested one output at a time.

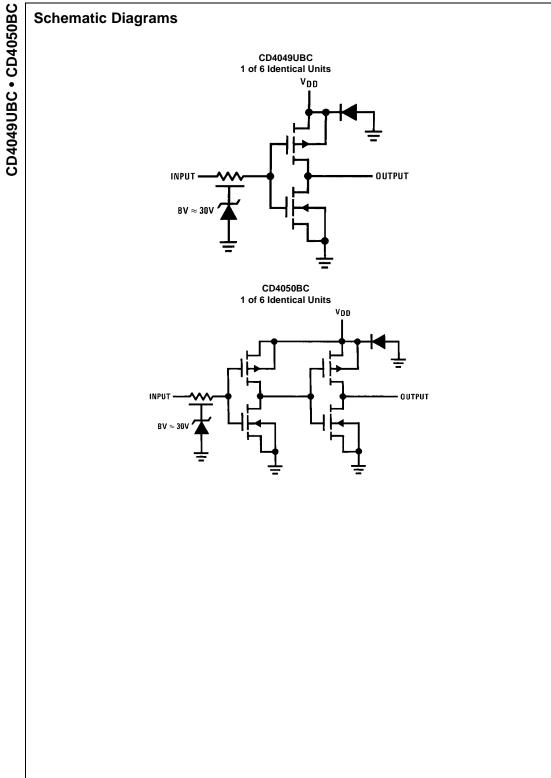

## AC Electrical Characteristics (Note 5)

$T_A = 25$ °C,  $C_L = 50$  pF,  $R_L = 200$ k,  $t_r = t_f = 20$  ns, unless otherwise specified

| Symbol           | Parameter              | Conditions     | Min | Тур | Max  | Units |

|------------------|------------------------|----------------|-----|-----|------|-------|

| t <sub>PHL</sub> | Propagation Delay Time | $V_{DD} = 5V$  |     | 30  | 65   |       |

|                  | HIGH-to-LOW Level      | $V_{DD} = 10V$ |     | 20  | 40   | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 15  | 30   |       |

| t <sub>PLH</sub> | Propagation Delay Time | $V_{DD} = 5V$  |     | 45  | 85   |       |

|                  | LOW-to-HIGH Level      | $V_{DD} = 10V$ |     | 25  | 45   | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 20  | 35   |       |

| t <sub>THL</sub> | Transition Time        | $V_{DD} = 5V$  |     | 30  | 60   |       |

|                  | HIGH-to-LOW Level      | $V_{DD} = 10V$ |     | 20  | 40   | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 15  | 30   |       |

| t <sub>TLH</sub> | Transition Time        | $V_{DD} = 5V$  |     | 60  | 120  |       |

|                  | LOW-to-HIGH Level      | $V_{DD} = 10V$ |     | 30  | 55   | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 25  | 45   |       |

| C <sub>IN</sub>  | Input Capacitance      | Any Input      |     | 15  | 22.5 | pF    |

Note 5: AC Parameters are guaranteed by DC correlated testing.

### AC Electrical Characteristics (Note 6)

CD4050BC  $T_A = 25^{\circ}\text{C}, \ C_L = 50 \ \text{pF}, \ R_L = 200 \text{k}, \ t_r = t_f = 20 \ \text{ns}, \ \text{unless otherwise specified}$

| Symbol           | Parameter              | Conditions     | Min | Тур | Max | Units |

|------------------|------------------------|----------------|-----|-----|-----|-------|

| t <sub>PHL</sub> | Propagation Delay Time | $V_{DD} = 5V$  |     | 60  | 110 |       |

|                  | HIGH-to-LOW Level      | $V_{DD} = 10V$ |     | 25  | 55  | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 20  | 30  |       |

| t <sub>PLH</sub> | Propagation Delay Time | $V_{DD} = 5V$  |     | 60  | 120 |       |

|                  | LOW-to-HIGH Level      | $V_{DD} = 10V$ |     | 30  | 55  | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 25  | 45  |       |

| t <sub>THL</sub> | Transition Time        | $V_{DD} = 5V$  |     | 30  | 60  |       |

|                  | HIGH-to-LOW Level      | $V_{DD} = 10V$ |     | 20  | 40  | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 15  | 30  |       |

| t <sub>TLH</sub> | Transition Time        | $V_{DD} = 5V$  |     | 60  | 120 |       |

|                  | LOW-to-HIGH Level      | $V_{DD} = 10V$ |     | 30  | 55  | ns    |

|                  |                        | $V_{DD} = 15V$ |     | 25  | 45  |       |

| C <sub>IN</sub>  | Input Capacitance      | Any Input      |     | 5   | 7.5 | pF    |

Note 6: AC Parameters are guaranteed by DC correlated testing.

# **Switching Time Waveforms**

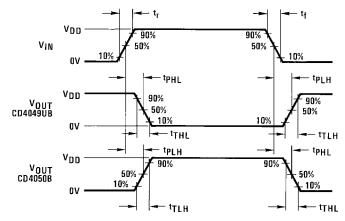

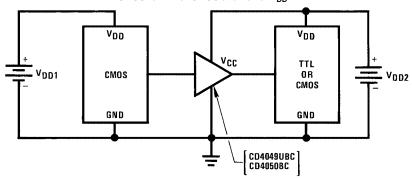

# **Typical Applications**

#### CMOS to TLL or CMOS at a Lower $\ensuremath{\text{V}_{\text{DD}}}$

$V_{DD1} \ge V_{DD2}$

In the case of the CD4049UBC the output drive capability increases with increasing input voltage. E.g., If  $V_{\rm DD1}$  = 10V the CD4049UBC could drive 4 TTL loads.

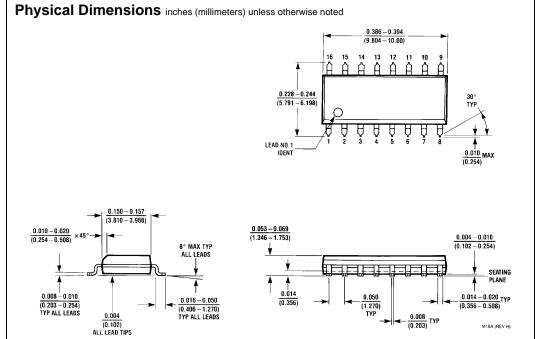

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow Package Number M16A

M16A (REV H)

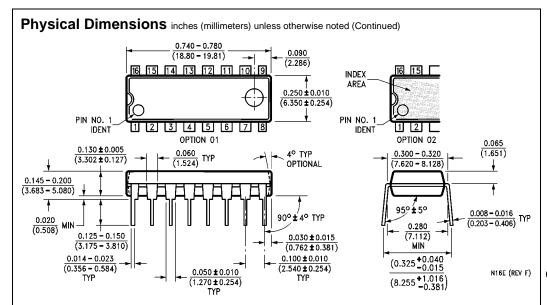

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide Package Number N16E

Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com

Search:

Go

DATASHEETS, SAMPLES, BUY

TECHNICAL INFORMATION APPLICATIONS DESIGN CENTER SUPPORT COMPANY INVESTORS MY F.

Qualification Support

Home >> Find products >>

## CD4049UBC

Hex Inverting Buffer

#### Contents

- General description

- Features

- Product status/pricing/packaging

- Order Samples

#### **General description**

The CD4049UBC and CD4050BC hex buffers are monolithic complementary MOS (CMOS) integrated circuits constructed with N- and P-channel enhancement mode transistors. These devices feature logic level conversion using only one supply voltage ( $V_{\mathrm{DD}}$ ). The input signal high level ( $V_{IH}$ ) can exceed the  $V_{DD}$  supply voltage when these devices are used for logic level conversions. These devices are intended for use as hex buffers, CMOS to DTL/TTL converters, or as CMOS current drivers, and at  $V_{DD}$  = 5.0V, they can drive directly two DTL/TTL loads over the full operating temperature range.

#### back to top

#### **Features**

- Wide supply voltage range: 3.0V to 15V

- Direct drive to 2 TTL loads at 5.0V over full temperature range

- High source and sink current capability

- Special input protection permits input voltages greater than V<sub>DD</sub>

#### back to top

Product status/pricing/packaging

BUY

# BUY

Datasheet Download this datasheet

e-mail this datasheet

This page Print version

#### **Related Links**

Request samples

How to order products

**Product Change Notices** (PCNs)

Support

Sales support

Quality and reliability

Design center

| Product | Product status | Pb-free Status | Pricing* | Package type | Leads | Packing method | Package Marking Convention** |

|---------|----------------|----------------|----------|--------------|-------|----------------|------------------------------|

|         |                |                |          |              |       |                |                              |

| CD4049UBCM   | Full Production | Full<br>Production | \$0.172 | SOIC | 16 | RAIL      | Line 1: \$Y (Fairchild logo) &Z (Asm. Plant Code) &2 (2-Digit Date Code) &T (Die Trace Code) Line 2: CD4049UBCM                                                                   |

|--------------|-----------------|--------------------|---------|------|----|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CD4049UBCMX  | Full Production | Full<br>Production | \$0.172 | SOIC | 16 | TAPE REEL | Line 1: <b>\$Y</b> (Fairchild logo) & <b>Z</b> (Asm. Plant Code) & <b>2</b> (2-Digit Date Code) & <b>T</b> (Die Trace Code) Line 2: CD4049UBCM                                    |

| CD4049UBCN   | Full Production | Full<br>Production | \$0.265 | DIP  | 16 | RAIL      | Line 1: <b>\$Y</b> (Fairchild logo) & <b>Z</b> (Asm. Plant Code) & <b>4</b> (4-Digit Date Code) & <b>T</b> (Die Trace Code) & <b>P</b> (Marketing Status Code) Line 2: CD4049UBCN |

| CD4049UBCSJ  | Full Production | Full<br>Production | \$0.233 | SOP  | 16 | RAIL      | Line 1: <b>\$Y</b> (Fairchild logo) & <b>Z</b> (Asm. Plant Code) & <b>2</b> (2-Digit Date Code) & <b>T</b> (Die Trace Code) Line 2: CD4049UBC                                     |

| CD4049UBCSJX | Full Production | Full<br>Production | \$0.233 | SOP  | 16 | TAPE REEL | Line 1: <b>\$Y</b> (Fairchild logo)<br>& <b>Z</b> (Asm. Plant Code)<br>& <b>2</b> (2-Digit Date Code)<br>& <b>T</b> (Die Trace Code)<br>Line 2: CD4049UBC                         |

<sup>\*</sup> Fairchild 1,000 piece Budgetary Pricing

\*\* A sample button will appear if the part is available through Fairchild's on-line samples program. If there is no sample button, please contact a Fairchild distributor to obtain samples

Indicates product with Pb-free second-level interconnect. For more information click here.

Package marking information for product CD4049UBC is available. Click here for more information.

#### back to top

### **Qualification Support**

Click on a product for detailed qualification data

| Product     |

|-------------|

| CD4049UBCM  |

| CD4049UBCMX |

| CD4049UBCN  |

|             |

# back to top

### © 2007 Fairchild Semiconductor

Products | Design Center | Support | Company News | Investors | My Fairchild | Contact Us | Site Index | Privacy Policy | Site Terms & Conditions | Standard Terms & Conditions |