🖉 Order

Now

**TUSB1064** SLLSF48C - MARCH 2018 - REVISED SEPTEMBER 2019

# TUSB1064 USB TYPE-C<sup>™</sup> DP Alt Mode 10 Gbps Sink-Side Linear Redriver Crosspoint Switch

#### 1 Features

- USB Type-C<sup>™</sup> crosspoint switch supporting - USB 3.1 Gen 2 + 2 DP 1.4 lanes

- 4 DP 1.4 lanes

- USB 3.1 Gen 2 up to 10 Gbps

- DisplayPort 1.4 up to 8.1 Gbps (HBR3)

- VESA DisplayPort<sup>™</sup> alt mode UFP D redriving crosspoint switch supporting c, d, and e pin assignments

- Ultra-low-power architecture

- Linear redriver with up to 12 dB equalization

- Transparent to DisplayPort link training

- Automatic LFPS de-emphasis control to meet USB 3.1 certification requirements

- Configuration through GPIO or I<sup>2</sup>C

- Hot-plug capable

- Industrial temperature range: -40°C to 85°C (TUSB1064I)

- Commercial temperature range: 0°C to 70°C (TUSB1064)

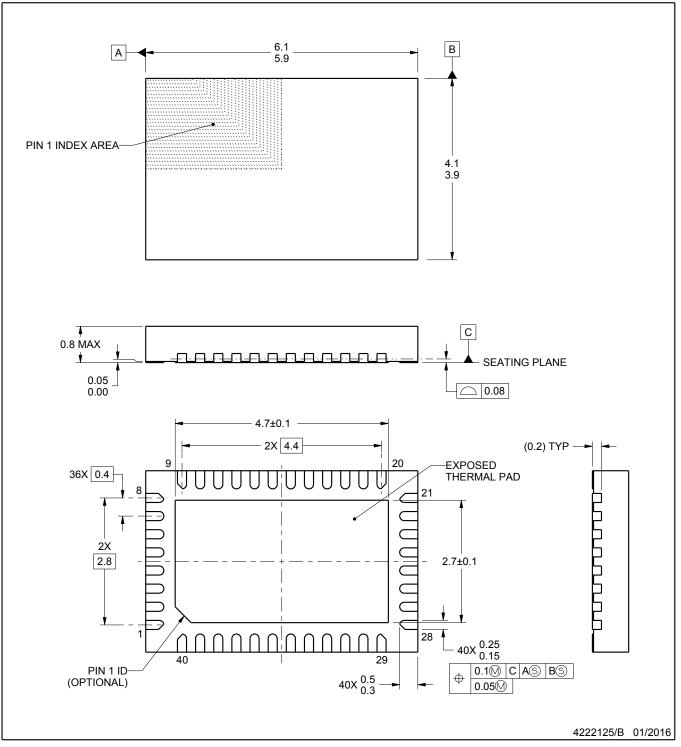

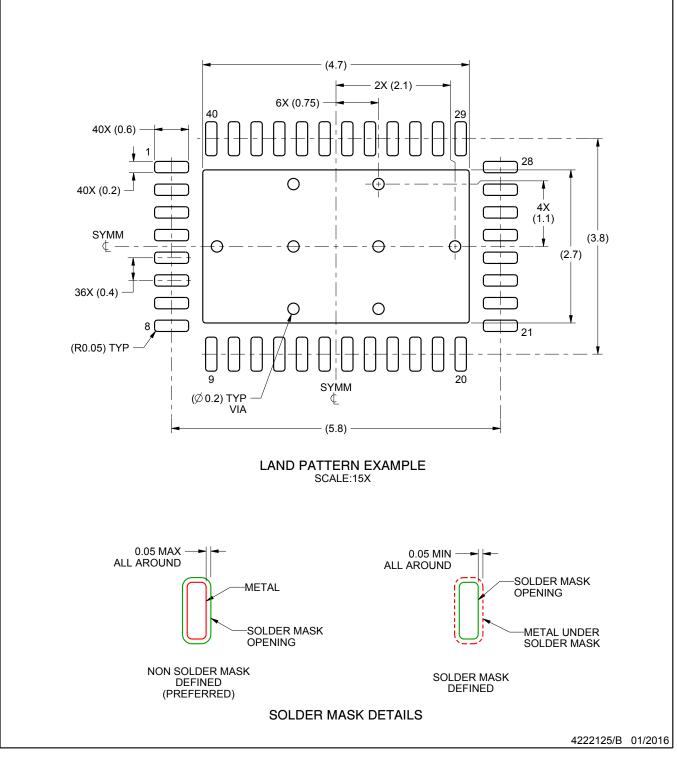

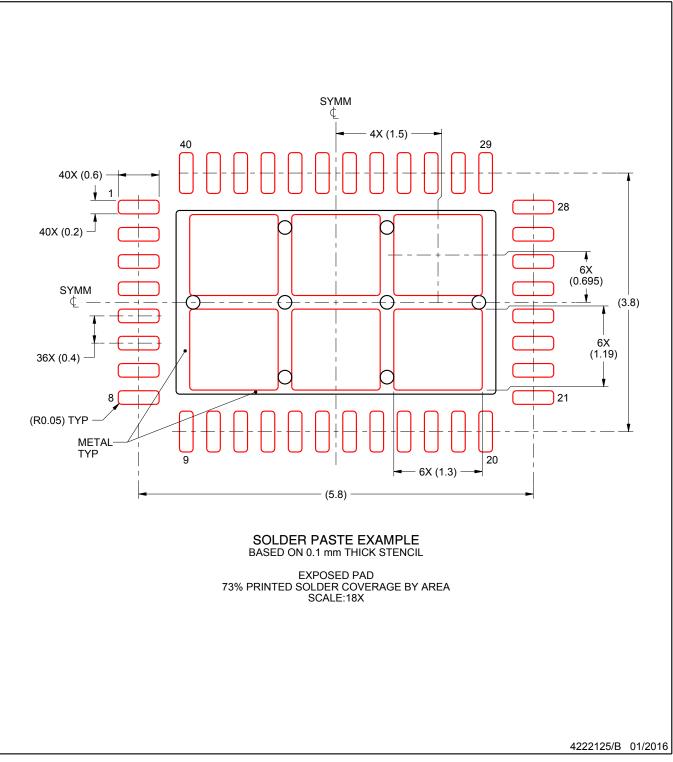

- 4 mm x 6 mm, 0.4 mm Pitch WQFN package

# 2 Applications

- Monitors

- HDTV

- Projectors

- **Docking stations**

# 3 Description

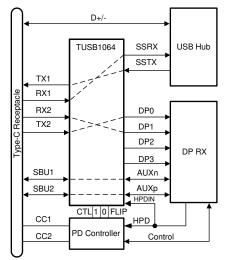

The TUSB1064 s a VESA USB Type-C<sup>™</sup> Alt Mode redriving switch supporting USB 3.1 data rates up to 10 Gbps and DisplayPort 1.4 up to 8.1 Gbps for upstream facing port (Sink). The device is used for UFP D pin assignments C, D, and E from the VESA DisplayPort Alt Mode on USB Type-C Standard.

The TUSB1064 provides several levels of receive linear equalization to compensate for inter symbol interference (ISI) due to cable and board trace loss. Operates on a single 3.3-V supply and comes in a commercial temperature range and industrial temperature range.

# Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |

|-------------|-----------|-------------------|--|

| TUSB1064    |           | 4.00 mm x 6.00 mm |  |

| TUSB1064I   | WQFN (40) |                   |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

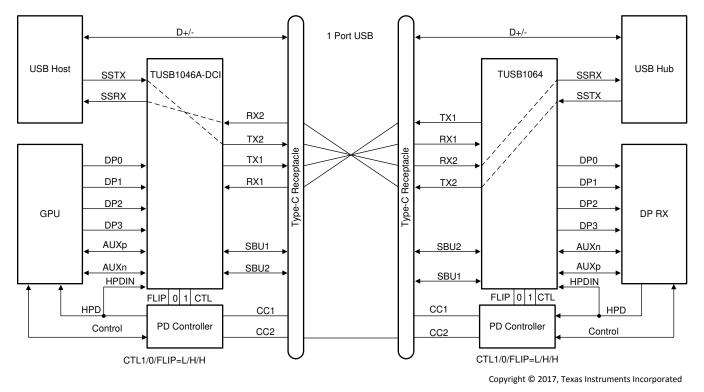

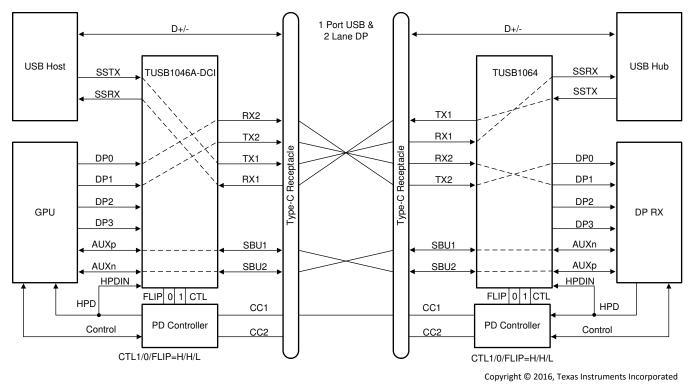

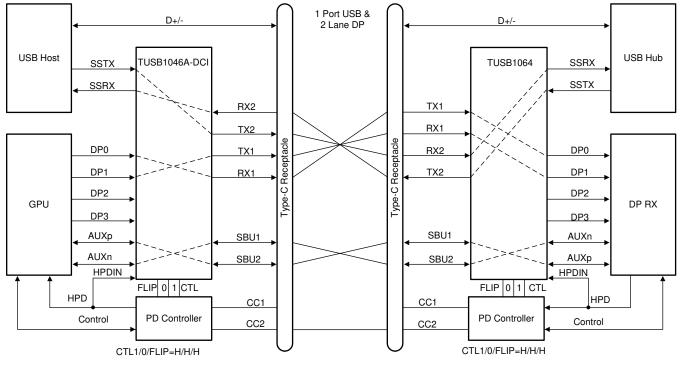

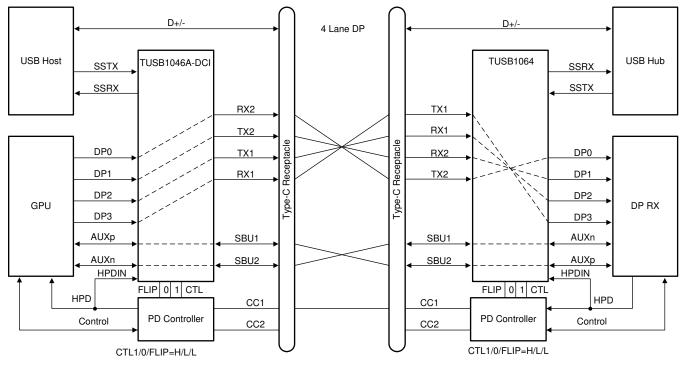

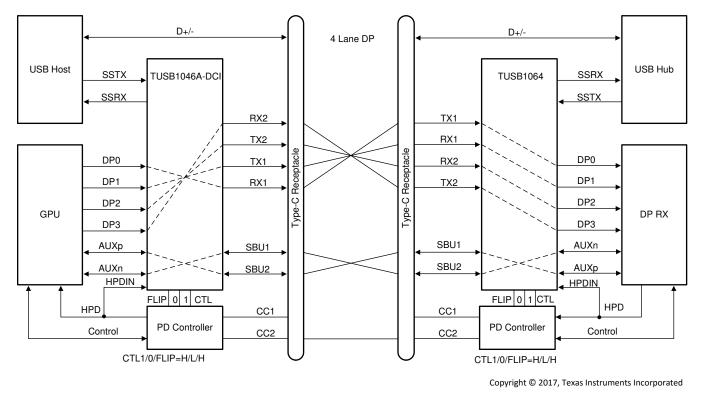

# **TUSB1064 Use-Case Example**

# **Simplified Schematics**

Page

# **Table of Contents**

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions 3      |

| 6 | Spe  | cifications5                       |

|   | 6.1  | Absolute Maximum Ratings 5         |

|   | 6.2  | ESD Ratings5                       |

|   | 6.3  | Recommended Operating Conditions 5 |

|   | 6.4  | Thermal Information 5              |

|   | 6.5  | ELECTRICAL CHARACTERISTICS 6       |

|   | 6.6  | Switching Characteristics 9        |

|   | 6.7  | Timing Requirements 10             |

|   | 6.8  | Typical Characteristics 11         |

| 7 | Para | ameter Measurement Information 13  |

| 8 | Deta | ailed Description 15               |

|   | 8.1  | Overview 15                        |

|   | 8.2  | Functional Block Diagram 16        |

|   | 8.3  | Feature Description 17             |

|    | 8.4  | Device Functional Modes                         | 18 |

|----|------|-------------------------------------------------|----|

|    | 8.5  | Programming                                     | 23 |

|    | 8.6  | Register Maps                                   | 25 |

| 9  | App  | lication and Implementation                     | 30 |

|    | 9.1  | Application Information                         | 30 |

|    | 9.2  | Typical Application                             | 30 |

|    | 9.3  | System Examples                                 | 35 |

| 10 | Pow  | er Supply Recommendations                       | 40 |

| 11 | Lay  | out                                             | 41 |

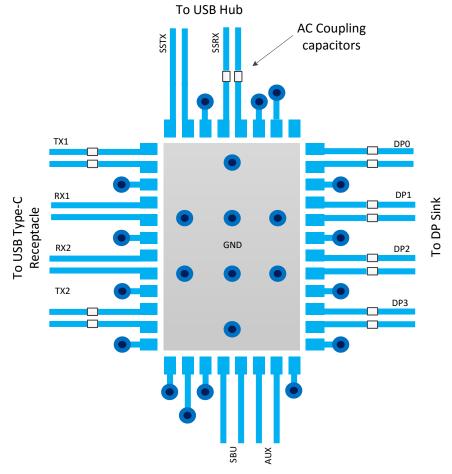

|    | 11.1 |                                                 |    |

|    | 11.2 | Layout Example                                  | 41 |

| 12 | Dev  | ice and Documentation Support                   | 42 |

|    | 12.1 | Receiving Notification of Documentation Updates | 42 |

|    | 12.2 | Community Resources                             | 42 |

|    | 12.3 | Trademarks                                      | 42 |

|    | 12.4 | Electrostatic Discharge Caution                 | 42 |

|    | 12.5 | Glossary                                        | 42 |

| 13 | Mec  | hanical, Packaging, and Orderable               |    |

|    |      | mation                                          | 42 |

|    |      |                                                 |    |

# **4** Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision B (May 2019) to Revision C                             |                  |  |

|------------------------------------------------------------------------------|------------------|--|

| Added note to disable AUX snoop to resolve interop issues with a non-complia | nt AUX source 17 |  |

| Changes from Revision A (November 2018) to Revision B                        | Page             |  |

| • | Added following to pin 38 description: If I2C_EN = "F", then this pin must be set to "F" or "0" |

|---|-------------------------------------------------------------------------------------------------|

| • | Changed G <sub>LF</sub> min, typ, and max from -1, 0, 1 to -2.5, 0.5, and 3.5 respectively      |

| • | Added G <sub>LF_LFPS_TX1/2</sub> to AC electrical                                               |

## Changes from Original (March 2018) to Revision A

| • | Changed the RNQ pin image appearance                                                                          | . 3 |

|---|---------------------------------------------------------------------------------------------------------------|-----|

| • | Changed the column on EN From: I To: 2 Level I (PD)                                                           | . 4 |

| • | Changed the EN pin Description in the Pin Functions table                                                     | . 4 |

|   | Changed the HPDIN pin From: I/O To: 2 Level I                                                                 |     |

| • | Added pull-down indicator (PD) in the I/O column on FLIP/SCL and CTL0/SDA pins                                | . 4 |

| • | Added Junction temperature to absolute maximum ratings table.                                                 | . 5 |

| • | From: Internal pull-down resistance for CTL1. To: Internal pull-down resistance for CTL1, CTL0, FLIP, and EN. | . 6 |

|   | Deleted EN from Note 1 of Table 8                                                                             |     |

| _ |                                                                                                               |     |

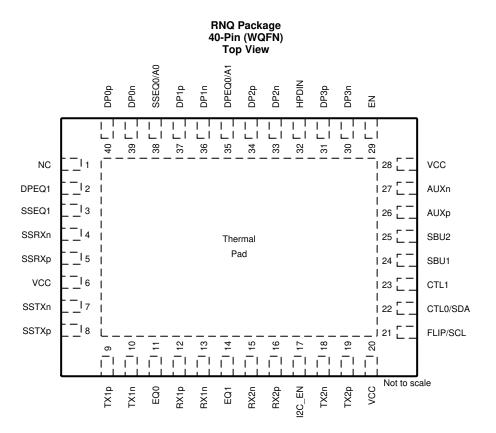

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN   |     | I/O      | DESCRIPTION                                                                                                  |  |  |

|-------|-----|----------|--------------------------------------------------------------------------------------------------------------|--|--|

| NAME  | NO. | 1/0      | DESCRIPTION                                                                                                  |  |  |

| DP0p  | 40  | Diff O   | DP Differential positive output for DisplayPort Lane 0.                                                      |  |  |

| DP0n  | 39  | Diff O   | DP Differential negative output for DisplayPort Lane 0.                                                      |  |  |

| DP1p  | 37  | Diff O   | DP Differential positive output for DisplayPort Lane 1.                                                      |  |  |

| DP1n  | 36  | Diff O   | DP Differential negative output for DisplayPort Lane 1.                                                      |  |  |

| DP2p  | 34  | Diff O   | DP Differential positive output for DisplayPort Lane 2.                                                      |  |  |

| DP2n  | 33  | Diff O   | DP Differential negative output for DisplayPort Lane 2.                                                      |  |  |

| DP3p  | 31  | Diff O   | DP Differential positive output for DisplayPort Lane 3.                                                      |  |  |

| DP3n  | 30  | Diff O   | DP Differential negative output for DisplayPort Lane 3.                                                      |  |  |

| TX1n  | 10  | Diff I/O | Differential negative input for DisplayPort or differential negative output for USB3.1 upstream facing port. |  |  |

| TX1p  | 9   | Diff I/O | Differential positive input for DisplayPort or differential positive output for USB3.1 upstream facing port. |  |  |

| RX1n  | 13  | Diff I   | Differential negative input for DisplayPort or USB3.1 upstream facing port.                                  |  |  |

| RX1p  | 12  | Diff I   | Differential positive input for DisplayPort or USB 3.1 upstream facing port.                                 |  |  |

| RX2p  | 16  | Diff I   | Differential positive input for DisplayPort or USB 3.1 upstream facing port.                                 |  |  |

| RX2n  | 15  | Diff I   | Differential negative input for DisplayPort or USB 3.1 upstream facing port.                                 |  |  |

| TX2p  | 19  | Diff I/O | Differential positive input for DisplayPort or differential positive output for USB3.1 upstream Facing port. |  |  |

| TX2n  | 18  | Diff I/O | Differential negative input for DisplayPort or differential negative output for USB3.1 upstream Facing port. |  |  |

| SSTXp | 8   | Diff I   | Differential positive input for USB3.1 downstream facing port.                                               |  |  |

| SSTXn | 7   | Diff I   | Differential negative input for USB3.1 downstream facing port.                                               |  |  |

| SSRXp | 5   | Diff O   | Differential positive output for USB3.1 downstream facing port.                                              |  |  |

TUSB1064 SLLSF48C – MARCH 2018 – REVISED SEPTEMBER 2019

www.ti.com

NSTRUMENTS

Texas

# Pin Functions (continued)

| PIN      |             |                                 |                                                                                                                                                                                                                                                                                                                                       |  |

|----------|-------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME     | NO.         | I/O                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                           |  |

| SSRXn    | 4           | Diff O                          | Differential negative output for USB3.1 downstream facing port.                                                                                                                                                                                                                                                                       |  |

| EQ1      | 14          | 4 Level I                       | This pin along with EQ0 sets the USB receiver equalizer gain for upstream facing RX1 and RX2 when USB used. Up to 11dB of EQ available.                                                                                                                                                                                               |  |

| EQ0      | 11          | 4 Level I                       | This pin along with EQ1 sets the USB receiver equalizer gain for upstream facing RX1 and RX2 when USB used. Up to 11 dB of EQ available.                                                                                                                                                                                              |  |

| EN       | 29          | 2 Level I<br>(PD)               | Device Enable, when I2C_EN = '0'. Device disable function not used when I2C_EN $\neq$ '0'.<br>_ = Device Disabled<br>H = Device Enabled<br>On rising edge of EN pin, the device will sample all 4-level inputs including the I2C_EN pin. EN pin<br>will not reset the I <sup>2</sup> C registers.                                     |  |

| HPDIN    | 32          | 2 Level I                       | Hot Plug Detect. This pin is an input for Hot Plug Detect received from DisplayPort sink. When<br>HPDIN is Low for greater than 2ms, all DisplayPort lanes are disabled while the AUX to SBU<br>switch will remain closed.                                                                                                            |  |

| I2C_EN   | 17          | 4 Level I                       | $ \begin{array}{l} I^2 C \mbox{ Programming Mode or GPIO Programming Select. I2C is only disabled when this pin is '0'. \\ 0 = GPIO \mbox{ mode } (I^2 C \mbox{ disabled}) \\ R = TI \mbox{ Test Mode } (I^2 C \mbox{ enabled at 3.3 V}) \\ F = I^2 C \mbox{ enabled at 1.8 V} \\ 1 = I^2 C \mbox{ enabled at 3.3 V}. \end{array} $   |  |

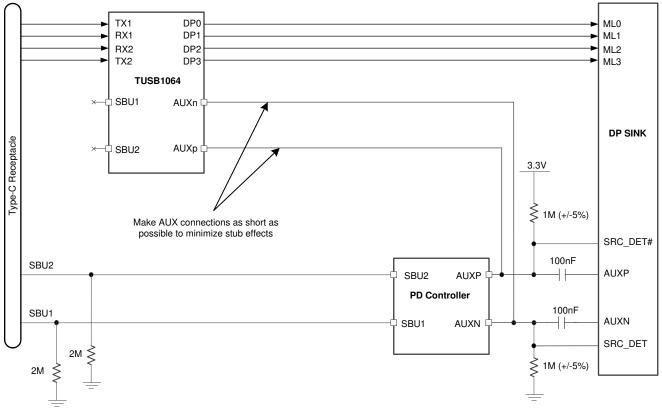

| SBU1     | 24          | I/O, CMOS                       | SBU1. This pin should be DC coupled to the SBU1 pin on the Type-C receptacle. A 2-M ohm resistor to GND is also recommended.                                                                                                                                                                                                          |  |

| SBU2     | 25          | I/O, CMOS                       | SBU2. This pin should be DC coupled to the SBU2 pin on the Type-C receptacle. A 2-M ohm resistor to GND is also recommended.                                                                                                                                                                                                          |  |

| AUXp     | 26          | I/O, CMOS                       | AUXp. DisplayPort AUX positive I/O connected to the DisplayPort sink through a AC coupling capacitor. In addition to AC coupling capacitor, this pin also requires a 1M resistor to DP_PWR (3.3 V). This pin along with AUXN is used by the TUSB1064 for AUX snooping and is routed to SBU1/2 based on the orientation of the Type-C. |  |

| AUXn     | 27          | I/O, CMOS                       | AUXn. DisplayPort AUX negative I/O connected to the DisplayPort sink through a AC coupling capacitor. In addition to AC coupling capacitor, this pin also requires a 1M resistor to GND. This pin along with AUXP is used by the TUSB1064 for AUX snooping and is routed to SBU1/2 based on the orientation of the Type-C.            |  |

| DPEQ1    | 2           | 4 Level I                       | DisplayPort Receiver EQ. This along with DPEQ0 will select the DisplayPort receiver equalization gain.                                                                                                                                                                                                                                |  |

| DPEQ0/A1 | 35          | 4 Level I                       | DisplayPort Receiver EQ. This along with DPEQ1 will select the DisplayPort receiver equalization gain. When I2C_EN $\neq$ '0', this pin will also set the TUSB1064 I <sup>2</sup> C address.                                                                                                                                          |  |

| SSEQ1    | 3           | 4 Level I                       | Along with SSEQ0, sets the USB receiver equalizer gain for downstream facing SSTXP/N.                                                                                                                                                                                                                                                 |  |

| SSEQ0/A0 | 38          | 4 Level I                       | Along with SSEQ1, sets the USB receiver equalizer gain for downstream facing SSTXP/N. When $I2C\_EN \neq '0'$ , this pin will also set the TUSB1064 $I^2C$ address. If $I2C\_EN = "F"$ , then this pin must be set to "F" or "0".                                                                                                     |  |

| FLIP/SCL | 21          | 2 Level I<br>(Failsafe)<br>(PD) | When I2C_EN = '0' this is Flip control pin, otherwise this pin is I <sup>2</sup> C clock When used for I <sup>2</sup> C clock pullup to I <sup>2</sup> C master's VCC I2C supply.                                                                                                                                                     |  |

| CTL0/SDA | 22          | 2 Level I<br>(Failsafe)<br>(PD) | When I2C_EN = '0' this is a USB3.1 Switch control pin, otherwise this pin is $I^2C$ data. When used for $I^2C$ data pullup to $I^2C$ master's VCC I2C supply.                                                                                                                                                                         |  |

| CTL1     | 23          | 2 Level I<br>(Failsafe)<br>(PD) | DP Alt mode Switch Control Pin. When I2C_EN = '0', this pin will enable or disable DisplayPort functionality. Otherwise, when I2C_EN ≠ '0', DisplayPort functionality is enabled and disabled through I <sup>2</sup> C registers.<br>L = DisplayPort Disabled.<br>H = DisplayPort Enabled.                                            |  |

| VCC      | 6, 20, 28   | Р                               | 3.3-V Power Supply                                                                                                                                                                                                                                                                                                                    |  |

| NC       | 1           | NC                              | C No connect pin. Leave open.                                                                                                                                                                                                                                                                                                         |  |

| GND      | Thermal Pad | G                               | Ground                                                                                                                                                                                                                                                                                                                                |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature and voltage range (unless otherwise noted)<sup>(1)</sup>

|                      |                                             | MIN  | MAX  | UNIT |

|----------------------|---------------------------------------------|------|------|------|

| V <sub>CC</sub>      | Supply Voltage Range                        | -0.3 | 4    | V    |

| V <sub>IN_DIFF</sub> | Differential Voltage at Differential Inputs |      | ±2.5 | V    |

| V <sub>IN_SE</sub>   | Input Voltage at Differential Inputs        | -0.5 | 4    | V    |

| V <sub>IN_CMOS</sub> | Input Voltage at CMOS Inputs                | -0.3 | 4    | V    |

| <b>-</b>             | TUSB1064 Junction Temperature               |      | 110  | °C   |

| IJ                   | TUSB1064I Junction Temperature              |      | 125  | °C   |

| T <sub>STG</sub>     | Storage temperature                         | -65  | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                          | VALUE | UNIT |

|--------------------|-------------------------|------------------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | ±5000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | ±1500 | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature and voltage range (unless otherwise noted)

|                      |                                                                | MIN | NOM | MAX | UNIT |

|----------------------|----------------------------------------------------------------|-----|-----|-----|------|

| T <sub>A</sub>       | Ambient temperature for TUSB1064                               | 0   |     | 70  | °C   |

| T <sub>A</sub>       | Ambient temperature for TUSB1064I                              | -40 |     | 85  | °C   |

| V <sub>CC</sub>      | Supply voltage                                                 | 3   | 3.3 | 3.6 | V    |

| V <sub>CC_RAMP</sub> | Power supply ramp                                              | 0.1 |     | 100 | ms   |

| V <sub>I2C</sub>     | Supply that external resistors on SDA and SCL are pulled up to | 1.7 |     | 3.6 | V    |

| V <sub>PSN</sub>     | Power supply noise on VCC                                      |     |     | 100 | mV   |

# 6.4 Thermal Information

|                                              | TUSB1064                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THERMAL METRIC <sup>(1)</sup>                | RNQ (WQFN)                                                                                                                                                                                                                                    | UNIT                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              | 40 PINS                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                          |

| Junction-to-ambient thermal resistance       | 37.6                                                                                                                                                                                                                                          | °C/W                                                                                                                                                                                                                                                                                                                                                                                     |

| Junction-to-case (top) thermal resistance    | 20.7                                                                                                                                                                                                                                          | °C/W                                                                                                                                                                                                                                                                                                                                                                                     |

| Junction-to-board thermal resistance         | 9.5                                                                                                                                                                                                                                           | °C/W                                                                                                                                                                                                                                                                                                                                                                                     |

| Junction-to-top characterization parameter   | 0.2                                                                                                                                                                                                                                           | °C/W                                                                                                                                                                                                                                                                                                                                                                                     |

| Junction-to-board characterization parameter | 9.4                                                                                                                                                                                                                                           | °C/W                                                                                                                                                                                                                                                                                                                                                                                     |

| Junction-to-case (bottom) thermal resistance | 2.3                                                                                                                                                                                                                                           | °C/W                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              | Junction-to-ambient thermal resistance         Junction-to-case (top) thermal resistance         Junction-to-board thermal resistance         Junction-to-top characterization parameter         Junction-to-board characterization parameter | THERMAL METRIC <sup>(1)</sup> RNQ (WQFN)           40 PINS           Junction-to-ambient thermal resistance         37.6           Junction-to-case (top) thermal resistance         20.7           Junction-to-board thermal resistance         9.5           Junction-to-top characterization parameter         0.2           Junction-to-board characterization parameter         9.4 |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

NSTRUMENTS

**Texas**

# 6.5 ELECTRICAL CHARACTERISTICS

over operating free-air temperature and voltage range (unless otherwise noted)

| over operating free-air temperature and voltage range (unless otherwise noted) |                                                                    |                                                                                                  |                           |      |                           |      |

|--------------------------------------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------|------|---------------------------|------|

|                                                                                | PARAMETER                                                          | TEST CONDITIONS                                                                                  | MIN                       | TYP  | MAX                       | UNIT |

| Power                                                                          |                                                                    |                                                                                                  |                           |      |                           |      |

| P <sub>CC-</sub><br>ACTIVE-<br>USB                                             | Average active power in USB-only mode while in U0.                 | CTL1 = L; CTL0 = H; Link in U0 at 10Gbps;                                                        |                           | 330  |                           | mW   |

| P <sub>CC-</sub><br>ACTIVE-<br>USB-DP                                          | Average active power in USB + 2 lane<br>DP mode.                   | CTL1 = H; CTL0 = H; USB in U0 at<br>10Gbps; DP at 8.1Gbps;                                       |                           | 660  |                           | mW   |

| P <sub>CC-</sub><br>ACTIVE-DP                                                  | Average active power in 4 lane DP mode.                            | CTL1 = H; CTL0 = L; Four DP lanes at 8.1Gbps                                                     |                           | 660  |                           | mW   |

| P <sub>CC-NC-</sub><br>USB                                                     | Average power in USB mode while in disconnect state.               | CTL1 = L; CTL0 = H; No USB device detected;                                                      |                           | 2.5  |                           | mW   |

| P <sub>CC-U2U3</sub>                                                           | Average power in USB mode while in U2/U3 state                     | CTL1 = L; CTL0 = H; Link in U2 or U3;                                                            |                           | 2.5  |                           | mW   |

| P <sub>CC-</sub><br>SHUTDOW<br>N                                               | Average power in Shutdown mode.                                    | CTL1 = L; CTL0 = L; I2C_EN = "0";                                                                |                           | 0.7  |                           | mW   |

|                                                                                | MOS Inputs(EQ[1:0], SSEQ[1:0], DPEQ[1                              | :0], I2C_EN)                                                                                     | I                         |      | I                         |      |

| I <sub>IH</sub>                                                                | High-level input current                                           | V <sub>CC</sub> = 3.6 V; V <sub>IN</sub> = 3.6 V                                                 | 20                        |      | 80                        | μA   |

| IIL                                                                            | Low-level input current                                            | V <sub>CC</sub> = 3.6 V; V <sub>IN</sub> = 0 V                                                   | -160                      |      | -40                       | μA   |

|                                                                                | Threshold 0 / R                                                    | V <sub>CC</sub> = 3.3 V                                                                          |                           | 0.55 |                           | V    |

| 4-Level<br>V <sub>TH</sub>                                                     | Threshold R/ Float                                                 | V <sub>CC</sub> = 3.3 V                                                                          |                           | 1.65 |                           | V    |

| ▼ IH                                                                           | Threshold Float / 1                                                | V <sub>CC</sub> = 3.3 V                                                                          |                           | 2.7  |                           | V    |

| R <sub>PU</sub>                                                                | Internal pull up resistance                                        |                                                                                                  |                           | 45   |                           | kΩ   |

| R <sub>PD</sub>                                                                | Internal pull-down resistance                                      |                                                                                                  |                           | 95   |                           | kΩ   |

| 2-State C                                                                      | MOS Input (CTL0, CTL1, FLIP, EN, HPDI                              | N) CTL1, CTL0 and FLIP are Failsafe                                                              |                           |      |                           |      |

| V <sub>IH</sub>                                                                | High-level input voltage                                           |                                                                                                  | 2                         |      | 3.6                       | V    |

| V <sub>IL</sub>                                                                | Low-level input voltage                                            |                                                                                                  | 0                         |      | 0.8                       | V    |

| R <sub>PD</sub>                                                                | Internal pull-down resistance for CTL1, CTL0, FLIP, and EN.        |                                                                                                  |                           | 500  |                           | kΩ   |

| I <sub>IH</sub>                                                                | High-level input current                                           | V <sub>IN</sub> = 3.6 V                                                                          | -25                       |      | 25                        | μA   |

| IIL                                                                            | Low-level input current                                            | V <sub>IN</sub> = GND, V <sub>CC</sub> = 3.6 V                                                   | -25                       |      | 25                        | μA   |

| I2C Contr                                                                      | ol Pins SCL, SDA                                                   |                                                                                                  | +                         |      |                           |      |

| V <sub>IH</sub>                                                                | High-level input voltage                                           | I2C_EN ! = 0                                                                                     | 0.7 x<br>V <sub>I2C</sub> |      | 3.6                       | V    |

| V <sub>IL</sub>                                                                | Low-level input voltage                                            | I2C_EN ! = 0                                                                                     | 0                         |      | 0.3 ×<br>V <sub>I2C</sub> | V    |

| V <sub>OL</sub>                                                                | Low-level output voltage                                           | I2C_EN ! = 0; I <sub>OL</sub> = 3 mA                                                             | 0                         |      | 0.4                       | V    |

| I <sub>OL</sub>                                                                | Low-level output current                                           | I2C_EN ! = 0; V <sub>OL</sub> = 0.4 V                                                            | 20                        |      |                           | mA   |

| I <sub>i_I2C</sub>                                                             | Input current on SDA pin                                           | 0.1 × V <sub>I2C</sub> < Input voltage < 3.3 V                                                   | -10                       |      | 10                        | μA   |

| C <sub>i_l2C</sub>                                                             | Input capacitance                                                  |                                                                                                  |                           |      | 10                        | pF   |

| USB Diffe                                                                      | erential Receiver (RX1P/N, RX2P/N, SSTX                            | (P/N)                                                                                            |                           |      |                           |      |

| V <sub>RX-DIFF-</sub><br>PP                                                    | Input differential peak-peak voltage<br>swing linear dynamic range | AC-coupled differential peak-to-peak<br>signal measured post CTLE through a<br>reference channel |                           | 2000 |                           | mVpp |

| V <sub>RX-DC-</sub><br>CM                                                      | Common-mode voltage bias in the receiver (DC)                      |                                                                                                  |                           | 0    |                           | V    |

| R <sub>RX-DIFF-</sub><br>DC                                                    | Differential input impedance (DC)                                  | Present after a USB3.1 device is detected on TXP/TXN                                             | 72                        |      | 120                       | Ω    |

| R <sub>RX-CM-</sub><br>DC                                                      | Receiver DC Common Mode impedance                                  | Present after a USB3.1 device is detected on TXP/TXN                                             | 18                        |      | 30                        | Ω    |

# **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature and voltage range (unless otherwise noted)

|                                                         | PARAMETER                                                                                     | TEST CONDITIONS                                                                                                | MIN  | ΤΥΡ  | MAX  | UNIT |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| Z <sub>RX-HIGH-</sub><br>IMP-DC-<br>POS                 | Common-mode input impedance with termination disabled (DC)                                    | Present when no USB3.1 device is detected on TXP/TXN. Measured over the range of 0-500 mV with respect to GND. | 25   |      |      | kΩ   |

| V <sub>SIGNAL</sub> -<br>DET-DIFF-<br>PP                | Input Differential peak-to-peak Signal<br>Detect Assert Level                                 | at 10Gbps, No loss and bit rate PRBS7 pattern                                                                  |      | 79   |      | mV   |

| V <sub>RX-IDLE-</sub><br>DET-DIFF-<br>PP                | Input Differential peak-to-peak Signal<br>Detect De-assert Level                              | at 10 Gbps, No loss and bit rate PRBS7 pattern                                                                 |      | 58   |      | mV   |

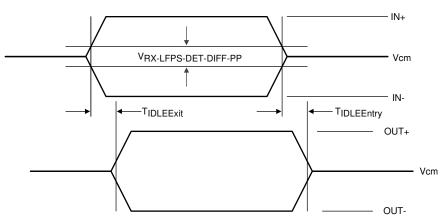

| V <sub>RX-LFPS-</sub><br>DET-DIFF-<br>PP                | Low-frequency Periodic Signaling (LFPS)<br>Detect Threshold                                   | Below the minimum is squelched.                                                                                | 100  |      | 300  | mV   |

| C <sub>RX</sub>                                         | RX input capacitance to GND                                                                   | At 2.5 GHz                                                                                                     |      | 0.5  | 1    | pF   |

| RL <sub>RX-</sub><br>DIFF                               | Differential Return Loss                                                                      | 50 MHz – 1.25 GHz at 90 Ω                                                                                      |      | -13  |      | dB   |

| RL <sub>RX-</sub><br>DIFF                               | Differential Return Loss                                                                      | 5 GHz at 90 $\Omega$                                                                                           |      | -9   |      | dB   |

| RL <sub>RX-CM</sub>                                     | Common Mode Return Loss                                                                       | 50 MHz – 5 GHz at 90 Ω                                                                                         |      | -8   |      | dB   |

| EQ <sub>SSP</sub>                                       | Receiver equalization                                                                         | SSEQ[1:0] and EQ[1:0] at 5 GHz.                                                                                |      | 12   |      | dB   |

|                                                         | rential Transmitter (TX1P/N, TX2P/N, SS                                                       | RXP/N)                                                                                                         |      |      |      |      |

| V <sub>TX-DIFF-</sub><br>PP                             | Transmitter dynamic differential voltage swing range.                                         |                                                                                                                |      | 1300 |      | mVpp |

| V <sub>TX-RCV-</sub><br>DETECT                          | Amount of voltage change allowed<br>during Receiver Detection                                 | at 3.3 V                                                                                                       |      |      | 600  | mV   |

| V <sub>TX-CM-</sub><br>IDLE-<br>DELTA                   | Transmitter idle common-mode voltage change while in U2/U3 and not actively transmitting LFPS | measured at the connector side of the AC coupling caps with 50 $\Omega$ load                                   | -600 |      | 600  | mV   |

| V <sub>TX-DC-</sub><br>CM                               | Common-mode voltage bias in the transmitter (DC)                                              |                                                                                                                | 0    |      | 2    | V    |

| V <sub>TX-CM-</sub><br>AC-PP-<br>ACTIVE                 | Tx AC Common-mode voltage active                                                              | At 3.3V; Max mismatch from Txp+Txn for both time and amplitude                                                 |      |      | 100  | mVpp |

| V <sub>TX-IDLE-</sub><br>DIFF-AC-<br>PP                 | AC Electrical idle differential peak-to-<br>peak output voltage                               | At package pins                                                                                                | 0    |      | 10   | mV   |

| V <sub>TX-IDLE-</sub><br>DIFF-DC                        | DC Electrical idle differential output voltage                                                | At package pins after low-pass filter to remove AC component                                                   | 0    |      | 14   | mV   |

| V <sub>TX-CM-</sub><br>DC-<br>ACTIVE-<br>IDLE-<br>DELTA | Absolute DC common mode voltage between U1 and U0                                             | At package pin                                                                                                 |      |      | 200  | mV   |

| C <sub>TX</sub>                                         | TX input capacitance to GND                                                                   | At 2.5 GHz                                                                                                     |      |      | 1.25 | pF   |

| R <sub>TX-DIFF</sub>                                    | Differential impedance of the driver                                                          |                                                                                                                | 75   |      | 120  | Ω    |

| C <sub>AC-</sub><br>COUPLING                            | AC Coupling capacitor                                                                         |                                                                                                                | 75   |      | 265  | nF   |

| R <sub>TX-CM</sub>                                      | Common-mode impedance of the driver                                                           | Measured with respect to AC ground over 0-500 mV                                                               | 18   |      | 30   | Ω    |

| I <sub>TX-SHORT</sub>                                   | TX short circuit current                                                                      | TX+/- shorted to GND                                                                                           |      |      | 67   | mA   |

| RL <sub>TX-DIFF</sub>                                   | Differential Return Loss                                                                      | 50 MHz – 1.25 GHz at 90 $\Omega$                                                                               |      | -17  |      | dB   |

| RL <sub>TX-</sub><br>DIFF-5G                            | Differential Return Loss                                                                      | 5 GHz at 90 $\Omega$                                                                                           |      | -12  |      | dB   |

| RL <sub>TX-CM</sub>                                     | Common Mode Return Loss                                                                       | 50 MHz – 5 GHz at 90 Ω                                                                                         |      | -9   |      | dB   |

| AC Electr                                               | ical Characteristics for USB and DP                                                           |                                                                                                                |      |      |      |      |

Copyright © 2018–2019, Texas Instruments Incorporated

NSTRUMENTS

Texas

# ELECTRICAL CHARACTERISTICS (continued)

| over operating | free-air | temperature | and | voltage range | (unless | otherwise | noted) |

|----------------|----------|-------------|-----|---------------|---------|-----------|--------|

|                |          |             |     |               | (       |           | ,      |

|                                | PARAMETER                                                                         | TEST CONDITIONS                                                                            | MIN  | ТҮР  | MAX | UNIT |

|--------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|------|-----|------|

| Crosstalk                      | Differential Cross Talk between TX and RX signal Pairs                            | at 5 GHz                                                                                   |      | -27  |     | dB   |

| G <sub>LF</sub>                | Low-frequency voltage gain.                                                       | at 100 MHz, 600 mVpp V <sub>ID</sub>                                                       | -2.5 | 0.5  | 3.5 | dB   |

| G <sub>LF_LFPS</sub><br>_TX1/2 | Low-frequency voltage gain for SSTX-<br>>TX1/TX2 path.                            | at 10 to 50MHz sine wave; 1.0Vpp $V_{\text{ID}};$ EQ = 0; FLIP = 0 and 1;                  | 0    | 0.8  | 1.6 | dB   |

| CP <sub>1 dB-LF</sub>          | Low-frequency 1-dB compression point                                              | at 100 MHz, 200 mVpp < V <sub>ID</sub> < 2000<br>mVpp                                      |      | 1000 |     | mVpp |

| CP <sub>1 dB-</sub><br>HF      | High-frequency 1-dB compression point                                             | at 5 GHz, 200 mVpp < V <sub>ID</sub> < 2000 mVpp                                           |      | 770  |     | mVpp |

| f <sub>LF</sub>                | Low-frequency cutoff                                                              | $200 \text{ mVpp} < \text{V}_{\text{ID}} < 2000 \text{ mVpp}$                              |      | 20   | 50  | kHz  |

| D <sub>J_10G</sub>             | TX output deterministic jitter                                                    | 200 mVpp < V <sub>ID</sub> < 2000 mVpp, PRBS7,<br>10 Gbps                                  |      | 0.10 |     | Ulpp |

| D <sub>J_8.1G</sub>            | TX output deterministic jitter                                                    | 200 mVpp < V <sub>ID</sub> < 2000 mVpp, PRBS7,<br>8.1 Gbps                                 |      | 0.08 |     | Ulpp |

| T <sub>J_10G</sub>             | TX output total jitter                                                            | 200 mVpp < V <sub>ID</sub> < 2000 mVpp, PRBS7,<br>10 Gbps                                  |      | 0.13 |     | Ulpp |

| T <sub>J_8.1G</sub>            | TX output total jitter                                                            | 200 mVpp < V <sub>ID</sub> < 2000 mVpp, PRBS7,<br>8.1 Gbps                                 |      | 0.12 |     | Ulpp |

| DisplayPo                      | ort Receiver (TX1P/N, TX2P/N, RX1P/N, F                                           | X2P/N)                                                                                     |      |      |     |      |

| V <sub>ID_PP</sub>             | Peak-to-peak input differential dynamic voltage range                             |                                                                                            |      | 2000 |     | mV   |

| V <sub>IC</sub>                | Input Common Mode Voltage                                                         |                                                                                            |      | 0    |     | V    |

| C <sub>AC</sub>                | AC coupling capacitance                                                           |                                                                                            | 75   |      | 265 | nF   |

| EQ <sub>DP</sub>               | Receiver Equalizer                                                                | DPEQ1, DPEQ0 at 4.05 GHz                                                                   |      | 12   |     | dB   |

| d <sub>R</sub>                 | Data rate                                                                         | HBR3                                                                                       |      |      | 8.1 | Gbps |

| R <sub>ti</sub>                | Input Termination resistance                                                      |                                                                                            | 80   | 100  | 120 | Ω    |

| DisplayPo                      | ort Transmitter (DP[3:0]P/N)                                                      |                                                                                            |      |      |     |      |

| V <sub>TX-</sub><br>DIFFPP     | VOD dynamic range                                                                 |                                                                                            |      | 1300 |     | mV   |

| I <sub>TX-SHORT</sub>          | TX short circuit current                                                          | TX+/- shorted to GND                                                                       |      |      | 67  | mA   |

| AUXP/N a                       | nd SBU1/2                                                                         |                                                                                            |      |      |     |      |

| R <sub>ON</sub>                | Output ON resistance                                                              | $V_{CC}$ = 3.3 V; $V_{IN}$ = 0 to 0.4 V for AUXP; $V_{IN}$ = 2.7 V to 3.6 V for AUXN       |      | 5    | 10  | Ω    |

| R <sub>ON-</sub><br>MISMATCH   | $\Delta \text{ON}$ resistance mismatch within pair                                | $V_{CC}$ = 3.3 V; $V_{IN}$ = 0 to 0.4 V for AUXP; $V_{IN}$ = 2.7 V to 3.6 V for AUXN       |      |      | 1   | Ω    |

| R <sub>ON_FLAT</sub>           | ON resistance flatness (RONmax–RON min) measured at identical VCC and temperature | $V_{CC}$ = 3.3 V; $V_{IN}$ = 0 to 0.4 V for AUXP; $V_{IN}$ = 2.7 V to 3.6 V for AUXN       |      |      | 2   | Ω    |

| V <sub>AUXP_D</sub><br>C_CM    | AUX Channel DC common mode voltage for AUXP and SBU2.                             | V <sub>CC</sub> = 3.3 V                                                                    | 0    |      | 0.4 | V    |

| V <sub>AUXN_D</sub><br>c_cm    | AUX Channel DC common mode voltage for AUXN and SBU1                              | V <sub>CC</sub> = 3.3 V                                                                    | 2.7  |      | 3.6 | V    |

| C <sub>AUX_ON</sub>            | ON-state capacitance                                                              | $V_{CC} = 3.3 \text{ V}; \text{ CTL1} = 1; \text{ V}_{IN} = 0 \text{ V or } 3.3 \text{ V}$ |      | 4    | 7   | pF   |

| C <sub>AUX_OFF</sub>           | OFF-state capacitance                                                             | $V_{CC} = 3.3 \text{ V}; \text{ CTL1} = 0; \text{ V}_{IN} = 0 \text{ V or } 3.3 \text{ V}$ |      | 3    | 6   | pF   |

| -                              |                                                                                   |                                                                                            |      | -    |     |      |

# 6.6 Switching Characteristics

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                      |                                                                                                                       | TEST CONDITIONS | MIN                                  | TYP | MAX  | UNIT |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------|--------------------------------------|-----|------|------|

| AUXp/n a                       | nd SBU1/2                                                                                                             |                 |                                      |     |      |      |

| T <sub>AUX_PD</sub>            | Switch propagation delay                                                                                              |                 |                                      |     | 1400 | ps   |

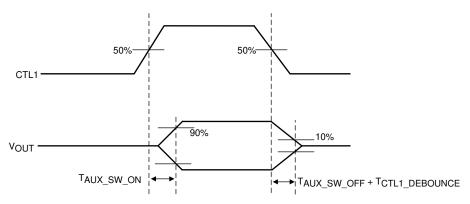

| T <sub>AUX_SW</sub>            | Switching time CTL1 to switch OFF. Not including T <sub>CTL1_DEBOUNCE</sub> .                                         |                 |                                      |     | 7500 | ns   |

| T <sub>AUX_SW</sub><br>_ON     | Switching time CTL1 to switch ON                                                                                      |                 |                                      |     | 3000 | ns   |

| T <sub>AUX_INT</sub><br>RA     | Intra-pair output skew                                                                                                |                 |                                      |     | 400  | ps   |

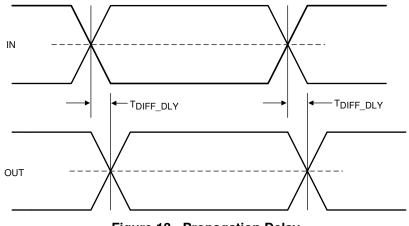

| USB3.1 a                       | nd DisplayPort mode transition requirement                                                                            | t (GPIO mode)   |                                      |     |      |      |

| T <sub>GP_USB_</sub><br>4DP    | Min overlap of CTL0 and CTL1 when<br>transitioning from USB 3.1 only mode to<br>4-Lane DisplayPort mode or vice versa |                 | 4                                    |     |      | μs   |

| T <sub>CTL1_DE</sub><br>BOUNCE | CTL1 and HPDIN debounce time when transitioning from H to L                                                           |                 | 3                                    |     | 10   | ms   |

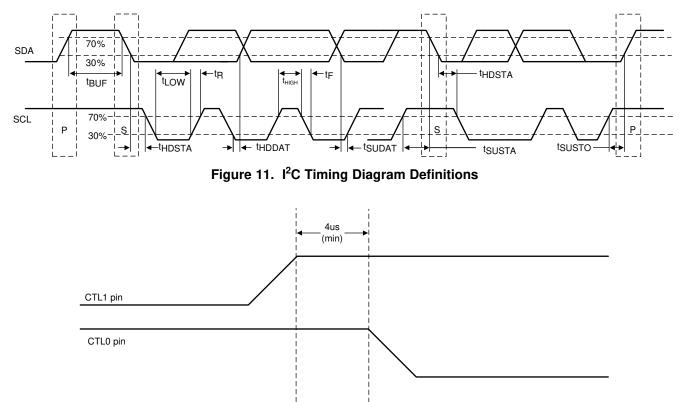

| I2C (SDA                       | and SCL)                                                                                                              |                 |                                      |     |      |      |

| f <sub>SCL</sub>               | I2C clock frequency                                                                                                   |                 |                                      |     | 1    | MHz  |

| t <sub>BUF</sub>               | Bus free time between START and STOP conditions                                                                       |                 | 0.5                                  |     |      | μs   |

| t <sub>hdsta</sub>             | Hold time after repeated START<br>condition. After this period, the first clock<br>pulse is generated                 |                 | 0.26                                 |     |      | μs   |

| t <sub>LOW</sub>               | Low period of the I2C clock                                                                                           |                 | 0.5                                  |     |      | μs   |

| t <sub>HIGH</sub>              | High period of the I2C clock                                                                                          |                 | 0.26                                 |     |      | μs   |

| t <sub>susta</sub>             | Setup time for a repeated START condition                                                                             |                 | 0.26                                 |     |      | μs   |

| t <sub>hddat</sub>             | Data hold time                                                                                                        |                 | 0                                    |     |      | μs   |

| t <sub>SUDAT</sub>             | Data setup time                                                                                                       |                 | 50                                   |     |      | ns   |

| t <sub>R</sub>                 | Rise time of both SDA and SCL signals                                                                                 |                 |                                      |     | 120  | ns   |

| t <sub>F</sub>                 | Fall time of both SDA and SCL signals                                                                                 |                 | 20 ×<br>(V <sub>I2C</sub> /5.5<br>V) |     | 120  | ns   |

| t <sub>susto</sub>             | Setup time for STOP condition                                                                                         |                 | 0.26                                 |     |      | μs   |

| C <sub>b</sub>                 | Capacitive load for each bus line                                                                                     |                 |                                      |     | 100  | pF   |

SLLSF48C - MARCH 2018 - REVISED SEPTEMBER 2019

www.ti.com

NSTRUMENTS

Texas

# 6.7 Timing Requirements

|                                 |                                                                                                        | MIN | NOM | MAX | UNIT |

|---------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| USB 3.1                         |                                                                                                        |     |     |     |      |

| t <sub>IDLEEntry</sub> ,        | Delay from U0 to electrical idle                                                                       |     | 10  |     | ns   |

| t <sub>IDLEExit_U1</sub>        | U1 exist time: break in electrical idle to the transmission of LFPS                                    |     | 6   |     | ns   |

| t <sub>IDLEExit_U2</sub><br>U3  | U2/U3 exit time: break in electrical idle to transmission of LFPS                                      |     | 10  |     | μs   |

| t <sub>RXDET_INT</sub><br>VL    | RX detect interval while in Disconnect                                                                 |     |     | 12  | ms   |

| t <sub>IDLEExit_DIS</sub><br>C  | Disconnect Exit Time                                                                                   |     | 10  |     | μs   |

| t <sub>Exit_SHTDN</sub>         | Shutdown Exit Time (CTL0 = V <sub>CC</sub> /2 to U2/U3)                                                |     | 1   |     | ms   |

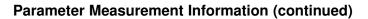

| t <sub>DIFF_DLY</sub>           | Differential Propagation Delay (20%-80% of differential voltage measured 1.7 inch from the output pin) |     |     | 300 | ps   |

| t <sub>PWRUPACTI</sub><br>VE    | Time when Vcc reaches 70% to device active                                                             |     |     | 1   | ms   |

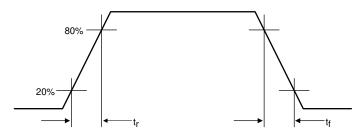

| t <sub>R</sub> , t <sub>F</sub> | Output Rise/Fall Time                                                                                  |     | 40  |     | ps   |

| t <sub>RF-MM</sub>              | Output Rise/Fall time mismatch (20%-80% of differential voltage measured 1.7 inch from the output pin) |     |     | 5   | ps   |

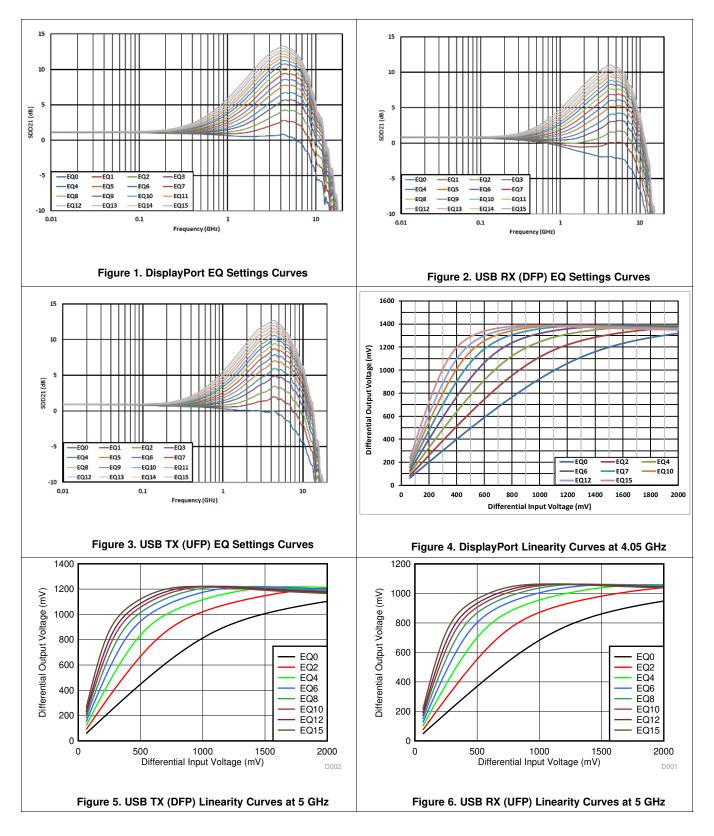

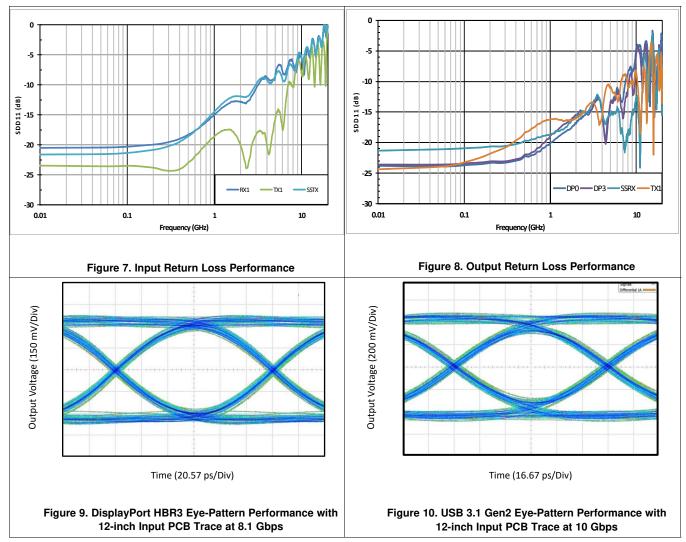

# 6.8 Typical Characteristics

# **Typical Characteristics (continued)**

# 7 Parameter Measurement Information

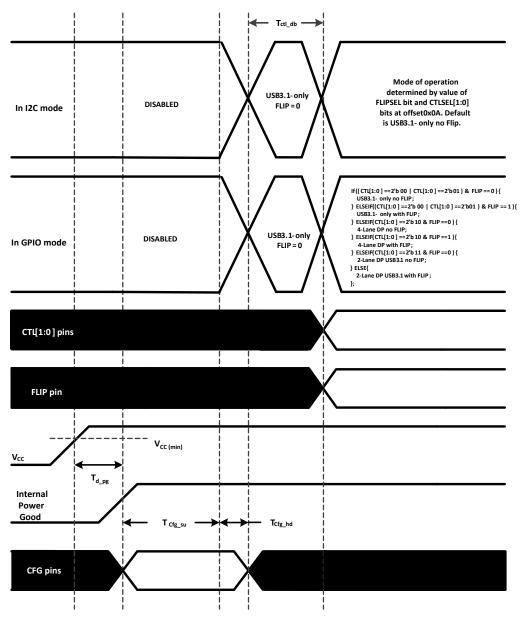

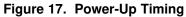

Figure 12. USB3.1 to 4-Lane DisplayPort in GPIO Mode

Figure 13. Propagation Delay

TEXAS INSTRUMENTS

www.ti.com

Figure 14. Electrical Idle Mode Exit and Entry Delay

Figure 15. Output Rise and Fall Times

Figure 16. AUX and SBU Switch ON and OFF Timing Diagram

# 8 Detailed Description

# 8.1 Overview

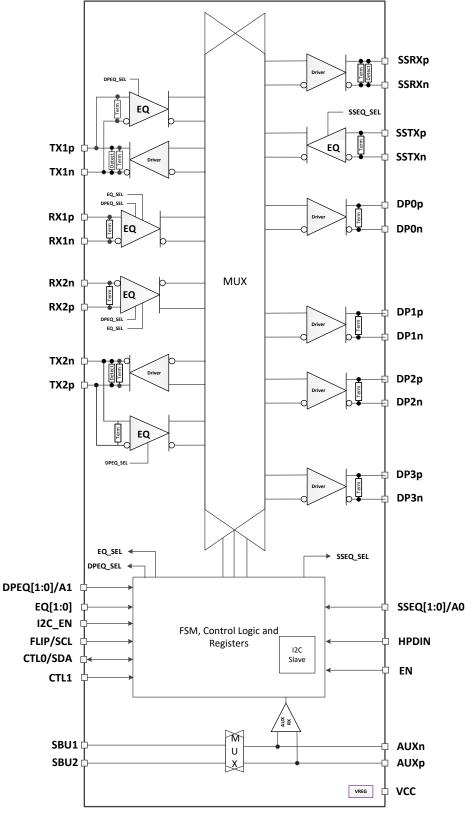

The TUSB1064 is a VESA USB Type-C Alt Mode redriving switch supporting data rates up to 8.1 Gbps for upstream facing port. This device uses 5<sup>th</sup> generation USB redriver technology. The device is used for UFP pin assignments C and D from the VESA DisplayPort Alt Mode on USB Type-C Standard.

The TUSB1064 provides several levels of receive equalization to compensate for cable and board trace loss which if not equalized causes inter-symbol interference (ISI) when USB 3.1 Gen 2 or DisplayPort 1.4 signals travel across a PCB or cable. This device requires a 3.3-V power supply. It comes in a commercial temperature range and industrial temperature range.

For a sink application, the TUSB1064 enables the system to pass both transmitter compliance and receiver jitter tolerance tests for USB 3.1 Gen 2 and DisplayPort version 1.4 HBR3. The re-driver recovers incoming data by applying equalization that compensates for channel loss, and drives out signals with a high differential voltage. Each channel has a receiver equalizer with selectable gain settings. The equalization should be set based on the amount of insertion loss in the channels connected to the TUSB1064. Independent equalization control for each channel can be set using EQ[1:0], SSEQ[1:0], and DPEQ[1:0] pins.

The TUSB1064 advanced state machine makes it transparent to hosts and devices. After power up, the TUSB1064 periodically performs receiver detection on the TX pairs. If it detects a USB 3.1 receiver, the RX termination is enabled, and the TTUSB1064 is ready to re-drive.

The device ultra-low-power architecture operates at a 3.3-V power supply and achieves Enhanced performance. The automatic LFPS De-Emphasis control further enables the system to be USB3.1 compliant.

TUSB1064 SLLSF48C – MARCH 2018 – REVISED SEPTEMBER 2019

www.ti.com

# 8.2 Functional Block Diagram

Copyright © 2017, Texas Instruments Incorporated

## 8.3 Feature Description

## 8.3.1 USB 3.1

The TUSB1064 supports USB 3.1 Gen 2 datarates up to 10 Gbps. The TUSB1064 supports all the USB defined power states (U0, U1, U2, and U3). Because the TUSB1064 is a linear redriver, it can't decode USB3.1 physical layer traffic. The TUSB1064 monitors the actual physical layer conditions like receiver termination, electrical idle, LFPS, and SuperSpeed signaling rate to determine the USB power state of the USB 3.1 interface.

The TUSB1064 features an intelligent low frequency periodic signaling (LFPS) detector. The LFPS detector automatically senses the low frequency signals and disables receiver equalization functionality. When not receiving LFPS, the TUSB1064 enables receiver equalization based on the EQ[1:0] and SSEQ[1:0] pins or values programmed into EQ1\_SEL, EQ2\_SEL, and SSEQ\_SEL registers.

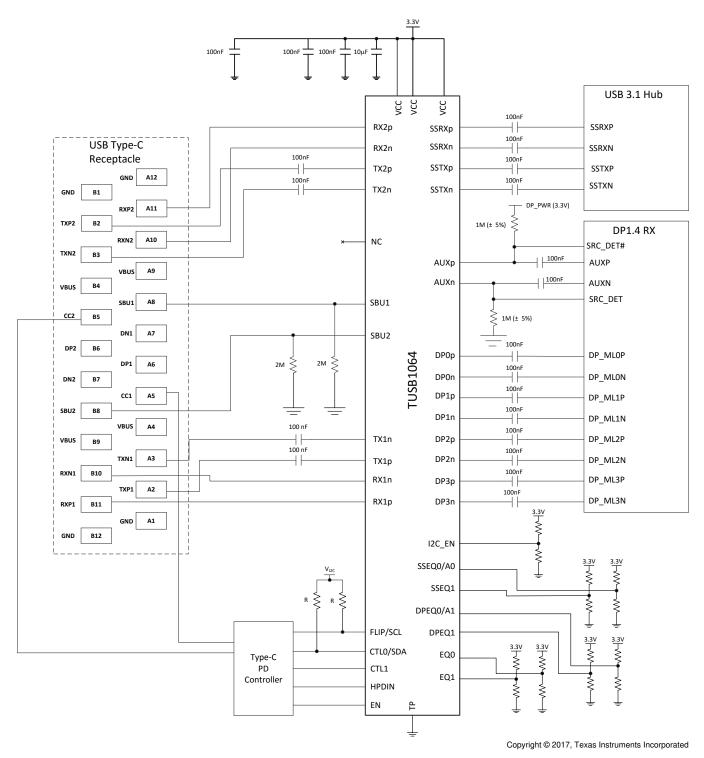

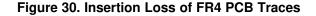

## 8.3.2 DisplayPort

The TUSB1064 supports up to 4 DisplayPort lanes at datarates up to 8.1Gbps (HBR3). The TUSB1064, when configured in DisplayPort mode, monitors the native AUX traffic as it traverses between DisplayPort source and DisplayPort sink. For the purposes of reducing power, the TUSB1064 manages the number of active DisplayPort lanes based on the content of the AUX transactions. The TUSB1064 snoops native AUX writes to DisplayPort sink's DPCD registers 0x00101 (LANE\_COUNT\_SET) and 0x00600 (SET\_POWER\_STATE). TUSB1064disables/enables lanes based on value written to LANE\_COUNT\_SET. The TUSB1064 disables all lanes when SET\_POWER\_STATE is in the D3. Otherwise, active lanes are based on value of LANE\_COUNT\_SET.

DisplayPort AUX snooping is enabled by default but can be disabled by changing the AUX\_SNOOP\_DISABLE register. Once AUX snoop is disabled, management of TUSB1064 DisplayPort lanes are controlled through various configuration registers.

### NOTE

AUX snooping feature is only supported when TUSB1064 is configured for I2C mode. When TUSB1064 is configured for GPIO mode, the AUX snoop feature is disabled and all four DP lanes are enabled if HPDIN is asserted high.

When TUSB1064's AUX snoop feature is enabled, the syncs defined by the DisplayPort standard must be received in order for AUX snoop feature to function properly. AUX writes to panel's DPCD address 0x00600 and 0x00101 should result in SET\_POWER\_STATE and LANE\_COUNT\_SET fields at TUSB1064's offset 0x12 to get set to the appropriate value. If these fields do not get set correctly, then incoming AUX may not be compliant. If this is the case, then it is best to disable AUX snoop by setting the AUX\_SNOOP\_DISABLE field at offset 0x13.

### 8.3.3 4-level Inputs

The TUSB1064 has (I2C\_EN, EQ[1:0], DPEQ[1:0], and SSEQ[1:0]) 4-level inputs pins that are used to control the equalization gain and place TUSB1064 into different modes of operation. These 4-level inputs utilize a resistor divider to help set the 4 valid levels and provide a wider range of control settings. There is an internal 35 k $\Omega$  pull-up and a 95 k $\Omega$  pull-down. These resistors, together with the external resistor connection combine to achieve the desired voltage level.

| LEVEL | SETTINGS                                                                                         |

|-------|--------------------------------------------------------------------------------------------------|

| 0     | Option 1: Tie 1 K $\Omega$ 5% to GND.<br>Option 2: Tie directly to GND.                          |

| R     | Tie 20 KΩ 5% to GND.                                                                             |

| F     | Float (leave pin open)                                                                           |

| 1     | Option 1: Tie 1 K $\Omega$ 5%to V <sub>CC</sub> .<br>Option 2: Tie directly to V <sub>CC</sub> . |

### **Table 1. 4-Level Control Pin Settings**

# NOTE

All four-level inputs are latched on rising edge of internal reset. After t<sub>cfg\_hd</sub>, the internal pull-up and pull-down resistors will be isolated in order to save power.

## 8.3.4 Receiver Linear Equalization

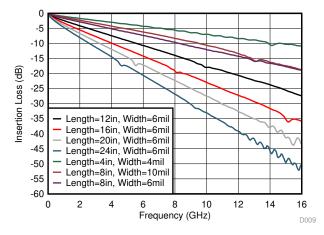

The purpose of receiver equalization is to compensate for channel insertion loss and the resulting inter-symbol interference in the system before the input or after the output of the TUSB1064. The receiver overcomes these losses by attenuating the low frequency components of the signals with respect to the high frequency components. The proper gain setting should be selected to match the channel insertion loss. Two 4-level input pins enable up to 16 possible equalization settings. USB3.1 upstream path, USB3.1 downstream path, and DisplayPort each have their own two 4-level inputs. The TUSB1064 also provides the flexibility of adjusting settings through I<sup>2</sup>C registers.

# 8.4 Device Functional Modes

## 8.4.1 Device Configuration in GPIO Mode

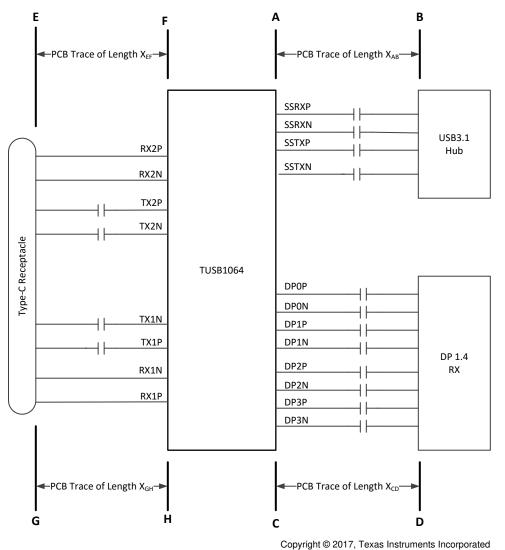

The TUSB1064 is in GPIO configuration when  $I2C\_EN = "0"$ . The TUSB1064 supports the following configurations: USB 3.1 only, 2 DisplayPort lanes + USB 3.1, or 4 DisplayPort lanes (no USB 3.1). The CTL1 pin controls whether DisplayPort is enabled. The combination of CTL1 and CTL0 selects between USB 3.1 only, 2 lanes of DisplayPort, or 4-lanes of DisplayPort as detailed in Table 2. The AUXp or AUXn to SBU1 or SBU2 mapping is controlled based on Table 3.

After power-up ( $V_{CC}$  from 0 V to 3.3 V), the TUSB1064 defaults to USB3.1 mode. The USB PD controller upon detecting no device attached to Type-C port or USB3.1 operation not required by attached device must take TUSB1064 out of USB3.1 mode by transitioning the CTL0 pin from L to H and back to L.

| CTL1 PIN | CTL0 PIN | FLIP PIN | CONFIGURATION                           | VESA DisplayPort ALT MODE<br>UFP_D CONFIGURATION |

|----------|----------|----------|-----------------------------------------|--------------------------------------------------|

| L        | L        | L        | Power Down                              | —                                                |

| L        | L        | Н        | Power Down                              | —                                                |

| L        | Н        | L        | One Port USB 3.1 - No Flip              | _                                                |

| L        | Н        | Н        | One Port USB 3.1 – With Flip            | —                                                |

| Н        | L        | L        | 4 Lane DP - No Flip                     | С                                                |

| Н        | L        | Н        | 4 Lane DP – With Flip                   | С                                                |

| Н        | Н        | L        | One Port USB 3.1 + 2 Lane DP- No Flip   | D                                                |

| Н        | Н        | Н        | One Port USB 3.1 + 2 Lane DP- With Flip | D                                                |

### Table 2. GPIO Configuration Control

# Table 3. GPIO AUXp or AUXn to SBU1 or SBU2 Mapping

|          | •        |                                                               |

|----------|----------|---------------------------------------------------------------|

| CTL1 PIN | FLIP PIN | MAPPING                                                       |

| н        | L        | $\begin{array}{l} SBU1 \to AUXn \\ SBU2 \to AUXp \end{array}$ |

| н        | Н        | $\begin{array}{l} SBU2 \to AUXn \\ SBU1 \to AUXp \end{array}$ |

| L > 2 ms | х        | Open                                                          |

Table 4 details the TUSB1064 mux routing. This table is valid for both I<sup>2</sup>C and GPIO configuration modes.

| Table 4. INPUT to OUTPUT Mapping |          |          |                   |              |  |

|----------------------------------|----------|----------|-------------------|--------------|--|

| CTL1 PIN                         | CTL0 PIN | FLIP PIN | FROM<br>INPUT PIN | OUTPUT PIN   |  |

| 1                                | 1        | 1        |                   |              |  |

| L                                | L        | L        | NA                | NA           |  |

| L                                | L        | Н        | NA                | NA           |  |

|                                  |          |          | RX1p              | SSRXp        |  |

| L                                | Н        | L        | RX1n              | SSRXn        |  |

|                                  |          |          | SSTXp             | TX1p         |  |

|                                  |          |          | SSTXn             | TX1n         |  |

|                                  |          |          | RX2p              | SSRXp        |  |

| L                                | н        | н        | RX2n              | SSRXn        |  |

|                                  |          |          | SSTXp             | TX2p         |  |

|                                  |          |          | SSTXn             | TX2n         |  |

|                                  |          |          | TX2p              | DP0p         |  |

|                                  |          |          | TX2n              | DP0n         |  |

|                                  |          |          | RX2p              | DP1p         |  |

| Н                                | L        | L        | RX2n              | DP1n         |  |

| 11                               | L        | L        | RX1p              | DP2p         |  |