Technical documentation

Support & training

DRV8662 SLOS709C – JUNE 2011 – REVISED DECEMBER 2022

# DRV8662 Piezo Haptic Driver with Integrated Boost Converter

# 1 Features

- High-Voltage Piezo Haptic Driver

- $\,$  Drives up to 100 nF at 200  $V_{PP}$  and 300 Hz  $\,$

- Drives up to 150 nF at 150  $V_{PP}$  and 300 Hz

- Drives up to 330 nF at 100 V<sub>PP</sub> and 300 Hz

- Drives up to 680 nF at 50 V<sub>PP</sub> and 300 Hz

- Differential Output

- Integrated Boost Converter

- Adjustable Boost Voltage

- Adjustable Current Limit

- Integrated Power FET and Diode

- No Transformer Required

- Fast Start Up Time of 1.5 ms

- Wide Supply Voltage Range of 3.3 V to 5.5 V

- 1.8 V Compatible Digital Pins

- Thermal Protection

- Available in a 4 mm × 4 mm × 0.9 mm QFN package (RGP)

# 2 Applications

- Mobile Phones

- Tablets

- Portable Computers

- Keyboards and Mice

- Touch Enabled Devices

# **3 Description**

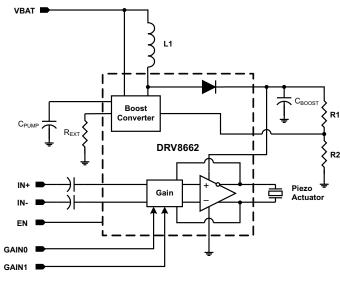

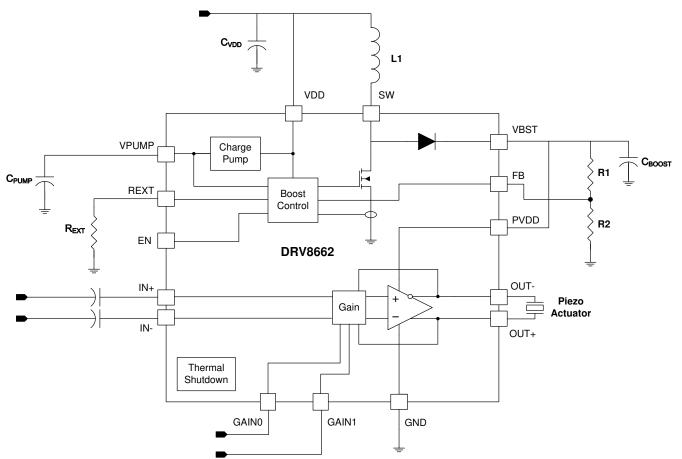

The DRV8662 is a single-chip piezo haptic driver with integrated 105 V boost switch, integrated power diode, and integrated fully-differential amplifier. This versatile device is capable of driving both high-voltage and low-voltage piezo haptic actuators. The input signal can be either differential or single-ended. The DRV8662 supports four GPIO-controlled gains: 28.8 dB, 34.8 dB, 38.4 dB, and 40.7 dB.

The boost voltage is set using two external resistors, and the boost current limit is programmable via the  $R_{EXT}$  resistor. The boost converter architecture will not allow the demand on the supply current to exceed the limit set by the  $R_{EXT}$  resistor; therefore, the DRV8662 is well-suited for portable applications. This feature also allows the user to optimize the DRV8662 circuit for a given inductor based on the desired performance requirements.

A typical start-up time of 1.5 ms makes the DRV8662 an ideal piezo driver for fast haptic responses. Thermal overload protection prevents the device from being damaged when over driven.

#### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| DRV8662     | VQFN (20) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

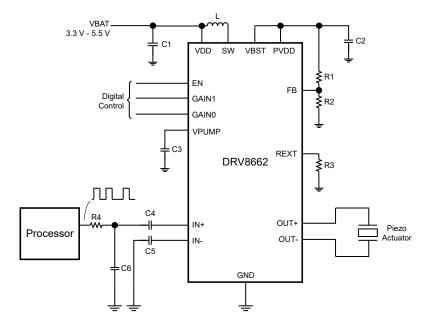

**Simplified Schematic**

# **Table of Contents**

| 1 Features                           | 1              |

|--------------------------------------|----------------|

| 2 Applications                       | 1              |

| 3 Description                        | 1              |

| 4 Revision History                   |                |

| 5 Pin Configuration and Functions    | 3              |

| 6 Specifications                     | 4              |

| 6.1 Absolute Maximum Ratings         | 4              |

| 6.2 ESD Ratings                      | 4              |

| 6.3 Recommended Operating Conditions | 4              |

| 6.4 Thermal Information              | 5              |

| 6.5 Electrical Characteristics       | <mark>5</mark> |

| 6.6 Timing Requirements              | 5              |

| 6.7 Typical Characteristics          | <mark>6</mark> |

| 7 Detailed Description               | 8              |

| 7.1 Overview                         |                |

| 7.2 Functional Block Diagram         | 8              |

| 7.3 Feature Description                 | 9  |

|-----------------------------------------|----|

| 7.4 Device Functional Modes             |    |

| 7.5 Programming                         | 11 |

| 8 Application and Implementation        |    |

| 8.1 Application Information             |    |

| 8.2 Typical Application                 |    |

| 9 Power Supply Recommendations          |    |

| 10 Layout                               |    |

| 10.1 Layout Guidelines                  |    |

| 10.2 Layout Example                     |    |

| 11 Device and Documentation Support     |    |

| 11.1 Documentation Support              |    |

| 11.2 Trademarks                         |    |

| 12 Mechanical, Packaging, and Orderable |    |

| Information                             |    |

|                                         |    |

# **4 Revision History**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| Changes from Revision B (July 2014) to Revision C (December 2022)                                                                                                                                                                                                                                                                                                                                                | Page               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Changed V <sub>DD</sub> MIN spec from 3.0 to 3.3                                                                                                                                                                                                                                                                                                                                                                 | 4                  |

| Changes from Revision A (November 2012) to Revision B (July 2014)                                                                                                                                                                                                                                                                                                                                                | Page               |

| <ul> <li>Added Device Information and ESD Rating tables, Feature Description section, Device Functional<br/>Application and Implementation section, Power Supply Recommendations section, Layout section<br/>and Documentation Support section, and Mechanical, Packaging, and Orderable Information sec</li> <li>Added the Thermal Information table after the Recommend Operating Conditions table.</li> </ul> | n, Device<br>tion1 |

| Changes from Revision * (June 2011) to Revision A (November 2012)                                                                                                                                                                                                                                                                                                                                                | Page               |

| Added C <sub>L</sub> , V <sub>IL</sub> , V <sub>IH</sub> specs to Recommended Operating Conditions table                                                                                                                                                                                                                                                                                                         | 4                  |

| Added amplifier bandwidth spec (BW) to the Electrical Characteristics table for each gain setting.                                                                                                                                                                                                                                                                                                               | 5                  |

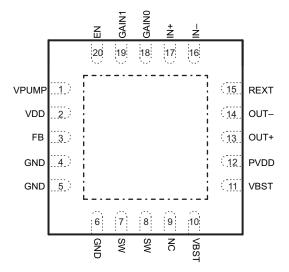

# **5** Pin Configuration and Functions

#### Table 5-1. Pin Functions

| PIN   |           | INPUT/ OUTPUT/ | DESCRIPTION                                                       |  |

|-------|-----------|----------------|-------------------------------------------------------------------|--|

| NAME  | NO. (RGP) | POWER (I/O/P)  | DESCRIPTION                                                       |  |

| EN    | 20        | I              | Chip enable                                                       |  |

| FB    | 3         | I              | Boost feedback                                                    |  |

| GAIN0 | 18        | I              | Gain programming pin – LSB                                        |  |

| GAIN1 | 19        | I              | Gain programming pin – MSB                                        |  |

| GND   | 4, 5, 6   | Р              | Ground                                                            |  |

| IN+   | 17        | I              | Non-inverting input (If unused, connect to GND through capacitor) |  |

| IN–   | 16        | I              | Inverting input (If unused, connect to GND through capacitor)     |  |

| OUT+  | 13        | 0              | Non-inverting output                                              |  |

| OUT-  | 14        | 0              | Inverting output                                                  |  |

| PVDD  | 12        | Р              | Amplifier supply voltage                                          |  |

| REXT  | 15        | I              | Resistor to ground, sets boost current limit                      |  |

| SW    | 7, 8      | Р              | Internal boost switch pin                                         |  |

| VBST  | 10, 11    | Р              | Boost output voltage                                              |  |

| VDD   | 2         | Р              | Power supply (connect to battery)                                 |  |

| VPUMP | 1         | Р              | Internal Charge-pump voltage                                      |  |

# 6 Specifications 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                |                                                     |                                | MIN  | MAX                  | UNIT |

|----------------|-----------------------------------------------------|--------------------------------|------|----------------------|------|

|                | Supply voltage                                      | VDD                            | -0.3 | 6.0                  | V    |

| VI             | Input voltage                                       | IN+, IN–, EN, GAIN0, GAIN1, FB | -0.3 | V <sub>DD</sub> +0.3 | V    |

|                | Boost/Output Voltage                                | PVDD, SW, OUT+, OUT-           |      | 120                  | V    |

| T <sub>A</sub> | Operating free-air temp                             | erature range                  | -40  | 70                   | °C   |

| TJ             | Γ <sub>J</sub> Operating junction temperature range |                                |      | 150                  | °C   |

| Sto            | orage temperature, T <sub>stg</sub>                 |                                |      | 85                   | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                          | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22- $C101^{(2)}$ | ±1500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

### 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                              |                                |                               | MIN | TYP                  | MAX  | UNIT |

|------------------|------------------------------|--------------------------------|-------------------------------|-----|----------------------|------|------|

| $V_{DD}$         | Supply voltage               | VDD                            |                               | 3.3 |                      | 5.5  | V    |

| V <sub>BST</sub> | Boost voltage                | VBST                           |                               | 15  |                      | 105  | V    |

| V <sub>IN</sub>  | Differential input voltage   |                                |                               |     | 1.8 <mark>(1)</mark> |      | V    |

|                  |                              | VBST = 105 V, Frequency = 500  | Hz, V <sub>O,PP</sub> = 200 V |     |                      | 50   |      |

|                  |                              | VBST = 105 V, Frequency = 300  | Hz, V <sub>O,PP</sub> = 200 V |     |                      | 100  |      |

|                  |                              | VBST = 80 V, Frequency = 300 H | Iz, V <sub>O,PP</sub> = 150 V |     |                      | 150  | nF   |

| CL               | Load capacitance             | VBST = 55 V, Frequency = 300 H | Hz, V <sub>O,PP</sub> = 100 V |     |                      | 330  |      |

|                  |                              | VBST = 30 V, Frequency = 300 H | Ηz, V <sub>O,PP</sub> = 50 V  |     |                      | 680  |      |

|                  |                              | VBST = 25 V, Frequency = 300 H | Hz, V <sub>O,PP</sub> = 40 V  |     |                      | 1    |      |

|                  |                              | VBST = 15 V, Frequency = 300 H | Iz, V <sub>O,PP</sub> = 20 V  |     |                      | 3    | μF   |

| V <sub>IL</sub>  | Digital input low voltage    | EN, GAIN0, GAIN1               | V <sub>DD</sub> = 3.6 V       |     |                      | 0.75 | V    |

| V <sub>IH</sub>  | Digital input high voltage   | EN, GAIN0, GAIN1               | V <sub>DD</sub> = 3.6 V       | 1.4 |                      |      | V    |

| R <sub>EXT</sub> | Current limit control resist | or                             |                               | 6   |                      | 35   | kΩ   |

| L                | Inductance for Boost Con     | verter                         |                               | 3.3 |                      |      | μH   |

(1) Gains are optimized for a 1.8V peak input

### 6.4 Thermal Information

|                       |                                              |               | UNIT |

|-----------------------|----------------------------------------------|---------------|------|

|                       |                                              | RGP (20 Pins) | UNIT |

| R <sub>θJA</sub>      | Junction-to-ambient thermal resistance       | 33.1          |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 30.9          |      |

| R <sub>θJB</sub>      | Junction-to-board thermal resistance         | 8.7           | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.4           | 0/00 |

| Ψјв                   | Junction-to-board characterization parameter | 8.7           |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.5           |      |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

# **6.5 Electrical Characteristics**

$T_A = 25^{\circ}C$ ,  $V_{O,PP} = V_{OUT+} - V_{OUT-} = 200$  V,  $C_L = 47$  nF,  $A_V = 40$  dB, L = 4.7 µH (unless otherwise noted)

|                 | PARAMETER                            | TEST CO                                                         | ONDITIONS                                          | MIN | TYP  | MAX | UNIT |

|-----------------|--------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|-----|------|-----|------|

| I <sub>IL</sub> | Digital input low current            | EN, GAIN0, GAIN1                                                | V <sub>DD</sub> = 3.6 V, V <sub>IN</sub> = 0 V     |     |      | 1   | μA   |

| I <sub>IH</sub> | Digital input high current           | EN, GAIN0, GAIN1                                                | $V_{DD}$ = 3.6 V, $V_{IN}$ = $V_{DD}$              |     |      | 5   | μA   |

| I <sub>SD</sub> | Shut down current                    | V <sub>DD</sub> = 3.6 V, V <sub>EN</sub> = 0 V                  |                                                    |     | 13   |     | μA   |

|                 |                                      | V <sub>DD</sub> = 3.6 V, V <sub>EN</sub> = V <sub>DD</sub> , VB | ST = 105 V, no signal                              |     | 24   |     | mA   |

|                 | Quiescent current                    | V <sub>DD</sub> = 3.6 V, V <sub>EN</sub> = V <sub>DD</sub> , VB | ST = 80 V, no signal                               |     | 13   |     | mA   |

| IDDQ            | Quiescent current                    | V <sub>DD</sub> = 3.6 V, V <sub>EN</sub> = V <sub>DD</sub> , VB | ST = 55 V, no signal                               |     | 9    |     | mA   |

|                 |                                      | V <sub>DD</sub> = 3.6 V, V <sub>EN</sub> = V <sub>DD</sub> , VB | ST = 30 V, no signal                               |     | 5    |     | mA   |

| R <sub>IN</sub> | Input impedance                      | All gains                                                       |                                                    |     | 100  |     | kΩ   |

|                 |                                      | GAIN<1:0> = 00                                                  |                                                    |     | 28.8 |     |      |

| ^               | M Amplifier gain                     | GAIN<1:0> = 01                                                  |                                                    |     | 34.8 |     | dB   |

| A <sub>V</sub>  | Ampiner gain                         | GAIN<1:0> = 10                                                  |                                                    |     | 38.4 |     |      |

|                 |                                      | GAIN<1:0> = 11                                                  |                                                    |     | 40.7 |     |      |

|                 |                                      | GAIN<1:0> = 00, V <sub>O,PP</sub> = 50                          | ) V, No Load                                       |     | 20   |     |      |

| BW              | Amplifian Dandwidth                  | GAIN<1:0> = 01, V <sub>O,PP</sub> = 10                          | 00 V, No Load                                      |     | 10   |     |      |

| DVV             | Amplifier Bandwidth                  | GAIN<1:0> = 10, V <sub>O,PP</sub> = 15                          | GAIN<1:0> = 10, V <sub>O,PP</sub> = 150 V, No Load |     | 7.5  |     | kHz  |

|                 |                                      | GAIN<1:0> = 11, V <sub>O,PP</sub> = 20                          | 0 V, No Load                                       |     | 5    |     |      |

|                 |                                      | V <sub>DD</sub> = 3.6 V, C <sub>L</sub> = 10 nF, f =            | 150 Hz, V <sub>O,PP</sub> = 200 V                  |     | 75   |     |      |

|                 | Average battery current during       | V <sub>DD</sub> = 3.6 V, C <sub>L</sub> = 10 nF, f =            | 300 Hz, V <sub>O,PP</sub> = 200 V                  |     | 115  |     | m (  |

| IBAT, AVG       | operation                            | V <sub>DD</sub> = 3.6 V, C <sub>L</sub> = 47 nF, f =            | 150 Hz, V <sub>O,PP</sub> = 200 V                  |     | 210  |     | mA   |

|                 |                                      | V <sub>DD</sub> = 3.6 V, C <sub>L</sub> = 47 nF, f =            | 300 Hz, V <sub>O,PP</sub> = 200 V                  |     | 400  |     |      |

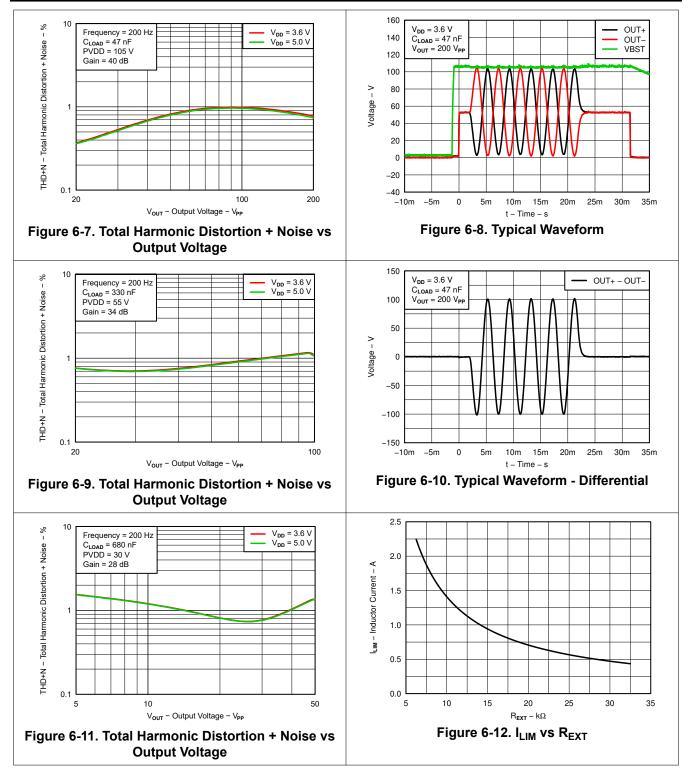

| THD+N           | Total harmonic distortion plus noise | f = 300 Hz, V <sub>O,PP</sub> = 200 V                           |                                                    |     | 1%   |     |      |

# 6.6 Timing Requirements

|                 |               |                                                                                 | MIN | TYP | MAX | UNIT |  |

|-----------------|---------------|---------------------------------------------------------------------------------|-----|-----|-----|------|--|

| t <sub>SU</sub> | Start-up time | $V_{DD}$ = 3.6 V, time from EN high until boost and amplifier are fully enabled |     | 1.5 |     | ms   |  |

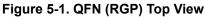

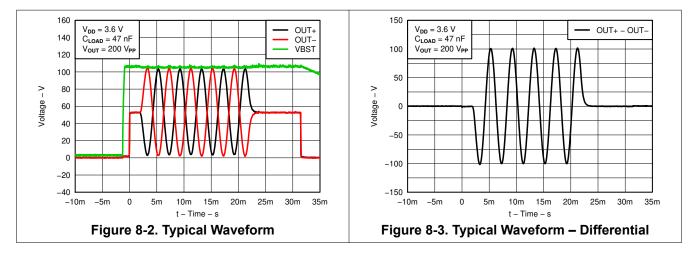

# 6.7 Typical Characteristics

$V_{DD}$  = 3.6 V,  $R_{EXT}$  = 7.5 k $\Omega$ , L = 4.7  $\mu$ H, Differential Input

DRV8662 SLOS709C – JUNE 2011 – REVISED DECEMBER 2022

# 7 Detailed Description

# 7.1 Overview

The DRV8662 accepts the typical battery range used in portable applications (3.3 V to 5.5 V) and creates a boosted supply rail with an integrated DC-DC converter. This boosted supply rail is fed to an internal, high-voltage, fully-differential amplifier that is capable of driving capacitive loads such as piezos with signals up to 200 V<sub>PP</sub>. No transformer is required for boost operation. Only a single inductor is needed. The boost power FET and power diode are both integrated within the device.

## 7.2 Functional Block Diagram

### 7.3 Feature Description

#### 7.3.1 Fast Start-up (Enable Pin)

The DRV8662 features a fast startup time, which is essential for achieving low latency in haptic applications. When the EN pin transitions from low to high, the boost supply is turned on, the input capacitor is pre-charged, and the amplifier is enabled in a typical 1.5 ms total startup time. In the system application, the entire system latency should be kept to less than 30 ms total to be imperceptible to the end user. At 1.5 ms, the DRV8662 will be a small percentage of the total system latency.

#### 7.3.2 Gain Control

The gain from IN+/IN– to OUT+/OUT– is given by the table below.

| GAIN1 | GAIN0 | Gain (dB) |

|-------|-------|-----------|

| 0     | 0     | 28.8      |

| 0     | 1     | 34.8      |

| 1     | 0     | 38.4      |

| 1     | 1     | 40.7      |

The gains are optimized to achieve approximately 50  $V_{PP}$ , 100  $V_{PP}$ , 150  $V_{PP}$ , or 200  $V_{PP}$  at the output without clipping from a 1.8 V peak single-ended input signal source.

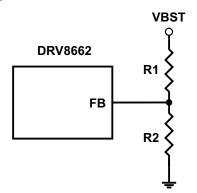

#### 7.3.3 Adjustable Boost Voltage

The output voltage of the integrated boost converter may be adjusted by a resistive feedback divider between the boost output voltage (VBST) and the feedback pin (FB). The boost voltage should be programmed to a value greater than the maximum peak signal voltage that the user expects to create with the DRV8662 amplifier. Lower boost voltages will achieve better system efficiency when lower amplitude signals are applied, so the user should take care not to use a higher boost voltage than necessary. The maximum allowed boost voltage is 105V.

#### 7.3.4 Adjustable Boost Current Limit

The current limit of the boost switch may be adjusted via a resistor to ground placed on the REXT pin. The programmed current limit should be less than the rated saturation limit of the inductor selected by the user to avoid damage to both the inductor and the DRV8662. If the combination of the programmed limit and inductor saturation is not high enough, then the output current of the boost converter will not be high enough to regulate the boost output voltage under heavy load conditions. This will, in turn, cause the boosted rail to sag, possibly causing distortion of the output waveform.

#### 7.3.5 Internal Charge Pump

The DRV8662 has an integrated charge pump to provide adequate gate drive for internal nodes. The output of this charge pump is placed on the VPUMP pin. An X5R or X7R storage capacitor of 0.1  $\mu$ F with a voltage rating of 10 V or greater must be placed at this pin.

#### 7.3.6 Thermal Shutdown

The DRV8662 contains an internal temperature sensor that will shut down both the boost converter and the amplifier when the temperature threshold is exceeded. When the die temperature falls below the threshold, the device will restart operation automatically as long as the EN pin is high. Continuous operation of the DRV8662 is not recommended. Most haptic use models only operate the DRV8662 in short bursts. The thermal shutdown function will protect the DRV8662 from damage when overdriven, but usage models which drive the DRV8662 into thermal shutdown should always be avoided.

# 7.4 Device Functional Modes

#### 7.4.1 Startup/shutdown Sequencing

A simple startup sequence should be employed to maintain smooth haptic operation. If the sequence is not followed, unintended haptic events or sounds my occur. Use the following steps to play back each haptic waveform.

### 7.4.1.1 PWM Source

- 1. Send 50% duty cycle from the processor to the DRV8662 input filter. This is to allow the source and input filter to settle before the DRV8662 is fully enabled. At the same time (or on the next available processor cycle), transition the DRV8662 enable pin from logic low to logic high.

- 2. Wait 2 ms to ensure that the DRV8662 circuitry is fully enabled and settled.

- 3. Begin and complete playback of the haptic waveform. The haptic waveform PWM should end with a 50% duty cycle to bring the differential output back to 0 V.

- 4. Transition the DRV8662 enable pin from high to low and power down the PWM source.

#### 7.4.1.2 DAC Source

- 1. Set the DAC to its mid-scale code. This is to allow the source and input capacitors to settle before the DRV8662 is fully enabled. At the same time (or on the next available processor cycle), transition the DRV8662 enable pin from logic low to logic high.

- 2. Wait 2 ms to ensure that the DRV8662 circuitry is fully enabled and settled.

- 3. Begin and complete playback of the haptic waveform. The haptic waveform should end with a mid-scale DAC code to bring the differential output back to 0 V.

- 4. Transition the DRV8662 enable pin from high to low and power down the DAC source.

#### 7.4.2 Low-voltage Operation

The lowest gain setting is optimized for 50 V<sub>PP</sub> with a boost voltage of 30 V. Some applications may not need 50 V<sub>PP</sub>, so the user may elect to program the boost converter as low as 15 V to improve efficiency. When using boost voltages lower than 30 V, some special considerations are in order. First, to reduce boost ripple to an acceptable level, a 50 V rated, 0.22  $\mu$ F boost capacitor is recommended. Second, the full-scale input range may need adjustment to avoid clipping. Normally, a 1.8 V, single-ended PWM signal will give 50 V<sub>PP</sub> at the lowest gain. For example, if the boost voltage is set to 25 V for a 40 V<sub>PP</sub> full-scale output signal, the full-scale input range drops to 1.44 V for single-ended PWM inputs. An input voltage divider may be desired in this case if a 1.8V I/O is used as a PWM source.

### 7.5 Programming

### 7.5.1 Programming the Boost Voltage

The boost output voltage (VBST) is programmed via two external resistors as shown in Figure 7-1.

Figure 7-1. Boost Voltage Programming

The boost output voltage is given by Equation 1:

$$V_{\text{BOOST}} = V_{\text{FB}} \left[ 1 + \frac{R_1}{R_2} \right]$$

(1)

where  $V_{FB}$  = 1.32 V.

VBST should be programmed to a value 5.0 V greater than the largest peak voltage expected in the system to allow adequate amplifier headroom. Since the programming range for the boost voltage extends to 105 V, the leakage current through the resistor divider can become significant. It is recommended that the sum of the resistance of R1 and R2 be greater than 500 k $\Omega$ . Note that when resistor values greater than 1 M $\Omega$  are used, PCB contamination may cause boost voltage inaccuracy. Exercise caution when soldering large resistances, and clean the area when finished for best results.

#### 7.5.2 Programing the Boost Current Limit

The peak current drawn from the supply through the inductor is set solely by the  $R_{EXT}$  resistor. Note that this peak current limit is independent of the inductance value chosen, but the inductor should be capable of handling this programmed limit. The relationship of  $R_{EXT}$  to  $I_{LIM}$  is approximated by Equation 2.

$$R_{EXT} = \left( K \frac{V_{REF}}{I_{LIM}} \right) - R_{INT}$$

(2)

where K = 10500,  $V_{REF}$  = 1.35 V,  $R_{INT}$  = 60  $\Omega$ , and  $I_{LIM}$  is the desired peak current limit through the inductor.

### **8** Application and Implementation

#### Note

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The DRV8662 is typically used in systems that require haptic feedback using high-voltage Piezo actuators. These systems typically contain an applications processor or microcontroller, which generates a haptic waveform. This section contains two examples of such systems and how to appropriately configure the input signal for the DRV8662.

#### 8.2 Typical Application

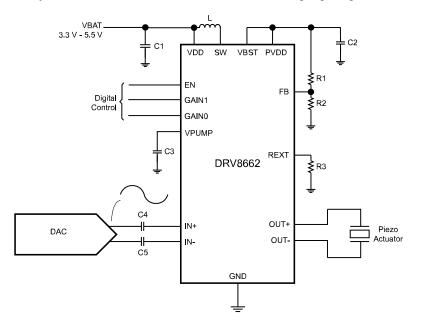

#### 8.2.1 DRV8662 System Diagram with DAC Input

In the following DRV8662 diagram, the DRV8662 is configured with a differential DAC input and a generic Piezo actuator. This is useful for systems that have an available DAC or analog signal generator.

Figure 8-1. DRV8662 System Diagram with DAC Input

#### 8.2.1.1 Design Requirements

For this example, use the parameters shown in Table 8-1.

| Table 8-1. Design Requirements           |                           |  |  |  |  |  |  |

|------------------------------------------|---------------------------|--|--|--|--|--|--|

| DESIGN PARAMETER                         | EXAMPLE VALUE             |  |  |  |  |  |  |

| VDD                                      | 3.3 V – 5.5 V             |  |  |  |  |  |  |

| Boost Converter                          | 20-105 V                  |  |  |  |  |  |  |

| Output Voltage                           | 2 x Boost Converter (Vpp) |  |  |  |  |  |  |

| Differential Input Voltage (IN+,<br>IN-) | 1.8 Vp Sine wave          |  |  |  |  |  |  |

Table 8-2 contains a list of components required for configuring the DRV8662. The components labeled "Standard" can be used "as-is"; and, the components labeled "Configure" require the designer to evaluate specific system requirements.

| COMPONENT   | DESCRIPTION                                    | RECOMMENDED VALUE                         | UNIT | USE       |

|-------------|------------------------------------------------|-------------------------------------------|------|-----------|

| CVDD        | VDD bypass capacitor                           | 0.1                                       | μF   | Standard  |

| CPUMP       | Voltage pump capacitor                         | 0.1                                       | μF   | Standard  |

| CIN+ / CIN- | IN+ / IN- AC coupling capacitors               | 1                                         | μF   | Standard  |

| REXT        | Boost current limit resistor                   | See Programing the Boost Current<br>Limit | Ω    | Configure |

| CPVDD       | Boost converter output capacitor               | See Boost Capacitor Selection             | μF   | Configure |

| L           | Boost converter inductor                       | See Inductor Selection                    | μH   | Configure |

| R1          | Boost converter high-side<br>feedback resistor | See Programming the Boost<br>Voltage      | Ω    | Configure |

| R2          | Boost converter low-side<br>feedback resistor  | SeeProgramming the Boost<br>Voltage       | Ω    | Configure |

#### Table 8-2. List of Components

### 8.2.1.2 Detailed Design Procedure

#### 8.2.1.2.1 Inductor Selection

Inductor selection plays a critical role in the performance of the DRV8662. The range of recommended inductances is from 3.3  $\mu$ H to 22  $\mu$ H. In general, higher inductances within a given manufacturer's inductor series have lower saturation current limits, and vice-versa. When a larger inductance is chosen, the DRV8662 boost converter will automatically run at a lower switching frequency and incur less switching losses; however, larger values of inductance may have higher equivalent series resistance (ESR), which will increase the parasitic inductor losses. Since lower values of inductance generally have higher saturation currents, they are a better choice when attempting to maximize the output current of the boost converter. The following table has sample inductors that provide adequate performance.

For inductor recommendations, see DRV8662EVM User's Guide (SLOU319)

#### 8.2.1.2.2 Piezo Actuator Selection

There are several key specifications to consider when choosing a piezo actuator for haptics such as dimensions, blocking force, and displacement. However, the key electrical specifications from the driver perspective are voltage rating and capacitance. At the maximum frequency of 500 Hz, the DRV8662 is optimized to drive up to 50 nF at 200  $V_{PP}$ , which is the highest voltage swing capability. It will drive larger capacitances if the programmed boost voltage is lowered and/or the user limits the input frequency range to lower frequencies (e.g. 300 Hz).

For piezo actuator recommendations, see the DRV8662EVM User's Guide (SLOU319).

#### 8.2.1.2.3 Boost Capacitor Selection

The boost output voltage may be programmed as high as 105V. A capacitor with a voltage rating of at least the boost output voltage must be selected. Since ceramic capacitors tend to come in ratings of 100 V or 250 V, a 250 V rated 100 nF capacitor of the X5R or X7R type is recommended for the 105 V case. The selected capacitor should have a minimum working capacitance of at least 50 nF.

#### 8.2.1.2.4 Current Consumption Calculation

It is useful to understand how the voltage driven onto a piezo actuator relates to the current consumption from the power supply. Modeling a piezo element as a pure capacitor is reasonably accurate. The equation for the current through a capacitor for an applied sinusoid is given by Equation 3:

$$I_{Capacitor(Peak)} = 2\pi \times f \times C \times V_P$$

(3)

where f is the frequency of the sinusoid in Hz, C is the capacitance of the piezo load in farads, and  $V_P$  is the peak voltage. At the power supply (usually a battery), the actuator current is multiplied by the boost-supply ratio and divided by the efficiency of the boost converter as shown by Equation 4.

$$I_{BAT(Peak)} = 2\pi \times f \times C \times V_P \times \frac{V_{Boost}}{V_{BAT} \times \mu_{Boost}}$$

(4)

Substituting typical values for the variables of this equation yields a typical peak current seen by the battery with a sine input as in Equation 5.

$$I_{BAT(Peak)} = 2\pi \times 300 \ Hz \times 50 \ nF \times 100 \times \frac{105}{3.6 \times 0.7} = 392 \ mA \tag{5}$$

#### 8.2.1.2.5 Input Filter Considerations

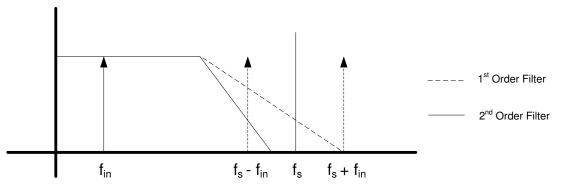

Depending on the quality of the source signal provided to the DRV8662, an input filter may be required. Some key factors to consider are whether the source is generated from a DAC or from PWM and the out-of-band content generated. If proper anti-image rejection filtering is used to eliminate image components, the filter can possibly be eliminated depending on the magnitude of the out-of-band components. If PWM is used, at least a 1<sup>st</sup> order RC filter is required. The PWM sample rate should be greater than 30 kHz to keep the PWM ripple from reaching the piezo element and dissipating unnecessary power. A 2<sup>nd</sup> order RC filter may be desirable to further eliminate out-of-band signal content to further drive down power dissipation and eliminate audible noise.

#### 8.2.1.3 Application Curves

#### 8.2.2 DRV8662 System Diagram with Filtered Single-Ended PWM Input

The DRV8662 can be used with a PWM input signal for systems that do not have an available DAC or analog output. Most piezo actuator systems require a PWM input filter to remove any unwanted noise.

#### Figure 8-4. DRV8662 System Diagram with Filtered Single-Ended PWM Input

#### 8.2.2.1 Design Requirements

For this example, use the parameters shown in Table 8-3.

| Table 0-5. Design Requirements           |                           |  |  |  |  |  |  |

|------------------------------------------|---------------------------|--|--|--|--|--|--|

| DESIGN PARAMETER                         | EXAMPLE VALUE             |  |  |  |  |  |  |

| VDD                                      | 3.3 V – 5.5 V             |  |  |  |  |  |  |

| Boost Converter                          | 20-105 V                  |  |  |  |  |  |  |

| Output Voltage                           | 2 x Boost Converter (Vpp) |  |  |  |  |  |  |

| Differential Input Voltage (IN+,<br>IN-) | 1.8 Vp PWM                |  |  |  |  |  |  |

Table 8-3. Design Requirements

Table 8-4 contains a list of components required for configuring the DRV8662. The components labeled "Standard" can be used "as-is"; and, the components labeled "Configure" require the designer to evaluate specific system requirements.

| Table 6-4. List of Components |                                                |                                        |      |           |  |  |  |  |  |

|-------------------------------|------------------------------------------------|----------------------------------------|------|-----------|--|--|--|--|--|

| COMPONENT                     | DESCRIPTION                                    | RECOMMENDED VALUE                      | UNIT | USE       |  |  |  |  |  |

| CVDD                          | VDD bypass capacitor                           | 0.1                                    | μF   | Standard  |  |  |  |  |  |

| CPUMP                         | Voltage pump capacitor                         | 0.1                                    | μF   | Standard  |  |  |  |  |  |

| CIN+ / CIN-                   | IN+ / IN- AC coupling capacitors               | 1                                      | μF   | Standard  |  |  |  |  |  |

| REXT                          | Boost current limit resistor                   | See Programing the Boost Current Limit | Ω    | Configure |  |  |  |  |  |

| CPVDD                         | Boost converter output capacitor               | See Boost Capacitor Selection          | μF   | Configure |  |  |  |  |  |

| L                             | Boost converter inductor                       | See Inductor Selection                 | μH   | Configure |  |  |  |  |  |

| R1                            | Boost converter high-side<br>feedback resistor | See Programming the Boost Voltage      | Ω    | Configure |  |  |  |  |  |

#### Table 8-4. List of Components

| Table 8-4. List of Components (continued)                                        |                                               |                                  |   |           |  |  |  |  |  |

|----------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------|---|-----------|--|--|--|--|--|

| COMPONENT         DESCRIPTION         RECOMMENDED VALUE         UNIT         USE |                                               |                                  |   |           |  |  |  |  |  |

| R2                                                                               | Boost converter low-side<br>feedback resistor | SeeProgramming the Boost Voltage | Ω | Configure |  |  |  |  |  |

#### 8.2.2.2 Detailed Design Procedure

Use the following section for designing the DRV8662 input filter. See the DRV8662 System with DAC Input Detailed Design Procedure for the remaining design.

#### 8.2.2.2.1 Input Filter Design

When using a PWM input, a low-pass filter is required. The primary parameters for determining the input filter are the PWM input frequency and sample rate. Because haptic waveforms are typically less than 500Hz, the input filter must attenuate frequencies above 500 Hz. For samples rates above 20 kHz, a simple first-order RC filter is recommended; however, for sample rates much lower (such as 8 kHz), a first-order filter may not sufficiently attenuate the high-frequency content. Thus, for lower sampling rates, a second-order RC filter may be required. The DRV8662EVM User's Guide contains example filter configurations for both first-order and second-order filters. The DRV8662EVM default configuration uses a second-order, differential filter, but it can be replaced by a first-order, single-ended or differential filter.

Apply these criteria to select an input filter:

- 1. First-order RC filters, both single-ended and differential, are recommended for 20 kHz and higher data sample rates. The first-order filters have adequate settling time and the fewest components.

- 2. Second-order filters are recommended for noiseless operation when using a lower data sample rate where a sharper cutoff is necessary.

- 3. The attenuation at the PWM carrier frequency should be at least -40 dB for haptic applications.

#### 8.2.2.3 Application Curves

See DRV8662 System with DAC Input Application Curves.

# 9 Power Supply Recommendations

The recommended voltage supply range for the DRV8662 is 3.3 V to 5.5 V. For proper operation, place a 0.1  $\mu$ F low equivalent series resistance (ESR) supply-bypass capacitor of X5R or X7R type near the VDD pin with a voltage rating of at least 10 V.

The internal charge pump requires a 0.1  $\mu$ F capacitor of X5R or X7R type with a voltage rating of 10 V or greater be placed between the VPUMP pin and GND for proper operation and stability. Do not use the charge pump as a voltage source for any other devices.

# 10 Layout 10.1 Layout Guidelines

- To achieve optimum device performance, use of the thermal footprint outlined by this datasheet is recommended. See land pattern diagram for exact dimensions. The DRV8662 power pad must be soldered directly to the thermal pad on the printed circuit board. The printed circuit board thermal pad should be connected to the ground net with thermal vias to any existing backside/internal copper ground planes. Connection to a ground plane on the top layer near the corners of the device is also recommended.

- Another key layout consideration is to keep the boost programming resistors (R1 and R2) as close as

possible to the FB pin of the DRV8662. Care should be taken to avoid getting the FB trace near the SW

trace.

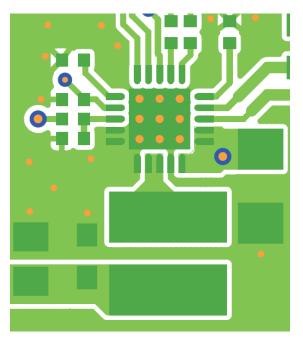

# 10.2 Layout Example

Figure 10-1. Layout Example

# **11 Device and Documentation Support**

### **11.1 Documentation Support**

### 11.1.1 Related Documentation

DRV8662EVM User's Guide (SLOU319)

DRV8662 Configuration Guide (SLOA198)

### 11.2 Trademarks

All trademarks are the property of their respective owners.

### 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

### PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| DRV8662RGPR      | ACTIVE        | QFN          | RGP                | 20   | 3000           | RoHS & Green    | NIPDAU                               | Level-4-260C-72 HR   | -40 to 70    | 8662                    | Samples |

| DRV8662RGPT      | ACTIVE        | QFN          | RGP                | 20   | 250            | RoHS & Green    | NIPDAU                               | Level-4-260C-72 HR   | -40 to 70    | 8662                    | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

www.ti.com

# PACKAGE OPTION ADDENDUM

www.ti.com

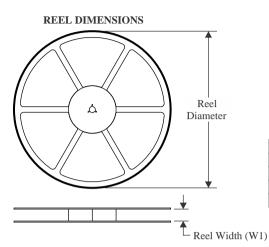

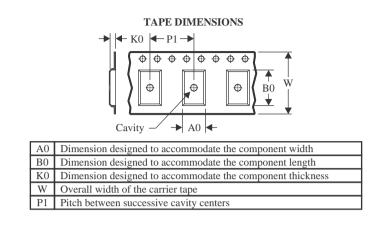

# TAPE AND REEL INFORMATION

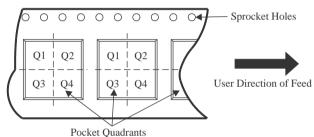

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| DRV8662RGPR                 | QFN             | RGP                | 20 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| DRV8662RGPT                 | QFN             | RGP                | 20 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

www.ti.com

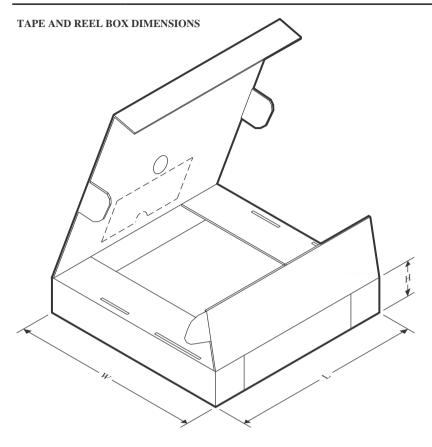

# PACKAGE MATERIALS INFORMATION

20-Apr-2023

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV8662RGPR | QFN          | RGP             | 20   | 3000 | 346.0       | 346.0      | 33.0        |

| DRV8662RGPT | QFN          | RGP             | 20   | 250  | 210.0       | 185.0      | 35.0        |

# **RGP 20**

4 x 4, 0.5 mm pitch

# **GENERIC PACKAGE VIEW**

# VQFN - 1 mm max height

VERY THIN QUAD FLATPACK

Images above are just a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

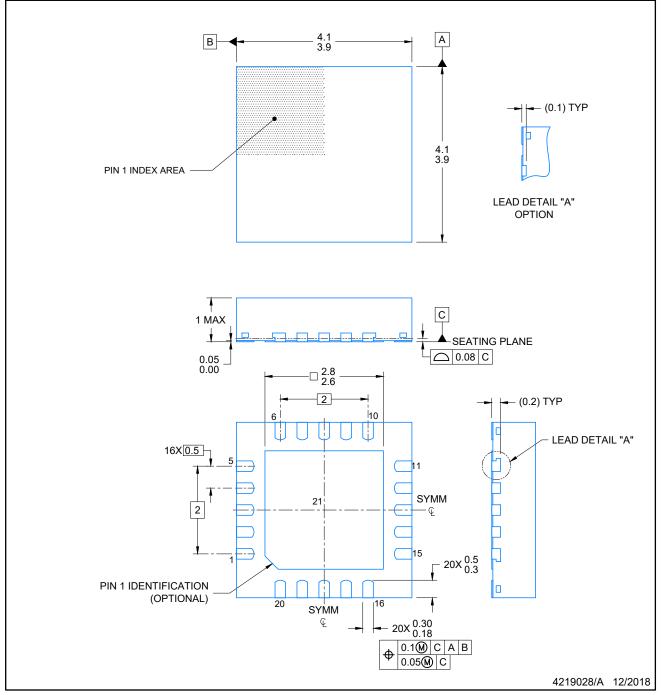

# **RGP0020D**

# **PACKAGE OUTLINE**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK- NO LEAD

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

- 2. This drawing is subject to change without notice.

- 3. The package thermal pad must be soldered to the printed circuit board for optimal thermal and mechanical performance.

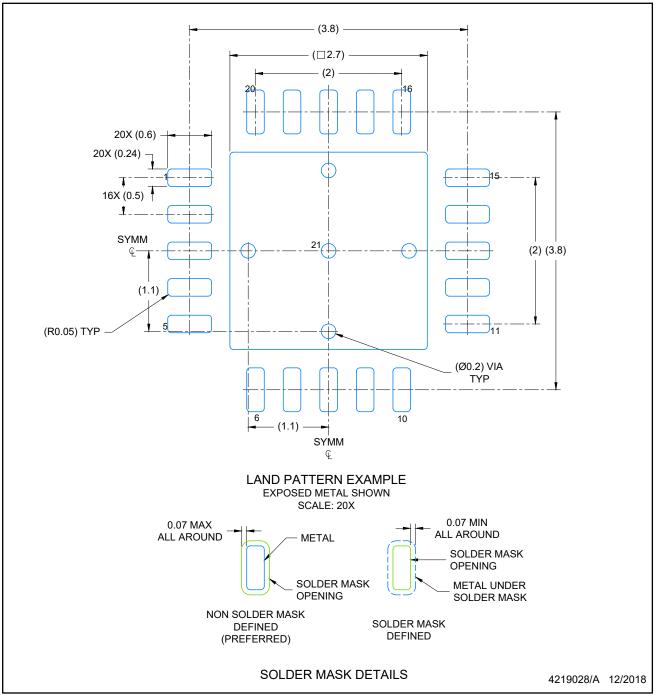

# **RGP0020D**

# **EXAMPLE BOARD LAYOUT**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

- 4. This package is designed to be soldered to a thermal pad on the board. For more information, see Texas Instruments literature number SLUA271 (www.ti.com/lit/slua271).

- 5. Vias are optional depending on application, refer to device data sheet. If any vias are implemented, refer to their locations shown on this view. It is recommended that vias under paste be filled, plugged or tented.

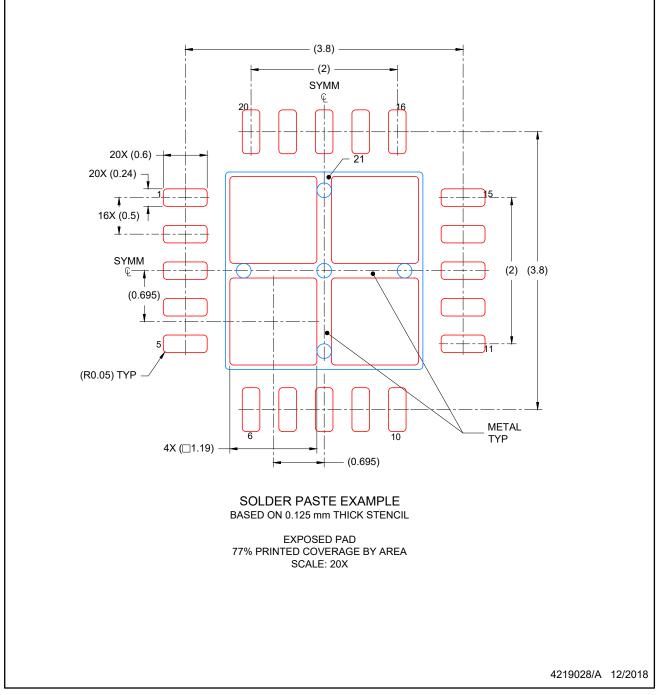

# **RGP0020D**

# **EXAMPLE STENCIL DESIGN**

# VQFN - 1 mm max height

PLASTIC QUAD FLATPACK- NO LEAD

NOTES: (continued)

6. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated