TUSB2043 4-PORT HUB FOR THE UNIVERSAL SERIAL BUS WITH OPTIONAL SERIAL EEPROM INTERFACE SLLS308A – FEBRUARY 1999 – REVISED AUGUST 1999

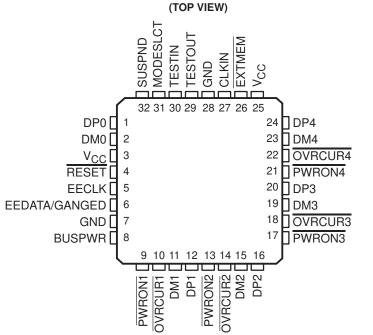

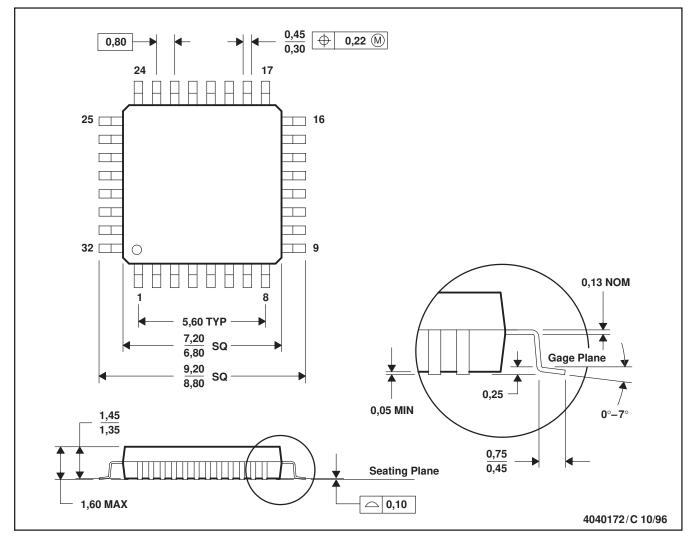

**VF PACKAGE**

- Universal Serial Bus (USB) Version 1.1 Compliant

- 32-Pin TQFP Package With a 0.8 mm Pin Pitch

- 3.3-V Low Power ASIC Logic

- Integrated USB Transceivers

- State Machine Implementation Requires No Firmware Programming

- One Upstream Port and Four Downstream Ports

- All Downstream Ports Support Full-Speed and Low-Speed Operations

- Two Power Source Modes - Self-Powered Mode

- Bus-Powered Mode

- Power Switching and Over-Current Reporting is Provided Ganged or Per Port

- Supports Suspend and Resume Operations

- Supports Programmable Vendor ID and Product ID With External Serial EEPROM

- 3-State EEPROM Interface Allows EEPROM Sharing

- Push-Pull Outputs for PWRON Eliminate the Need for External Pullup Resistors

- Noise Filtering on OVRCUR Provides Immunity to Voltage Spikes

- Package Pinout Allows 2-Layer PCB

- Migrated From Proven TUSB2040 Hub

- Lower Cost Than the TUSB2040 Hub

#### description

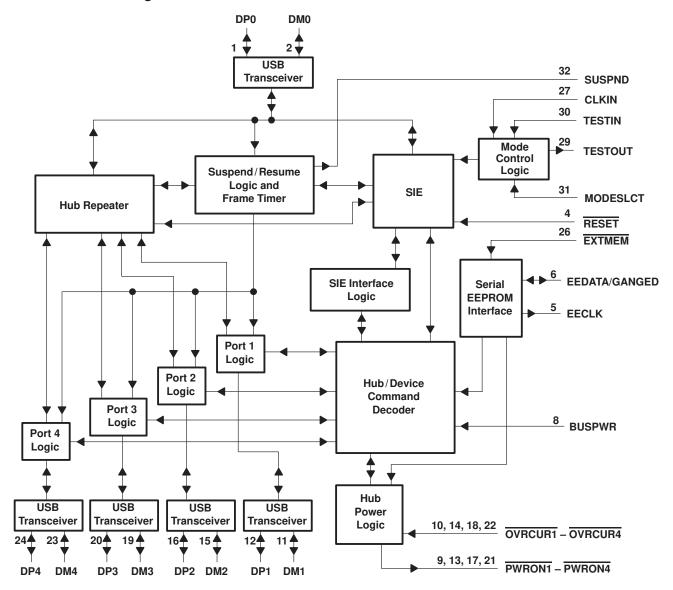

The TUSB2043 is a 3.3 V CMOS hub device that provides one upstream port and four downstream ports in compliance with the 1.1 Universal Serial Bus (USB) specification. Because this device is implemented with a digital state machine instead of a microcontroller, no firmware programming is required. Fully compliant USB transceivers are integrated into the ASIC for all upstream and downstream ports. The downstream ports support both full-speed and low-speed devices by automatically setting the slew rate according to the speed of the device attached to the ports. The configuration of the BUSPWR pin selects either the bus-powered or the self-powered mode.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

#### description (continued)

Configuring the GANGED input determines the power switching and over-current detection modes for the downstream ports. External power management devices such as the TPS2044 are required to control the 5-V source to the downstream ports according to the corresponding values of the PWRON pin. Upon detecting any over-current conditions, the power management device sets the corresponding OVRCUR pin of the TUSB2043 to a logic low. If GANGED is high, all PWRON outputs switch together and if any OVRCUR is activated, all ports transition to power-off state. If GANGED is low, the PWRON outputs and OVRCUR inputs operate on a per port basis.

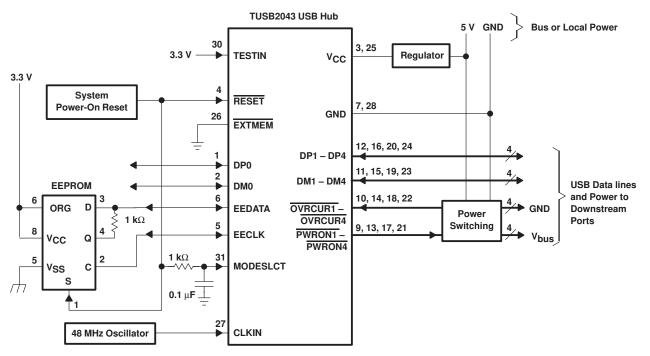

The EXTMEM pin enables or disables the optional EEPROM interface. When the EXTMEM pin is high, the product ID (PID) displayed during enumeration is General-Purpose USB Hub. For this default, pin 5 is disabled and pin 6 functions as the GANGED input pin. If custom PID and Vendor ID (VID) descriptors are desired, the EXTMEM pin must be low (EXTMEM = 0). For this configuration, pin 5 and pin 6 function as the EEPROM interface with pin 5 and pin 6 functioning as the EECLK and EEDATA, respectively. See Table 1 for a description of the EEPROM memory map.

Other useful features of the TUSB2043 include a package with a 0.8 mm pin pitch for easy PCB routing and assembly, push-pull outputs for the PWRON pins eliminate the need for pullup resistors required by traditional open collector I/Os, and OVRCUR pins with noise filtering for increased immunity to voltage spikes.

## TUSB2043 4-PORT HUB FOR THE UNIVERSAL SERIAL BUS WITH OPTIONAL SERIAL EEPROM INTERFACE SLLS308A – FEBRUARY 1999 – REVISED AUGUST 1999

## functional block diagram

# **TUSB2043** 4-PORT HUB FOR THE UNIVERSAL SERIAL BUS WITH OPTIONAL SERIAL EEPROM INTERFACE SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

## **Terminal Functions**

| TERMINAL<br>NAME NO.      |                   |     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|---------------------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                           |                   | I/O |                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| BUSPWR                    | 8                 | I   | Power source indicator. BUSPWR is an active high input that indicates whether the downstream ports source their power from the USB cable or a local power supply. For the bus-power mode, this pin should be pulled to 3.3 V, and for the self-powered mode, this pin should be pulled low. This standard TTL input must not change dynamically during operation.                                                               |  |  |  |

| DM0                       | 2                 | I/O | Root port USB differential data minus. DM0 paired with DP0 constitutes the upstream USB port.                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| DM1 – DM4                 | 11, 15,<br>19, 23 | I/O | USB differential data minus. DM1 – DM4 paired with DP1 – DP4 support up to four downstream USB ports.                                                                                                                                                                                                                                                                                                                           |  |  |  |

| DP0                       | 1                 | I/O | Root port USB differential data plus. DP0 paired with DM0 constitutes the upstream USB port.                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| DP1 – DP4                 | 12, 16,<br>20, 24 | I/O | USB differential data plus. DP1 – DP4 paired with DM1 – DM4 support up to four downstream USB ports.                                                                                                                                                                                                                                                                                                                            |  |  |  |

| EECLK                     | 5                 | 0   | EEPROM serial clock. When $\overrightarrow{\text{EXTMEM}}$ is high, the $\overrightarrow{\text{EEPROM}}$ interace is disabled. The $\overrightarrow{\text{EECLK}}$ pin is disabled and should be left floating (unconnected). When $\overrightarrow{\text{EXTMEM}}$ is low, $\overrightarrow{\text{EECLK}}$ acts as a 3-state serial clock output to the $\overrightarrow{\text{EEPROM}}$ with a 100 $\mu$ A internal pulldown. |  |  |  |

| EEDATA/<br>GANGED         | 6                 | I/O | EEPROM serial data/power management mode indicator. When EXTMEM is high, EEDATA/GANGED selects between gang or per-port power over-current detection for the downstream ports. When EXTMEM is low, EEDATA/GANGED acts as a serial data I/O for the EEPROM and is internally pulled down with a 100 $\mu$ A pulldown. This standard TTL input must not change dynamically during operation.                                      |  |  |  |

| EXTMEM                    | 26                | I   | EEPROM read enable. When EXTMEM is high, the serial EEPROM interface of the device is disabled. When EXTMEM is low, terminals 5 and 6 are configured as the clock and data pins of the serial EEPROM interface, respectively.                                                                                                                                                                                                   |  |  |  |

| GND                       | 7, 28             |     | Ground. GND terminals must be tied to ground for proper operation.                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| OVRCUR1 –<br>OVRCUR4      | 10, 14,<br>18, 22 | I   | Over-current inputs. OVRCUR1 – OVRCUR4 are active low, standard TTL inputs. For per-port over current detection, one over-current input is available for each of the four downstream ports. In the ganged mode, any OVRCUR input may be used and all OVRCUR pins should be tied together. OVRCUR pins are active low inputs with noise filtering logic.                                                                         |  |  |  |

| <u>PWRON1</u> –<br>PWRON4 | 9, 13,<br>17, 21  | 0   | Power-on/-off control signals. $\overline{PWRON1} - \overline{PWRON4}$ are active low, push-pull outputs. Push-pull outputs eliminate the pullup resistors which open-drain outputs require. However, the external power switches that connect to these pins must be able to operate with 3.3 V inputs because these outputs cannot drive 5 V signals.                                                                          |  |  |  |

| RESET                     | 4                 | I   | Reset. RESET is an active low TTL input with hysteresis and must be asserted at power up. When RESET is asserted, all logic is initialized.                                                                                                                                                                                                                                                                                     |  |  |  |

| SUSPND                    | 32                | 0   | Suspend status. SUSPND is an active high output available for external logic power down operations. During the suspend mode, SUSPND is high. SUSPND is low for normal operation.                                                                                                                                                                                                                                                |  |  |  |

| MODESLCT                  | 31                | I   | Mode select pin. With a simple RC circuit, this pin ensures the normal operation mode is selected. Refer to application information section for detailed information.                                                                                                                                                                                                                                                           |  |  |  |

| CLKIN                     | 27                | 1   | 48 MHz clock input. Tie this pin to the output of the oscillator.                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| V <sub>CC</sub>           | 3, 25             |     | 3.3-V supply voltage                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| TESTIN                    | 30                | I   | Test input pin. This pin is used as a test input pin during production test. TESTIN must be tied to VCC (3.3 V) for normal operation.                                                                                                                                                                                                                                                                                           |  |  |  |

| TESTOUT                   | 29                | 0   | Test output pin. This pin is used as a test output pin during production test. TESTOUT must be left open during normal operation.                                                                                                                                                                                                                                                                                               |  |  |  |

SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> (see Note 1)                                                 | 0.5 V to 3.6 V                    |

|----------------------------------------------------------------------------------------------------|-----------------------------------|

| Input voltage range, V <sub>1</sub>                                                                | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Output voltage range, VO                                                                           | –0.5 V to V <sub>CC</sub> + 0.5 V |

| Input clamp current, I <sub>IK</sub> , (V <sub>I</sub> < 0 V or V <sub>I</sub> > V <sub>CC</sub> ) | ±20 mA                            |

| Output clamp current, $I_{OK}$ , ( $V_O < 0 V$ or $V_O > V_{CC}$ )                                 | ±20 mA                            |

| Storage temperature range, T <sub>stg</sub>                                                        | –65°C to 150°C                    |

| Operating free-air temperature range, TA                                                           | 0°C to 70°C                       |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage levels are with respect to GND.

#### recommended operating conditions

|                                                             | MIN      | NOM | MAX             | UNIT |

|-------------------------------------------------------------|----------|-----|-----------------|------|

| Supply voltage, V <sub>CC</sub>                             | 3        | 3.3 | 3.6             | V    |

| Input voltage, TTL/LVCMOS, VI                               | 0        | ,   | V <sub>CC</sub> | V    |

| Output voltage, TTL/LVCMOS, VO                              | 0        | ,   | V <sub>CC</sub> | V    |

| High-level input voltage, signal-ended receiver, VIH(REC)   | 2        | ,   | VCC             | V    |

| Low-level input voltage, signal-ended receiver, VIL(REC)    |          |     | 0.8             | V    |

| High-level input voltage, TTL/LVCMOS, VIH(TTL)              | 2        | ,   | VCC             | V    |

| Low-level input voltage, TTL/LVCMOS, VIL(TTL)               | 0        |     | 0.8             | V    |

| Operating free-air temperature, T <sub>A</sub>              | 0        |     | 70              | °C   |

| External series, differential driver resistor, R(DRV)       | 22 (-5%) | 2   | 2 (5%)          | Ω    |

| Operating (dc differential driver) high speed mode, f(OPRH) |          |     | 12              | Mb/s |

| Operating (dc differential driver) low speed mode, f(OPRL)  |          |     | 1.5             | Mb/s |

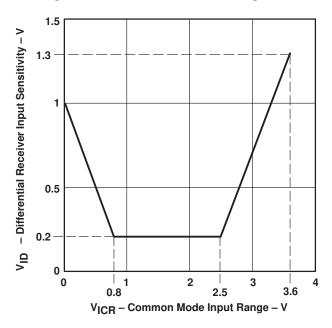

| Common mode, input range, differential receiver, V(ICR)     | 0.8      |     | 2.5             | V    |

| Input transition times, t <sub>t</sub> , TTL/LVCMOS         | 0        |     | 25              | ns   |

| Junction temperature range, TJ                              | 0        |     | 115             | °C   |

SLLS308A – FEBRUARY 1999 – REVISED AUGUST 1999

# electrical characteristics over recommended ranges of operating free-air temperature and supply voltage (unless otherwise noted)

|                     | PARAMETER                                           |                | TEST CONDITIONS                                           | MIN                   | MAX  | UNIT |  |

|---------------------|-----------------------------------------------------|----------------|-----------------------------------------------------------|-----------------------|------|------|--|

|                     |                                                     | TTL/LVCMOS     | I <sub>OH</sub> = -4 mA                                   | V <sub>CC</sub> - 0.5 |      |      |  |

| VOH                 | High-level output voltage                           | USB data lines | $R(DRV) = 15 k\Omega$ , to GND                            | 2.8                   |      | V    |  |

|                     |                                                     | USB data lines | $I_{OH} = -12 \text{ mA} \text{ (without } R_{(DRV)})$    | V <sub>CC</sub> - 0.5 |      |      |  |

|                     |                                                     | TTL/LVCMOS     | I <sub>OL</sub> = 4 mA                                    |                       | 0.5  |      |  |

| VOL                 | Low-level output voltage                            | USB data lines | $R(DRV) = 1.5 \text{ k} \Omega \text{ to } 3.6 \text{ V}$ |                       | 0.3  | V    |  |

|                     |                                                     | USB data lines | $I_{OL} = 12 \text{ mA} \text{ (without } R_{(DRV)})$     |                       | 0.5  |      |  |

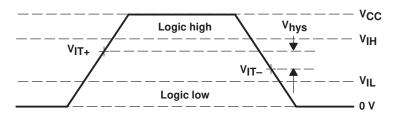

| V. <del></del>      | Positive input threshold voltage                    | TTL/LVCMOS     |                                                           |                       | 1.8  | V    |  |

| VIT+                |                                                     | Single-ended   | $0.8 \text{ V} \le \text{V}_{ICR} \le 2.5 \text{ V}$      |                       | 1.8  |      |  |

| \/. <b>_</b>        | Negative-input threshold voltage                    | TTL/LVCMOS     |                                                           | 0.8                   |      | v    |  |

| V <sub>IT</sub> -   |                                                     | Single-ended   | $0.8 \text{ V} \le \text{V}_{ICR} \le 2.5 \text{ V}$      | 1                     |      |      |  |

|                     | · · · · · + · · · · · · · · · · · · · ·             | TTL/LVCMOS     |                                                           | 0.3                   | 0.7  | V    |  |

| V <sub>hys</sub>    | Input hysteresis <sup>†</sup> ( $V_{T+} - V_{T-}$ ) | Single-ended   | $0.8 \text{ V} \le \text{V}_{ICR} \le 2.5 \text{ V}$      | 300                   | 500  | mV   |  |

| 1                   | Llich impedance output ourrent                      | TTL/LVCMOS     | V = V <sub>CC</sub> or GND‡                               |                       | ±10  | μΑ   |  |

| loz                 | High-impedance output current                       | USB data lines | $0 V \le V_O \le V_{CC}$                                  |                       | ±10  |      |  |

| Ι <sub>Ι</sub>      | Low-level input current                             | TTL/LVCMOS     | VI = GND                                                  |                       | -1   | μA   |  |

| IIН                 | High-level input current                            | TTL/LVCMOS     | VI = VCC                                                  |                       | 1    | μA   |  |

| <sup>z</sup> o(DRV) | Driver output impedance                             | USB data lines | Static V <sub>OH</sub> or V <sub>OL</sub>                 | 7.1                   | 19.9 | Ω    |  |

| VID                 | Differential input voltage                          | USB data lines | $0.8 \text{ V} \le \text{V}_{ICR} \le 2.5 \text{ V}$      | 0.2                   |      | V    |  |

| 1                   |                                                     |                | Normal operation                                          |                       | 40   | mA   |  |

| ICC                 | Input supply current                                |                | Suspend mode                                              |                       | 1    | μA   |  |

<sup>†</sup> Applies for input buffers with hysteresis

‡ Applies for open drain buffers

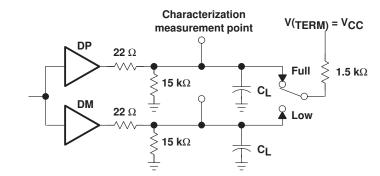

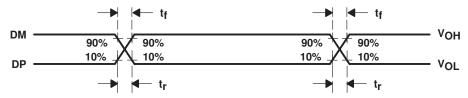

# differential driver switching characteristics over recommended ranges of operating free-air temperature and supply voltage, $C_L = 50 \text{ pF}$ (unless otherwise noted)

#### full speed mode

| PARAMETER                                        |                                   | TEST CONDITIONS            |     | MAX  | UNIT |

|--------------------------------------------------|-----------------------------------|----------------------------|-----|------|------|

| t <sub>r</sub> Transition rise time for DP or DM |                                   | See Figure 1 and Figure 2  | 4   | 20   | ns   |

| t <sub>f</sub> †                                 | Transition fall time for DP or DM | See Figure 1 and Figure 2  | 4   | 20   | ns   |

| <sup>t</sup> (RFM)                               | Rise/fall time matching§          | $(t_{f}/t_{f}) \times 100$ | 90% | 110% |      |

| V <sub>O(CRS)</sub>                              | Signal crossover output voltage§  |                            | 1.3 | 2.0  | V    |

§ Characterized only. Limits are approved by design and are not production tested

#### low speed mode

|                     | PARAMETER                          | TEST CONDITIONS                                    |                           |     | MAX  | UNIT |

|---------------------|------------------------------------|----------------------------------------------------|---------------------------|-----|------|------|

| t <sub>r</sub>      | Transition rise time for DP or DM§ | $C_L = 200 \text{ pF}$ to 600 pF,                  | See Figure 1 and Figure 2 | 75  | 300  | ns   |

| tf                  | Transition fall time for DP or DM§ | $C_L = 200 \text{ pF} \text{ to } 600 \text{ pF},$ | See Figure 1 and Figure 2 | 75  | 300  | ns   |

| <sup>t</sup> (RFM)  | Rise/fall time matching§           | (t <sub>r</sub> /t <sub>f</sub> ) x 100            |                           | 80% | 120% |      |

| V <sub>O(CRS)</sub> | Signal crossover output voltage§   | $C_L = 200 \text{ pF}$ to 600 pF                   |                           | 1.3 | 2.0  | V    |

§ Characterized only. Limits are approved by design and are not production tested

SLLS308A – FEBRUARY 1999 – REVISED AUGUST 1999

Figure 1. Differential Driver Switching Load

NOTE: The  $t_r/t_f$  ratio is measured as  $t_r(DP)/t_f(DM)$  and  $t_r(DM)/t_f(DP)$  at each crossover point.

#### **Figure 2. Differential Driver Timing Waveforms**

Figure 3. Differential Receiver Input Sensitivity vs Common Mode Input Range

Figure 4. Single-Ended Receiver Input Signal Parameter Definitions

## TUSB2043 4-PORT HUB FOR THE UNIVERSAL SERIAL BUS WITH OPTIONAL SERIAL EEPROM INTERFACE SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

**APPLICATION INFORMATION**

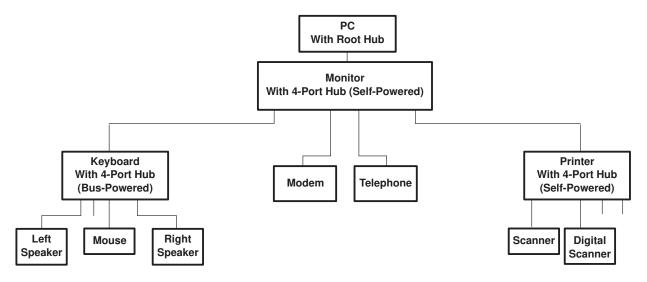

A major advantage of USB is the ability to connect 127 functions configured in up to six logical layers (tiers) to a single personal computer (see Figure 5).

## Figure 5. USB Tiered Configuration Example

Another advantage of USB is that all peripherals are connected using a standardized four-wire cable that provides both communication and power distribution. The power configurations are bus-powered and self-powered modes. The maximum current that may be drawn from the USB 5-V line during power up is 100 mA. For the bus-powered mode, a hub can draw a maximum of 500 mA from the 5-V line of the USB cable. A bus-powered hub must always be connected downstream to a self-powered hub, unless it is the only hub connected to the PC and there are no high-powered functions connected downstream. In the self-powered mode, the hub is connected to an external power supply and can supply up to 500 mA to each downstream port. High-powered functions may draw a maximum of 500 mA from each downstream port and may only be connected downstream to self-powered hubs. Per the USB specification, in the bus-powered mode, each downstream port can provide a maximum of 100 mA of current, and in the self-powered mode, each downstream port can provide a maximum of 500 mA for current.

Both bus-powered and self-powered hubs require over-current protection for all downstream ports. The two types of protection are individual port management (individual port basis) or ganged port management (multiple port basis). Individual port management requires power management devices for each individual downstream port, but adds robustness to the USB system because, in the event of an over-current condition, the USB host only powers down the port that has the condition. The ganged configuration uses fewer power management devices and thus has lower system costs, but in the event of an over-current condition on any of the downstream ports, all the ganged ports are disabled by the USB host.

Using a combination of the BUSPWR and EEDATA/GANGED inputs, the TUSB2043 supports four modes of power management: bus-powered hub with either individual port power management or ganged port power management, and the self-powered hub with either individual port power management or ganged port power management. Texas Instruments supplies the complete hub solution because we offer this TUSB2043, the TUSB2077 (7-port) and the TUSB2140B (4-port with I<sup>2</sup>C) hubs along with the power management chips needed to implement a fully USB Specification 1.1 compliant system.

# **APPLICATION INFORMATION**

## **USB design notes**

The following sections provide block diagram examples of how to implement the TUSB2043 device. Note, even though no resistors are shown, pullup, pulldown, and series resistors must still be used to properly implement this device. Figure 1 shows a few resistors that must be used for the USB lines, and for a general reference design, one is available on the TI USB web site at http://www.ti.com/sc/usb.

Figure 6 is a block diagram example of how to connect the external EEPROM if a custom product ID and vendor ID are desired.

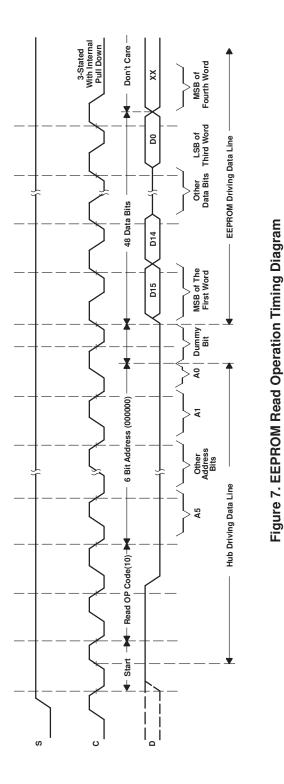

Figure 7 is an example of how to generate the 48-MHz clock signal. Figure 7 shows the EEPROM read operation timing diagram. Figures 8, 9 and 10 illustrate how to connect the TUSB2043 device for different power source and port power management combinations.

Figure 6. Typical Application of the TUSB2043 USB Hub

SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

# **APPLICATION INFORMATION**

#### programming the EEPROM

An SGS Thompson M93C46 EEPROM or equivalent is used for storing the programmable VID and PID. When the EEPROM interface is enabled ( $\overline{\text{EXTMEM}} = 0$ ), the EECLK and EEDATA are internally pulled down (100 µA) inside the TUSB2043. The internal pulldowns are disabled when the EEPROM interface is disabled (EXTMEM = 1).

The EEPROM is programmed with the three 16-bit locations as shown in Table 1. Connecting pin 6 of the EEPROM high (ORG = 1) organizes the EEPROM memory into  $64 \times 16$  bit words.

| ADDRESS | D15                  | D14          | D13 | D12–D8   | D7–D0 |  |

|---------|----------------------|--------------|-----|----------|-------|--|

| 00000   | 0 GANGED 00000 00000 |              |     | 00000000 |       |  |

| 00001   |                      | VID Low-byte |     |          |       |  |

| 00010   | PID High-byte PID L  |              |     |          |       |  |

|         | XXXXXXXX             |              |     |          |       |  |

#### Table 1. EEPROM Memory Map

The D and Q signals of the EEPROM must be tied together using a 1 k $\Omega$  resistor with the common I/O operations forming a single-wire bus. After system power-on reset, the TUSB2043 performs a one-time access read operation from the EEPROM if the EXTMEM pin is pulled low and the chip select(s) of the EEPROM is connected to the system power-on reset. Initially, the EEDATA pin will be driven by the TUSB2043 to send a start bit (1) which is followed by the read instruction (10) and the starting-word address (00000). Once the read instruction is received, the instruction and address are decoded by the EEPROM, which then sends the data to the output shift register. At this point, the hub stops driving the EEDATA pin and the EEPROM starts driving. A dummy (0) bit is then output and the first three 16-bit words in the EEPROM are output with the most significant bit (MSB) first.

The output data changes are triggered by the rising edge of the clock provided by the TUSB2043 on the EECLK pin. The SGS-Thompson M936C46 EEPROM is recommended, because it advances to the next memory location by automatically incrementing the address internally. Any EEPROM used must have the automatic internal address advance function. After reading the three words of data from the EEPROM, the TUSB2043 puts the EEPROM interface into a high-impedance condition (pulled down internally) to allow other logic to share the EEPROM. The EEPROM read operation is summarized in Figure 8. For more details on EEPROM operation, refer to SGS-Thompson Microelectronics M93C46 Serial Microwire Bus EEPROM data sheet.

POST OFFICE BOX 655303 DALLAS, TEXAS 75265

SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

# **APPLICATION INFORMATION**

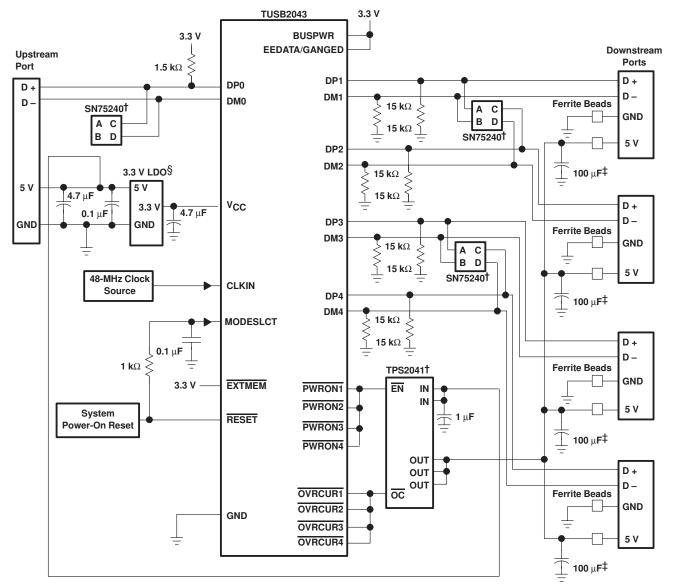

#### bus-powered hub, ganged port power management

When used in bus-powered mode, the TUSB2043 supports up to four downstream ports by controlling a TPS2041 device capable of supplying 100 mA of current to each downstream port. Bus-powered hubs must implement power switching to ensure current demand is held below 100 mA when the hub is hot-plugged into the system. Utliizing the TPS2041 for ganged power management provides over-current protection for the downstream ports. The SN75240 transient suppressors reduce inrush current and voltage spikes on the data lines. The OVRCUR signals should be tied together for a ganged operation.

<sup>†</sup>TPS2041 and SN75240 are Texas Instruments devices.

‡ 120 μF per hub is the minimum required per the USB specification, version 1.1. However, TI recommends a 100 μF low ESR tantulum capacitor per port for immunity to voltage droop.

\$ LDO is a 5 V to 3.3 V voltage regulator

#### Figure 8. TUSB2043 Bus-Powered Hub, Ganged Port Power Management Application

# **APPLICATION INFORMATION**

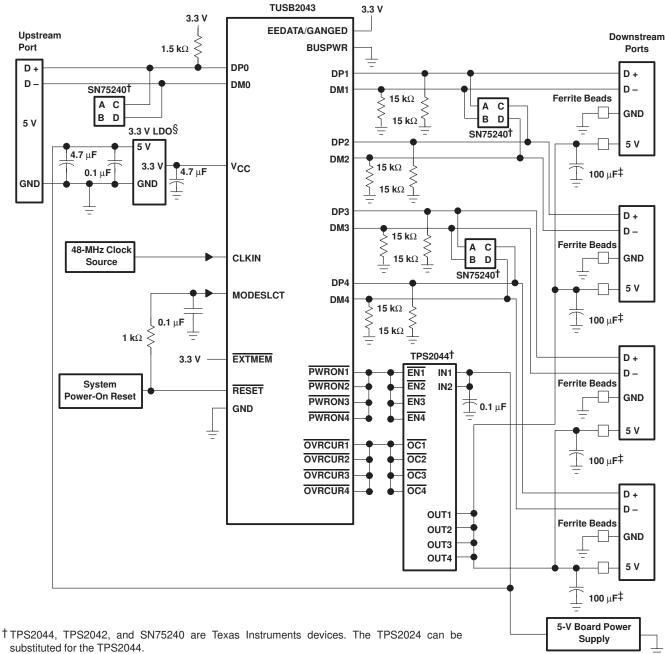

## self-powered hub, ganged port power management

The TUSB2043 can also be implemented for ganged port power management in a self-powered configuration. The implementation is very similar to the bus-powered example with the exception that a self-powered port supplies 500 mA of current to each downstream port. The over-current protection can be provided by a TPS2044 quad device or a TPS2024 single power switch.

<sup>‡</sup> 120 μF per hub is the minimum required per the USB specification, version 1.1. However, TI recommends a 100 μF low ESR tantulum capacitor per port for immunity to voltage droop.

\$ LDO is a 5 V to 3.3 V voltage regulator

#### Figure 9. TUSB2043 Self-Powered Hub, Ganged Port Power Management Application

SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

# **APPLICATION INFORMATION**

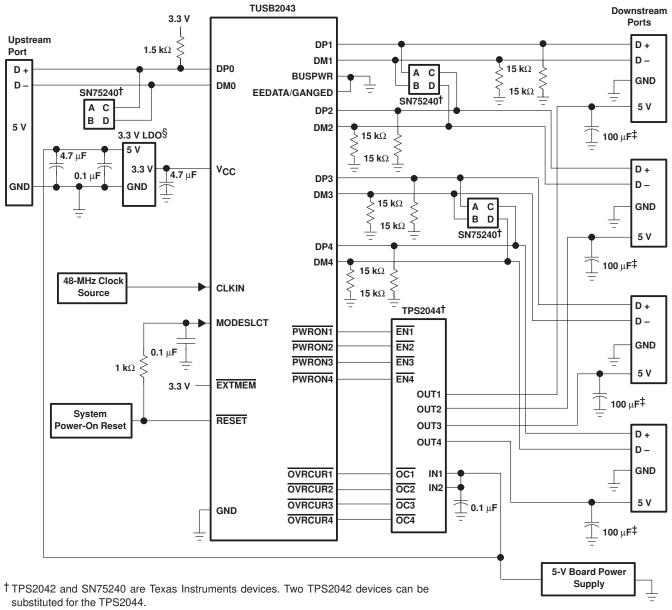

### self-powered hub, individual port power management

In a self-powered configuration, the TUSB2043 can be implemented for individual port-power management when used with the TPS2044 because it is capable of supplying 500 mA of current to each downstream port and can provide current limiting on a per port basis. When the hub detects a fault on a downstream port, power is removed from only the port with the fault and the remaining ports continue to operate normally. Self-powered hubs are required to implement over-current protection and report overcurrent conditions. The SN75240 transient suppressors reduce inrush current and voltage spikes on the data lines.

<sup>‡</sup>120 μF per hub is the minimum required per the USB specification, version 1.1. However, TI recommends a 100 μF low ESR tantulum capacitor per port for immunity to voltage droop.

\$ LDO is a 5 V to 3.3 V voltage regulator

#### Figure 10. TUSB2043 Self-Powered Hub, Individual Port-Power Management Application

SLLS308A - FEBRUARY 1999 - REVISED AUGUST 1999

## **MECHANICAL DATA**

## VF (S-PQFP-G32)

#### PLASTIC QUAD FLATPACK

NOTES: A. All linear dimensions are in millimeters.

B. This drawing is subject to change without notice.

C. Falls within JEDEC MS-026

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated