SBOS061B - FEBRUARY 1997 - REVISED AUGUST 2004

# 4-20mA CURRENT TRANSMITTER with Sensor Excitation and Linearization

## **FEATURES**

- LOW UNADJUSTED ERROR

- TWO PRECISION CURRENT SOURCES: 800µA each

- LINEARIZATION

- 2- OR 3-WIRE RTD OPERATION

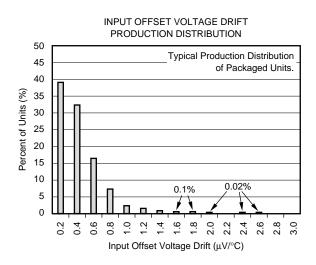

- LOW OFFSET DRIFT: 0.4μV/°C

- LOW OUTPUT CURRENT NOISE: 30nApp

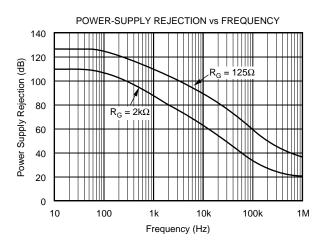

- HIGH PSR: 110dB minimum HIGH CMR: 86dB minimum

- WIDE SUPPLY RANGE: 7.5V to 36V

- DIP-14 AND SO-14 PACKAGES

## DESCRIPTION

The XTR105 is a monolithic 4-20mA, 2-wire current transmitter with two precision current sources. It provides complete current excitation for platinum RTD temperature sensors and bridges, instrumentation amplifiers, and current output circuitry on a single integrated circuit.

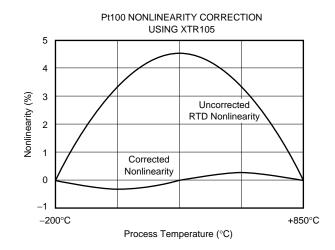

Versatile linearization circuitry provides a 2nd-order correction to the RTD, typically achieving a 40:1 improvement in linearity.

Instrumentation amplifier gain can be configured for a wide range of temperature or pressure measurements. Total unadjusted error of the complete current transmitter is low enough to permit use without adjustment in many applications. This includes zero output current drift, span drift, and nonlinearity. The XTR105 operates on loop power-supply voltages down to 7.5V.

The XTR105 is available in DIP-14 and SO-14 surfacemount packages and is specified for the -40°C to +85°C industrial temperature range.

## **APPLICATIONS**

- INDUSTRIAL PROCESS CONTROL

- **FACTORY AUTOMATION**

- SCADA REMOTE DATA ACQUISITION

- REMOTE TEMPERATURE AND PRESSURE **TRANSDUCERS**

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

#### **ABSOLUTE MAXIMUM RATINGS(1)**

| Power Supply, V+ (referenced to the I <sub>O</sub> pin)              |

|----------------------------------------------------------------------|

| Input Voltage, $V_{IN+}$ , $V_{IN-}$ (referenced to the $I_{O}$ pin) |

| Storage Temperature Range55°C to +125°C                              |

| Lead Temperature (soldering, 10s)+300°C                              |

| Output Current Limit                                                 |

| Junction Temperature+165°C                                           |

|                                                                      |

NOTE: (1) Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION(1)

| PRODUCT | PACKAGE-LEAD        | PACKAGE<br>DESIGNATOR | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA, QUANTITY |

|---------|---------------------|-----------------------|-----------------------------------|--------------------|--------------------|------------------------------|

| XTR105  | DIP-14              | N                     | -40°C to +85°C                    | XTR105PA           | XTR105PA           | Rails, 25                    |

| "       | II .                | "                     | "                                 | XTR105P            | XTR105P            | Rails, 25                    |

| XTR105  | SO-14 Surface-Mount | D                     | -40°C to +85°C                    | XTR105UA           | XTR105UA           | Rails, 58                    |

| "       | II .                | "                     | "                                 | XTR105UA           | XTR105UA/2K5       | Tape and Reel, 2500          |

| XTR105  | SO-14 Surface-Mount | D                     | -40°C to +85°C                    | XTR105U            | XTR105U            | Rails, 58                    |

| "       | "                   | "                     | "                                 | XTR105U            | XTR105U/2K5        | Tape and Reel, 2500          |

NOTE: (1) For the most current package and ordering information, see the Package Option Addendum located at the end of this data sheet.

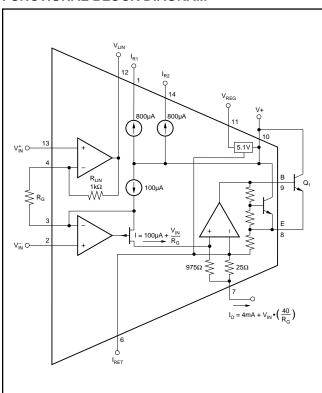

#### **FUNCTIONAL BLOCK DIAGRAM**

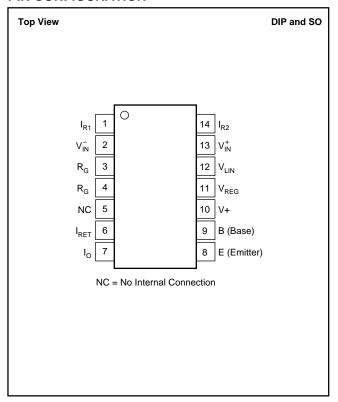

#### **PIN CONFIGURATION**

# **ELECTRICAL CHARACTERISTICS**

At  $T_A$  = +25°C, V+ = 24V, and TIP29C external transistor, unless otherwise noted.

|                                                                                                                                                                                            |                                                                                   |                           | XTR105P, U                                                                           |                                             |             | ΓR105PA, <sup>↓</sup>                   | UA                                   |                                                                                        |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|---------------------------|--------------------------------------------------------------------------------------|---------------------------------------------|-------------|-----------------------------------------|--------------------------------------|----------------------------------------------------------------------------------------|--|

| PARAMETER                                                                                                                                                                                  | CONDITIONS                                                                        | MIN                       | TYP                                                                                  | MAX                                         | MIN         | TYP                                     | MAX                                  | UNITS                                                                                  |  |

| OUTPUT Output Current Equation Output Current, Specified Range Over-Scale Limit Under-Scale Limit                                                                                          | I <sub>REG</sub> = 0V                                                             | I <sub>o</sub> = 4 24 1.8 | V <sub>IN</sub> • (40/R <sub>G</sub> )                                               | ) + 4mA, V <sub>II</sub><br>20<br>30<br>2.6 | in Volts, F | R <sub>G</sub> in Ω  * *                | *<br>*<br>*                          | A<br>mA<br>mA<br>mA                                                                    |  |

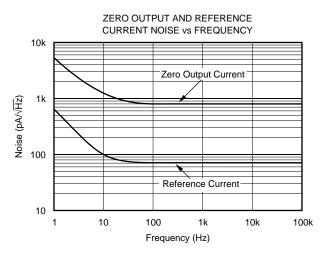

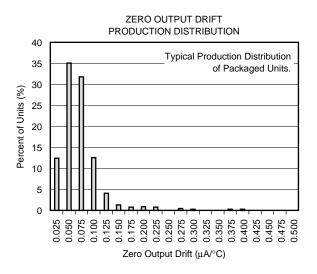

| ZERO OUTPUT <sup>(1)</sup> Initial Error vs Temperature vs Supply Voltage, V+ vs Common-Mode Voltage vs V <sub>REG</sub> Output Current Noise, 0.1Hz to 10Hz                               | $V_{IN} = 0V$ , $R_G = \infty$<br>V + = 7.5V to $36VV_{CM} = 1.25V to 3.5V^{(2)}$ |                           | 4<br>±5<br>±0.07<br>0.04<br>0.02<br>0.3<br>0.03                                      | ±25<br>±0.5<br>0.2                          |             | * * * * * *                             | ±50<br>±0.9<br>*                     | mA<br>μΑ<br>μΑ/°C<br>μΑ/V<br>μΑ/V<br>μΑ/mA<br>μΑ <sub>PP</sub>                         |  |

| SPAN Span Equation (transconductance) Initial Error <sup>(3)</sup> vs Temperature <sup>(3)</sup> Nonlinearity, Ideal Input <sup>(4)</sup>                                                  | Full-Scale ( $V_{IN}$ ) = 50mV<br>Full-Scale ( $V_{IN}$ ) = 50mV                  |                           | S = 40/R <sub>G</sub><br>±0.05<br>±3<br>0.003                                        | ±0.2<br>±25<br>0.01                         |             | *<br>*<br>*                             | ±0.4<br>*<br>*                       | A/V<br>%<br>ppm/°C<br>%                                                                |  |

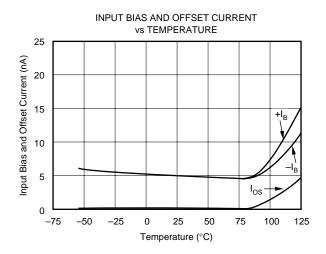

| INPUT <sup>(5)</sup> Offset Voltage vs Temperature vs Supply Voltage, V+ vs Common-Mode Voltage, RTI (CMRR) Common-Mode Input Range <sup>(2)</sup> Input Bias Current vs Temperature       | $V_{CM} = 2V$ $V+ = 7.5V \text{ to } 36V$ $V_{CM} = 1.25V \text{ to } 3.5V^{(2)}$ | 1.25                      | ±50<br>±0.4<br>±0.3<br>±10                                                           | ±100<br>±1.5<br>±3<br>±50<br>3.5<br>25      | *           | * * * * * * * * * * * * * * * * * * * * | ±250<br>±3<br>*<br>±100<br>*         | μV<br>μV/°C<br>μV/V<br>μV/V<br>V<br>nA<br>pA/°C                                        |  |

| Input Offset Current vs Temperature Impedance, Differential Common-Mode Noise, 0.1Hz to 10Hz  CURRENT SOURCES                                                                              | V <sub>O</sub> = 2V <sup>(6)</sup>                                                |                           | ±0.2<br>5<br>0.1    1<br>5    10<br>0.6                                              | ±3                                          |             | * * * * *                               | ±10                                  | nA<br>pA/°C<br>GΩ    pF<br>GΩ    pF<br>μV <sub>PP</sub>                                |  |

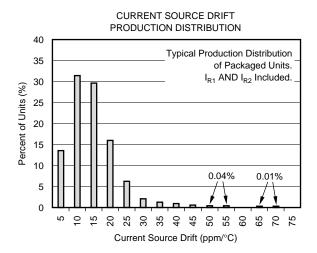

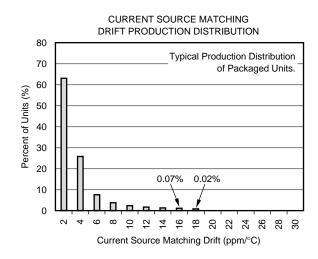

| Current Accuracy vs Temperature vs Power Supply, V+ Matching vs Temperature vs Power Supply, V+ Compliance Voltage, Positive Negative <sup>(2)</sup> Output Impedance Noise, 0.1Hz to 10Hz | $V_0 = 2 V_0$ $V_1 = 7.5 V \text{ to } 36 V$ $V_2 = 7.5 V \text{ to } 36 V$       | (V+) - 3<br>0             | 800<br>±0.05<br>±15<br>±10<br>±0.02<br>±3<br>1<br>(V+) - 2.5<br>-0.2<br>150<br>0.003 | ±0.2<br>±35<br>±25<br>±0.1<br>±15<br>10     | * *         | ****                                    | ±0.4<br>±75<br>*<br>±0.2<br>±30<br>* | μΑ<br>%<br>ppm/°C<br>ppm/V<br>%<br>ppm/°C<br>ppm/V<br>V<br>V<br>MΩ<br>μΑ <sub>PP</sub> |  |

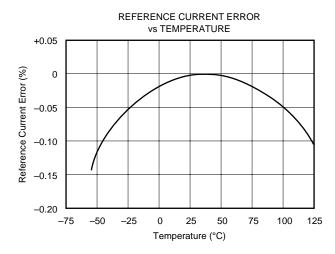

| V <sub>REG</sub> <sup>(2)</sup> Accuracy vs Temperature vs Supply Voltage, V+ Output Current Output Impedance                                                                              |                                                                                   |                           | 5.1<br>±0.02<br>±0.2<br>1<br>±1<br>75                                                | ±0.1                                        |             | * * * * *                               | *                                    | V<br>V<br>mV/°C<br>mV/V<br>mA                                                          |  |

| LINEARIZATION R <sub>LIN</sub> (internal) Accuracy vs Temperature                                                                                                                          |                                                                                   |                           | 1<br>±0.2<br>±25                                                                     | ±0.5<br>±100                                |             | *<br>*<br>*                             | ±1<br>*                              | kΩ<br>%<br>ppm/°C                                                                      |  |

| POWER SUPPLY<br>Specified<br>Voltage Range                                                                                                                                                 |                                                                                   | +7.5                      | +24                                                                                  | +36                                         | *           | *                                       | *                                    | V<br>V                                                                                 |  |

| TEMPERATURE RANGE Specification, $T_{MIN}$ to $T_{MAX}$ Operating Storage Thermal Resistance, $\theta_{JA}$                                                                                |                                                                                   | -40<br>-55<br>-55         |                                                                                      | +85<br>+125<br>+125                         | *<br>*<br>* |                                         | *<br>*<br>*                          | °C<br>°C<br>°C                                                                         |  |

| DIP-14 SO-14 Surface-Mount                                                                                                                                                                 |                                                                                   |                           | 80<br>100                                                                            |                                             |             | *                                       |                                      | °C/W                                                                                   |  |

<sup>\*</sup> Specification same as XTR105P and XTR105U.

NOTES: (1) Describes accuracy of the 4mA low-scale offset current. Does not include input amplifier effects. Can be trimmed to zero.

- (2) Voltage measured with respect to  $I_{RET}$  pin.

- (3) Does not include initial error or TCR of gain-setting resistor, R<sub>G</sub>.

- (4) Increasing the full-scale input range improves nonlinearity.

- (5) Does not include Zero Output initial error.

- (6) Current source output voltage with respect to  $I_{RET}$  pin.

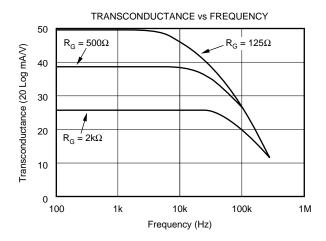

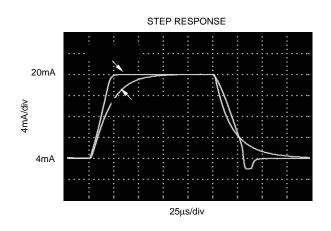

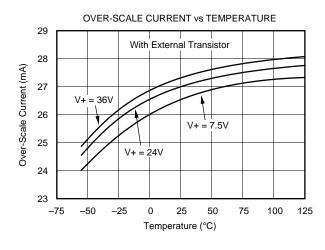

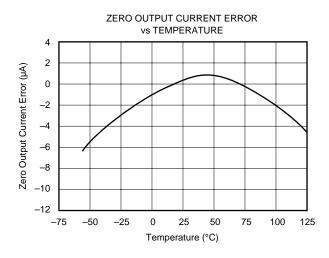

# TYPICAL CHARACTERISTICS

At  $T_A = +25$ °C and V+ = 24V, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25$ °C and V+ = 24V, unless otherwise noted.

# **TYPICAL CHARACTERISTICS (Cont.)**

At  $T_A = +25$ °C and V+ = 24V, unless otherwise noted.

### APPLICATION INFORMATION

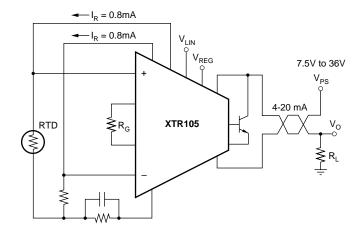

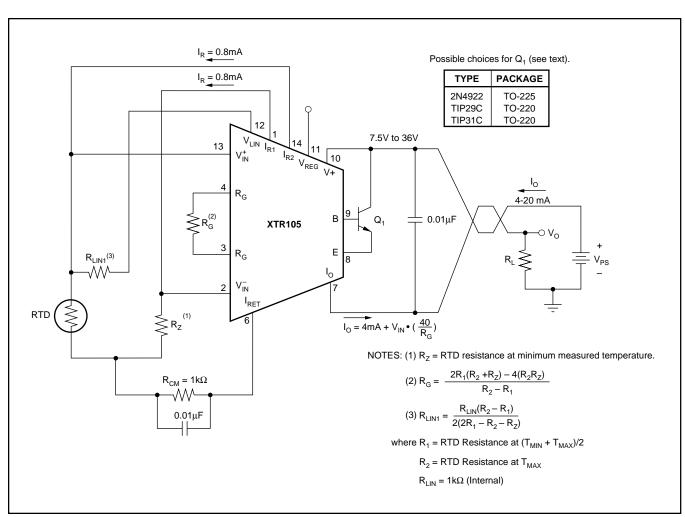

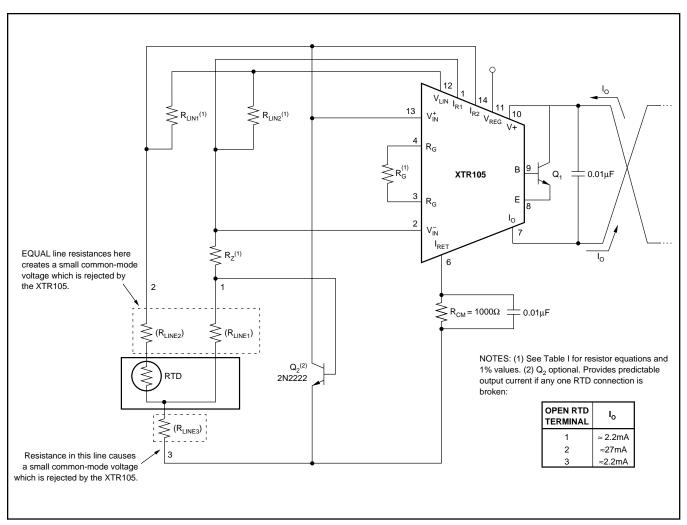

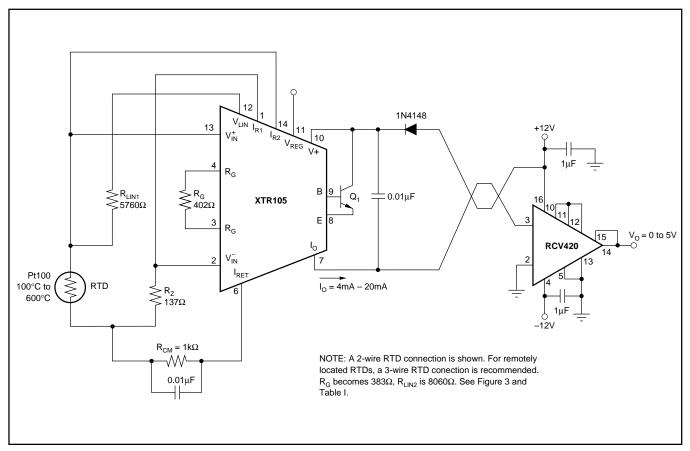

Figure 1 shows the basic connection diagram for the XTR105. The loop power supply,  $V_{PS}$ , provides power for all circuitry. Output loop current is measured as a voltage across the series load resistor,  $R_{\rm I}$ .

Two matched 0.8mA current sources drive the RTD and zero-setting resistor,  $R_{Z}.$  The instrumentation amplifier input of the XTR105 measures the voltage difference between the RTD and  $R_{Z}.$  The value of  $R_{Z}$  is chosen to be equal to the resistance of the RTD at the low-scale (minimum) measurement temperature.  $R_{Z}$  can be adjusted to achieve 4mA output at the minimum measurement temperature to correct for input offset voltage and reference current mismatch of the XTR105.

$R_{CM}$  provides an additional voltage drop to bias the inputs of the XTR105 within their common-mode input range.  $R_{CM}$  should be bypassed with a  $0.01\mu F$  capacitor to minimize common-mode noise. Resistor  $R_G$  sets the gain of the instrumentation amplifier according to the desired temperature range.  $R_{LIN1}$  provides 2nd-order linearization correction to the RTD, typically achieving a 40:1 improvement in linearity. An additional resistor is required for 3-wire RTD connections (see Figure 3).

The transfer function through the complete instrumentation amplifier and voltage-to-current converter is:

$$I_O = 4mA + V_{IN} \cdot (40/R_G)$$

( $V_{IN}$  in volts,  $R_G$  in ohms)

where V<sub>IN</sub> is the differential input voltage.

As evident from the transfer function, if no  $R_{\rm G}$  is used the gain is zero and the output is simply the XTR105's zero current. The value of  $R_{\rm G}$  varies slightly for 2-wire RTD and 3-wire RTD connections with linearization.  $R_{\rm G}$  can be calculated from the equations given in Figure 1 (2-wire RTD connection) and Table I (3-wire RTD connection).

The  $I_{RET}$  pin is the return path for all current from the current sources and  $V_{REG}$ . The  $I_{RET}$  pin allows any current used in external circuitry to be sensed by the XTR105 and to be included in the output current without causing an error.

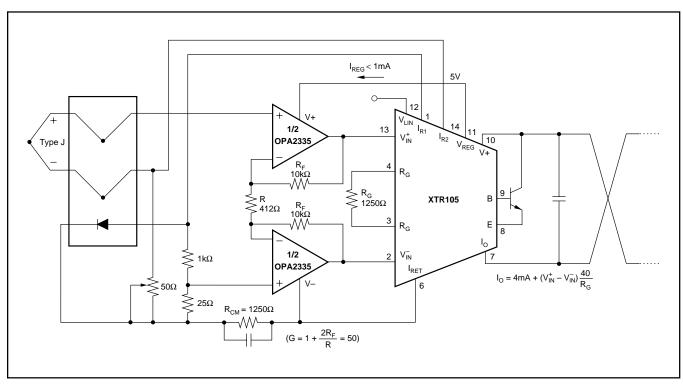

The  $V_{REG}$  pin provides an on-chip voltage source of approximately 5.1V and is suitable for powering external input circuitry (refer to Figure 6). It is a moderately accurate voltage reference—it is not the same reference used to set the  $800\mu A$  current references.  $V_{REG}$  is capable of sourcing approximately 1mA of current. Exceeding 1mA may affect the 4mA zero output.

FIGURE 1. Basic 2-Wire RTD Temperature Measurement Circuit with Linearization.

#### MEASUREMENT TEMPERATURE SPAN $\Delta T$ (°C)

600°C

18 7/511

4750

7150

60.4/487

7500 100/475

4870

7150

137/453

4750

6810

174/442 4530 6490

700°C

18 7/590

4020

6420

60.4/562

100/549

4020

6340

137/536

3920

6040

800°C

18 7/665

3480

5900

60.4/649

3570

100/634

3480

5620

900°C

18 7/750

3090

5360

60.4/732

R<sub>Z</sub>/R<sub>G</sub> R<sub>LIN1</sub>

R<sub>LIN2</sub>

1000°C

18 7/845

2740

4990

|                  |                             |                            | WILAGOI                    | KEINIEINI II              | INFERAIC                 |

|------------------|-----------------------------|----------------------------|----------------------------|---------------------------|--------------------------|

| T <sub>MIN</sub> | 100°C                       | 200°C                      | 300°C                      | 400°C                     | 500°C                    |

| –200°C           | 18.7/86.6<br>15000<br>16500 | 18.7/169<br>9760<br>11500  | 18.7/255<br>8060<br>10000  | 18.7/340<br>6650<br>8870  | 18.7/422<br>5620<br>7870 |

| -100°C           | 60.4/80.6<br>27400<br>29400 | 60.4/162<br>15400<br>17800 | 60.4/243<br>10500<br>13000 | 60.4/324<br>7870<br>10200 | 60.4/402<br>6040<br>8660 |

| 0°C              | 100/78.7<br>33200<br>35700  | 100/158<br>16200<br>18700  | 100/237<br>10500<br>13000  | 100/316<br>7680<br>10000  | 100/392<br>6040<br>8250  |

| 100°C            | 137/75<br>31600<br>34000    | 137/150<br>15400<br>17800  | 137/226<br>10200<br>12400  | 137/301<br>7500<br>9760   | 137/383<br>5760<br>8060  |

| 200°C            | 174/73.2<br>30900<br>33200  | 174/147<br>15000<br>17400  | 174/221<br>9760<br>12100   | 174/294<br>7150<br>9310   | 174/365<br>5620<br>7680  |

| 300°C            | 210/71.5<br>30100<br>32400  | 210/143<br>14700<br>16500  | 210/215<br>9530<br>11500   | 210/287<br>6980<br>8870   | 210/357<br>5360<br>7320  |

| 400°C            | 249/68.1<br>28700<br>30900  | 249/137<br>14000<br>16200  | 249/205<br>9090<br>11000   | 249/274<br>6650<br>8450   |                          |

| 500°C            | 280/66.5<br>28000<br>30100  | 280/133<br>13700<br>15400  | 280/200<br>8870<br>10500   |                           |                          |

| 600°C            | 316/64.9<br>26700<br>28700  | 313/130<br>13000<br>14700  |                            |                           |                          |

| 700°C            | 348/61.9<br>26100<br>27400  |                            | -                          |                           |                          |

| 800°C            | 374/60.4<br>24900<br>26700  |                            |                            |                           |                          |

NOTE: The values listed in this table are 1% resistors (in  $\Omega$ ). Exact values may be calculated from the following equa-

$R_7 = RTD$  resistance at minimum measured temperature.

$$R_G = \frac{2(R_2 - R_Z)(R_1 - R_Z)}{(R_2 - R_1)}$$

$$R_{LIN1} = \frac{R_{LIN}(R_2 - R_1)}{2(2R_1 - R_2 - R_2)}$$

$$R_{LIN2} = \frac{(R_{LIN} + R_G)(R_2 - R_1)}{2(2R_1 - R_2 - R_7)}$$

where:  $R_1 = RTD$  resistance at  $(T_{MIN} + T_{MAX})/2$

$R_2 = RTD$  resistance at  $T_{MAX}$

$R_{LIN} = 1k\Omega$  (Internal)

#### **EXAMPLE:**

The measurement range is -100°C to +200°C for a 3-wire Pt100 RTD connection. Determine the values for R<sub>S</sub>, R<sub>G</sub>, R<sub>LIN1</sub>, and R<sub>LIN2</sub>. Look up the values from the chart or calculate the values according to the equations provided.

#### **METHOD 1: TABLE LOOK UP**

For  $T_{MIN} = -100^{\circ}C$  and  $\Delta T = -300^{\circ}C$ , the 1% values are:

$R_Z = 60.4\Omega$  $R_{LIN1} = 10.5k\Omega$

$R_G = 243\Omega$  $R_{LIN2} = 13k\Omega$

#### **METHOD 2: CALCULATION**

Step 1: Determine R<sub>Z</sub>, R<sub>1</sub>, and R<sub>2</sub>.

$R_Z$  is the RTD resistance at the minimum measured temperature,  $T_{MIN} = -100$  °C. Using Equation 1 at right gives  $R_Z = 60.25\Omega$  (1% value is  $60.4\Omega$ ).

$R_2$  is the RTD resistance at the maximum measured temperature,  $T_{MAX}$  = 200°C. Using Equation 2 at right gives  $R_2 = 175.84\Omega$ .

R<sub>1</sub> is the RTD resistance at the midpoint measured temperature,

$T_{MID} = (T_{MIN} + T_{MAX})/2 = 50$ °C.  $R_1$  is NOT the average of  $R_7$  and  $R_2$ . Using Equation 2 at right gives  $R_1 = 119.40\Omega$ .

Step 2: Calculate  $R_G$ ,  $R_{LIN1}$ , and  $R_{LIN2}$  using equations above.

$R_G = 242.3\Omega$  (1% value is 243 $\Omega$ )

$R_{LIN1} = 10.413k\Omega$  (1% value is  $10.5k\Omega$ )

$R_{LIN2} = 12.936k\Omega$  (1% value is  $13k\Omega$ )

#### Calculation of Pt100 Resistance Values

(according to DIN IEC 751)

(Equation 1) Temperature range from -200°C to 0°C:  $R_{(T)} = 100 [1 + 3.90802 \cdot 10^{-3} \cdot T - 0.5802 \cdot 10^{-6} \cdot$  $T^2 - 4.27350 \cdot 10^{-12} (T - 100) T^3$

(Equation 2) Temperature range from 0°C to +850°C:  $R_{(T)} = 100 (1 + 3.90802 \cdot 10^{-3} \cdot T - 0.5802 \cdot 10^{-6} \cdot T_2)$

where:  $R_{(T)}$  is the resistance in  $\Omega$  at temperature T. T is the temperature in °C.

NOTE: Most RTD manufacturers provide reference tables for resistance values at various temperatures.

TABLE I. R<sub>z</sub>, R<sub>G</sub>, R<sub>LIN1</sub>, and R<sub>LIN2</sub> Standard 1% Resistor Values for 3-Wire Pt100 RTD Connection with Linearization.

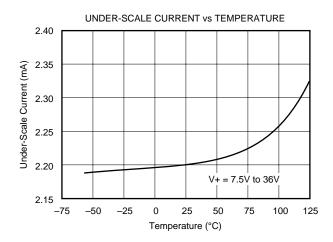

A negative input voltage,  $V_{\text{IN}}$ , will cause the output current to be less than 4mA. Increasingly negative V<sub>IN</sub> will cause the output current to limit at approximately 2.2mA. Refer to the typical characteristic Under-Scale Current vs Temperature.

Increasingly positive input voltage (greater than the full-scale input) will produce increasing output current according to the transfer function, up to the output current limit of approximately 27mA. Refer to the typical characteristic Over-Scale Current vs Temperature.

#### **EXTERNAL TRANSISTOR**

Transistor  $Q_1$  conducts the majority of the signal-dependent 4-20mA loop current. Using an external transistor isolates the majority of the power dissipation from the precision input and reference circuitry of the XTR105, maintaining excellent accuracy.

Since the external transistor is inside a feedback loop, its characteristics are not critical. Requirements are:  $V_{CEO} = 45V$  min,  $\beta = 40$  min, and  $P_D = 800$ mW. Power dissipation requirements may be lower if the loop power-supply voltage is less than 36V. Some possible choices for  $Q_1$  are listed in Figure 1.

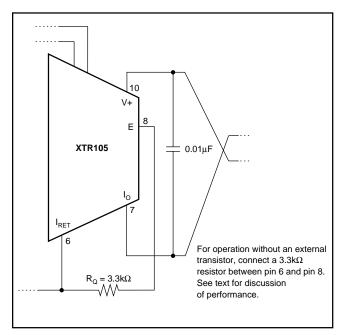

The XTR105 can be operated without this external transistor, however, accuracy will be somewhat degraded due to the internal power dissipation. Operation without  $Q_1$  is not recommended for extended temperature ranges. A resistor (R = 3.3k $\Omega$ ) connected between the I<sub>RET</sub> pin and the E (emitter) pin may be needed for operation below 0°C without  $Q_1$  to ensure the full 20mA full-scale output, especially with V+ near 7.5V.

FIGURE 2. Operation Without an External Transistor.

#### **LOOP POWER SUPPLY**

XTR105

SBOS061B

The voltage applied to the XTR105, V+, is measured with respect to the  $I_{\rm O}$  connection, pin 7. V+ can range from 7.5V to 36V. The loop-supply voltage, V<sub>PS</sub>, will differ from the voltage applied to the XTR105 according to the voltage drop on the current sensing resistor,  $R_{\rm L}$  (plus any other voltage drop in the line).

If a low loop-supply voltage is used,  $R_L$  (including the loop wiring resistance) must be made a relatively low value to assure that V+ remains 7.5V or greater for the maximum loop current of 20mA:

$$R_L max = \left(\frac{(V+) - 7.5V}{20mA}\right) - R_{WIRING}$$

It is recommended to design for V+ equal or greater than 7.5V with loop currents up to 30mA to allow for out-of-range input conditions.

The low operating voltage (7.5V) of the XTR105 allows operation directly from personal computer power supplies (12V  $\pm$ 5%). When used with the RCV420 current loop receiver (see Figure 7), the load resistor voltage drop is limited to 3V.

#### **ADJUSTING INITIAL ERRORS**

Many applications require adjustment of initial errors. Input offset and reference current mismatch errors can be corrected by adjustment of the zero resistor,  $R_Z$ . Adjusting the gain-setting resistor,  $R_G$ , corrects any errors associated with gain.

#### 2- AND 3-WIRE RTD CONNECTIONS

In Figure 1, the RTD can be located remotely simply by extending the two connections to the RTD. With this remote 2-wire connection to the RTD, line resistance will introduce error. This error can be partially corrected by adjusting the values of  $R_Z$ ,  $R_G$ , and  $R_{LIN1}$ .

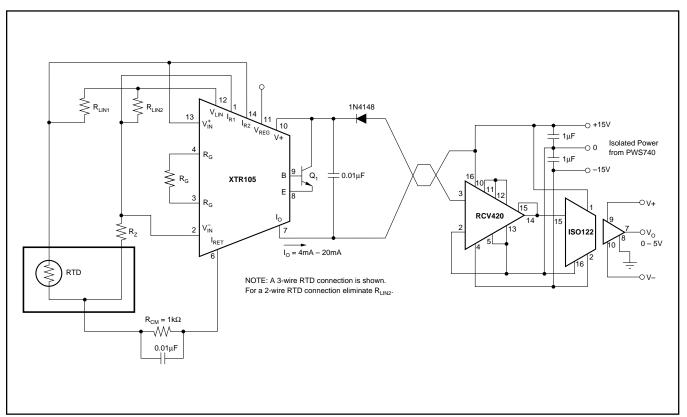

A better method for remotely located RTDs is the 3-wire RTD connection (see Figure 3). This circuit offers improved accuracy.  $R_{\rm Z}$ 's current is routed through a third wire to the RTD. Assuming line resistance is equal in RTD lines 1 and 2, this produces a small common-mode voltage that is rejected by the XTR105. A second resistor,  $R_{\rm LIN2}$ , is required for linearization.

Note that although the 2-wire and 3-wire RTD connection circuits are very similar, the gain-setting resistor,  $R_{\text{G}}$ , has slightly different equations:

2-wire:

$$R_G = \frac{2R_1(R_2 + R_Z) - 4(R_2R_Z)}{R_2 - R_1}$$

3-wire:

$$R_G = \frac{2(R_2 - R_Z)(R_1 - R_Z)}{R_2 - R_1}$$

where:  $R_Z$  = RTD resistance at  $T_{MIN}$

$R_1 = RTD$  resistance at  $(T_{MIN} + T_{MAX})/2$

$R_2$  = RTD resistance at  $T_{MAX}$

To maintain good accuracy, at least 1% (or better) resistors should be used for  $R_{\text{G}}.$  Table I provides standard 1%  $R_{\text{G}}$  resistor values for a 3-wire Pt100 RTD connection with linearization.

#### LINEARIZATION

RTD temperature sensors are inherently (but predictably) nonlinear. With the addition of one or two external resistors,  $R_{LIN1}$  and  $R_{LIN2}$ , it is possible to compensate for most of this nonlinearity resulting in 40:1 improvement in linearity over the uncompensated output.

See Figure 1 for a typical 2-wire RTD application with linearization. Resistor  $R_{\text{LIN1}}$  provides positive feedback and controls linearity correction.  $R_{\text{LIN1}}$  is chosen according to the desired temperature range. An equation is given in Figure 1.

In 3-wire RTD connections, an additional resistor,  $R_{LIN2}$ , is required. As with the 2-wire RTD application,  $R_{LIN1}$  provides positive feedback for linearization.  $R_{LIN2}$  provides an offset canceling current to compensate for wiring resistance encountered in remotely located RTDs.  $R_{LIN1}$  and  $R_{LIN2}$  are chosen such that their currents are equal. This makes the voltage drop in the wiring resistance to the RTD a common-mode signal that is rejected by the XTR105. The nearest standard 1% resistor values for  $R_{LIN1}$  and  $R_{LIN2}$  should be adequate for most applications. Table I provides the 1% resistor values for a 3-wire Pt100 RTD connection.

If no linearity correction is desired, the  $V_{LIN}$  pin should be left open. With no linearization,  $R_G = 2500 \cdot V_{FS}$ , where  $V_{FS} = \text{full-scale}$  input range.

#### **RTDs**

The text and figures thus far have assumed a Pt100 RTD. With higher resistance RTDs, the temperature range and input voltage variation should be evaluated to ensure proper common-mode biasing of the inputs. As mentioned earlier,  $R_{CM}$  can be adjusted to provide an additional voltage drop to bias the inputs of the XTR105 within their common-mode input range.

#### **ERROR ANALYSIS**

See Table II for how to calculate the effect various error sources have on circuit accuracy. A sample error calculation for a typical RTD measurement circuit (Pt100 RTD, 200°C measurement span) is provided. The results reveal the XTR105's excellent accuracy, in this case 1.1% unadjusted. Adjusting resistors  $R_{\rm G}$  and  $R_{\rm Z}$  for gain and offset errors improves circuit accuracy to 0.32%. Note that these are worst-case errors; ensured maximum values were used in the calculations and all errors were assumed to be positive (additive). The XTR105 achieves performance that is difficult to obtain with discrete circuitry and requires less space.

#### **OPEN-CIRCUIT PROTECTION**

The optional transistor  $Q_2$  in Figure 3 provides predictable behavior with open-circuit RTD connections. It assures that if any one of the three RTD connections is broken, the XTR105's output current will go to either its high current limit ( $\approx$  27mA) or low current limit ( $\approx$  2.2mA). This is easily detected as an out-of-range condition.

FIGURE 3. Remotely Located RTDs with 3-Wire Connection.

### **SAMPLE ERROR CALCULATION**

RTD value at 4mA Output ( $R_{RTD \, MIN}$ ): 100 $\Omega$  RTD Measurement Range: 200°C Ambient Temperature Range ( $\Delta T_A$ ): 5V Common-Mode Voltage Change ( $\Delta CM$ ): 0.1V

|                                                 |                                                                                                             | SAMPLE                                                                |             | ROR<br>Full Scale) |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------|--------------------|

| ERROR SOURCE                                    | ERROR EQUATION                                                                                              | ERROR CALCULATION(1)                                                  | UNADJ.      | ADJUST.            |

| INPUT                                           |                                                                                                             |                                                                       |             |                    |

| Input Offset Voltage                            | V <sub>OS</sub> /(V <sub>IN MAX</sub> ) • 10 <sup>6</sup>                                                   | 100μV/(800μA • 0.38Ω/°C • 200°C) • 10 <sup>6</sup>                    | 1645        | 0                  |

| vs Common-Mode                                  | CMRR • ΔCM/(V <sub>IN MAX</sub> ) • 10 <sup>6</sup>                                                         | 50μV/V • 0.1V/(800μA • 0.38Ω/°C • 200°C) • 10 <sup>6</sup>            | 82          | 82                 |

| Input Bias Current                              | I <sub>B</sub> /I <sub>REF</sub> • 10 <sup>6</sup>                                                          | 0.025μA/800μA • 10 <sup>6</sup>                                       | 31          | 0                  |

| Input Offset Current                            | I <sub>OS</sub> • R <sub>RTD MIN</sub> /(V <sub>IN MAX</sub> ) • 10 <sup>6</sup>                            | 3nA • 100Ω/(800μA • 0.38Ω/°C • 200°C) • 10 <sup>6</sup>               | 5           | 0                  |

|                                                 |                                                                                                             | Total Input Error:                                                    | 1763        | 82                 |

| EXCITATION                                      |                                                                                                             |                                                                       |             |                    |

| Current Reference Accuracy                      | I <sub>REF</sub> Accuracy (%)/100% • 10 <sup>6</sup>                                                        | 0.2%/100% • 10 <sup>6</sup>                                           | 2000        | 0                  |

| vs Supply                                       | (I <sub>REF</sub> vs V+) • ΔV+                                                                              | 25ppm/V • 5V                                                          | 125         | 125                |

| Current Reference Matching                      | I <sub>REF</sub> Matching (%)/100% • 800μA •                                                                | 0.1%/100% • 800μA • 100Ω/(800μA • 0.38Ω/°C • 200°C) • 10 <sup>6</sup> | 1316        | 0                  |

| vs Supply                                       | R <sub>RTD MIN</sub> /(V <sub>IN MAX</sub> ) • 10 <sup>6</sup><br>(I <sub>REF</sub> Matching vs V+) • ∆V+ • | 10ppm/V • 5V • 800μA • 100Ω/(800μA • 0.38Ω/°C • 200°C)                | 66          | 66                 |

|                                                 | R <sub>RTD MIN</sub> /(V <sub>IN MAX</sub> )                                                                | Total Excitation Error:                                               | 3507        | 191                |

| GAIN                                            |                                                                                                             | Total Excitation Error.                                               | 3307        | 191                |

| Span                                            | Span Error (%)/100% • 10 <sup>6</sup>                                                                       | 0.2%/100% • 10 <sup>6</sup>                                           | 2000        | 0                  |

| Nonlinearity                                    | Nonlinearity (%)/100% • 10 <sup>6</sup>                                                                     | 0.01%/100% • 106                                                      | 100         | 100                |

| . to timiloumly                                 | 110111111100111111111111111111111111111                                                                     | Total Gain Error:                                                     | 2100        | 100                |

| OUTPUT                                          |                                                                                                             |                                                                       |             |                    |

| Zero Output                                     | (I <sub>ZERO</sub> – 4mA) /16000μA • 10 <sup>6</sup>                                                        | 25μΑ/16000μΑ • 10 <sup>6</sup>                                        | 1563        | 0                  |

| vs Supply                                       | (I <sub>ZERO</sub> vs V+) • ΔV+/16000μA • 10 <sup>6</sup>                                                   | 0.2μΑ/V • 5V/16000μΑ • 10 <sup>6</sup>                                | 63          | 63                 |

|                                                 |                                                                                                             | Total Output Error:                                                   | 1626        | 63                 |

| DRIFT ( $\Delta T_A = 20^{\circ}C$ )            | - 4 4                                                                                                       |                                                                       |             |                    |

| Input Offset Voltage                            | Drift • ∆T <sub>A</sub> /(V <sub>IN MAX</sub> ) • 10 <sup>6</sup>                                           | 1.5μV/°C • 20°C/(800μA • 0.38Ω/°C • 200°C) • 10 <sup>6</sup>          | 493         | 493                |

| Input Bias Current (typical)                    | Drift • ΔT <sub>A</sub> /800μA • 10 <sup>6</sup>                                                            | 20pA/°C • 20°C/800μA • 10 <sup>6</sup>                                | 0.5         | 0.5                |

| Input Offset Current (typical)                  | Drift • ΔT <sub>A</sub> • R <sub>RTD MIN</sub> /(V <sub>IN MAX</sub> ) • 10 <sup>6</sup>                    | 5pA/°C • 20°C • 100W/(800μA • 0.38Ω/°C • 200°C) • 106                 | 0.2         | 0.2                |

| Current Reference Accuracy                      | Drift • $\Delta T_A$                                                                                        | 35ppm/°C • 20°C                                                       | 700         | 700                |

| Current Reference Matching                      | Drift • ΔT <sub>A</sub> • 800μA • R <sub>RTD MIN</sub> /(V <sub>IN MAX</sub> )                              | 15ppm/°C • 20°C • 800μA • 100Ω/(800μA • 0.38Ω/°C • 200°C)             | 395         | 395                |

| Span<br>Zara Output                             | Drift • ΔT <sub>A</sub>                                                                                     | 25ppm/°C • 20°C                                                       | 500         | 500                |

| Zero Output                                     | Drift • ΔT <sub>A</sub> /16000μA • 10 <sup>6</sup>                                                          | 0.5μΑ/°C • 20°C/16000μΑ • 10 <sup>6</sup>                             | 626         | 626                |

| NOISE (0.4H= 40.40H= 4:)                        |                                                                                                             | Total Drift Error:                                                    | 2715        | 2715               |

| NOISE (0.1Hz to 10Hz, typ) Input Offset Voltage | v <sub>n</sub> /(V <sub>IN MAX</sub> ) • 10 <sup>6</sup>                                                    | 0.6μV/(800μA • 0.38Ω/°C • 200°C) • 10 <sup>6</sup>                    | 10          | 10                 |

| Current Reference                               | I <sub>REF</sub> Noise • R <sub>RTD MIN</sub> /(V <sub>IN MAX</sub> ) • 10 <sup>6</sup>                     | 3nA • 100Ω/(800μA • 0.38Ω/°C • 200°C) • 10 <sup>6</sup>               | 5           | 5                  |

| Zero Output                                     | I <sub>ZERO</sub> Noise/16000μA • 10 <sup>6</sup>                                                           | 0.03μΑ/16000μΑ • 106                                                  | 2           | 2                  |

| 2010 Calput                                     | 1 <sub>2ERO</sub> 110000μ (* 10                                                                             | Total Noise Error:                                                    | 17          | 17                 |

|                                                 |                                                                                                             | Total Holde Ellot.                                                    | <del></del> |                    |

NOTE (1): All errors are min/max and referred to input unless otherwise stated.

TOTAL ERROR: 11728 3168 (1.17%) (0.32%)

TABLE II. Error Calculation.

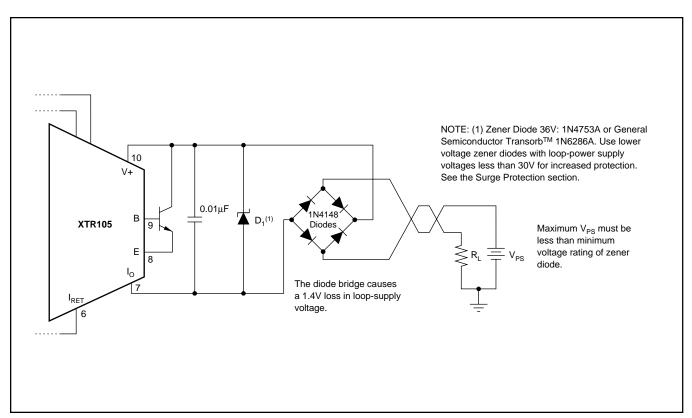

#### REVERSE-VOLTAGE PROTECTION

The XTR105's low compliance rating (7.5V) permits the use of various voltage protection methods without compromising operating range. Figure 4 shows a diode bridge circuit that allows normal operation even when the voltage connection lines are reversed. The bridge causes a two diode drop (approximately 1.4V) loss in loop-supply voltage. This results in a compliance voltage of approximately 9V—satisfactory for most applications. If a 1.4V drop in loop supply is too much, a diode can be inserted in series with the loop-supply voltage and the V+ pin. This protects against reverse output connection lines with only a 0.7V loss in loop-supply voltage.

#### SURGE PROTECTION

Remote connections to current transmitters can sometimes be subjected to voltage surges. It is prudent to limit the maximum surge voltage applied to the XTR105 to as low as practical. Various zener diodes and surge clamping diodes are specially designed for this purpose. Select a clamp diode with as low a voltage rating as possible for best protection. For example, a 36V protection diode will assure proper transmitter operation at normal loop voltages, yet will provide an appropriate level of protection against voltage surges. Characterization tests on three production lots showed no damage to the XTR105 within loop-supply voltages up to 65V.

Most surge protection zener diodes have a diode characteristic in the forward direction that will conduct excessive current, possibly damaging receiving-side circuitry if the loop connections are reversed. If a surge protection diode is used, a series diode or diode bridge should be used for protection against reversed connections.

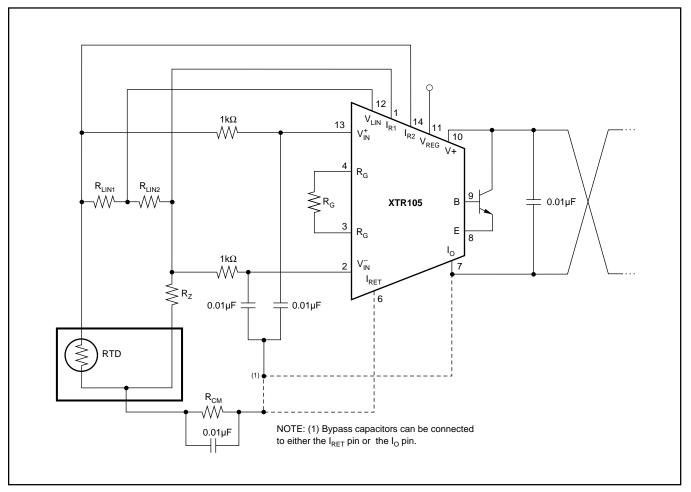

#### RADIO FREQUENCY INTERFERENCE

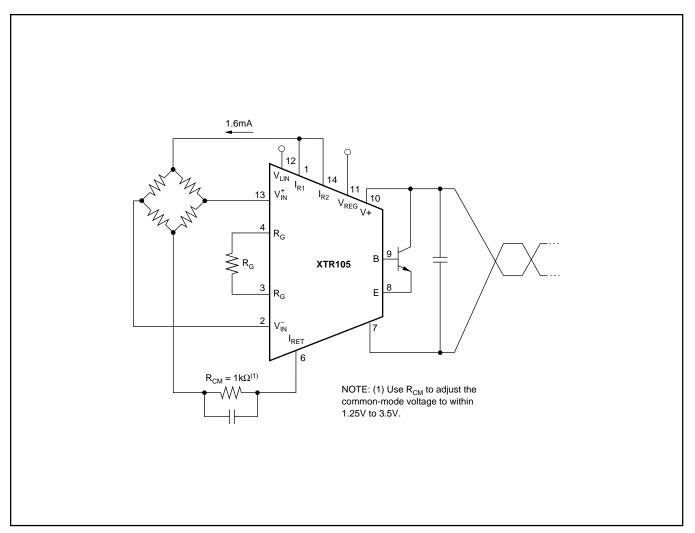

The long wire lengths of current loops invite radio frequency (RF) interference. RF can be rectified by the sensitive input circuitry of the XTR105 causing errors. This generally appears as an unstable output current that varies with the position of loop supply or input wiring.

If the RTD sensor is remotely located, the interference may enter at the input terminals. For integrated transmitter assemblies with short connections to the sensor, the interference more likely comes from the current loop connections.

Bypass capacitors on the input reduce or eliminate this input interference. Connect these bypass capacitors to the  $I_{RET}$  terminal (see Figure 5). Although the dc voltage at the  $I_{RET}$  terminal is not equal to 0V (at the loop supply,  $V_{PS}$ ), this circuit point can be considered the transmitter's "ground." The  $0.01\mu F$  capacitor connected between V+ and  $I_O$  may help minimize output interference.

FIGURE 4. Reverse Voltage Operation and Over-Voltage Surge Protection.

FIGURE 5. Input Bypassing Technique with Linearization.

FIGURE 6. Thermocouple Low Offset, Low Drift Loop Measurement with Diode Cold Junction Compensation.

FIGURE 7. ±12V Powered Transmitter/Receiver Loop.

FIGURE 8. Isolated Transmitter/Receiver Loop.

FIGURE 9. Bridge Input, Current Excitation.

www.ti.com 14-Sep-2023

#### PACKAGING INFORMATION

| Orderable Device | Status  | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| XTR105P          | LIFEBUY | PDIP         | N                  | 14   | 25             | RoHS & Green | Call TI                       | N / A for Pkg Type  | -40 to 85    | XTR105P<br>A            |         |

| XTR105PA         | LIFEBUY | PDIP         | N                  | 14   | 25             | RoHS & Green | Call TI                       | N / A for Pkg Type  | -40 to 85    | XTR105P<br>A            |         |

| XTR105U          | LIFEBUY | SOIC         | D                  | 14   | 50             | RoHS & Green | Call TI                       | Level-3-260C-168 HR | -40 to 85    | XTR105U                 |         |

| XTR105UA         | LIFEBUY | SOIC         | D                  | 14   | 50             | RoHS & Green | Call TI                       | Level-3-260C-168 HR | -40 to 85    | XTR105U<br>A            |         |

| XTR105UA/2K5     | ACTIVE  | SOIC         | D                  | 14   | 2500           | RoHS & Green | NIPDAU                        | Level-3-260C-168 HR | -40 to 85    | XTR105U<br>A            | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

## **PACKAGE OPTION ADDENDUM**

www.ti.com 14-Sep-2023

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

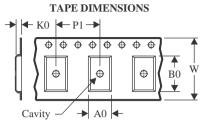

### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

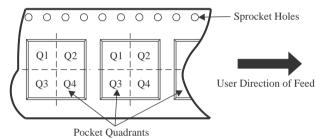

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       |      | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| XTR105UA/2K5 | SOIC | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

**PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

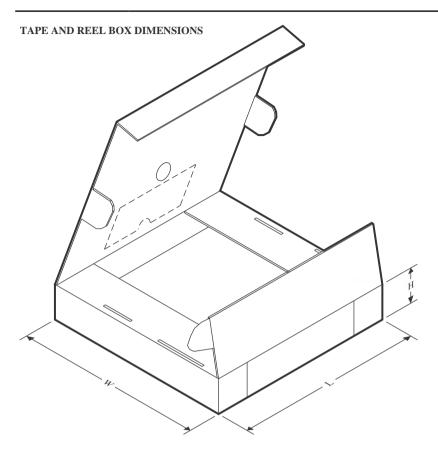

#### \*All dimensions are nominal

| Ì | Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|---|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| ı | XTR105UA/2K5 | SOIC         | D               | 14   | 2500 | 356.0       | 356.0      | 35.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 3-Jun-2022

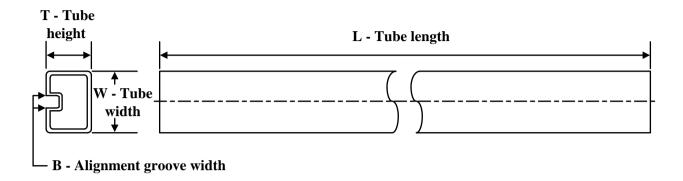

### **TUBE**

\*All dimensions are nominal

| Device   | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|----------|--------------|--------------|------|-----|--------|--------|--------|--------|

| XTR105P  | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230  | 4.32   |

| XTR105PA | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230  | 4.32   |

| XTR105U  | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

| XTR105UA | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

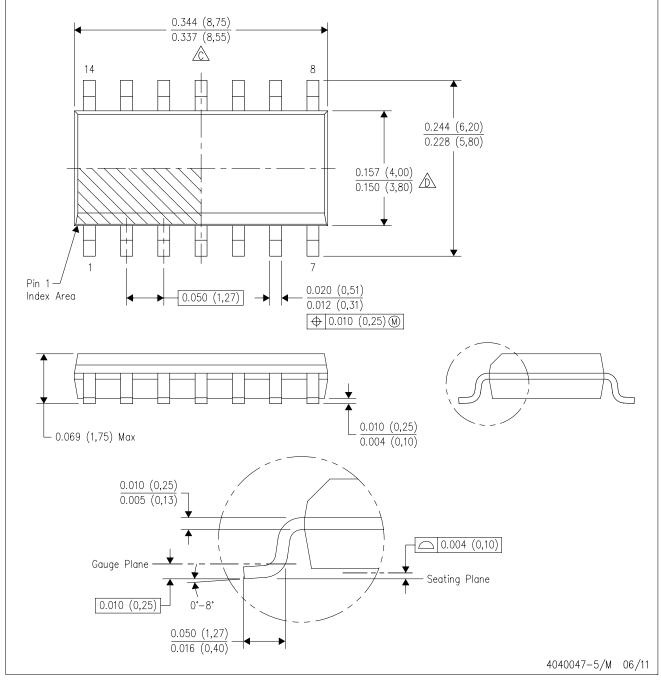

# D (R-PDSO-G14)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AB.

# D (R-PDSO-G14)

# PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

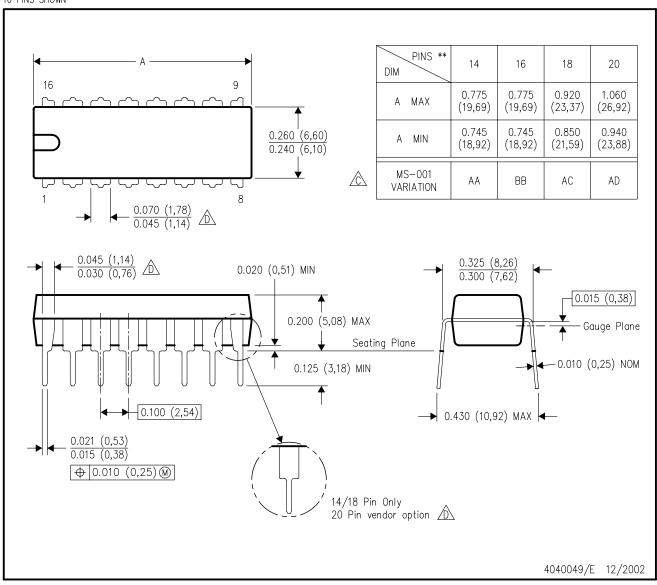

# N (R-PDIP-T\*\*)

## PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- The 20 pin end lead shoulder width is a vendor option, either half or full width.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated