March 1999

NM25C020 2K-Bit Serial CMOS EEPROM

Serial Periphrial Interface (SPI) Synchronous

Bus

# NM25C020 2K-Bit Serial CMOS EEPROM (Serial Peripheral Interface (SPI) Synchronous Bus)

## **General Description**

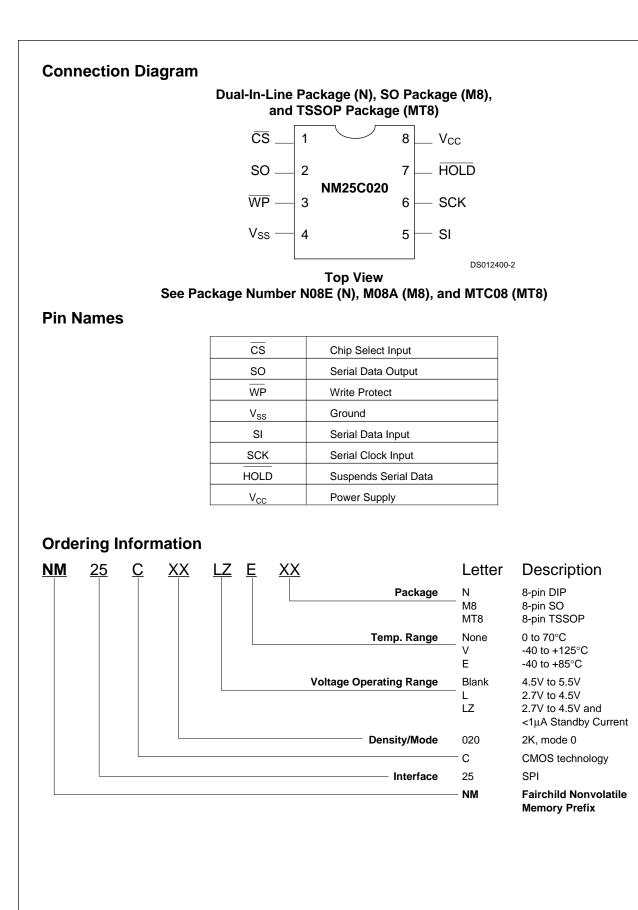

The NM25C020 is a 2048-bit CMOS EEPROM with an SPI compatible serial interface. The NM25C020 is designed for data storage in applications requiring both non-volatile memory and insystem data updates. This EEPROM is well suited for applications using the 68HC11 series of microcontrollers that support the SPI interface for high speed communication with peripheral devices via a serial bus to reduce pin count. The NM25C020 is implemented in Fairchild Semiconductor's floating gate CMOS process that provides superior endurance and data retention.

The serial data transmission of this device requires four signal lines to control the device operation: Chip Select ( $\overline{CS}$ ), Clock (SCK), Data In (SI), and Serial Data Out (SO). All programming cycles are completely self-timed and do not require an erase before WRITE.

BLOCK WRITE protection is provided by programming the STA-TUS REGISTER with one of four levels of write protection. Additionally, separate WRITE enable and WRITE disable instructions are provided for data protection.

Hardware data protection is provided by the WP pin to protect against inadvertent programming. The HOLD pin allows the serial communication to be suspended without resetting the serial sequence.

#### Features

- 2.1 MHz clock rate @ 2.7V to 5.5V

- 2048 bits organized as 256 x 8

- Multiple chips on the same 3-wire bus with separate chip select lines

- Self-timed programming cycle

- Simultaneous programming of 1 to 4 bytes at a time

- Status register can be polled during programming to monitor READY/BUSY

- Write Protect (WP) pin and write disable instruction for both hardware and software write protection

- Block write protect feature to protect against accidental writes

- Endurance: 1,000,000 data changes

- Data retention greater than 40 years

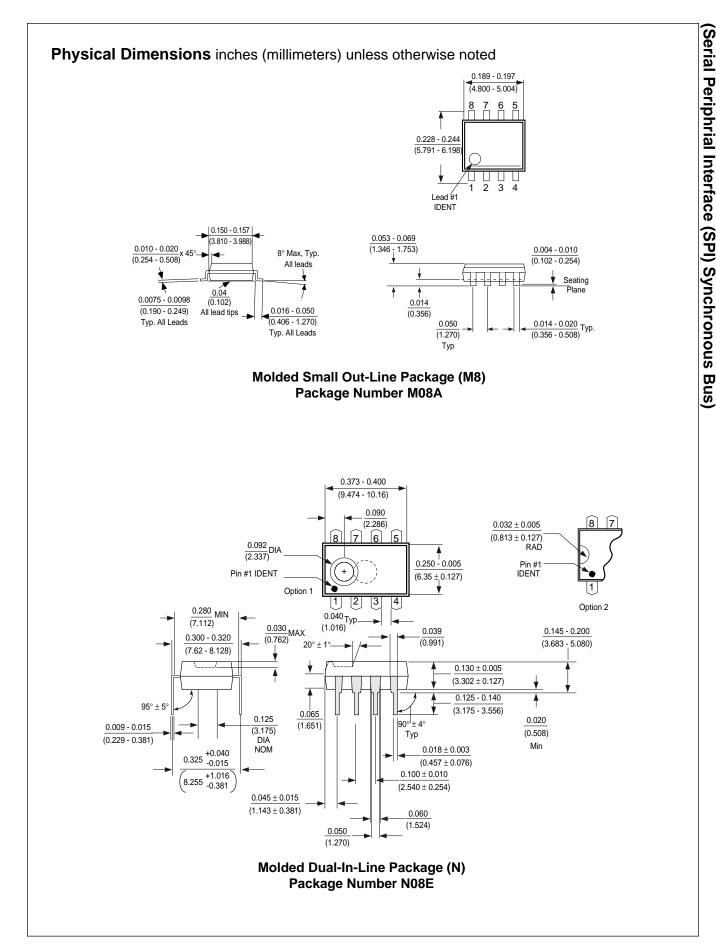

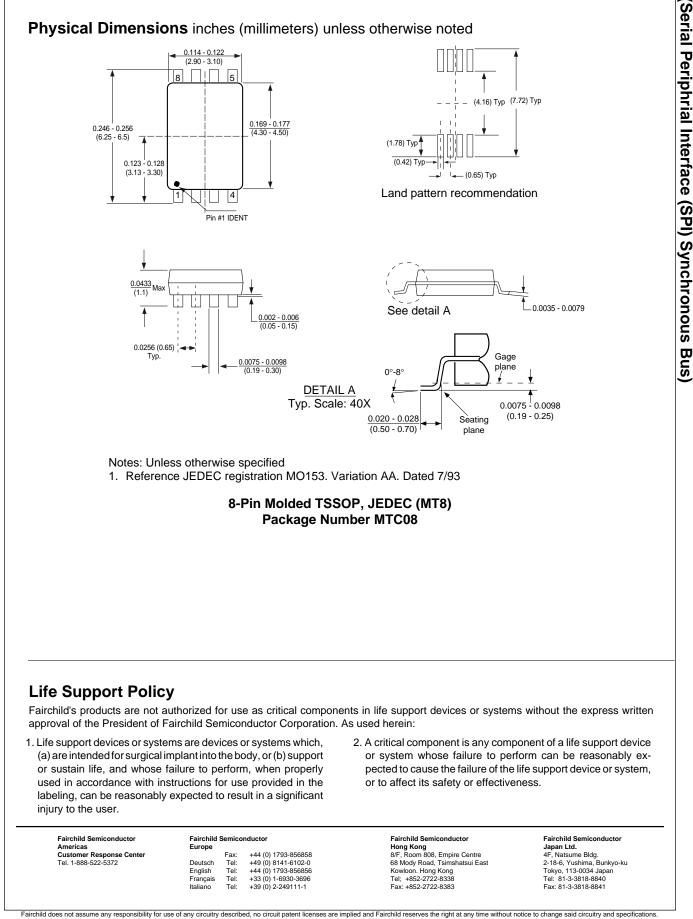

- Packages available: 8-pin DIP, 8-pin SO, or 8-pin TSSOP

#### Block Diagram CS Vcc Instruction HOLD Vss Decoder SCK Control Logic WF and Clock Instruction SI Register Generators Program Address High Voltage Enable Counter/ Generator Register and Program VPP Timer EEPROM Array Decoder 2048 Bits 1 of 256 (256 x 8) Read/Write Amps Data In/Out Register Data Out so 8 Bits Buffer Non-Volatile Status Register DS012400-1

# Standard Voltage $4.5 \le V_{CC} \le 5.5V$ Specifications

## Absolute Maximum Ratings (Note 1)

| Ambient Storage Temperature                           | -65°C to +150°C |

|-------------------------------------------------------|-----------------|

| All Input or Output Voltage with<br>Respect to Ground | +6.5V to -0.3V  |

| Lead Temp. (Soldering, 10 sec.)                       | +300°C          |

| ESD Rating                                            | 2000V           |

## **Operating Conditions**

| Ambient Operating Temperature   |                 |

|---------------------------------|-----------------|

| NM25C020                        | 0°C to +70°C    |

| NM25C020E                       | -40°C to +85°C  |

| NM25C020V                       | -40°C to +125°C |

| Power Supply (V <sub>CC</sub> ) | 4.5V to 5.5V    |

## DC and AC Electrical Characteristics $4.5V \le V_{CC} \le 5.5V$ (unless otherwise specified)

| Symbol            | Parameter               | Conditions                         | Min                   | Max                   | Units |

|-------------------|-------------------------|------------------------------------|-----------------------|-----------------------|-------|

| I <sub>CC</sub>   | Operating Current       | $\overline{CS} = V_{IL}$           |                       | 3                     | mA    |

| I <sub>CCSB</sub> | Standby Current         | $\overline{CS} = V_{CC}$           |                       | 50                    | μA    |

| I <sub>IL</sub>   | Input Leakage           | $V_{IN} = 0$ to $V_{CC}$           | -1                    | +1                    | μΑ    |

| I <sub>OL</sub>   | Output Leakage          | $V_{OUT} = GND \text{ to } V_{CC}$ | -1                    | +1                    | μA    |

| V <sub>IL</sub>   | CMOS Input Low Voltage  |                                    | -0.3                  | V <sub>CC</sub> * 0.3 | V     |

| V <sub>IH</sub>   | CMOS Input High Voltage |                                    | 0.7 * V <sub>CC</sub> | V <sub>CC</sub> + 0.3 | V     |

| V <sub>OL</sub>   | Output Low Voltage      | I <sub>OL</sub> = 1.6 mA           |                       | 0.4                   | V     |

| V <sub>OH</sub>   | Output High Voltage     | I <sub>OH</sub> = -0.8 mA          | V <sub>CC</sub> - 0.8 |                       | V     |

| f <sub>OP</sub>   | SCK Frequency           |                                    |                       | 2.1                   | MHz   |

| t <sub>RI</sub>   | Input Rise Time         |                                    |                       | 2.0                   | μs    |

| t <sub>FI</sub>   | Input Fall Time         |                                    |                       | 2.0                   | μs    |

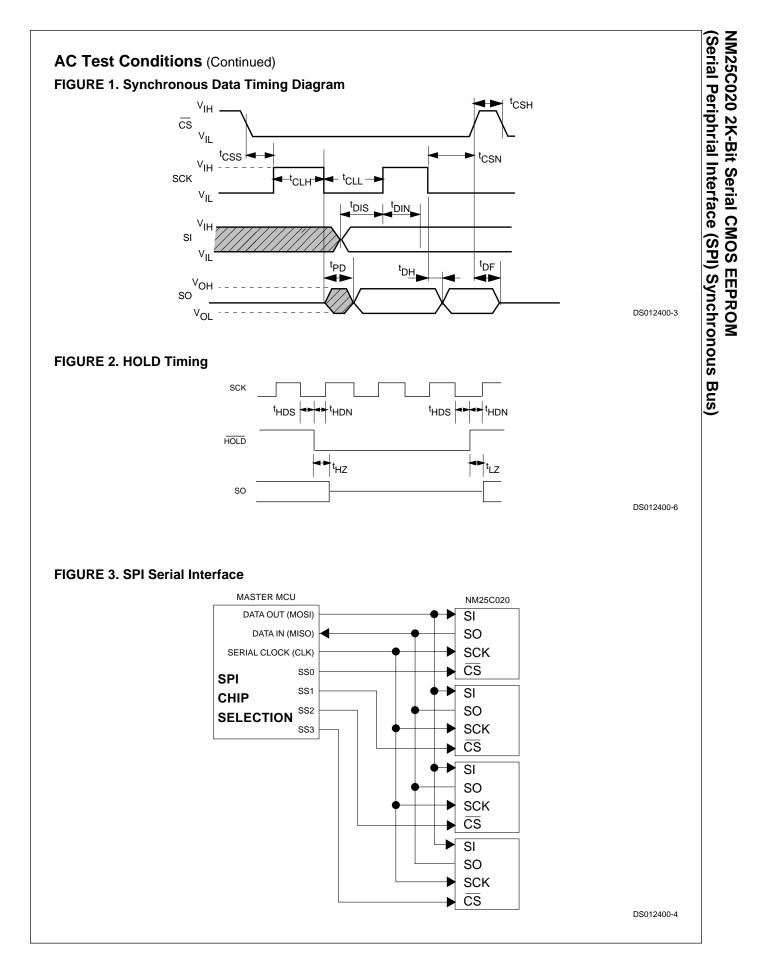

| t <sub>CLH</sub>  | Clock High Time         | (Note 2)                           | 190                   |                       | ns    |

| t <sub>CLL</sub>  | Clock Low Time          | (Note 2)                           | 190                   |                       | ns    |

| t <sub>CSH</sub>  | Min CS High Time        | (Note 3)                           | 240                   |                       | ns    |

| t <sub>CSS</sub>  | CS Setup Time           |                                    | 240                   |                       | ns    |

| t <sub>DIS</sub>  | Data Setup Time         |                                    | 100                   |                       | ns    |

| t <sub>HDS</sub>  | HOLD Setup Time         |                                    | 90                    |                       | ns    |

| t <sub>CSN</sub>  | CS Hold Time            |                                    | 240                   |                       | ns    |

| t <sub>DIN</sub>  | Data Hold Time          |                                    | 100                   |                       | ns    |

| t <sub>HDN</sub>  | HOLD Hold Time          |                                    | 90                    |                       | ns    |

| t <sub>PD</sub>   | Output Delay            | C <sub>L</sub> = 200 pF            |                       | 240                   | ns    |

| t <sub>DH</sub>   | Output Hold Time        |                                    | 0                     |                       | ns    |

| t <sub>LZ</sub>   | HOLD to Output Low Z    |                                    |                       | 100                   | ns    |

| t <sub>DF</sub>   | Output Disable Time     | C <sub>L</sub> = 200 pF            |                       | 240                   | ns    |

| t <sub>HZ</sub>   | HOLD to Output High Z   |                                    |                       | 100                   | ns    |

| t <sub>WP</sub>   | Write Cycle Time        | 1–4 Bytes                          |                       | 10                    | ms    |

## **Capacitance** $T_A = 25^{\circ}C$ , f = 2.1/1 MHz (Note 4)

| Symbol           | Test               | Тур | Max | Units |

|------------------|--------------------|-----|-----|-------|

| C <sub>OUT</sub> | Output Capacitance | 3   | 8   | pF    |

| C <sub>IN</sub>  | Input Capacitance  |     | 6   | pF    |

## **AC Test Conditions**

| Output Load                        | C <sub>L</sub> = 200 pF                    |

|------------------------------------|--------------------------------------------|

| Input Pulse Levels                 | 0.1 * $V_{CC}$ – 0.9 * $V_{CC}$            |

| Timing Measurement Reference Level | 0.3 * V <sub>CC</sub> 07 * V <sub>CC</sub> |

Note 1: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: The  $f_{OP}$  frequency specification specifies a minimum clock period of  $1/f_{OP}$ . Therefore, for every  $f_{OP}$  clock cycle,  $t_{CLH} + t_{CLL}$  must be equal to or greater than  $1/f_{OP}$ . For example, if the 2.1MHz period = 476ns and  $t_{CLH} = 190ns$ ,  $t_{CLL}$  must be 286ns.

Note 3: CS must be brought high for a minimum of t<sub>CSH</sub> between consecutive instruction cycles.

Note 4: This parameter is periodically sampled and not 100% tested.

0°C to +70°C -40°C to +85°C -40°C to +125°C 2.7V–4.5V

## Low Voltage 2.7V $\leq$ V\_{CC} $\leq$ 4.5V Specifications

Absolute Maximum Ratings (Note 5)

| Ambient Storage Temperature      | -65°C to +150°C | Ambient Operating Temperature   |

|----------------------------------|-----------------|---------------------------------|

| All Input or Output Voltage with |                 | NM25C020L/LZ                    |

| Respect to Ground                | +6.5V to -0.3V  | NM25C020LE/LZE<br>NM25C020LV    |

| Lead Temp. (Soldering, 10 sec.)  | +300°C          |                                 |

| ESD Rating                       | 2000V           | Power Supply (V <sub>CC</sub> ) |

## DC and AC Electrical Characteristics $2.7V \le V_{CC} \le 4.5V$ (unless otherwise specified)

|                   |                     |         |                             |                       |                       | C020L/LE 25C0<br>D20LZ/LZE |                       |          |  |

|-------------------|---------------------|---------|-----------------------------|-----------------------|-----------------------|----------------------------|-----------------------|----------|--|

| Symbol            | Parameter           | Part    | Conditions                  | Min.                  | Max.                  | Min                        | Max                   | Units    |  |

| I <sub>CC</sub>   | Operating Current   |         | $\overline{CS} = V_{IL}$    |                       | 3                     |                            | 3                     | mA       |  |

| I <sub>CCSB</sub> | Standby Current     | L<br>LZ | $\overline{CS} = V_{CC}$    |                       | 10<br>1               |                            | 10<br>N/A             | μΑ<br>μΑ |  |

| IIL               | Input Leakage       |         | $V_{IN} = 0$ to $V_{CC}$    | -1                    | 1                     | -1                         | 1                     | μA       |  |

| I <sub>OL</sub>   | Output Leakage      |         | $V_{OUT} = GND$ to $V_{CC}$ | -1                    | 1                     | -1                         | 1                     | μA       |  |

| V <sub>IL</sub>   | Input Low Voltage   |         |                             | -0.3                  | V <sub>CC</sub> * 0.3 | -0.3                       | V <sub>CC</sub> * 0.3 | V        |  |

| VIH               | Input High Voltage  |         |                             | 0.7 * V <sub>CC</sub> | V <sub>CC</sub> + 0.3 | 0.7 * V <sub>CC</sub>      | V <sub>CC</sub> + 0.3 | V        |  |

| V <sub>OL</sub>   | Output Low Voltage  |         | I <sub>OL</sub> = 0.8 mA    |                       | 0.4                   |                            | 0.4                   | V        |  |

| V <sub>OH</sub>   | Output High Voltage |         | I <sub>OH</sub> = -0.8 mA   | V <sub>CC</sub> - 0.8 |                       | V <sub>CC</sub> - 0.8      |                       | V        |  |

| f <sub>OP</sub>   | SCK Frequency       |         |                             |                       | 1.0                   |                            | 1.0                   | MHz      |  |

| t <sub>RI</sub>   | Input Rise Time     |         |                             |                       | 2.0                   |                            | 2.0                   | μs       |  |

| t <sub>FI</sub>   | Input Fall Time     |         |                             |                       | 2.0                   |                            | 2.0                   | μs       |  |

| t <sub>CLH</sub>  | Clock High Time     |         | (Note 6)                    | 410                   |                       | 410                        |                       | ns       |  |

| t <sub>CLL</sub>  | Clock Low Time      |         | (Note 6)                    | 410                   |                       | 410                        |                       | ns       |  |

| t <sub>CSH</sub>  | Min. CS High Time   |         | (Note 7)                    | 500                   |                       | 500                        |                       | ns       |  |

| t <sub>CSS</sub>  | CS Setup Time       |         |                             | 500                   |                       | 500                        |                       | ns       |  |

| t <sub>DIS</sub>  | Data Setup Time     |         |                             | 100                   |                       | 100                        |                       | ns       |  |

| t <sub>HDS</sub>  | HOLD Setup Time     |         |                             | 240                   |                       | 240                        |                       | ns       |  |

| t <sub>CSN</sub>  | CS Hold Time        |         |                             | 500                   |                       | 500                        |                       | ns       |  |

| t <sub>DIN</sub>  | Data Hold Time      |         |                             | 100                   |                       | 100                        |                       | ns       |  |

| t <sub>HDN</sub>  | HOLD Hold Time      |         |                             | 240                   |                       | 240                        |                       | ns       |  |

| t <sub>PD</sub>   | Output Delay        |         | C <sub>L</sub> = 200 pF     |                       | 500                   |                            | 500                   | ns       |  |

| t <sub>DH</sub>   | Output Hold Time    |         |                             | 0                     |                       | 0                          |                       | ns       |  |

| t <sub>LZ</sub>   | HOLD Output Low Z   |         |                             |                       | 240                   |                            | 240                   | ns       |  |

| t <sub>DF</sub>   | Output Disable Time |         | C <sub>L</sub> = 200 pF     |                       | 500                   |                            | 500                   | ns       |  |

| t <sub>HZ</sub>   | HOLD to Output Hi Z |         |                             |                       | 240                   |                            | 240                   | ns       |  |

| t <sub>WP</sub>   | Write Cycle Time    |         | 1-4 Bytes                   |                       | 15                    |                            | 15                    | ms       |  |

#### **Capacitance** $T_A = 25^{\circ}C$ , f = 2.1/1 MHz (Note 8)

| Symbol           | Test               | Тур | Max | Units |

|------------------|--------------------|-----|-----|-------|

| C <sub>OUT</sub> | Output Capacitance | 3   | 8   | pF    |

| C <sub>IN</sub>  | Input Capacitance  | 2   | 6   | pF    |

## **AC Test Conditions**

**Operating Conditions**

| Output Load                        | $I_{OL} = 10 \ \mu A$ , $I_{OH} = 10 \ \mu A$ |

|------------------------------------|-----------------------------------------------|

| Input Pulse Levels                 | 0.3V to 3.5V                                  |

| Timing Measurement Reference Level | l                                             |

| Input                              | 0.4V and 1.6V                                 |

| Output                             | 0.8V and 1.6V                                 |

|                                    |                                               |

Note 5: Stress above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 6: The  $f_{OP}$  frequency specification specifies a minimum clock period of  $1/f_{OP}$ . Therefore, for every  $f_{OP}$  clock cycle,  $t_{CLH} + t_{CLL}$  must be equal to or greater than  $1/f_{OP}$ . For example, if the 2.1MHz period = 476ns and  $t_{CLH} = 190ns$ ,  $t_{CLL}$  must be 286ns.

**Note 7:**  $\overline{CS}$  must be brought high for a minimum of t<sub>CSH</sub> between consecutive instruction cycles.

Note 8: This parameter is periodically sampled and not 100% tested.

# NM25C020 2K-Bit Serial CMOS EEPROM (Serial Periphrial Interface (SPI) Synchronous Bus

# **Functional Description**

#### **TABLE 1. Instruction Set**

| Instruction<br>Name | Instruction<br>Opcode | Operation                      |

|---------------------|-----------------------|--------------------------------|

| WREN                | 00000110              | Set Write Enable Latch         |

| WRDI                | 00000100              | Reset Write Enable Latch       |

| RDSR                | 00000101              | Read Status Register           |

| WRSR                | 00000001              | Write Status Register          |

| READ                | 00000011              | Read Data from Memory<br>Array |

| WRITE               | 00000010              | Write Data to Memory Array     |

**MASTER**: The device that generates the serial clock is designated as the master. The NM25C020 can never function as a master.

**SLAVE**: The NM25C020 always operates as a slave as the serial clock pin is always an input.

**TRANSMITTER/RECEIVER**: The NM25C020 has separate pins for data transmission (SO) and reception (SI).

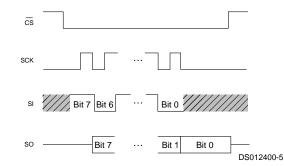

**MSB**: The Most Significant Bit is the first bit transmitted and received.

**CHIP SELECT**: The chip is selected when pin  $\overline{CS}$  is low. When the chip is *not* selected, data will not be accepted from pin SI, and the output pin SO is in high impedance.

**SERIAL OP-CODE**: The first byte transmitted after the chip is selected with CS going low contains the op-code that defines the operation to be performed.

**PROTOCOL**: When connected to the SPI port of a 68HC11 microcontroller, the NM25C020 accepts a clock phase of 0 and a clock polarity of 0. The SPI protocol for this device defines the byte transmitted on the SI and SO data lines for proper chip operation. See Figure 4.

Data is clocked in on the positive SCK edge and out on the negative SCK edge.

**HOLD**: The HOLD pin is used in conjunction with the CS to select the device. Once the device is selected and a serial sequence is underway, HOLD may be forced low to suspend further serial communication with the device without resetting the serial sequence. Note that HOLD must be brought low while the SCK pin is low. The device must remain selected during this sequence. To resume serial communication HOLD is brought high while the SCK pin is low. The SO pin is at a high impedance state during HOLD.

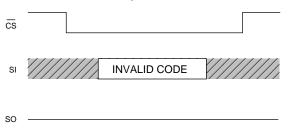

**INVALID OP-CODE**: After an invalid code is received, no data is shifted into the NM25C020, and the SO data output pin remains high impedance until a new  $\overline{CS}$  falling edge reinitializes the serial communication. See Figure 5.

#### FIGURE 5. Invalid Op-Code

DS012400-7

## Functional Description (Continued)

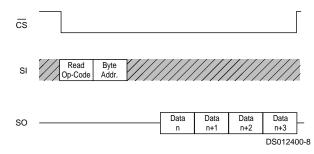

**READ SEQUENCE:** Reading the memory via the serial SPI link requires the following sequence. The  $\overline{CS}$  line is pulled low to select the device. The READ op-code is transmitted on the SI line followed by the byte address (A7–A0) to be read. After this is done, data on the SI line becomes don't care. The data (D7–D0) at the address specified is then shifted out on the SO line. If only one byte is to be read, the  $\overline{CS}$  line can be pulled back to the high level. It is possible to continue the READ sequence as the byte address is automatically incremented and data will continue to be shifted out as clock pulses are continuously applied. When the highest address (000) allowing the entire memory to be read in one continuous READ cycle. See Figure 6.

#### **FIGURE 6. Read Sequence**

**READ STATUS REGISTER (RDSR)**: The Read Status Register (RDSR) instruction provides access to the status register and is used to interrogate the READY/BUSY and WRITE ENABLE status of the chip. (Two non-volatile status register bits are used to select one of four levels of BLOCK WRITE PROTECTION.) The status register format is shown in Table 2.

#### **TABLE 2. Status Register Format**

| Bit |

|-----|-----|-----|-----|-----|-----|-----|-----|

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

| Х   | Х   | Х   | Х   | BP1 | BP0 | WEN |     |

#### X = Don't Care

Status register Bit 0 = 0 (RDY) indicates that the device is READY; Bit 0 = 1 indicates that a program cycle is in progress. Bit 1 = 0(WEN) indicates that the device is not WRITE ENABLED; Bit 1 = 1indicates that the device is WRITE ENABLED. Non-volatile status register Bits 2 and 3 (BP0 and BP1) indicate the level of BLOCK WRITE PROTECTION selected. The block write protection levels and corresponding status register control bits are shown in Table 3. Note that if a RDSR instruction is executed during a programming cycle only the RDY bit is valid. All other bits are 1s. See Figure 7.

#### **FIGURE 7. Read Status**

#### **TABLE 3. Block Write Protection Levels**

| Level | Status Re | Array |                      |

|-------|-----------|-------|----------------------|

|       | BP1       | BP0   | Address<br>Protected |

| 0     | 0         | 0     | None                 |

| 1     | 0         | 1     | C0-FF                |

| 2     | 1         | 0     | 80-FF                |

| 3     | 1         | 1     | 00-FF                |

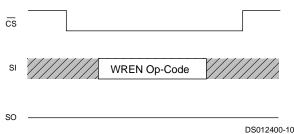

WRITE ENABLE (WREN): When  $V_{CC}$  is applied to the chip, it "powers up" in the write disable state. Therefore, all programming modes must be preceded by a WRITE ENABLE (WREN) instruction. At the completion of a WRITE or WRSR cycle the device is automatically returned to the write disable state. Note that a WRITE DISABLE (WRDI) instruction will also return the device to the write disable state. See Figure 8.

#### FIGURE 8. Write Enable

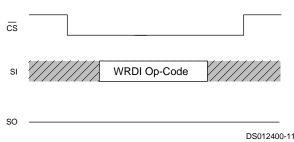

**WRITE DISABLE (WRDI)**: To protect against accidental data disturbance the WRITE DISABLE (WRDI) instruction disables all programming modes. See Figure 9.

#### FIGURE 9. Write Disable

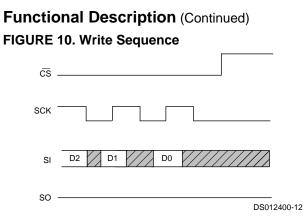

WRITE SEQUENCE: To program the device, the WRITE PRO-TECT (WP) pin must be held high and two separate instructions must be executed. The chip must first be write enabled via the WRITE ENABLE instruction and then a WRITE instruction must be executed. Moreover, the address of the memory location(s) to be programmed must be outside the protected address field selected by the Block Write Protection Level. See Table 3.

A WRITE command requires the following sequence. The  $\overline{CS}$  line is pulled low to select the device, then the WRITE op-code is transmitted on the SI line followed by the byte address(A7–A0) and the corresponding data (D7-D0) to be written. **Programming will start after the CS pin is forced back to a high level.** Note that the LOW to HIGH transition of the  $\overline{CS}$  pin must occur during the SCK low time immediately after clocking in the D0 data bit. See Figure 10.

The READY/BUSY status of the device can be determined by executing a READ STATUS REGISTER (RDSR) instruction. Bit 0 = 1 indicates that the WRITE cycle is still in progress and Bit 0 = 0 indicates that the WRITE cycle has ended. During the WRITE programming cycle (Bit 0 = 1) only the READ STATUS REGISTER instruction is enabled.

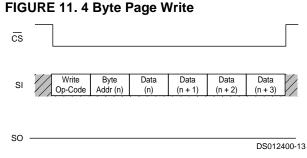

The NM25C020 is capable of a 4 byte PAGE WRITE operation. After receipt of each byte of data the two low order address bits are internally incremented by one. The seven high order bits of the address will remain constant. If the master should transmit more than 4 bytes of data, the address counter will "roll over," and the previously loaded data will be reloaded. See Figure 11.

#### At the completion of a WRITE cycle the device is automatically returned to the write disable state.

If the device is not WRITE enabled, the device will ignore the WRITE instruction and return to the standby state when  $\overline{CS}$  is forced high. A new  $\overline{CS}$  falling edge is required to re-initialize the serial communication.

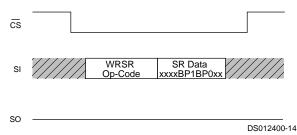

**WRITE STATUS REGISTER (WRSR):** The WRITE STATUS REGISTER (WRSR) instruction is used to program the non-volatile status register Bits 2 and 3 (BP0 and BP1). The WRITE PROTECT ( $\overline{WP}$ ) pin must be held high and two separate instructions must be executed. The chip must first be write enabled via the WRITE ENABLE instruction and then a WRSR instruction must be executed.

The WRSR command requires the following sequence. The  $\overline{CS}$  line is pulled low to select the device and then the WRSR op-code is transmitted on the SI line followed by the data to be programmed. See Figure 12.

#### FIGURE 12. Write Status Register

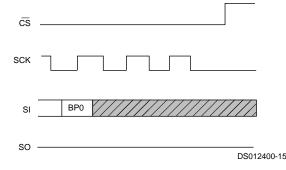

Note that the first four bits are don't care bits followed by BP1 and BP0 then two additional don't care bits. Programming will start after the CS pin is forced back to a high level. As in the WRITE instruction the LOW to HIGH transition of the CS pin must occur during the SCK low time immediately after clocking in the last don't care bit. See Figure 13.

#### FIGURE 13. Start WRSR Condition

The READY/BUSY status of the device can be determined by executing a READ STATUS REGISTER (RDSR) instruction. Bit 0 = 1 indicates that the WRSR cycle is still in progress and Bit 0 = 0 indicates that the WRSR cycle has ended.

At the completion of a WRITE cycle the device is automatically returned to the write disable state.

NM25C020 2K-Bit Serial CMOS EEPROM

NM25C020 2K-Bit Serial CMOS EEPROM

| Fairchild Semiconductor                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -1                                                                                                           | etric   Cross Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| find products                                                                                                                                                                                                                                                                                | Home >> Find products >>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Inid productsProducts groupsAnalog and MixedSignalDiscreteInterfaceLogicMicrocontrollersNon-VolatileMemoryOptoelectronicsMarkets andapplicationsNew productsProduct selection andparametric searchCross-referencesearchtechnical informationbuy productstechnical supportmy Fairchildcompany | NM25C020   Product information   Contents   General description   Features   Product   status/pricing/packaging   Application notes   General description   The NM25C020 is a 2048-bit CMOS   EEPROM with an SPI compatible serial   interface. The NM25C020 is designed for data   storage in applications requiring both non-   volatile memory and in-system data updates.   This EEPROM is well suited for applications   using the 68HC11 series of microcontrollers   that support the SPI interface for high speed   communication with peripheral devices via a   serial bus to reduce pin count. The NM25C020   is implemented in Fairchild Semiconductor's   floating gate CMOS process that provides   superior endurance and data retention.   The serial data transmission of this device   requires four signal lines to control the device   operation: Chip Select (CS#), Clock (SCK),   Data In (SI), and Serial Data Out (SO). All   programming cycles are completely self-timed | Datasheet<br>Download this<br>datasheet<br>PDF<br>e-mail this datasheet<br>[E-<br>This page<br>Print version | Related LinksRequest samplesDatted LineHow to order productsDatted LineProduct Change Notices(PCNs)Datted LineDistributor and field salesrepresentativesDatted LineQuality and reliabilityDasted LineDasted LineDatted LineDistributor and field salesrepresentativesDatted LineDasted Line </th |

and do not require an erase before WRITE.

BLOCK WRITE protection is provided by programming the STATUS REGISTER with

Hardware data protection is provided by the WP# pin to protect against accidental data changes. The HOLD# pin allows the serial communication to be suspended without

one of four levels of write protection. Additionally, separate WRITE enable and WRITE program disable instructions are

provided for data protection.

resetting the serial sequence.

#### Features

- 2.1 MHz clock rate @ 2.7V to 5.5V

- 2048-bits organized as 256 x 8

- Multiple chips on the same 3-wire bus with separate chip select lines

- Self-timed programming cycle

- Simultaneous programming of 1 to 4 bytes at a time

- Status register can be polled during programming to monitor READY/BUSY

- Write Protect (WP#) pin and write disable instruction for both hardware and software write protection

- Block write protect feature to protect against accidental writes

- Endurance: 1,000,000 data changes

- Data retention greater than 40 years

- Packages available: 8-pin DIP, 8-pin SO or 8-pin TSSOP

#### back to top

Product status/pricing/packaging

| Product        | Product status                     | Pricing* | Package<br>type | Leads | Package<br>marking                  | Packing<br>method |

|----------------|------------------------------------|----------|-----------------|-------|-------------------------------------|-------------------|

| NM25C020DWF    | Not recommended for new designs    | N/A      | Wafer           | N/A   | N/A                                 | RAIL              |

| NM25C020LEMT8X | Not recommended<br>for new designs | \$1.06   | TSSOP           | 8     | &2&T<br>\$Y502<br>&Z25C020<br>LEMT8 | TAPE<br>REEL      |

| NM25C020LZEM8  | Not recommended<br>for new designs | \$1.03   | SOIC            | 8     | \$Y&Z&2&T<br>25020<br>LZE           | RAIL              |

| NM25C020VM8    | Not recommended<br>for new designs | \$1.04   | SOIC            | 8     | \$Y&Z&2&T<br>25C02<br>0VM8          | RAIL              |

| NM25C020LEM8   | Not recommended<br>for new designs | \$1.03   | SOIC            | 8     | \$Y&Z&2&T<br>25C02<br>0LE           | RAIL              |

| NM25C020LEMT8  | Not recommended<br>for new designs | \$1.06   | TSSOP           | 8     | &2&T<br>\$Y502<br>&Z25C020<br>LEMT8 | RAIL              |

| NM25C020LZEMT8  | Not recommended for new designs    | \$1.07 | TSSOP | 8   | &2&T<br>\$Y502<br>&Z25C020<br>LZE | RAIL         |

|-----------------|------------------------------------|--------|-------|-----|-----------------------------------|--------------|

| NM25C020LN      | Not recommended<br>for new designs | \$1.00 | DIP   | 8   | \$Y&Z&2&T<br>25C020<br>LN         | RAIL         |

| NM25C020VM8X    | Not recommended for new designs    | \$1.04 | SOIC  | 8   | \$Y&Z&2&T<br>25C02<br>0VM8        | TAPE<br>REEL |

| NM25C020M8X     | Not recommended for new designs    | \$0.97 | SOIC  | 8   | \$Y&Z&2&T<br>25C02<br>0M8         | TAPE<br>REEL |

| NM25C020LEN     | Not recommended for new designs    | \$1.03 | DIP   | 8   | \$Y&Z&2&T<br>25C020<br>LEN        | RAIL         |

| NM25C020LZM8X   | Not recommended for new designs    | \$1.01 | SOIC  | 8   | \$Y&Z&2&T<br>25C20<br>LZM8        | TAPE<br>REEL |

| NM25C020DICE    | Not recommended for new designs    | N/A    | Wafer | N/A | N/A                               | RAIL         |

| NM25C020LZEMT8X | Not recommended<br>for new designs | \$1.07 | TSSOP | 8   | &2&T<br>\$Y502<br>&Z25C020<br>LZE | TAPE<br>REEL |

| NM25C020N       | Not recommended<br>for new designs | \$0.97 | DIP   | 8   | \$Y&Z&2&T<br>25C020<br>N          | RAIL         |

| NM25C020LZM8    | Not recommended<br>for new designs | \$1.01 | SOIC  | 8   | \$Y&Z&2&T<br>25020<br>LZM8        | RAIL         |

| NM25C020LZEM8X  | Not recommended<br>for new designs | \$1.03 | SOIC  | 8   | \$Y&Z&2&T<br>25020<br>LZE         | TAPE<br>REEL |

| NM25C020EM8X    | Not recommended<br>for new designs | \$1.00 | SOIC  | 8   | \$Y&Z&2&T<br>25C02<br>0EM8        | TAPE<br>REEL |

| NM25C020EM8     | Not recommended for new designs    | \$1.00 | SOIC  | 8   | \$Y&Z&2&T<br>25C02<br>0EM8        | RAIL         |

| NM25C020M8      | Not recommended<br>for new designs | \$0.97 | SOIC  | 8   | \$Y&Z&2&T<br>25C02<br>0M8         | RAIL         |

| NM25C020LVM8    | Not recommended<br>for new designs | \$1.06 | SOIC  | 8   | \$Y&Z&2&T<br>25020<br>LVM8        | RAIL         |

| NM25C020LM8X    | Not recommended for new designs    | \$1.00 | SOIC  | 8   | \$Y&Z&2&T<br>25C02<br>0LM8        | TAPE<br>REEL |

| NM25C020LM8   | Not recommended<br>for new designs | \$1.00 | SOIC | 8 | \$Y&Z&2&T<br>25C02<br>0LM8 | RAIL         |

|---------------|------------------------------------|--------|------|---|----------------------------|--------------|

| NM25C020LEM8X | Not recommended for new designs    | \$1.03 | SOIC | 8 | \$Y&Z&2&T<br>25C02<br>0LE  | TAPE<br>REEL |

| NM25C020EN    | Not recommended for new designs    | \$1.00 | DIP  | 8 | \$Y&Z&2&T<br>25C020<br>EN  | RAIL         |

\* 1,000 piece Budgetary Pricing

back to top

Application notes

<u>AN-860: AN-860 Protecting Data in Serial EEPROMS</u> (28 K) Jul 19, 2002

back to top

<u>Home</u> | <u>Find products</u> | <u>Technical information</u> | <u>Buy products</u> | <u>Support</u> | <u>Company</u> | <u>Contact us</u> | <u>Site index</u> | <u>Privacy policy</u>

© Copyright 2002 Fairchild Semiconductor