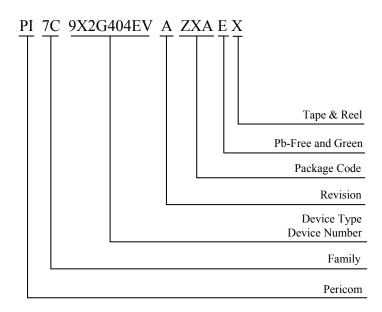

# **PI7C9X2G404EV** PCI EXPRESS GEN 2 PACKET SWITCH **4-Port, 4-Lane, ExtremeLo PCIe 2.0 Packet Switch** *DATASHEET*

REVISION 9 August 2022

1545 Barber Lane Milpitas, CA 95035 Telephone: 408-232-9100 FAX: 408-434-1040 Internet: <u>http://www.diodes.com</u>

#### IMPORTANT NOTICE

1. DIODES INCORPORATED (Diodes) AND ITS SUBSIDIARIES MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO ANY INFORMATION CONTAINED IN THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

2. The Information contained herein is for informational purpose only and is provided only to illustrate the operation of Diodes' products described herein and application examples. Diodes does not assume any liability arising out of the application or use of this document or any product described herein. This document is intended for skilled and technically trained engineering customers and users who design with Diodes' products. Diodes' products may be used to facilitate safety-related applications; however, in all instances customers and users are responsible for (a) selecting the appropriate Diodes products for their applications, (b) evaluating the suitability of Diodes' products for their applications, (c) ensuring their applications, which incorporate Diodes' products, comply the applicable legal and regulatory requirements as well as safety and functional-safety related standards, and (d) ensuring they design with appropriate safeguards (including testing, validation, quality control techniques, redundancy, malfunction prevention, and appropriate treatment for aging degradation) to minimize the risks associated with their applications.

3. Diodes assumes no liability for any application-related information, support, assistance or feedback that may be provided by Diodes from time to time. Any customer or user of this document or products described herein will assume all risks and liabilities associated with such use, and will hold Diodes and all companies whose products are represented herein or on Diodes' websites, harmless against all damages and liabilities.

4. Products described herein may be covered by one or more United States, international or foreign patents and pending patent applications. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks and trademark applications. Diodes does not convey any license under any of its intellectual property rights or the rights of any third parties (including third parties whose products and services may be described in this document or on Diodes' website) under this document.

products provided Diodes' to Diodes' Standard Terms Conditions are subject and of Sale (https://www.diodes.com/about/company/terms-and-conditions/terms-and-conditions-of-sales/) or other applicable terms. This document does not alter or expand the applicable warranties provided by Diodes. Diodes does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

6. Diodes' products and technology may not be used for or incorporated into any products or systems whose manufacture, use or sale is prohibited under any applicable laws and regulations. Should customers or users use Diodes' products in contravention of any applicable laws or regulations, or for any unintended or unauthorized application, customers and users will (a) be solely responsible for any damages, losses or penalties arising in connection therewith or as a result thereof, and (b) indemnify and hold Diodes and its representatives and agents harmless against any and all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim relating to any noncompliance with the applicable laws and regulations, as well as any unintended or unauthorized application.

7. While efforts have been made to ensure the information contained in this document is accurate, complete and current, it may contain technical inaccuracies, omissions and typographical errors. Diodes does not warrant that information contained in this document is error-free and Diodes is under no obligation to update or otherwise correct this information. Notwithstanding the foregoing, Diodes reserves the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. This document is written in English but may be translated into multiple languages for reference. Only the English version of this document is the final and determinative format released by Diodes.

8. Any unauthorized copying, modification, distribution, transmission, display or other use of this document (or any portion hereof) is prohibited. Diodes assumes no responsibility for any losses incurred by the customers or users or any third parties arising from any such unauthorized use.

9. This Notice may be periodically updated with the most recent version available at https://www.diodes.com/about/company/terms-and-conditions/important-notice

DIODES is a trademark of Diodes Incorporated in the United States and other countries. The Diodes logo is a registered trademark of Diodes Incorporated in the United States and other countries. © 2022 Diodes Incorporated. All Rights Reserved.

www.diodes.com

# **REVISION HISTORY**

| Date       | <b>Revision Number</b> | Description                                                                                             |

|------------|------------------------|---------------------------------------------------------------------------------------------------------|

| 09/06/2017 |                        | Preliminary Datasheet                                                                                   |

|            |                        | Reg40h[15:8] next item point to 4ch for both up/downport port                                           |

|            |                        | MSI register are for both up&downport, not downport only anymore                                        |

|            |                        | Multiple Message Capable modify form 3b'001 to 3'b010                                                   |

|            |                        | Update 74h[7], 8Ch[7][12].                                                                              |

|            |                        | Update 340h[4][5]                                                                                       |

|            |                        | Add cfg offset 300h to 314h                                                                             |

| 12/19/2017 | 1                      | Update 8Ch[12]                                                                                          |

|            |                        | Add cfg offset 318h and 31Ch                                                                            |

|            |                        | Update 98h[15:0]                                                                                        |

|            |                        | Update REG[9c]: trigger[6:3], clear[2], port[1:0], and REG[a0]                                          |

|            |                        | Update Ini for $REG[98][15:0] = 0126$                                                                   |

|            |                        | Add cfg offset B0h to FFh                                                                               |

|            |                        | Delete Misc Control 5 (offset 314h)                                                                     |

|            |                        | Updated section 15 Ordering Information                                                                 |

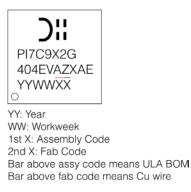

|            |                        | Added Fig 13-3 Part Marking                                                                             |

|            |                        | Update Feature                                                                                          |

|            |                        | Add Chap 6.2 and 6.3                                                                                    |

| 07/12/2018 | 2                      | Update 7.2.54 OPERATION MODE – OFFSET 98h                                                               |

|            |                        | Add Chap 13                                                                                             |

|            |                        | Update Table 9-3                                                                                        |

|            |                        | Update Table 12-1                                                                                       |

|            |                        | Updated Section 1 Features                                                                              |

|            |                        | Updated 3.2 Port Configuration Signals                                                                  |

| 01/15/0010 | 19 3                   | Updated Section 7.2.125 MISC CONTROL 0 REGISTER – OFFSET 300h                                           |

| 01/15/2019 |                        | Updated Section 7.2.126 MISC CONTROL 1 REGISTER – OFFSET 304h                                           |

|            |                        | Updated Section 10 Power Management                                                                     |

| 00/20/2010 |                        | Updated Section 12.1 Absolute Maximum Ratings                                                           |

| 02/20/2019 | 4                      | New revision number due to document control process                                                     |

| 09/12/2019 | 5                      | Updated Section 12.4 Power Consumption                                                                  |

|            |                        | Updated Section 15 Ordering Information                                                                 |

|            |                        | Updated Section 1 Features                                                                              |

| 10/15/2019 | 6                      | Updated Section 3.1 PCI Express Interface Signals<br>Updated Table 5-2 Receiver Signal Detect Threshold |

|            |                        | Updated Figure 14-3 Part Marking                                                                        |

|            |                        | Updated Section 8 Clock Scheme                                                                          |

|            |                        | Updated Section 5-1 Physical Layer Circuit                                                              |

|            |                        | Updated Table 6-1, 6-3, 6-5 and 6-6                                                                     |

| 07/29/2020 | 7                      | Updated Figure 6-6 and 6-9                                                                              |

|            |                        | Updated Section 6.1.4 and 7.2.2                                                                         |

|            |                        | Updated Notes for Table 12-2 DC Electrical Characteristics                                              |

| 12/15/2020 | 8                      | For Datasheet Status Change                                                                             |

|            | ~                      | Updated Section 1 FEATURES                                                                              |

|            |                        | Updated Section 3.1 PCI EXPRESS INTERFACE SIGNALS                                                       |

|            |                        | Updated Section 14 Package Information                                                                  |

|            |                        | Updated Section 7.2.47 PHY PARAMETER 2 – OFFSET 7Ch                                                     |

|            |                        | Updated Section 7.2.50 XPIP_CSR5 – OFFSET 88h                                                           |

|            |                        | Updated Section 7.2.68 LINK CONTROL REGISTER – OFFSET D0h                                               |

|            |                        | Updated Section 8 Clock Scheme                                                                          |

| 08/12/2022 | 9                      | Updated 6.1.3 EEPROM Space Address Map                                                                  |

|            |                        | Updated 6.1.4 Mapping EEPROM Contents to Configuration                                                  |

|            |                        | Updated Table 5-3, 6-1, 6-2, 6-3, 6-4, 6-5, 6-8 and 6-9                                                 |

|            |                        | Updated Chap 13 Thermal Data                                                                            |

|            |                        | Removed MEMORY ECC ERROR MASK AND STATUS Register                                                       |

|            |                        | Updated 7.2.51 TL_CSR0 – OFFSET 8Ch                                                                     |

|            |                        | Added Section 7.2.138 DEBUGOUT CONTROL – OFFSET 348h                                                    |

|            |                        | Added Section 7.2.138 DEBUGOUT DATA – OFFSET 34Ch                                                       |

# **TABLE OF CONTENTS**

| 2         GENERAL DESCRIPTION         12           3         PIN DESCRIPTION         14           3.1         PCIEXPRESS INTERFACE SIGNALS         14           3.2         PORT CONFIGURATION SIGNALS         15           3.3         MISCELLANFOLD SIGNALS         16           3.4         ITAG BOUNDARY SCAN SIGNALS         16           3.4         ITAG BOUNDARY SCAN SIGNALS         17           3.5         POWER PINS         17           4         PIN ASSIGNMENTS         19           4.1         PIN LIST OF 136-PIN AQEN         19           5         FUNCTIONAL DESCRIPTION         20           5.1.1         RECEIVER DETECTION         20           5.1.2         RECEIVER DETECTION         20           5.1.3         RECEIVER SIGNAL DETECTION         20           5.1.4         RECEIVER NUMBURIES         20           5.1.5         RECEIVER SIGNAL DETECTION         20           5.1.6         RECEIVER BUCKUIT         20           5.1.7         DRIFE AMPLITUDE         20           5.1.8         RECEIVER BUCKUIT         20           5.1.4         RECEIVER BUCKUIT         20           5.1.5         DRIFE AMPLITUDE <t< th=""><th>1</th><th>I FEATURES</th><th>11</th></t<> | 1 | I FEATURES                                          | 11 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------|----|

| 3.1       PCI EXPRESS INTERFACE SIGNALS       14         3.2       PORT CONFIGURATION SIGNALS       15         3.3       MISCELLANEOUS SIGNALS       16         3.4       JTAG BOUNDARY SCAN SIGNALS       17         3.5       POWER PINS       17         4       PIN ASSIGNMENTS       19         4.1       PIN LIST OF 136-PIN AQFN       19         5       FUNCTIONAL DESCRIPTION       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER DETECTION       20         5.1.3       RECEIVER BUTAL CIRCUIT       20         5.1.4       RECEIVER BUTALTATION       21         5.1.5       DRIVE AMPLITUDE       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE AMPLITUDE       22         5.1.8       TRANSMITER ELECTRICAL IDLE LATENCY       23         5.1.8       TRANSMITER FLOCTAL IDLE LATENCY       23         5.1.8       TRANSACTION LAYER (DL1)       23         5.1.4       TRANSMITER ELECTRICAL IDLE LATENCY       23         5.1.4       TRANSMITER ELECTRICAL IDLE LATENCY       23         5.1.8       TRANSACTION LAYER (DL1)       24         5.6.4<                                                                                    | 2 | 2 GENERAL DESCRIPTION                               |    |

| 3.2       PORT CONFIGURATION SIGNALS       15         3.3       MISCELLANEOUS SIGNALS       16         3.4       ITAG BOUNDARY SCAN SIGNALS       17         3.5       POWER PINS       17         3.6       INTROFENS       17         4       PIN ASSIGNMENTS       19         4.1       PIN LIST OF 136-PIN AQFN       19         5       FUNCTIONAL DESCRIPTION       20         5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER BUGAL DETECTION       20         5.1.3       RECEIVER BUGAL DETECTION       21         5.1.4       RECEIVER BUGAL DETECTION       21         5.1.5       DRIVE AMPLITUDE       22         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE DEMPHASIS       23         5.1.8       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.2       DATA LINK LAYER R(DL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.6.4       CPUH       25         5.6.5       CPLD       25         5.6.6.4       CPH       25 </th <th>3</th> <th>3 PIN DESCRIPTION</th> <th>14</th>                                                 | 3 | 3 PIN DESCRIPTION                                   | 14 |

| 3.2       PORT CONFIGURATION SIGNALS       15         3.3       MISCELLANEOUS SIGNALS       16         3.4       ITAG BOUNDARY SCAN SIGNALS       17         3.5       POWER PINS       17         3.6       INTROFENS       17         4       PIN ASSIGNMENTS       19         4.1       PIN LIST OF 136-PIN AQFN       19         5       FUNCTIONAL DESCRIPTION       20         5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER BUGAL DETECTION       20         5.1.3       RECEIVER BUGAL DETECTION       21         5.1.4       RECEIVER BUGAL DETECTION       21         5.1.5       DRIVE AMPLITUDE       22         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE DEMPHASIS       23         5.1.8       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.2       DATA LINK LAYER R(DL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.6.4       CPUH       25         5.6.5       CPLD       25         5.6.6.4       CPH       25 </td <td></td> <td>3.1 PCI EXPRESS INTERFACE SIGNALS</td> <td></td>                                    |   | 3.1 PCI EXPRESS INTERFACE SIGNALS                   |    |

| 3.4       JTAG BOUNDARY SCAN SIGNALS       17         3.5       POWER PINS       17         4       PIN ASSIGNMENTS       19         4.1       PIN LIST OF 136-PIN AQFN       19         5       FUNCTIONAL DESCRIPTION       20         5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER DETECTION       20         5.1.3       RECEIVER BUDALIZATION       21         5.1.4       TRANSMITTER SWING       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE MEMULTUDE       23         5.1.7       DRIVE DE-EMPHASIS       23         5.1.8       TRANSMITER ELECTRICAL IDLE LATENCY       23         5.1.7       DRIVE AMPLITUDE AND DE-EMPHASIS       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.4       ROUTING       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.                                                                                                                                |   |                                                     |    |

| 3.5       POWER PINS.       17         4       PIN ASSIGNMENTS       19         4.1       PIN LIST OF 136-PIN AQFN       19         5       FUNCTIONAL DESCRIPTION       20         5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER SIGAL DETECTION       21         5.1.3       RECEIVER USAL DETECTION       21         5.1.4       TRANSMITTER SWING       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE DE-EMPHASIS       23         5.18       TRANSMITTER ELECTRICAL IDLE LATENCY       23         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       QUEUE       24         5.6       TOXIC MAPPING       25         5.6.3       PH       25         5.6.4       CPLH       25         5.6.5       CPLH       25         5.6.6       CPLH       25         5.6.5       CPLH       25         5.6.6 <t< td=""><td></td><td>3.3 MISCELLANEOUS SIGNALS</td><td></td></t<>                                                                          |   | 3.3 MISCELLANEOUS SIGNALS                           |    |

| 4       PIN ASSIGNMENTS       19         4.1       PIN LIST OF 136-PIN AQFN       19         5       FUNCTIONAL DESCRIPTION       20         5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER SIGAL DETECTION       20         5.1.3       RECEIVER EQUALIZATION       21         5.1.4       TRANSMITTER SWING       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE AMPLITUDE AND DE-EMPHASIS       23         5.1.6       DRIVE AMPLITUDE       23         5.1.7       DRIVE DEFECTICAL IDLE LATENCY       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TCVC MAPPING       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       26         5.6.4       CPLI       25 </td <td></td> <td></td> <td></td>                                                                     |   |                                                     |    |

| 4.1       PIN LIST OF 136-PIN AQFN       19         5       FUNCTIONAL DESCRIPTION.       20         5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION.       20         5.1.2       RECEIVER SIGNAL DETECTION.       21         5.1.3       RECEIVER EQUALIZATION.       21         5.1.4       TRANSMITTER SWING.       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS.       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE AMPLITUDE       23         5.1.8       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLD       25         5.6.5       CPLD       25         5.6.4       CPLD       25         5.7       TRANSACTION ORDERING       25         5.8       PORT ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       IDW CONTROL                                                                                                                                                 |   |                                                     |    |

| 5       FUNCTIONAL DESCRIPTION       20         5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER SIGNAL DETECTION       21         5.1.3       RECEIVER EQUALIZATION       21         5.1.4       TRANSMITTER SWING       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE AMPLITUDE       23         5.1.8       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6       QUEUE       25         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLD       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.7       TRANSACTION ORDERING       25         5.7       T                                                                                                                                         | 4 |                                                     |    |

| 5.1       PHYSICAL LAYER CIRCUIT       20         5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER SIGNAL DETECTION       21         5.1.3       RECEIVER EQUALIZATION       21         5.1.4       TRANSMITTER SWING       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE DE-EMPHASIS       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY       23         5.2       DATA LINK LAYER (DL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       G.QUEUE       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.4       CPLH       26         5.7       TRANSACTION ORDERING       26         5.9       VCA RBITRATION       26         5.10       FLOW CONTROL       2                                                                                                                                                  |   | 4.1 PIN LIST OF 136-PIN AQFN                        |    |

| 5.1.1       RECEIVER DETECTION       20         5.1.2       RECEIVER SIGNAL DETECTION       21         5.1.3       RECEIVER EQUALIZATION       21         5.1.4       TRANSMITTER SWING       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE DE-EMPHASIS       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY       23         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TCVC MAPPING       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLI       25         5.7       TRANSACTION ORDERING       26         5.8       PORT ARBITRATION       26         5.9       VCA RBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSACTION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27                                                                                                                                    | 5 | 5 FUNCTIONAL DESCRIPTION                            | 20 |

| 5.1.2       RECEIVER SIGNAL DETECTION.       21         5.1.3       RECEIVER EQUALIZATION.       21         5.1.4       TRANSMITTER SWING.       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS.       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE AMPLITUDE       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY.       23         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION).       24         5.4       ROUTING       24         5.5       TCVC MAPPING       24         5.6       QUEUE.       25         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       CPLH       25         5.6.7       TRANSACTION ORDERING       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26                                                                                                                                                                  |   | 5.1 PHYSICAL LAYER CIRCUIT                          |    |

| 5.1.3       RECEIVER EQUALIZATION.       21         5.1.4       TRANSMITTER SWING.       21         5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS.       21         5.1.6       DRIVE AMPLITUDE.       22         5.1.7       DRIVE DE-EMPHASIS.       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY.       23         5.2       DATA LINK LAYER (DLL).       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION).       24         5.4       ROUTING       24         5.5       TC/VC MAPPING.       24         5.6       QUEUE.       24         5.6       QUEUE.       24         5.6.1       PH.       25         5.6.2       PD.       25         5.6.3       NPHD       25         5.6.4       CPLH.       25         5.6.5       CPD       25         5.6.4       CPLH       25         5.7       TRANSACTION ORDERING.       25         5.8       PORT ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSACTION NAYER TRANSMIT BLOCK (TLP ENCAP                                                                                                                                         |   |                                                     |    |

| 5.1.4       TRANSMITTĒR SWING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |                                                     |    |

| 5.1.5       DRIVE AMPLITUDE AND DE-EMPHASIS SETTINGS.       21         5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE DE-EMPHASIS       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY       23         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       PUD       25         5.6.7       TRANSACTION ORDERING       25         5.7       TRANSACTION ORDERING       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       ACCESS CONTROLS SERVICE                                                                                                                                                    |   |                                                     |    |

| 5.1.6       DRIVE AMPLITUDE       22         5.1.7       DRIVE DE-EMPHASIS       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY       23         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       CPLD       26         5.7       TRANSACTION ORDERING       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       A                                                                                                                                                                                     |   |                                                     |    |

| 5.1.7       DRIVE DE-EMPHASIS       23         5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY       23         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6       QUEUE       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.7       TRANSACTION ORDERING       25         5.7       TRANSACTION ORDERING       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       ACCESS CONTROLS SERVICE       27         6       EEPROM INTERFACE       28         6.1.1       AUTO MODE EERPOM ACCESS       28         6.1.2       EEPROM MODE AT RESET                                                                                                                                                         |   |                                                     |    |

| 5.1.8       TRANSMITTER ELECTRICAL IDLE LATENCY.       23         5.2       DATA LINK LAYER (DLL)       23         5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.7       TRANSACTION ORDERING       25         5.8       PORT ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         6       EEPROM INTERFACE       28         6.1.1       AUTO MODE SERVICE       27         6       EEPROM INTERFACE       28         6.1.2       EEPROM ACCESS       28         6.1.3       EEPROM MODE AT RESET       28 <td></td> <td></td> <td></td>                                                                                                                                 |   |                                                     |    |

| 5.3       TRANSACTION LAYER RECEIVE BLOCK (TLP DECAPSULATION)       24         5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6       QUEUE       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLD       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.5       CPLD       25         5.6.5       CPLD       25         5.6.5       CPLD       25         5.6.5       CPLD       26         5.9       VC ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TANSACTION SERVICE       27         6       EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS.       28         6.1.1       AUTO MODE EERPOM ACCESS.       28         6.1.2       EEPROM MODE AT RESET       28         6.1.3       EEPROM MODE AT RESET       28         6.1.4       MAPPING EEPROM CONTENTS TO CON                                                                                                                                                                                     |   |                                                     |    |

| 5.4       ROUTING       24         5.5       TC/VC MAPPING       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.7       TRANSACTION ORDERING       25         5.7       TRANSACTION ORDERING       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       ACCESS CONTROLS SERVICE       27         6       EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS       28         6.1       EEPROM INTERFACE       28         6.1.1       AUTO MODE EERPOM ACCESS       28         6.1.2       EEPROM MODE AT RESET       28         6.1.3       EEPROM SPACE ADDRESS MAP       28         6.1                                                                                                                                                                            |   | 5.2 DATA LINK LAYER (DLL)                           | 23 |

| 5.5       TC/VC MAPPING       24         5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.7       TRANSACTION ORDERING       25         5.7       TRANSACTION ORDERING       25         5.8       PORT ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       ACCESS CONTROLS SERVICE       27         6       EEPROM INTERFACE       28         6.1.1       AUTO MODE EERPOM ACCESS       28         6.1.2       EEPROM ACCESS       28         6.1.3       EEPROM OOT EAT RESET       28         6.1.4       MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS       30         6.1       SMBUS INTERFACE       40                                                                                                                                                                              |   |                                                     |    |

| 5.6       QUEUE       24         5.6.1       PH       25         5.6.2       PD       25         5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.6.5       CPLD       25         5.6.6       CPLD       25         5.7       TRANSACTION ORDERING       25         5.8       PORT ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       ACCESS CONTROLS SERVICE       27         6       EEPROM INTERFACE       28         6.1       EEPROM INTERFACE       28         6.1.1       AUTO MODE EERPOM ACCESS.       28         6.1.2       EEPROM MODE AT RESET       28         6.1.3       EEPROM CONTENTS TO CONFIGURATION REGISTERS.       30         6.1.4       MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS.       30         6.2.1       SMBUS WRITE       41         6.2.1       SMBUS WRACE       41 <td></td> <td></td> <td></td>                                                                                                                        |   |                                                     |    |

| 5.6.1       PH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                                     |    |

| 5.6.2       PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                                     |    |

| 5.6.3       NPHD       25         5.6.4       CPLH       25         5.6.5       CPLD       25         5.7       TRANSACTION ORDERING       25         5.8       PORT ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       ACCESS CONTROLS SERVICE       27         6       EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS       28         6.1       EEPROM INTERFACE       28         6.1.1       AUTO MODE EERPOM ACCESS.       28         6.1.2       EEPROM MODE AT RESET.       28         6.1.3       EEPROM CONTENTS TO CONFIGURATION REGISTERS.       30         6.1       MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS.       30         6.2       SMBUS INTERFACE       40         6.2.1       SMBUS WRITE       41         6.2.2       SMBUS WRITE       41         6.2.2       SMBUS READ       42                                                                                                                                                                                                                                                 |   |                                                     |    |

| 5.6.5       CPLD       25         5.7       TRANSACTION ORDERING       25         5.8       PORT ARBITRATION       26         5.9       VC ARBITRATION       26         5.10       FLOW CONTROL       26         5.11       TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)       27         5.12       ACCESS CONTROLS SERVICE       27         6       EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS       28         6.1       EEPROM INTERFACE       28         6.1.1       AUTO MODE EERPOM ACCESS       28         6.1.2       EEPROM MODE AT RESET       28         6.1.3       EEPROM SPACE ADDRESS MAP       28         6.1.4       MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS       30         6.2       SMBUS INTERFACE       40         6.2.1       SMBUS WRITE       41         6.2.2       SMBUS READ       42                                                                                                                                                                                                                                                                                                                                                                                  |   |                                                     |    |

| 5.7TRANSACTION ORDERING255.8PORT ARBITRATION265.9VC ARBITRATION265.10FLOW CONTROL265.11TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)275.12ACCESS CONTROLS SERVICE276EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS286.1EEPROM INTERFACE286.1.1AUTO MODE EERPOM ACCESS286.1.2EEPROM MODE AT RESET286.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                     |    |

| 5.8PORT ARBITRATION265.9VC ARBITRATION265.10FLOW CONTROL265.11TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)275.12ACCESS CONTROLS SERVICE276EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS286.1EEPROM INTERFACE286.1.1AUTO MODE EERPOM ACCESS286.1.2EEPROM MODE AT RESET286.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |                                                     |    |

| 5.9VC ARBITRATION265.10FLOW CONTROL265.11TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)275.12ACCESS CONTROLS SERVICE276EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS286.1EEPROM INTERFACE286.1.1AUTO MODE EERPOM ACCESS286.1.2EEPROM MODE AT RESET286.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |                                                     |    |

| 5.10FLOW CONTROL265.11TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)275.12ACCESS CONTROLS SERVICE276EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS.286.1EEPROM INTERFACE286.1.1AUTO MODE EERPOM ACCESS.286.1.2EEPROM MODE AT RESET286.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS.306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ.42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |                                                     |    |

| 5.11TRANSATION LAYER TRANSMIT BLOCK (TLP ENCAPSULATION)275.12ACCESS CONTROLS SERVICE276EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS286.1EEPROM INTERFACE286.1AUTO MODE EERPOM ACCESS286.1.2EEPROM MODE AT RESET286.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |                                                     |    |

| 5.12 ACCESS CONTROLS SERVICE276 EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS286.1 EEPROM INTERFACE286.1.1 AUTO MODE EERPOM ACCESS286.1.2 EEPROM MODE AT RESET286.1.3 EEPROM SPACE ADDRESS MAP286.1.4 MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS306.2 SMBUS INTERFACE406.2.1 SMBUS WRITE416.2.2 SMBUS READ42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |                                                     |    |

| 6.1       EEPROM INTERFACE.       28         6.1.1       AUTO MODE EERPOM ACCESS.       28         6.1.2       EEPROM MODE AT RESET.       28         6.1.3       EEPROM SPACE ADDRESS MAP.       28         6.1.4       MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS.       30         6.2       SMBUS INTERFACE       40         6.2.1       SMBUS WRITE.       41         6.2.2       SMBUS READ.       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                     |    |

| 6.1.1AUTO MODE EERPOM ACCESS.286.1.2EEPROM MODE AT RESET.286.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS.306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ.42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 6 | <b>5 EEPROM INTERFACE AND SYSTEM MANAGEMENT BUS</b> |    |

| 6.1.1AUTO MODE EERPOM ACCESS.286.1.2EEPROM MODE AT RESET.286.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS.306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ.42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 6.1 EEPROM INTERFACE                                |    |

| 6.1.3EEPROM SPACE ADDRESS MAP286.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                     |    |

| 6.1.4MAPPING EEPROM CONTENTS TO CONFIGURATION REGISTERS.306.2SMBUS INTERFACE406.2.1SMBUS WRITE416.2.2SMBUS READ.42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |                                                     |    |

| 6.2       SMBUS INTERFACE       40         6.2.1       SMBUS WRITE       41         6.2.2       SMBUS READ       42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                     |    |

| 6.2.1       SMBUS WRITE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |                                                     |    |

| 6.2.2 SMBUS READ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |                                                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                     |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |                                                     |    |

| 6.3.1<br>6.3.2 | I <sup>2</sup> C REGISTER WRITE ACCESS<br>I <sup>2</sup> C REGISTER READ ACCESS |    |

|----------------|---------------------------------------------------------------------------------|----|

|                | FC REGISTER READ ACCESS                                                         |    |

|                |                                                                                 |    |

|                | GISTER TYPES                                                                    |    |

|                | ANSPARENT MODE CONFIGURATION REGISTERS                                          |    |

| 7.2.1          | VENDOR ID REGISTER – OFFSET 00h                                                 |    |

| 7.2.2          | DEVICE ID REGISTER – OFFSET 00h                                                 |    |

| 7.2.3          | COMMAND REGISTER – OFFSET 04h                                                   |    |

| 7.2.4          | PRIMARY STATUS REGISTER – OFFSET 04h                                            |    |

| 7.2.5          | REVISION ID REGISTER – OFFSET 08h                                               |    |

| 7.2.6          | CLASS CODE REGISTER – OFFSET 08h                                                |    |

| 7.2.7          | CACHE LINE REGISTER – OFFSET 0Ch                                                |    |

| 7.2.8          | PRIMARY LATENCY TIMER REGISTER – OFFSET 0Ch                                     |    |

| 7.2.9          | HEADER TYPE REGISTER – OFFSET 0Ch                                               |    |

| 7.2.10         | PRIMARY BUS NUMBER REGISTER – OFFSET 18h                                        |    |

| 7.2.11         | SECONDARY BUS NUMBER REGISTER – OFFSET 18h                                      |    |

| 7.2.12         | SUBORDINATE BUS NUMBER REGISTER – OFFSET 18h                                    |    |

| 7.2.13         | SECONDARY LATENCY TIMER REGISTER – OFFSET 18h                                   |    |

| 7.2.14         | I/O BASE ADDRESS REGISTER – OFFSET 1Ch                                          |    |

| 7.2.15         | I/O LIMIT ADDRESS REGISTER – OFFSET 1Ch                                         |    |

| 7.2.16         | SECONDARY STATUS REGISTER – OFFSET 1Ch                                          |    |

| 7.2.17         | MEMORY BASE ADDRESS REGISTER – OFFSET 20h                                       |    |

| 7.2.18         | MEMORY LIMIT ADDRESS REGISTER – OFFSET 20h                                      |    |

| 7.2.19         | PREFETCHABLE MEMORY BASE ADDRESS REGISTER – OFFSET 24h                          |    |

| 7.2.20         | PREFETCHABLE MEMORY LIMIT ADDRESS REGISTER – OFFSET 24h                         |    |

| 7.2.21         | PREFETCHABLE MEMORY BASE ADDRESS UPPER 32-BITS REGISTER – OFFSET 28h            | 56 |

| 7.2.22         | PREFETCHABLE MEMORY LIMIT ADDRESS UPPER 32-BITS REGISTER – OFFSET 2Ch           | 57 |

| 7.2.23         | I/O BASE ADDRESS UPPER 16-BITS REGISTER – OFFSET 30h                            |    |

| 7.2.24         | I/O LIMIT ADDRESS UPPER 16-BITS REGISTER – OFFSET 30h                           |    |

| 7.2.25         | CAPABILITY POINTER REGISTER – OFFSET 34h                                        |    |

| 7.2.26         | INTERRUPT LINE REGISTER – OFFSET 3Ch                                            |    |

| 7.2.27         | INTERRUPT PIN REGISTER – OFFSET 3Ch                                             |    |

| 7.2.28         | BRIDGE CONTROL REGISTER – OFFSET 3Ch                                            |    |

| 7.2.29         | POWER MANAGEMENT CAPABILITY REGISTER – OFFSET 40h                               |    |

| 7.2.30         | POWER MANAGEMENT DATA REGISTER – OFFSET 44h                                     |    |

| 7.2.31         | PPB SUPPORT EXTENSIONS – OFFSET 44h                                             |    |

| 7.2.32         | DATA REGISTER – OFFSET 44h                                                      |    |

| 7.2.33         | MSI CAPABILITY REGISTER – OFFSET 4Ch                                            |    |

| 7.2.34         | MESSAGE CONTROL REGISTER – OFFSET 4Ch                                           |    |

| 7.2.35         | MESSAGE ADDRESS REGISTER – OFFSET 50h                                           |    |

| 7.2.36         | MESSAGE UPPER ADDRESS REGISTER – OFFSET 54h                                     |    |

| 7.2.37         | MESSAGE DATA REGISTER – OFFSET 58h                                              |    |

| 7.2.38         | VENDOR SPECIFIC CAPABILITY REGISTER – OFFSET 64h                                |    |

| 7.2.39         | XPIP CSR0 – OFFSET 68h (Test Purpose Only)                                      |    |

| 7.2.40         | XPIP CSR1 – OFFSET 6Ch (Test Purpose Only)                                      |    |

| 7.2.41         | REPLAY TIME-OUT COUNTER – OFFSET 70h                                            |    |

| 7.2.42         | ACKNOWLEDGE LATENCY TIMER – OFFSET 70h                                          |    |

| 7.2.43         | SWITCH OPERATION MODE – OFFSET 74h (Upstream Port)                              |    |

| 7.2.44         | SWITCH OPERATION MODE – OFFSET 74h (Opsicean Port)                              |    |

| 7.2.45         | XPIP CSR2 – OFFSET 78h                                                          |    |

| 7.2.45         | PHY PARAMETER 1 – OFFSET 78h (Upstream Port Only)                               |    |

| 7.2.40         | PHY PARAMETER 2 – OFFSET 7Ch                                                    |    |

| 7.2.47         | XPIP CSR3 – OFFSET 80h                                                          |    |

| 7.2.48         | $XPIP \ CSR4 - OFFSET 84h \dots$                                                |    |

| 1.2.49         | $AI II \_ CSR4 = OI'I'SE1 0411 \dots$                                           | 04 |

| 7.2.50           | XPIP CSR5 – OFFSET 88h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|