# **ICM7555**

# **General purpose CMOS timer**

Rev. 02 — 3 August 2009

**Product data sheet**

## 1. General description

The ICM7555 is a CMOS timer providing significantly improved performance over the standard NE/SE555 timer, while at the same time being a direct replacement for those devices in most applications. Improved parameters include low supply current, wide operating supply voltage range, low THRESHOLD, TRIGGER, and RESET currents, no crowbarring of the supply current during output transitions, higher frequency performance and no requirement to decouple CONTROL\_VOLTAGE for stable operation.

The ICM7555 is a stable controller capable of producing accurate time delays or frequencies.

In the one-shot mode, the pulse width of each circuit is precisely controlled by one external resistor and capacitor. For a stable operation as an oscillator, the free-running frequency and the duty cycle are both accurately controlled by two external resistors and one capacitor. Unlike the NE/SE555 device, the CONTROL\_VOLTAGE terminal need not be decoupled with a capacitor. The TRIGGER and RESET inputs are active LOW. The output inverter can source or sink currents large enough to drive TTL loads or provide minimal offsets to drive CMOS loads.

### 2. Features

- Exact equivalent in most applications for NE/SE555

- Low supply current: 80 μA (typical)

- Extremely low trigger, threshold, and reset currents: 20 pA (typical)

- High-speed operation: 500 kHz guaranteed

- Wide operating supply voltage range guaranteed 3 V to 16 V over full automotive temperatures

- Normal reset function; no crowbarring of supply during output transition

- Can be used with higher-impedance timing elements than the NE/SE555 for longer time constants

- Timing from microseconds through hours

- Operates in both astable and monostable modes

- Adjustable duty cycle

- High output source/sink driver can drive TTL/CMOS

- Typical temperature stability of 0.005 % / °C at 25 °C

- Rail-to-rail outputs

### **General purpose CMOS timer**

# 3. Applications

- Precision timing

- Pulse generation

- Sequential timing

- Time delay generation

- Pulse width modulation

- Pulse position modulation

- Missing pulse detector

# 4. Ordering information

Table 1. Ordering information

| Type number | Temperature range                                                   | Package |                                                           |         |  |  |  |  |  |

|-------------|---------------------------------------------------------------------|---------|-----------------------------------------------------------|---------|--|--|--|--|--|

|             |                                                                     | Name    | Description                                               | Version |  |  |  |  |  |

| ICM7555CD   | $T_{amb} = 0  ^{\circ}C \text{ to } +70  ^{\circ}C$                 | SO8     | plastic small outline package; 8 leads; body width 3.9 mm | SOT96-1 |  |  |  |  |  |

| ICM7555ID   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |         |                                                           |         |  |  |  |  |  |

| ICM7555CN   | $T_{amb} = 0  ^{\circ}C \text{ to } +70  ^{\circ}C$                 | DIP8    | plastic dual in-line package; 8 leads (300 mil)           | SOT97-1 |  |  |  |  |  |

| ICM7555IN   | $T_{amb} = -40  ^{\circ}\text{C} \text{ to } +85  ^{\circ}\text{C}$ |         |                                                           |         |  |  |  |  |  |

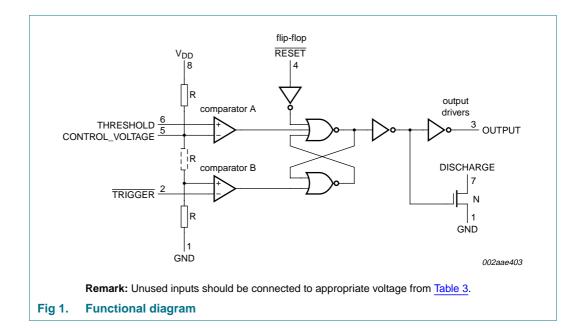

# 5. Functional diagram

**General purpose CMOS timer**

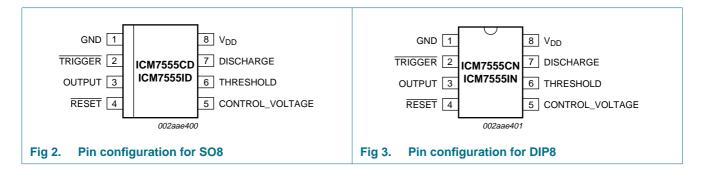

# 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

Table 2. Pin description

| Symbol          | Pin | Description                                |

|-----------------|-----|--------------------------------------------|

| GND             | 1   | supply ground                              |

| TRIGGER         | 2   | start timer input; (active LOW)            |

| OUTPUT          | 3   | timer logic level output                   |

| RESET           | 4   | timer inhibit input; (active LOW)          |

| CONTROL_VOLTAGE | 5   | timing capacitor upper voltage sense input |

| THRESHOLD       | 6   | timing capacitor lower voltage sense input |

| DISCHARGE       | 7   | timing capacitor discharge output          |

| $V_{DD}$        | 8   | supply voltage                             |

# 7. Functional description

Refer to Figure 1 "Functional diagram".

### 7.1 Function selection

Table 3. Function selection

| THRESHOLD voltage                | TRIGGER voltage                     | RESET[1] | OUTPUT | Discharge switch |

|----------------------------------|-------------------------------------|----------|--------|------------------|

| don't care                       | don't care                          | L        | L      | on               |

| > <sup>2</sup> / <sub>3</sub> V+ | > 1/ <sub>3</sub> V+                | Н        | L      | on               |

| $V_{th} < \frac{2}{3} V +$       | $V_{\text{trig}} > \frac{1}{3} V +$ | Н        | stable | stable           |

| don't care                       | < 1/ <sub>3</sub> V+                | Н        | H      | off              |

$<sup>\</sup>begin{tabular}{ll} [1] & \hline {\sf RESET} \ will \ dominate \ all \ other \ inputs; \end{tabular} \hline {\sf TRIGGER} \ will \ dominate \ over \ THRESHOLD. \end{tabular}$

CM7555\_2 © NXP B.V. 2009. All rights reserved.

### **General purpose CMOS timer**

# 8. Limiting values

Table 4. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                | Conditions                           | Min               | Max            | Unit |

|------------------|--------------------------|--------------------------------------|-------------------|----------------|------|

| $V_{DD}$         | supply voltage           |                                      |                   | 18             | V    |

| $V_{I}$          | input voltage            | TRIGGER                              | [ <u>1</u> ] -0.3 | $V_{DD} + 0.3$ | V    |

|                  |                          | CONTROL_VOLTAGE                      | -0.3              | $V_{DD} + 0.3$ | V    |

|                  |                          | THRESHOLD                            | -0.3              | $V_{DD} + 0.3$ | V    |

|                  |                          | RESET                                | -0.3              | $V_{DD} + 0.3$ | V    |

| Io               | output current           |                                      | -                 | 100            | mA   |

| Р                | power dissipation        | T <sub>amb</sub> = 25 °C (still air) | [2][3]            |                |      |

|                  |                          | DIP8 package                         | -                 | 1160           | mW   |

|                  |                          | SO8 package                          | -                 | 780            | mW   |

| T <sub>stg</sub> | storage temperature      |                                      | -65               | +150           | °C   |

| T <sub>sp</sub>  | solder point temperature | soldering 60 s                       | -                 | 300            | °C   |

|                  |                          |                                      |                   |                |      |

<sup>[1]</sup> Due to the SCR structure inherent in the CMOS process used to fabricate these devices, connecting any terminal to a voltage greater than V<sub>DD</sub> + 0.3 V or less than GND – 0.3 V may cause destructive latch-up. For this reason it is recommended that no inputs from external sources not operating from the same power supply be applied to the device before its power supply is established. In multiple systems, the supply of the ICM7555 must be turned on first.

- [2] Above 25 °C, derate at the following rates: DIP8 package at 9.3 mW / °C SO8 package at 6.2 mW / °C

- [3] Refer to Section 11.2 "Power supply considerations" section.

### 9. Characteristics

#### Table 5. Characteristics

$T_{amb}$  = 25 °C unless otherwise specified.

| G                   | •                                |                                                       |              |              |              |        |

|---------------------|----------------------------------|-------------------------------------------------------|--------------|--------------|--------------|--------|

| Sym<br>bol          | Parameter                        | Conditions                                            | Min          | Тур          | Max          | Unit   |

| $V_{DD}$            | supply voltage                   | $T_{min} \leq T_{amb} \leq T_{max}$                   | 3            | -            | 16           | V      |

| $I_{DD}$            | supply current[1]                | $V_{DD} = V_{min}$                                    | -            | 50           | 200          | μΑ     |

|                     |                                  | $V_{DD} = V_{max}$                                    | -            | 180          | 300          | μΑ     |

| Astab               | le mode timing[2][3]             |                                                       |              |              |              |        |

| $\Delta f/f$        | frequency stability              |                                                       | -            | 1.0          | 5.0          | %      |

| $\Delta f/\Delta V$ | frequency variation with voltage |                                                       | -            | 0.1          | 3.0          | %/V    |

| $\Delta f/\Delta T$ | frequency variation with         | $V_{DD} = 5 V$                                        | -            | 50           | -            | ppm/°C |

|                     | temperature[4]                   | V <sub>DD</sub> = 10 V                                | -            | 75           | -            | ppm/°C |

|                     |                                  | V <sub>DD</sub> = 15 V                                | -            | 100          | -            | ppm/°C |

| $V_{I}$             | input voltage                    | TRIGGER: V <sub>DD</sub> = 5 V                        | $0.29V_{DD}$ | $0.31V_{DD}$ | $0.34V_{DD}$ | V      |

|                     |                                  | CONTROL_VOLTAGE: V <sub>DD</sub> = 5 V                | $0.62V_{DD}$ | $0.65V_{DD}$ | $0.67V_{DD}$ | V      |

|                     |                                  | THRESHOLD: V <sub>DD</sub> = 5 V                      | $0.63V_{DD}$ | $0.65V_{DD}$ | $0.67V_{DD}$ | V      |

|                     |                                  | $\overline{RESET}$ : $V_{DD} = V_{min}$ and $V_{max}$ | $0.4V_{DD}$  | $0.7V_{DD}$  | $1.0V_{DD}$  | V      |

|                     |                                  |                                                       |              |              |              |        |

### **General purpose CMOS timer**

**Table 5.** Characteristics ...continued  $T_{amb} = 25 \,^{\circ}C$  unless otherwise specified.

| Sym<br>bol     | Parameter                 | Conditions                                                     | Min   | Тур  | Max | Unit |

|----------------|---------------------------|----------------------------------------------------------------|-------|------|-----|------|

| l <sub>l</sub> | input current             | TRIGGER                                                        |       |      |     |      |

|                |                           | $V_{DD} = V_{trig} = V_{max}$                                  | -     | 50   | -   | pА   |

|                |                           | $V_{DD} = V_{trig} = 5 \text{ V}$                              | -     | 10   | -   | pА   |

|                |                           | $V_{DD} = V_{trig} = V_{min}$                                  | -     | 1    | -   | pА   |

|                |                           | THRESHOLD                                                      |       |      |     |      |

|                |                           | $V_{DD} = V_{th} = V_{max}$                                    | -     | 50   | -   | pА   |

|                |                           | $V_{DD} = V_{th} = 5 \text{ V}$                                | -     | 10   | -   | pА   |

|                |                           | $V_{DD} = V_{th} = V_{min}$                                    | -     | 1    | -   | pА   |

|                |                           | RESET                                                          |       |      |     |      |

|                |                           | $V_{DD} = V_{rst} = V_{max}$                                   | -     | 100  | -   | pА   |

|                |                           | $V_{DD} = V_{rst} = 5 V$                                       | -     | 20   | -   | pА   |

|                |                           | $V_{DD} = V_{rst} = V_{min}$                                   | -     | 2    | -   | pА   |

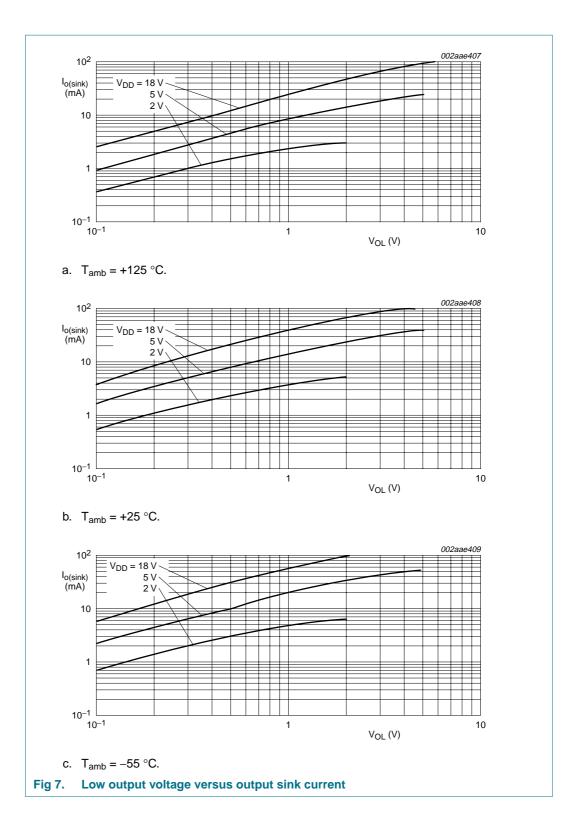

| $V_{OL}$       | LOW-level output voltage  | $V_{DD} = V_{max}$ ; $I_{sink} = 3.2 \text{ mA}$               | -     | 0.1  | 0.4 | V    |

|                |                           | $V_{DD} = 5 \text{ V}; I_{sink} = 3.2 \text{ mA}$              | -     | 0.2  | 0.4 | V    |

| $V_{OH}$       | HIGH-level output voltage | $I_{\text{source}} = -1.0 \text{ mA}$                          |       |      |     |      |

|                |                           | $V_{DD} = V_{max}$                                             | 15.25 | 15.7 | -   | V    |

|                |                           | $V_{DD} = 5 V_{max}$                                           | 4.0   | 4.5  | -   | V    |

| Vo             | output voltage            | DISCHARGE:<br>$V_{DD} = 5 \text{ V; } I_{DIS} = 10 \text{ mA}$ | -     | 0.2  | 0.4 | V    |

| $t_{r(o)}$     | output rise time[4]       | $R_L$ = 10 M $\Omega$ ; $C_L$ = 10 pF; $V_{DD}$ = 5 V          | -     | 45   | 75  | ns   |

| $t_{f(O)}$     | output fall time[4]       |                                                                | -     | 20   | 75  | ns   |

| fosc           | oscillator frequency      | astable mode                                                   | -     | -    | 500 | kHz  |

<sup>[1]</sup> The supply current value is essentially independent of the  $\overline{\text{TRIGGER}}$ , THRESHOLD and  $\overline{\text{RESET}}$  voltages.

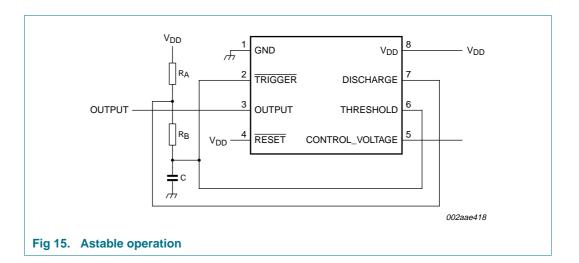

[2] Astable timing is calculated using the following equation:

$$f = \frac{1.38}{(R_A + 2R_B)C}$$

The components are defined in Figure 15.

[3]  $R_A$ ,  $R_B = 1 k\Omega$  to 100  $k\Omega$ ;  $C = 0.1 \mu F$ ; 5  $V < V_{DD} < 15 V$

[4] Parameter is not 100 % tested.

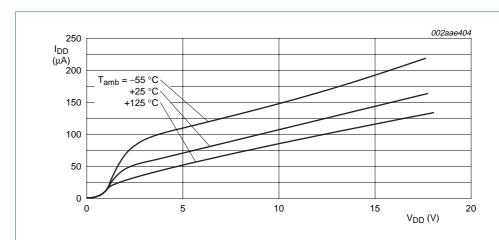

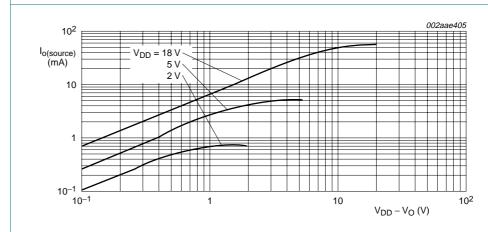

# 10. Typical performance curves

Fig 4. Supply current versus supply voltage

$T_{amb}$  = +25 °C.

Fig 5. High output voltage drop versus output source current

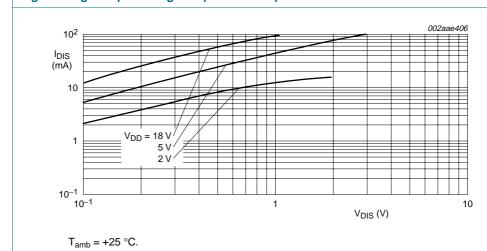

Fig 6. Discharge low output voltage versus discharge sink current

### **General purpose CMOS timer**

### **General purpose CMOS timer**

$\begin{array}{c} 30 & 40 \\ \text{lowest voltage level of } \overline{\text{TRIGGER}} \text{ pulse (\% V}_{\text{DD})} \end{array}$

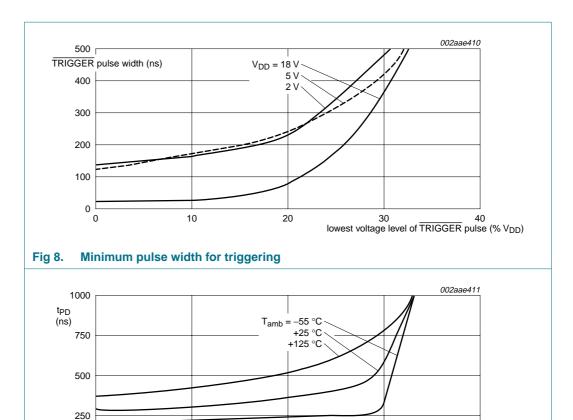

Fig 9. Propagation delay versus voltage level of  $\overline{TRIGGER}$  pulse ( $V_{DD} = 5 \text{ V}$ )

20

10

0

0

### **General purpose CMOS timer**

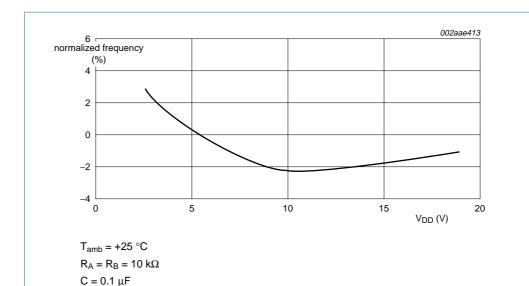

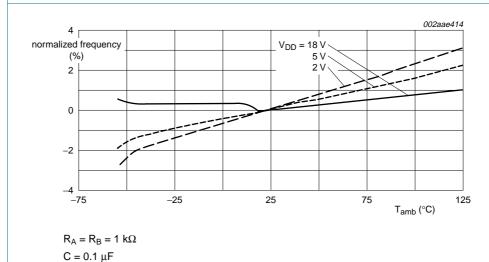

Fig 10. Normalized frequency stability as a function of supply voltage (astable mode)

Fig 11. Normalized frequency stability as a function of temperature (astable mode)

### **General purpose CMOS timer**

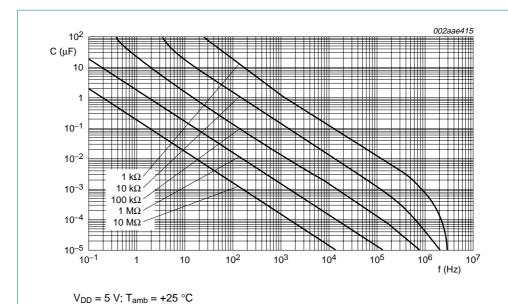

Fig 12. Free-running frequency as a function of  $R_{\rm A}$ ,  $R_{\rm B}$  resistance and external capacitance

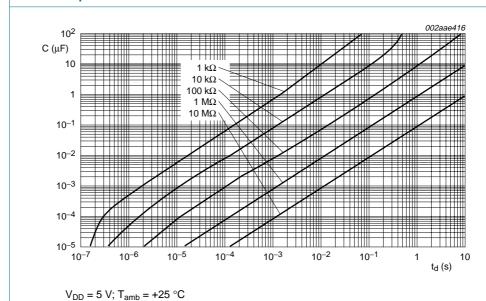

Fig 13. Monostable time delay versus RA resistance and external capacitance

**General purpose CMOS timer**

## 11. Application information

#### 11.1 General

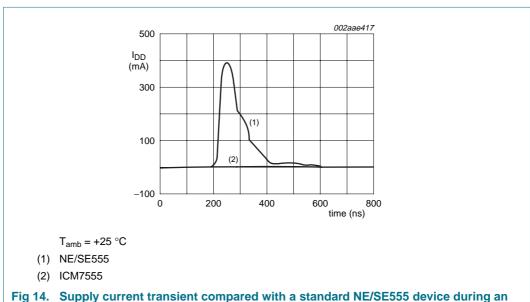

The ICM7555 device is, in most instances, a direct replacement for the NE/SE555 device. However, it is possible to effect economies in the external component count using the ICM7555. Because the NE/SE555 device produces large crowbar currents in the output driver, it is necessary to decouple the power supply lines with a good capacitor close to the device. The ICM7555 device produces no such transients. See Figure 14.

The ICM7555 produces supply current spikes of only 2 mA to 3 mA instead of 300 mA to 400 mA and supply decoupling is normally not necessary. Secondly, in most instances, the CONTROL\_VOLTAGE decoupling capacitors are not required since the input impedance of the CMOS comparators on chip are very high. Thus, for many applications, 2 capacitors can be saved using an ICM7555.

output transition

### 11.2 Power supply considerations

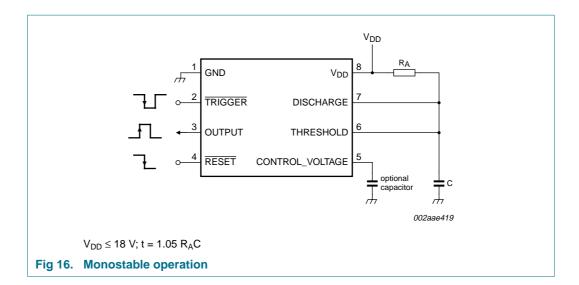

Although the supply current consumed by the ICM7555 device is very low, the total system supply can be high unless the timing components are high-impedance. Therefore, high values for R and low values for C in Figure 15 and Figure 16 are recommended.

### 11.3 Output drive capability

The output driver consists of a CMOS inverter capable of driving most logic families including CMOS and TTL. As such, if driving CMOS, the output swing at all supply voltages will equal the supply voltage. At a supply voltage of 4.5 V or more, the ICM7555 will drive at least 2 standard TTL loads.

ICM7555\_2 © NXP B.V. 2009. All rights reserved.

**General purpose CMOS timer**

### 11.4 Astable operation

If the circuit is connected as shown in Figure 15, it will trigger itself and free run as a multivibrator. The external capacitor charges through  $R_A$  and  $R_B$  and discharges through  $R_B$  only. Thus, the duty cycle ( $\delta$ ) may be precisely set by the ratio of these two resistors. In this mode of operation, the capacitor charges and discharges between  $\frac{1}{3}$   $V_{DD}$  and  $\frac{2}{3}$   $V_{DD}$ . Since the charge rate and the threshold levels are directly proportional to the supply voltage, the frequency of oscillation is independent of the supply voltage.

$$f = \frac{1.38}{(R_A + 2R_B) \times C} \tag{1}$$

$$\delta = \frac{R_A + R_B}{R_A + 2R_B} \tag{2}$$

#### 11.5 Monostable operation

In this mode of operation, the timer functions as a one-shot. Initially, the external capacitor (C) is held discharged by a transistor inside the timer. Upon application of a negative pulse to pin 2,  $\overline{TRIGGER}$ , the internal flip-flop is set, which releases the low-impedance on DISCHARGE; the external capacitor charges and drives the OUTPUT HIGH. The voltage across the capacitor increases exponentially with a time constant  $t=R_AC$ . When the voltage across the capacitor equals  $^2\!\!/_3$  V+, the comparator resets the flip-flop, which in turn discharges the capacitor rapidly and also drives the OUTPUT to its LOW state.  $\overline{TRIGGER}$  must return to a HIGH state before the OUTPUT can return to a LOW state.

#### **General purpose CMOS timer**

### 11.6 Control voltage

The CONTROL\_VOLTAGE terminal permits the two trip voltages for the THRESHOLD and TRIGGER internal comparators to be controlled. This provides the possibility of oscillation frequency modulation in the astable mode, or even inhibition of oscillation, depending on the applied voltage. In the monostable mode, delay times can be changed by varying the applied voltage to the CONTROL\_VOLTAGE pin.

### **11.7 RESET**

The RESET terminal is designed to have essentially the same trip voltage as the standard NE/SE555 device, i.e., 0.6 V to 0.7 V. At all supply voltages it represents an extremely high input impedance. The mode of operation of the RESET function is, however, much improved over the standard NE/SE555 device in that it controls only the internal flip-flop, which in turn controls simultaneously the state of the OUTPUT and DISCHARGE pins. This avoids the multiple threshold problems sometimes encountered with slow falling edges in the NE/SE555 devices.

**General purpose CMOS timer**

# 12. Package outline

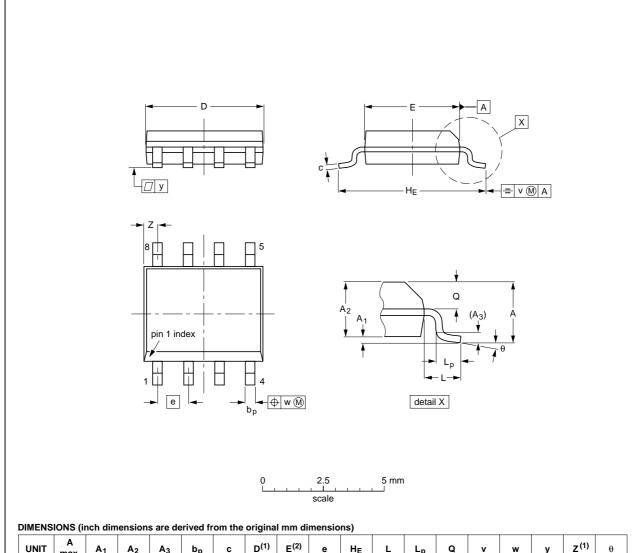

### SO8: plastic small outline package; 8 leads; body width 3.9 mm

SOT96-1

| UNIT   | A<br>max. | A <sub>1</sub> | A <sub>2</sub> | <b>A</b> <sub>3</sub> | bp           | С                | D <sup>(1)</sup> | E <sup>(2)</sup> | е    | HE             | L     | Lp             | Q          | v    | w    | у     | z <sup>(1)</sup> | θ  |

|--------|-----------|----------------|----------------|-----------------------|--------------|------------------|------------------|------------------|------|----------------|-------|----------------|------------|------|------|-------|------------------|----|

| mm     | 1.75      | 0.25<br>0.10   | 1.45<br>1.25   | 0.25                  | 0.49<br>0.36 | 0.25<br>0.19     | 5.0<br>4.8       | 4.0<br>3.8       | 1.27 | 6.2<br>5.8     | 1.05  | 1.0<br>0.4     | 0.7<br>0.6 | 0.25 | 0.25 | 0.1   | 0.7<br>0.3       | 8° |

| inches | 0.069     | 0.010<br>0.004 | 0.057<br>0.049 | 0.01                  |              | 0.0100<br>0.0075 | 0.20<br>0.19     | 0.16<br>0.15     | 0.05 | 0.244<br>0.228 | 0.041 | 0.039<br>0.016 |            | 0.01 | 0.01 | 0.004 | 0.028<br>0.012   | 0° |

#### Notes

- 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included.

- 2. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| INE  |        | REFER  | EUROPEAN  | ISSUE DATE     |                |                                 |  |

|------|--------|--------|-----------|----------------|----------------|---------------------------------|--|

| ION  | IEC    | JEDEC  | JEITA     |                | PROJECTION     | ISSUE DATE                      |  |

| 06-1 | 076E03 | MS-012 |           |                |                | <del>99-12-27</del><br>03-02-18 |  |

|      |        | IEC    | IEC JEDEC | TEC JEDEC JETA | IEC JEDEC JEHA | IEC JEDEC JEHA                  |  |

Fig 17. Package outline SOT96-1 (SO8)

©M7555\_2 © NXP B.V. 2009. All rights reserved.

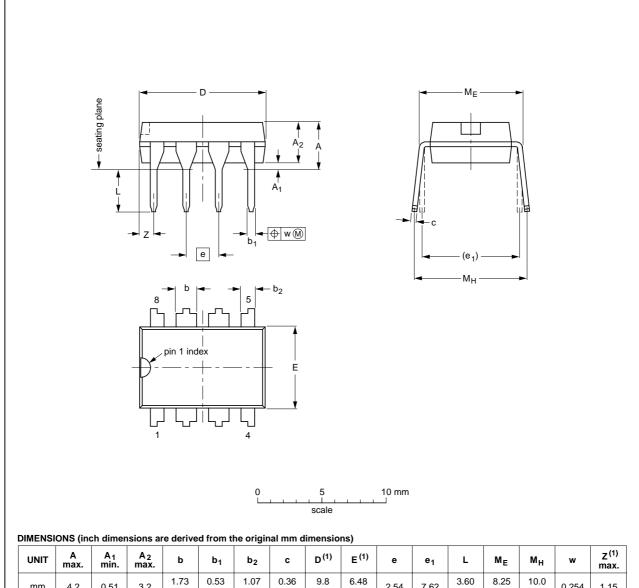

### DIP8: plastic dual in-line package; 8 leads (300 mil)

SOT97-1

| UNIT   | A<br>max. | A <sub>1</sub><br>min. | A <sub>2</sub><br>max. | b              | b <sub>1</sub> | b <sub>2</sub> | С              | D <sup>(1)</sup> | E <sup>(1)</sup> | е    | e <sub>1</sub> | L            | ME           | Мн           | w     | Z <sup>(1)</sup><br>max. |

|--------|-----------|------------------------|------------------------|----------------|----------------|----------------|----------------|------------------|------------------|------|----------------|--------------|--------------|--------------|-------|--------------------------|

| mm     | 4.2       | 0.51                   | 3.2                    | 1.73<br>1.14   | 0.53<br>0.38   | 1.07<br>0.89   | 0.36<br>0.23   | 9.8<br>9.2       | 6.48<br>6.20     | 2.54 | 7.62           | 3.60<br>3.05 | 8.25<br>7.80 | 10.0<br>8.3  | 0.254 | 1.15                     |

| inches | 0.17      | 0.02                   | 0.13                   | 0.068<br>0.045 | 0.021<br>0.015 | 0.042<br>0.035 | 0.014<br>0.009 | 0.39<br>0.36     | 0.26<br>0.24     | 0.1  | 0.3            | 0.14<br>0.12 | 0.32<br>0.31 | 0.39<br>0.33 | 0.01  | 0.045                    |

#### Note

1. Plastic or metal protrusions of 0.25 mm (0.01 inch) maximum per side are not included.

| OUTLINE |        | REFER  | EUROPEAN    | ISSUE DATE |            |                                 |  |

|---------|--------|--------|-------------|------------|------------|---------------------------------|--|

| VERSION | IEC    | JEDEC  | JEDEC JEITA |            | PROJECTION | 1330E DATE                      |  |

| SOT97-1 | 050G01 | MO-001 | SC-504-8    |            |            | <del>99-12-27</del><br>03-02-13 |  |

|         |        |        |             |            |            |                                 |  |

Fig 18. Package outline SOT97-1 (DIP8)

ICM7555\_2 © NXP B.V. 2009. All rights reserved.

**General purpose CMOS timer**

## 13. Soldering of SMD packages

This text provides a very brief insight into a complex technology. A more in-depth account of soldering ICs can be found in Application Note *AN10365 "Surface mount reflow soldering description"*.

### 13.1 Introduction to soldering

Soldering is one of the most common methods through which packages are attached to Printed Circuit Boards (PCBs), to form electrical circuits. The soldered joint provides both the mechanical and the electrical connection. There is no single soldering method that is ideal for all IC packages. Wave soldering is often preferred when through-hole and Surface Mount Devices (SMDs) are mixed on one printed wiring board; however, it is not suitable for fine pitch SMDs. Reflow soldering is ideal for the small pitches and high densities that come with increased miniaturization.

### 13.2 Wave and reflow soldering

Wave soldering is a joining technology in which the joints are made by solder coming from a standing wave of liquid solder. The wave soldering process is suitable for the following:

- Through-hole components

- Leaded or leadless SMDs, which are glued to the surface of the printed circuit board

Not all SMDs can be wave soldered. Packages with solder balls, and some leadless packages which have solder lands underneath the body, cannot be wave soldered. Also, leaded SMDs with leads having a pitch smaller than ~0.6 mm cannot be wave soldered, due to an increased probability of bridging.

The reflow soldering process involves applying solder paste to a board, followed by component placement and exposure to a temperature profile. Leaded packages, packages with solder balls, and leadless packages are all reflow solderable.

Key characteristics in both wave and reflow soldering are:

- Board specifications, including the board finish, solder masks and vias

- · Package footprints, including solder thieves and orientation

- The moisture sensitivity level of the packages

- Package placement

- Inspection and repair

- Lead-free soldering versus SnPb soldering

### 13.3 Wave soldering

Key characteristics in wave soldering are:

- Process issues, such as application of adhesive and flux, clinching of leads, board transport, the solder wave parameters, and the time during which components are exposed to the wave

- Solder bath specifications, including temperature and impurities

CM7555\_2 © NXP B.V. 2009. All rights reserved.

#### **General purpose CMOS timer**

### 13.4 Reflow soldering

Key characteristics in reflow soldering are:

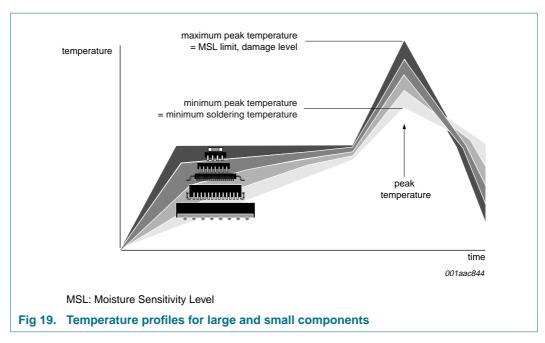

- Lead-free versus SnPb soldering; note that a lead-free reflow process usually leads to higher minimum peak temperatures (see <u>Figure 19</u>) than a SnPb process, thus reducing the process window

- Solder paste printing issues including smearing, release, and adjusting the process window for a mix of large and small components on one board

- Reflow temperature profile; this profile includes preheat, reflow (in which the board is heated to the peak temperature) and cooling down. It is imperative that the peak temperature is high enough for the solder to make reliable solder joints (a solder paste characteristic). In addition, the peak temperature must be low enough that the packages and/or boards are not damaged. The peak temperature of the package depends on package thickness and volume and is classified in accordance with Table 6 and 7

Table 6. SnPb eutectic process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C) |       |  |  |  |  |

|------------------------|---------------------------------|-------|--|--|--|--|

|                        | Volume (mm <sup>3</sup> )       |       |  |  |  |  |

|                        | < 350                           | ≥ 350 |  |  |  |  |

| < 2.5                  | 235                             | 220   |  |  |  |  |

| ≥ 2.5                  | 220                             | 220   |  |  |  |  |

Table 7. Lead-free process (from J-STD-020C)

| Package thickness (mm) | Package reflow temperature (°C)  Volume (mm³) |             |        |  |  |  |  |

|------------------------|-----------------------------------------------|-------------|--------|--|--|--|--|

|                        |                                               |             |        |  |  |  |  |

|                        | < 350                                         | 350 to 2000 | > 2000 |  |  |  |  |

| < 1.6                  | 260                                           | 260         | 260    |  |  |  |  |

| 1.6 to 2.5             | 260                                           | 250         | 245    |  |  |  |  |

| > 2.5                  | 250                                           | 245         | 245    |  |  |  |  |

Moisture sensitivity precautions, as indicated on the packing, must be respected at all times.

Studies have shown that small packages reach higher temperatures during reflow soldering, see Figure 19.

#### **General purpose CMOS timer**

For further information on temperature profiles, refer to Application Note *AN10365* "Surface mount reflow soldering description".

## 14. Soldering of through-hole mount packages

### 14.1 Introduction to soldering through-hole mount packages

This text gives a very brief insight into wave, dip and manual soldering.

Wave soldering is the preferred method for mounting of through-hole mount IC packages on a printed-circuit board.

### 14.2 Soldering by dipping or by solder wave

Driven by legislation and environmental forces the worldwide use of lead-free solder pastes is increasing. Typical dwell time of the leads in the wave ranges from 3 seconds to 4 seconds at 250 °C or 265 °C, depending on solder material applied, SnPb or Pb-free respectively.

The total contact time of successive solder waves must not exceed 5 seconds.

The device may be mounted up to the seating plane, but the temperature of the plastic body must not exceed the specified maximum storage temperature  $(T_{stg(max)})$ . If the printed-circuit board has been pre-heated, forced cooling may be necessary immediately after soldering to keep the temperature within the permissible limit.

### 14.3 Manual soldering

Apply the soldering iron (24 V or less) to the lead(s) of the package, either below the seating plane or not more than 2 mm above it. If the temperature of the soldering iron bit is less than 300  $^{\circ}$ C it may remain in contact for up to 10 seconds. If the bit temperature is between 300  $^{\circ}$ C and 400  $^{\circ}$ C, contact may be up to 5 seconds.

### **General purpose CMOS timer**

## 14.4 Package related soldering information

Table 8. Suitability of through-hole mount IC packages for dipping and wave soldering

| Package                         | Soldering metho | Soldering method        |  |

|---------------------------------|-----------------|-------------------------|--|

|                                 | Dipping         | Wave                    |  |

| CPGA, HCPGA                     | -               | suitable                |  |

| DBS, DIP, HDIP, RDBS, SDIP, SIL | suitable        | suitable <sup>[1]</sup> |  |

| PMFP[2]                         | -               | not suitable            |  |

<sup>[1]</sup> For SDIP packages, the longitudinal axis must be parallel to the transport direction of the printed-circuit board.

### 15. Abbreviations

Table 9. Abbreviations

| Acronym | Description                              |

|---------|------------------------------------------|

| CMOS    | Complementary Metal-Oxide Semiconductors |

| TTL     | Transistor-Transistor Logic              |

| SCR     | Silicon-Controlled Rectifier             |

<sup>[2]</sup> For PMFP packages hot bar soldering or manual soldering is suitable.

### **General purpose CMOS timer**

# 16. Revision history

### Table 10. Revision history

ICM7555\_1

19940831

| Document ID    | Release date                                                                                                                                | Data sheet status                                                                                                            | Change notice                                  | Supersedes                                  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------------------------------------------|--|

| ICM7555_2      | 20090803                                                                                                                                    | Product data sheet                                                                                                           | Onange node                                    | ICM7555_1                                   |  |

|                |                                                                                                                                             |                                                                                                                              | - 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1        |                                             |  |

| Modifications: | <ul> <li>The format of this data sheet has been redesigned to comply with the new identity guidelines of NXP<br/>Semiconductors.</li> </ul> |                                                                                                                              |                                                |                                             |  |

|                | <ul> <li>Legal texts have been adapted to the new company name where appropriate.</li> </ul>                                                |                                                                                                                              |                                                |                                             |  |

|                | <ul> <li>Provided separate pinning diagrams for SO8 and DIP8 packages (<u>Figure 2</u> and <u>Figure 3</u>,<br/>respectively).</li> </ul>   |                                                                                                                              |                                                |                                             |  |

|                | <ul> <li>Added <u>Table</u></li> </ul>                                                                                                      | 2 "Pin description".                                                                                                         |                                                |                                             |  |

|                | <ul> <li>Table 4 "Limi</li> </ul>                                                                                                           | ting values":                                                                                                                |                                                |                                             |  |

|                |                                                                                                                                             | $V_{TRIG},V_{CV},V_{TH},V_{RST}$ are rescolumn).                                                                             | eplaced with V <sub>I</sub> (specific pin na   | ames are now noted under                    |  |

|                |                                                                                                                                             | arameter "P <sub>DMAX</sub> , maximum<br>ı values given).                                                                    | power dissipation" replaced v                  | vith "P, power dissipation" (only           |  |

|                | <ul><li>Symbol/p</li></ul>                                                                                                                  | arameter "T <sub>STG</sub> , storage ter                                                                                     | nperature range" replaced with                 | h "T <sub>stg</sub> , storage temperature". |  |

|                | <ul> <li>Symbol c</li> </ul>                                                                                                                | hanged from "T <sub>SOLD</sub> " to "T <sub>sp</sub>                                                                         | , solder point temperature"                    |                                             |  |

|                | • Table 5 "Cha                                                                                                                              | racteristics":                                                                                                               |                                                |                                             |  |

|                | <ul> <li>Symbols</li> </ul>                                                                                                                 | $\Delta f/f$ , $\Delta f/\Delta V$ , $\Delta f/\Delta T$ , have been                                                         | added for Astable mode timir                   | ng.                                         |  |

|                |                                                                                                                                             | $V_{TRIG},V_{CV},V_{TH},V_{RST}$ are rescolumn).                                                                             | eplaced with V <sub>I</sub> (specific pin na   | ames are now noted under                    |  |

|                | <ul> <li>Symbols column).</li> </ul>                                                                                                        | I <sub>TRIG</sub> , I <sub>TH</sub> , I <sub>RST</sub> are replaced                                                          | with I <sub>I</sub> (specific pin names are    | e now noted under Conditions                |  |

|                |                                                                                                                                             | arameter "V <sub>DIS</sub> , discharge on the conditions of the conditions" are also are | utput voltage" changed to " $V_o$ column).     | , output voltage" (specific pin             |  |

|                | <ul><li>Symbol/p</li></ul>                                                                                                                  | arameter "t <sub>R</sub> , rise time of ou                                                                                   | tput" changed to "tr(o), output                | rise time".                                 |  |

|                | <ul><li>Symbol/p</li></ul>                                                                                                                  | arameter "t <sub>F</sub> , fall time of out                                                                                  | put" changed to "t <sub>f(o)</sub> , output fa | all time".                                  |  |

|                | <ul><li>Symbol "F</li></ul>                                                                                                                 | -<br>MAX" changed to "fosc, oscil                                                                                            | lator frequency".                              |                                             |  |

|                | <ul> <li>Section 11.4</li> </ul>                                                                                                            | "Astable operation": change                                                                                                  | ed symbol for duty cycle from                  | "D" to "δ".                                 |  |

|                | <ul> <li>Added <u>Section</u></li> </ul>                                                                                                    | on 12 "Package outline".                                                                                                     |                                                |                                             |  |

|                | <ul> <li>Added solde</li> </ul>                                                                                                             | ring information.                                                                                                            |                                                |                                             |  |

|                | <ul> <li>Added Section</li> </ul>                                                                                                           | on 15 "Abbreviations".                                                                                                       |                                                |                                             |  |

Product specification

ECN 853-1192 13721 dated 1994 Aug 31

#### **General purpose CMOS timer**

## 17. Legal information

#### 17.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 17.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

### 17.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental

damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

### 17.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

### 18. Contact information

For more information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: salesaddresses@nxp.com

CM7555\_2 © NXP B.V. 2009. All rights reserved.

### **General purpose CMOS timer**

## 19. Contents

| 1                      | General description                          | . 1             |

|------------------------|----------------------------------------------|-----------------|

| 2                      | Features                                     | . 1             |

| 3                      | Applications                                 | . 2             |

| 4                      | Ordering information                         | . 2             |

| 5                      | Functional diagram                           | . 2             |

| 6                      | Pinning information                          | . 3             |

| 6.1                    | Pinning                                      | . 3             |

| 6.2                    | Pin description                              | . 3             |

| 7                      | Functional description                       | . 3             |

| 7.1                    | Function selection                           | . 3             |

| 8                      | Limiting values                              | . 4             |

| 9                      | Characteristics                              | . 4             |

| 10                     | Typical performance curves                   | . 6             |

| 11                     | Application information                      | 11              |

| 11.1                   | General                                      | 11              |

| 11.2                   | Power supply considerations                  | 11              |

| 11.3                   | Output drive capability                      | 11              |

| 11.4                   | Astable operation                            |                 |

| 11.5                   | Monostable operation                         | 12              |

| 11.6                   | Control voltage                              | 13              |

| 11.7                   | RESET                                        | 13<br><b>14</b> |

| 12                     | Package outline                              |                 |

| 13                     | Soldering of SMD packages                    | 16              |

| 13.1                   | Introduction to soldering                    | 16              |

| 13.2<br>13.3           | Wave and reflow soldering                    | 16<br>16        |

| 13.3<br>13.4           | Wave soldering                               | 17              |

| 14                     | Soldering of through-hole mount packages .   | 18              |

| 1 <del>4</del><br>14.1 | Introduction to soldering through-hole mount | 10              |

| 14.1                   | packages                                     | 18              |

| 14.2                   | Soldering by dipping or by solder wave       | 18              |

| 14.3                   | Manual soldering                             | 18              |

| 14.4                   | Package related soldering information        | 19              |

| 15                     | Abbreviations                                | 19              |

| 16                     | Revision history                             | 20              |

| 17                     | Legal information                            | 21              |

| 17.1                   | Data sheet status                            | 21              |

| 17.2                   | Definitions                                  | 21              |

| 17.3                   | Disclaimers                                  | 21              |

| 17.4                   | Trademarks                                   | 21              |

| 18                     | Contact information                          | 21              |

| 19                     | Contents                                     | 22              |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.