Click here to ask an associate for production status of specific part numbers.

# 4.8V<sub>IN</sub>, 1.5A High-Efficiency, Ultra-Small Buck Converter

## **MAX77324**

## **General Description**

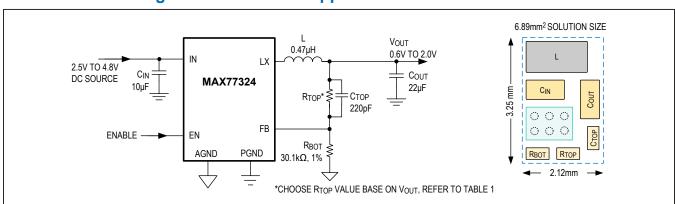

The MAX77324 is a single channel high-efficiency synchronous step-down (buck) converter capable of delivering up to 1.5A of current. With a 6.89mm<sup>2</sup> total solution size, up to 93% efficiency, and 40µA quiescent current, it is optimized for portable space constrained battery-operated applications.

The device operates over a 2.5V to 4.8V input voltage range to support Li+ battery powered applications. The output voltage is adjustable from 0.6V to 2V, with a better than 2% accuracy over the whole temperature range. The device uses constant-on-time PWM control scheme. A nominal 2MHz switching frequency reduces the overall solution footprint by use of small 0603 inductor. An automatic SKIP mode is also implemented to improve the light-load efficiency for MAX77324EWTAD+. MAX77324GEWTAD+ operates in PWM mode for all load conditions. The device provides low output voltage ripple, excellent line and load regulation, and transient response. A dedicated enable pin allows for simple hardware control.

Built-in undervoltage lockout (UVLO), soft-start, active output discharge, cycle-by-cycle short-circuit, and thermal shutdown protections insure safe operations under abnormal operating conditions.

The device is available in a space-saving 1.22mm x 0.85mm, 6-bump wafer-level package (WLP).

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- 1.5A Output Current Step-down Converter

- 2.5V to 4.8V V<sub>IN</sub> Range

- 0.6V to 2V Adjustable VOLIT Range, ±2% Accuracy

- MAX77324EWTAD+

- Skip Mode for High Light-Load Efficiency

- · 40µA Quiescent Current

- MAX77324GEWTAD+

- · PWM Mode Only

- 93% Peak Efficiency (3.8V<sub>IN</sub>, 1.8V<sub>OUT</sub>)

- 1µA Shutdown Current

- 2MHz Nominal Switching Frequency

- Enable Pin for Direct Hardware Control

- Cycle-by-Cycle Inductor Current Limit

- UVLO, Soft-Start, Active Output Discharge, Short-Circuit, and Thermal Shutdown Protections

- 1.22mm x 0.85mm, 6-Bump WLP

- 6.89mm<sup>2</sup> Total Solution Area

- Uses Small 0603 0.47µH Inductor

# **Applications**

- 1-Cell Battery Powered Equipment

- Portable/Wearables

- Internet of Things (IoT) Devices

- Space Constrained Equipment

# 1-Cell to Core Voltage Buck Converter Application Circuit

19-100206; Rev 3; 4/23

# 4.8V<sub>IN</sub>, 1.5A High-Efficiency, Ultra-Small Buck Converter

#### **Absolute Maximum Ratings**

| V <sub>IN</sub> to PGND         | 0.3V to 5.5V                  |

|---------------------------------|-------------------------------|

| EN to AGND                      | 0.3V to V <sub>IN</sub> +0.3V |

| PGND to AGND                    | 0.3V to +0.3V                 |

| FB to AGND                      | 0.3V to V <sub>IN</sub> +0.3V |

| LX Continuous Current (Note 1)  | 1.6A <sub>RMS</sub>           |

| Continuous Power Dissipation (M | ultilayer Board,              |

$T_A = +70^{\circ}C$ ) (derate 10.51mW/°C above +70°C) ......841mW

| 40°C to +85°C  |

|----------------|

| +150°C         |

| 40°C to +150°C |

| +260°C         |

|                |

Note 1: LX has internal clamp diodes to PGND and V<sub>IN</sub>. Applications that forward bias these diodes should not exceed the ICs package power dissipation limits.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Information**

#### **6 WLP**

| Package Code                           | W60H1+1                        |

|----------------------------------------|--------------------------------|

| Outline Number                         | 21-100206                      |

| Land Pattern Number                    | Refer to Application Note 1891 |

| Thermal Resistance, Four-Layer Board:  |                                |

| Junction to Ambient (θ <sub>JA</sub> ) | 95.15°C/W                      |

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN} = 3.8V, V_{FB} = 0.6V, typicals are at T_A = +25^{\circ}C$ . Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range  $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$  are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                            | SYMBOL                 | CONDITIONS                                             | MIN   | TYP  | MAX   | UNITS |  |

|--------------------------------------|------------------------|--------------------------------------------------------|-------|------|-------|-------|--|

| Input Voltage Range                  | V <sub>IN</sub>        |                                                        | 2.5   |      | 4.8   | V     |  |

| Input Undervoltage                   | V <sub>IN_UVLO_R</sub> | V <sub>IN</sub> rising                                 | 2.605 | 2.65 | 2.695 |       |  |

| Lockout                              | V <sub>IN_UVLO_F</sub> | V <sub>IN</sub> falling                                | 2.25  | 2.3  | 2.35  | V     |  |

| Shutdown Supply<br>Current           | I <sub>SHDN_85C</sub>  | EN = LOW, T <sub>A</sub> = -40°C to +85°C              |       | 1    |       |       |  |

|                                      | I <sub>SHDN_25C</sub>  | EN = LOW, T <sub>A</sub> = +25°C                       | -1    | +0.1 | +1    | μA    |  |

| Supply Quiescent<br>Current (Note 4) | I <sub>Q_SKIP</sub>    | No switching, no load, leakage from EN is not included |       | 40   |       | μA    |  |

| FB Voltage Accuracy                  | V <sub>FB</sub>        | No load, PWM mode                                      | 0.588 | 0.6  | 0.612 | V     |  |

| FB Input Current                     | I <sub>FB</sub>        |                                                        | -0.3  |      | +0.3  | μA    |  |

# **Electrical Characteristics (continued)**

$(V_{IN} = 3.8V, V_{FB} = 0.6V, typicals are at T_A = +25^{\circ}C$ . Limits are 100% production tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range  $(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$  are guaranteed by design and characterization, unless otherwise noted.)

| PARAMETER                             | SYMBOL                              | CONDITIONS                                                                                                          | MIN  | TYP   | MAX  | UNITS |

|---------------------------------------|-------------------------------------|---------------------------------------------------------------------------------------------------------------------|------|-------|------|-------|

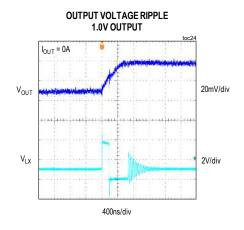

| Output Voltage Ripple                 | V <sub>OUT_PP_SKIP</sub>            | C <sub>OUT</sub> = 8μF (derated capacitance), skip region of operation V <sub>OUT</sub> = 1.2V (Note 2, Note 4)     |      | 20    |      | - mV  |

| Output voltage Ripple                 | V <sub>OUT_PP_PWM</sub>             | C <sub>OUT</sub> = 8μF (derated capacitance), PWM region of operation (Note 2)                                      |      | 10    |      | mv    |

| Line Regulation                       | V <sub>LINE</sub>                   | V <sub>IN</sub> = 2.5V to 4.8V                                                                                      |      | 0.2   |      | %/V   |

| Load Regulation                       | $V_{LOAD}$                          | (Note 2)                                                                                                            |      | 0.185 |      | %/A   |

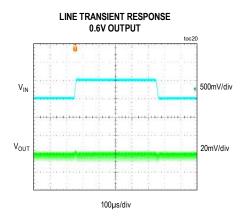

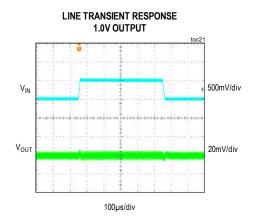

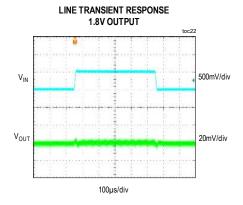

| Line Transient Response               | V <sub>OS1</sub> , V <sub>US1</sub> | $I_{OUT}$ = 750mA, $V_{IN}$ changes from 3.4V to 2.9V in 25µs (20mV/µs), L = 0.47µH, $C_{OUT\_NOM}$ = 22µF (Note 2) |      | 30    |      | mV    |

| Load Transient<br>Response            | V <sub>OS2</sub> , V <sub>US2</sub> | I <sub>OUT</sub> changes from 0A to 750mA in 6μs,<br>L = 0.47μH, C <sub>OUT_NOM</sub> = 22μF (Note 2)               |      | 30    |      | mV    |

| Soft-Start Slew Rate                  |                                     | Regulated at FB pin, V <sub>OUT</sub> = 0.6V, see the<br>Soft-Start section for more details (Note 2)               |      | 2.34  |      | mV/μs |

| Peak Current Limit                    | I <sub>LIM_PEAK</sub>               |                                                                                                                     | 2.63 | 3.00  | 3.37 | А     |

| Valley Current Limit                  | I <sub>LIM_VALLEY</sub>             |                                                                                                                     |      | 1.1   |      | А     |

| NMOS Zero-Crossing<br>Threshold       | I <sub>ZX</sub>                     | Skip region of operation (Note 4)                                                                                   |      | 30    |      | mA    |

| High-Side PMOS ON Resistance          | R <sub>DSON-HS</sub>                | IN to LX, I <sub>TEST</sub> = -150mA                                                                                |      | 100   |      | mΩ    |

| Low-Side NMOS ON<br>Resistance        | R <sub>DSON_LS</sub>                | LX to PGND, I <sub>TEST</sub> = 150mA                                                                               |      | 50    |      | mΩ    |

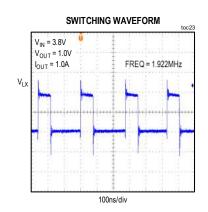

| Switching Frequency                   | f <sub>SW</sub>                     | V <sub>OUT</sub> = 1V, I <sub>OUT</sub> = 1A                                                                        |      | 2     |      | MHz   |

| Turn-On Delay Time                    | ton_dly                             | From EN asserting to LX switching (Note 2)                                                                          |      | 220   |      | μs    |

| Minimum Effective Output Capacitance  | C <sub>EFF_MIN</sub>                | 0mA ≤ I <sub>OUT</sub> ≤ 1.5A (Note 2)                                                                              | 8    |       |      | μF    |

| Output Active Discharge<br>Resistance | R <sub>DISCHG</sub>                 | Resistance from LX to PGND, EN = 0V                                                                                 |      | 100   |      | Ω     |

| 17/1 1 2 :                            | I <sub>LK 25C</sub>                 | V <sub>LX</sub> = 0V or 4.8V, T <sub>A</sub> = +25°C                                                                | -1   | 0.1   | +1   |       |

| LX Leakage Current                    | I <sub>LK</sub> 85C                 | V <sub>LX</sub> = 0V or 4.8V, T <sub>A</sub> = +85°C (Note 3)                                                       |      | 1     |      | μA    |

| Thermal Shutdown                      | T <sub>SHDN</sub>                   | Rising, 15°C hysteresis                                                                                             |      | 165   |      | °C    |

| EN Logic High Threshold               | V <sub>EN_HI</sub>                  | T <sub>A</sub> = +25°C                                                                                              | 1.2  |       |      | V     |

| EN Logic Low Threshold                | V <sub>EN_LO</sub>                  | T <sub>A</sub> = +25°C                                                                                              |      |       | 0.4  | V     |

| EN Pulldown Resistance                | R <sub>PD</sub>                     | Pulldown resistance from EN to AGND                                                                                 | 250  | 500   | 1000 | kΩ    |

Note 2: Guaranteed by design. Not production tested.

Note 3: Guaranteed by ATE characterization. Not directly tested in production.

Note 4: Not applicable to MAX77324GEWTAD+.

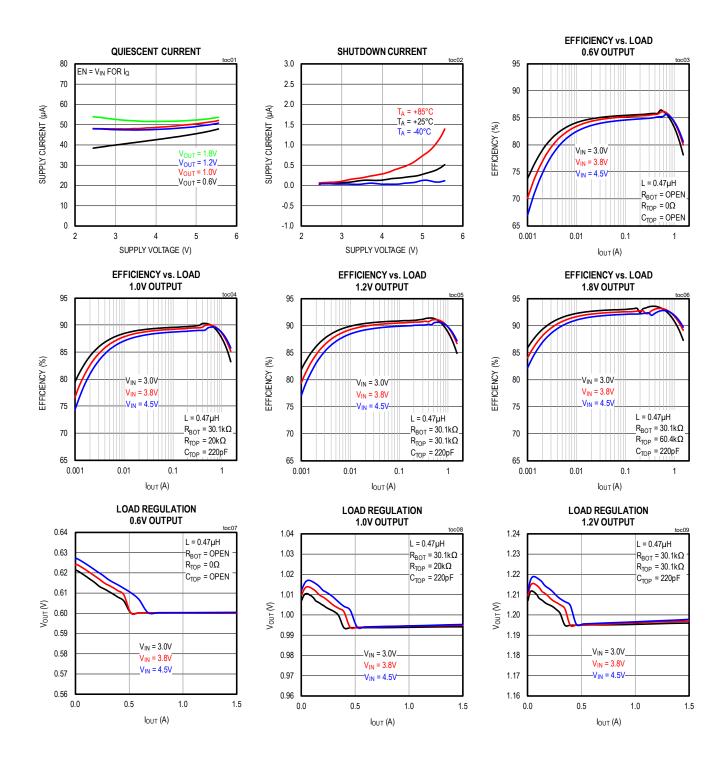

#### **Typical Operating Characteristics**

$(V_{IN} = +3.8V, T_A = +25^{\circ}C, unless otherwise noted. Inductor part number: GLULKR4701A. The data collected is for MAX77324EWTAD+).$

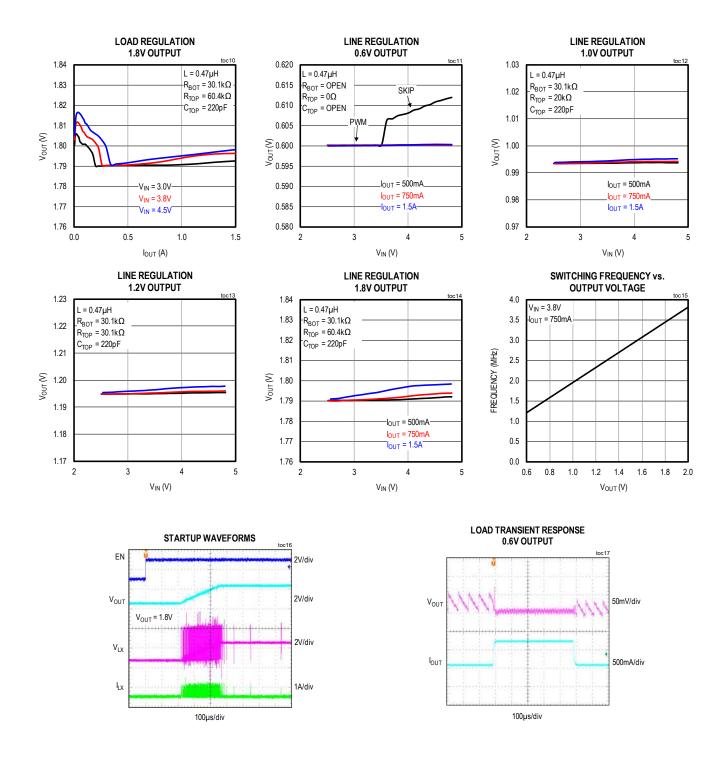

# **Typical Operating Characteristics (continued)**

$(V_{IN} = +3.8V, T_A = +25^{\circ}C, unless otherwise noted. Inductor part number: GLULKR4701A. The data collected is for MAX77324EWTAD+).$

# **Typical Operating Characteristics (continued)**

$(V_{IN} = +3.8V, T_A = +25^{\circ}C, unless otherwise noted. Inductor part number: GLULKR4701A. The data collected is for MAX77324EWTAD+).$

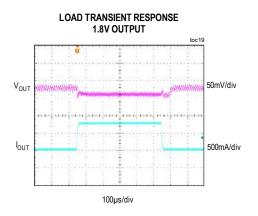

# LOAD TRANSIENT RESPONSE 1.0V OUTPUT toc 18 Vout |out | 500mA/div 100µs/div

# **Typical Operating Characteristics (continued)**

$(V_{IN} = +3.8V, T_A = +25^{\circ}C, unless otherwise noted. Inductor part number: GLULKR4701A. The data collected is for MAX77324EWTAD+).$

# 1.0V OUTPUT SHORT APPLIED RECOVERY Vout HICCUP/RETRY 500mV/div

SHORT-CIRCUIT HICCUP AND RECOVERY

1A/div 100µs/div

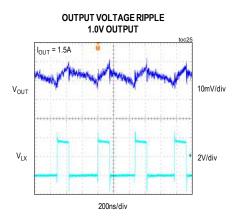

# **Pin Configuration**

# **Pin Description**

| PIN | NAME | FUNCTION                                                                                                                                                                                     |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1  | IN   | Power Input. Bypass to PGND with a 10µF ceramic capacitor.                                                                                                                                   |

| A2  | LX   | Buck Switching Node                                                                                                                                                                          |

| A3  | PGND | Power Ground. Connect to AGND on the PCB.                                                                                                                                                    |

| B1  | EN   | Active-High Buck Enable Input. An $500k\Omega$ internal pulldown resistance to AGND. Drive EN low to disable the device. Drive EN high to enable the device.                                 |

| B2  | AGND | Analog Ground. Connect to PGND on the PCB.                                                                                                                                                   |

| В3  | FB   | Feedback Input. Connect FB to the center tap of an external resistor-divider from the output to AGND to set the output voltage. See the Setting the Output Voltage section for more details. |

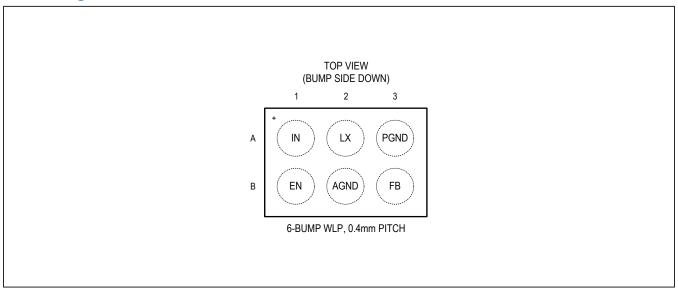

#### **Simplified Block Diagram**

#### **Detailed Description**

The MAX77324 is a high-efficiency synchronous stepdown converter with integrated MOSFETs that operates over a 2.5V to 4.8V input voltage range. The device supports up to 1.5A of load current. The device uses external feedback resistors to set the output between 0.6V to 2.0V.

The device automatically transitions between PWM and SKIP modes of operation when the load condition changes for MAX77324EWTAD+. The part always stays in PWM mode for MAX77324GEWTAD+. SKIP mode improves system light-load efficiency, while PWM mode maintains a constant-on-time switching. In SKIP mode, the device draws only 40µA of quiescent current from the supply input. In shutdown mode, the current consumption is reduced to less than 1µA.

An internal synchronous rectifier improves efficiency and eliminates the need for an external Schottky freewheeling diode. On-chip current sensing uses the on-resistance of the internal MOSFETs, eliminating current-sensing resistors and improving efficiency.

A soft-start voltage ramp reduces inrush current during startup. The enable (EN) pin turns on/off the device.

#### **Buck Converter Control Scheme**

The device uses Maxim's proprietary Quick-PWM<sup>™</sup> quick-response, constant-on-time PWM control scheme. This control scheme handles wide input/output voltage ratios with ease and provides immediate response to load

Quick-PWM is a trademark of Maxim Integrated Products, Inc.

transients, while maintaining a pseudo constant switching frequency.

During the first half of the switching cycle (on-time), current ramps up through the inductor, sourcing current to the output, and storing energy in a magnetic field.

During the second half of the switching cycle (off-time), the internal high-side MOSFET turns off and the internal low-side MOSFET turns on. The inductor releases the stored energy as its current ramps down and provides current to the output. The output capacitor stores a charge when the inductor current exceeds the load current and discharges when the inductor current is lower than load current, smoothing the voltage across the load.

#### **Enable Control (EN)**

Raise EN above  $V_{\mbox{EN\_HI}}$  (1.2V min) to enable the buck converter. Lower EN below VEN\_LO (0.4V max) to disable the buck.

Whenever the buck is enabled and  $V_{IN}$  is higher than  $V_{IN\_UVLO\_R}$ , the output voltage soft-starts. Soft-start avoids excessive supply inrush current and prevents supply voltage drop.

Driving EN low disables the switching and the output is discharged with a typical discharge resistor of  $100\Omega$  from FB pin to PGND. The same happens when the device gets disabled by thermal shutdown or when input UVLO triggers.

#### Shutdown Mode

Pulling the EN pin low causes the device to enter shutdown mode. In this mode, the device consumes less than  $1\mu$ A. In shutdown mode, the LX pin is tied to PGND through the  $100\Omega$  active discharge resistor.

#### **Current Sense and Current Limit**

The current-sense circuit amplifies the current-sense voltage generated by the high-side MOSFET's on-resistance and the inductor current ( $R_{DS(ON)} \times I_L$ ).

The internal high-side MOSFET has a current limit of 3A (typ). If the current flowing out of LX exceeds this maximum, the high-side MOSFET turns off and the low-side MOSFET turns on. This lowers the duty cycle and causes the output voltage to droop until the current limit is no longer exceeded. There is also a low-side MOSFET zero-crossing current threshold of 30mA (typ) under skip region of operation, to protect the device from current flowing into LX. If the current in the low-side MOSFET falls below 30mA, the low-side MOSFET turns off, and the inductor current continues to flow through the high-side MOSFET body diode back to the input until the beginning of the next cycle, or until the inductor current drops to zero.

#### **SKIP/PWM Operation**

The device automatically transitions from SKIP to fixed frequency operation as load current increases for MAX77324EWTAD+. The part always stays in PWM mode for MAX77324GEWTAD+.

In the PWM region of operation, the device operates with a nominal switching frequency of 2MHz. In the SKIP region, the device skips pulses at light loads for high efficiency. The advantage of the SKIP mode is higher efficiency at light loads because of the lower quiescent current drawn from the supply.

#### **Protection Features**

#### **Undervoltage Lockout (UVLO)**

The device supports an UVLO feature that prevents operations in case of low input voltage conditions. Regardless of the EN pin status, the device is disabled until the input voltage  $V_{\mbox{\footnotesize{IN}}}$  rises above the  $V_{\mbox{\footnotesize{IN}}}$  UVLO\_R threshold or  $V_{\mbox{\footnotesize{IN}}}$  falls below the  $V_{\mbox{\footnotesize{IN}}}$  UVLO\_F threshold.

Operations are halted until this condition is resolved.

#### Soft-Start

When starting up the device, the bias circuitry must be enabled and provided with adequate time to settle.

The bias circuitry is guaranteed to settle within 220 $\mu$ s, then the BUCK converter's soft-start operation begins. During the soft-start period, the ramping-up slew rate is regulated at the FB pin (typical 2.34mV/ $\mu$ s). To calculate the soft-start slew rate at V<sub>OUT</sub>, use the following equation:

$$SR_{SS\_VOUT} = \frac{R_{TOP} + R_{BOT}}{R_{BOT}} \times SR_{SS\_FB}$$

To calculate the soft-start time, use the following equation:

$$t_{SS} = \frac{v_{OUT}}{sr_{SS \ vout}}$$

The soft-start feature limits the inrush current during startup.

#### **Pre-Bias Output Startup**

The device supports starting up into a pre-biased output. If the output is at a pre-biased voltage, which is less than the target output voltage, the device ramps up the output voltage monotonically at the preset 2.34mV/µs (typ) FB slew-rate from the pre-biased level to the target level. If the output is at a pre-biased voltage which exceeds the target output voltage, no switching happens during the soft-start period.

#### **Output Active Discharge**

The device provides an internal  $100\Omega$  resistor from LX to PGND for output active discharge function. The internal resistor discharges the energy stored in the output capacitor to GND whenever the converter is disabled.

#### **Over-Current Protection (OCP)**

The device features a robust OCP scheme that protects the device and inductor under overload and output short-circuit conditions. A cycle-by-cycle peak current limit turns off the high-side MOSFET and turns on the low-side MOSFET whenever the high-side MOSFET current exceeds the internal peak current limit. The low-side MOSFET remains on until the inductor current reduces to the valley current limit. After that, the high-side MOSFET is turned on again and the cycle repeats.

The buck stops switching if eight consecutive on-times are ended by current limit. After switching stops, the buck waits for 8µs before attempting to soft-start again. This prevents inductor current from increasing uncontrollably due to the short-circuited output.

#### **Thermal Shutdown**

Thermal protection limits total power dissipation and protects the device from damage in case of an overload or short-circuit condition. The device has a thermal protection circuit which monitors temperature on the die. If the die temperature exceeds 165°C (T<sub>SHDN</sub>), a thermal shutdown event is initiated and the buck is disabled. The active discharge resistor is enabled when the device is disabled through thermal shutdown. After the thermal shutdown, if the die temperature reduces by 15°C, the buck is re-enabled.

#### **Applications Information**

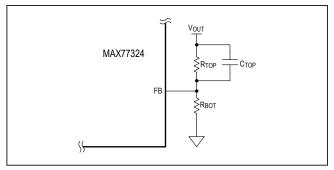

#### **Setting the Output Voltage**

The device uses resistors to set the output voltage between 0.6V and 2V. Connect a resistor divider between V<sub>OUT</sub>, FB, and AGND as shown in Figure 1. Choose R<sub>BOT</sub> (FB to AGND) to be less than or equal to  $30k\Omega$ . One percent accuracy resistors are highly recommended to keep the accuracy of V<sub>OUT</sub>. Calculate the value of R<sub>TOP</sub> (V<sub>OUT</sub> to FB) for a desired output voltage with Equation 1.

#### Equation 1:

$$R_{TOP} = R_{BOT} \times \left[ \frac{V_{OUT}}{V_{FB}} - 1 \right]$$

where  $V_{FB}$  is 0.6V and  $V_{OUT}$  is the desired output voltage.

$C_{\mathsf{TOP}}$  is to maintain the stability of the device. Suggest  $C_{\mathsf{TOP}}$  to be 220pF for the full operation range of the device.

#### **Enable the Device**

The device is enabled by raising EN above  $V_{EN\_HI}$  (1.2V min).

Table 1. Set the Output Voltage

| V <sub>OUT</sub> (V) | R <sub>TOP</sub> (kΩ) | R <sub>BOT</sub> (kΩ) | C <sub>TOP</sub> (PF) |

|----------------------|-----------------------|-----------------------|-----------------------|

| 0.6                  | Short                 | Open                  | Open                  |

| 0.85                 | 12.4                  | 30.1                  | 220                   |

| 0.9                  | 15                    | 30.1                  | 220                   |

| 0.95                 | 17.8                  | 30.1                  | 220                   |

| 1.0                  | 20                    | 30.1                  | 220                   |

| 1.1                  | 24.8                  | 30.1                  | 220                   |

| 1.2                  | 30.1                  | 30.1                  | 220                   |

| 1.35                 | 37.4                  | 30.1                  | 220                   |

| 1.5                  | 45.3                  | 30.1                  | 220                   |

| 1.8                  | 60.4                  | 30.1                  | 220                   |

| 2.0                  | 69.8                  | 30.1                  | 220                   |

Figure 1. Setting the Output Voltage for MAX77324

#### **Self-Enabled Operations**

Automatic self-enabling operation is possible with the device. Tying the EN pin directly to  $V_{IN}$  enables the device as soon as  $V_{IN}$  reaches the UVLO rising threshold, at which point the internal bias circuitry is initialized, and soft-start is initiated.

#### **Input and Output Capacitor Selection**

Choose  $C_{IN}$  to be a 10µF nominal capacitor. Larger values improve the decoupling for the buck converter, but increase inrush current from the voltage supply when connected.  $C_{IN}$  reduces the current peaks drawn from the input power source during buck operation and reduces switching noise in the system. The ESR/ESL of  $C_{IN}$  and its series PCB traces should be very low (i.e., < 15m $\Omega$  + < 2nH) for frequencies up to 2MHz. Ceramic capacitors with X5R or X7R dielectric are highly recommended due to their small size, low ESR, and small temperature coefficients.

Choose the  $C_{\text{IN}}$  capacitor voltage rating to be greater than the expected input voltage of the system.

Choose the output bypass capacitance ( $C_{OUT}$ ) to be  $22\mu F$ . Larger values of  $C_{OUT}$  improve load transient performance, but increase the input surge currents during soft-start and output voltage changes. The output filter capacitor must have low enough ESR to meet output ripple and load transient requirements. The output capacitance must be high enough to absorb the inductor energy while transitioning from full-load to no load conditions. When using high-capacitance, low-ESR capacitors, the filter capacitor's ESR dominates the output voltage ripple in continuous conduction mode. Therefore, the size of the output capacitor depends on the maximum ESR required to meet the output voltage ripple ( $V_{RIPPLE(P-P)}$ ) specifications:

$$V_{RIPPLE(P-P)} = ESR \times I_{LOAD} \times LIR$$

where LIR is the inductor's ripple current to average current ratio. Compute LIR with Equation 2.

#### **Equation 2:**

$$LIR = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times I_{I,OAD} \times L}$$

Where  $I_{LOAD}$  is the buck's output current in the particular application (1.5A, max),  $V_{IN}$  is the application's input voltage, and  $F_{SW}$  is 2MHz. Ceramic capacitors with X5R or X7R dielectric are highly recommended due to their small size, low ESR, and small temperature coefficients.

All ceramic capacitors derate with DC bias voltage (effective capacitance goes down as DC bias goes up). Generally, small case size capacitors derate heavily compared to larger case sizes (0603 case size performs better than 0402). Consider the effective capacitance value carefully by consulting the manufacturer's data sheet.

#### **Inductor Selection**

Select an inductor with a saturation current rating greater than or equal to the maximum peak current limit ( $I_{LIM-PEAK}$ ) of 3.37A. In general, inductors with lower saturation current and higher DCR ratings are physically small. Higher values of DCR reduce buck efficiency. Choose the RMS current rating of the inductor (the current at which the temperature rises appreciably) based on the expected load current.

The chosen inductor value should ensure that the peak inductor ripple current (I<sub>PEAK</sub>) is below the high-side MOSFET peak current limit (I<sub>LIM-PEAK</sub>) so that the buck can maintain regulation. A 0.47µH value of inductor is recommended through the operation range of the device.

Use Equation 3 and Equation 4 to compute  $I_{PEAK}$ . If  $I_{PEAK}$  is greater than  $I_{LIM-PEAK}$ , then increase the inductor value.

#### **Equation 3:**

$$I_{P-P} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times f_{SW} \times L}$$

#### Equation 4:

$$I_{PEAK} = I_{LOAD} + \frac{I_{P-P}}{2}$$

where I<sub>LOAD</sub> is the buck's output current in the particular application (1.5A max),  $V_{IN}$  is the application's largest expected input voltage (4.8V max), f<sub>SW</sub> depends on  $V_{OUT}$  setting, see the <u>Typical Operating Characteristics</u> to find f<sub>SW</sub> under various  $V_{OUT}$  settings.

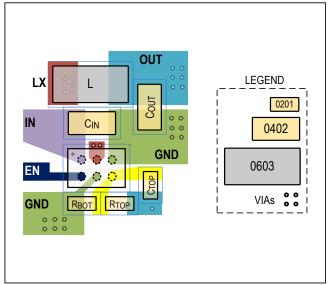

#### **PCB Layout Guidelines**

Careful circuit board layout is critical to achieve lowswitching power losses and clean, stable operation. Figure 2 shows an example PCB top-metal layout.

When designing the PCB, follow these guidelines:

- The input capacitor should be placed immediately next to the IN pin of the device. Since the device operates at 2MHz switching frequency, this placement is critical for effective decoupling of high-frequency noise from the IN pin.

- 2) Place the inductor and output capacitor close to the part and keep the loop area small.

- 3) Make the trace between LX and the inductor short and wide. Do not take up an excessive amount of area. The voltage on this node is switching very quickly and additional area creates more radiated emissions.

- Connect PGND and AGND together to the common ground on the second layer. Do not connect them anywhere else.

- 5) Keep the power traces and load connections short and wide. This practice is essential for high efficiency.

Figure 2. Example Layout

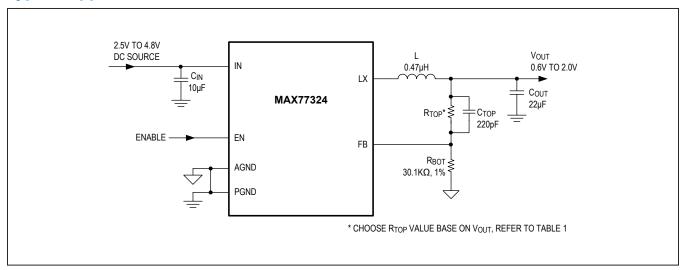

# **Typical Application Circuit**

# **Suggested Inductors**

| PART NUMBER     | INDUCTA<br>NCE [µH] | DC<br>RESISTANCE<br>[mΩ] | I RATING [A]<br>-30% (∆L/L) | I RATING [A]<br>∆T = 40°C<br>RISE | DIMENSIONS<br>L X W X H<br>[mm] | NOTE                                               |

|-----------------|---------------------|--------------------------|-----------------------------|-----------------------------------|---------------------------------|----------------------------------------------------|

| GLULKR4701A     | 0.47                | 20                       | 4.5                         | 4.9                               | 2.5 x 2.0 x 1.0                 | Optimize performance. Default on evaluation board. |

| DFE18SANR47MG0L | 0.47                | 54                       | 3.6                         | 2.6                               | 1.6 x 0.8 x 1.0                 | Optimize solution size.                            |

# Suggested Capacitors for both CIN and COUT

| PART NUMBER         | CAPACITANCE<br>[μF] | CAPACITANCE<br>TOLERANCE | K A I ING | TEMPERATURE<br>CHARACTERISTIC | DIMENSIONS<br>LXWXH<br>[mm] | NOTE                                                      |

|---------------------|---------------------|--------------------------|-----------|-------------------------------|-----------------------------|-----------------------------------------------------------|

| C1608X5R0J226M080AC | 22                  | ±20%                     | 6.3       | X5R                           | 1.6 x 0.8 x<br>0.8          | Optimize perfor-<br>mance. Default on<br>evaluation board |

| CL05A226MQ5QUNC     | 22                  | ±20%                     | 6.3       | X5R                           | 1.0 x 0.5 x<br>0.8          | Optimize solution size (higher capacitance derating).     |

# **Ordering Information**

| PART NUMBER      | VOUT                       | PIN-PACKAGE | MODE OF OPERATION       |

|------------------|----------------------------|-------------|-------------------------|

| MAX77324EWTAD+T  | Adjustable from 0.6V to 2V | 6 WLP       | Automatic Skip/PWM Mode |

| MAX77324GEWTAD+T | Adjustable from 0.6V to 2V | 6 WLP       | PWM Mode                |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

T = Tape and reel.

# **MAX77324**

# 4.8V<sub>IN</sub>, 1.5A High-Efficiency, Ultra-Small Buck Converter

# **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                              | PAGES<br>CHANGED      |

|--------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0                  | 1/18             | Initial release                                                                                                                                                                                                                                                          | _                     |

| 1                  | 3/18             | Updated Application Circuit, corrected typos in the <i>Package Information</i> table, added details in the <i>Electrical Characteristics</i> table, updated TOCs, added more information to the <i>Detailed Description</i> and <i>Application Information</i> sections. | 1–6, 8, 9,<br>11, 12  |

| 2                  | 1/22             | Updated General Description, Benefits and Features, Electrical Characteristics, Typical Operating Characteristics, Detailed Description, SKIP/PWM Operation, Inductor Selection, and Ordering Information                                                                | 1–7, 9, 10,<br>12, 13 |

| 3                  | 4/23             | Updated Electrical Characteristics                                                                                                                                                                                                                                       | 2                     |