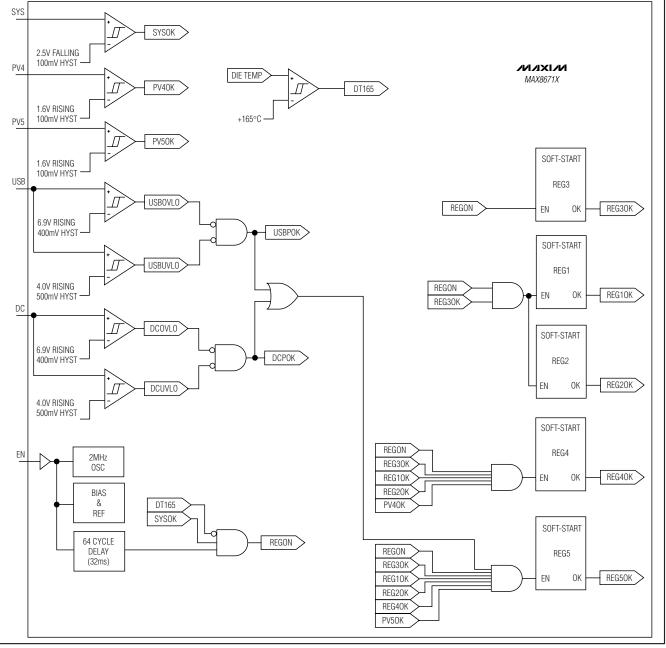

Figure 11. Enable/Disable Logic

# Enable/Disable (EN) and Sequencing

Figures 11, 12, and 13 show how the five MAX8671X regulators are enabled and disabled. With a valid SYS voltage and die temperature, asserting EN high enables REG1-REG4. Pulling EN low disables

REG1–REG5. REG5 is intended to power the system USB transceiver circuitry, which is only active when USB power is available. Therefore, a valid source must be on either the USB or DC input for REG5 to enable.

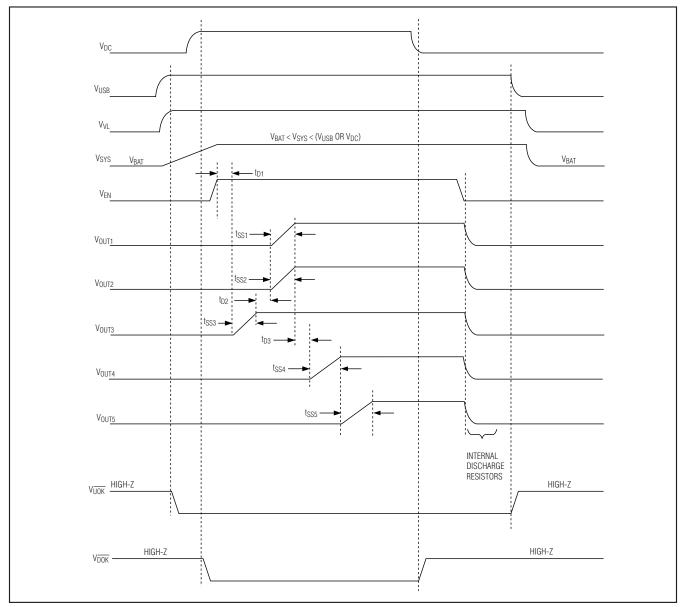

Figure 12. Enable and Disable Waveforms

The VL regulator is not controlled by EN. It is powered from the higher of USB or DC and automatically powers up when either of the power inputs exceeds approximately 1.5V. Similarly, VL automatically powers down when both the USB and DC power inputs are removed.

### Soft-Start/Inrush Current

The MAX8671X implements soft-start on many levels to control inrush current, to avoid collapsing supply volt-

ages, and to fully comply with the USB 2.0 specifications. All USB, DC, and charging functions implement soft-start. The USB and DC nodes only require  $4.7\mu$ F of input capacitance. Furthermore, all regulators implement soft-start to avoid transient overload of power inputs (Figure 12).

37

MAX8671X

### **Active Discharge in Shutdown**

Each MAX8671X regulator (REG1–REG5) has an internal 1k $\Omega$  resistor that discharges the output capacitor when the regulator is off. The discharge resistors ensure that the load circuitry powers down completely. The internal discharge resistors are connected when a regulator is disabled and when the device is in UVLO with an input voltage greater than 1.0V. With an input voltage less than 1.0V, the internal discharge resistors are not activated.

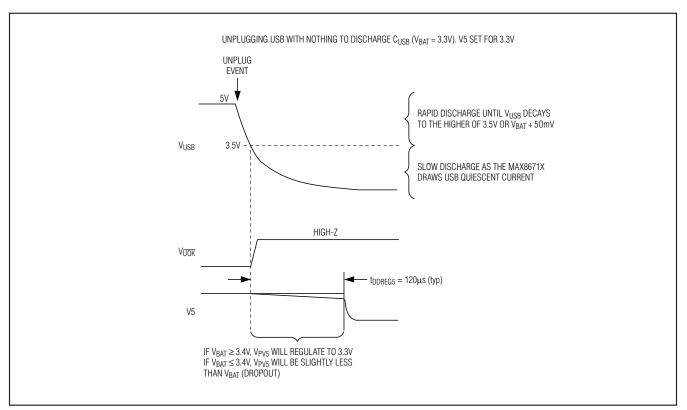

# Undervoltage and Overvoltage Lockout USB/DC UVLO

Undervoltage lockout (UVLO) prevents an input supply from being used when its voltage is below the operat-

ing range. When the USB voltage is less than the USB UVLO threshold (4.0V typ), the USB input is disconnected from SYS, and UOK goes high impedance. When the DC voltage is less than the DC UVLO threshold (4.0V typ), the DC input is disconnected from SYS, and DOK goes high impedance. In addition, when both USB and DC are in UVLO, the battery charger is disabled, and BAT is connected to SYS through the internal system load switch. REG1–REG4 are allowed to operate from the battery without power at USB or DC. REG5 is intended to power the system USB transceiver circuitry, which is only active when USB power is available. Therefore, a valid source must be present on either the USB or DC input for REG5 to enable.

Figure 13. REG5 Disable Detail

### USB/DC OVLO

Overvoltage lockout (OVLO) prevents an input supply from being used when its voltage exceeds the operating range. Both USB and DC withstand input voltages up to 14V. When the USB voltage is greater than the USB OVLO threshold (6.9V typ), the USB input is disconnected from SYS, and UOK goes high impedance. When the DC voltage is greater than the DC OVLO threshold (6.9V typ), the DC input is disconnected from SYS, and DOK goes high impedance. In addition, when both DC and USB are in OVLO, the battery charger is disabled, and BAT is connected to SYS through the internal system load switch. REG1-REG4 are allowed to operate from the battery when USB and DC are in overvoltage lockout. The VL supply remains active in OVLO. REG5 is intended to power the system USB transceiver circuitry, which is only active when USB power is available. A valid source must be present on either the USB or DC input for REG5 to enable.

SYS UVLO

A UVLO circuit monitors the voltage from SYS to ground (V<sub>SYS</sub>). When V<sub>SYS</sub> falls below V<sub>UVLO\_SYS</sub> (2.5V typ), REG1–REG5 are disabled. V<sub>UVLO\_SYS</sub> has a 100mV hysteresis. The VL supply remains active in SYS UVLO.

### REG4/REG5 UVLO

A UVLO circuit monitors the PV4 and PV5 LDO power inputs. When the PV\_ voltage is below 1.6V, it is invalid and the LDO is disabled.

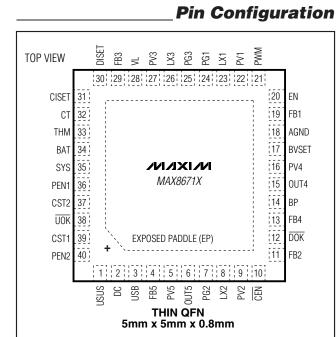

**Thermal Limiting and Overload Protection** The MAX8671X is packaged in a 5mm x 5mm x 0.8mm 40-pin thin QFN. Table 7 shows the thermal characteristics of this package. The MAX8671X has several mechanisms to control junction temperature in the event of a thermal overload.

# Table 7. 5mm x 5mm x 0.8mmThermal Characteristics

|                      | SINGLE-LAYER PCB                | MULTILAYER PCB                  |

|----------------------|---------------------------------|---------------------------------|

| Continuous           | 1777.8mW                        | 2857.1mW                        |

| Power<br>Dissipation | Derate 22.2mW/°C<br>above +70°C | Derate 35.7mW/°C<br>above +70°C |

| *θյд                 | 45°C/W                          | 28°C/W                          |

| θJC                  | 1.7°C/W                         | 1.7°C/W                         |

$^*\theta_{JA}$  is specified according to the JESD51 standard.

**Smart Power Selector Thermal-Overload Protection** The MAX8671X reduces the USB and DC current limits by 5%/°C when the die temperature exceeds +100°C. The system load (I<sub>SYS</sub>) has priority over the charger current, so input current is first reduced by lowering charge current. If the junction temperature still reaches +120°C in spite of charge-current reduction, no input current is drawn from USB and DC; the battery supplies the entire load and SYS is regulated 82mV (V<sub>BSREG</sub>) below BAT. Note that this on-chip thermal-limiting circuit is not related to and operates independently from the thermistor input.

### **Regulator Thermal-Overload Shutdown**

The MAX8671X disables all regulator outputs (except VL) when the junction temperature rises above +165°C, allowing the device to cool. When the junction temperature cools by approximately 15°C, the regulators resume the state indicated by the enable input (EN) by repeating their soft-start sequence. Note that this thermal-overload shutdown is a fail-safe mechanism; proper thermal design should ensure that the junction temperature of the MAX8671X never exceeds the absolute maximum rating of +150°C.

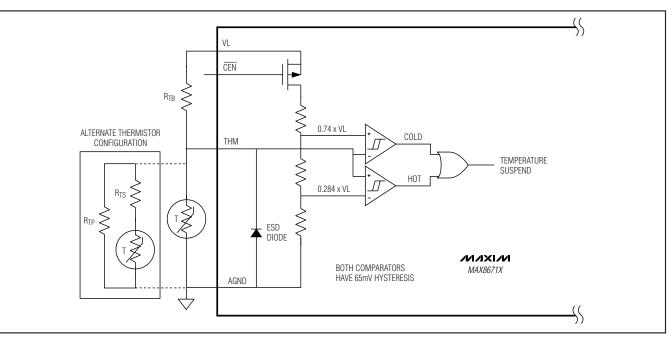

### Battery Charger Thermistor Input (THM)

The THM input connects to an external negative temperature coefficient (NTC) thermistor to monitor battery or system temperature. Charging is suspended when the thermistor temperature is out of range. Additionally, the charge timers are suspended and charge status indicators report that the charger is in thermistor suspend (CST[1:2] = 01). When the thermistor comes back into range, charging resumes and the charge timer continues from where it left off. Table 8 shows THM temperature limits for various thermistor material constants. If the battery temperature monitor is not required, bias THM midway between V<sub>L</sub> and AGND with a resistive divider— $100k\Omega \pm 5\%$  resistors are recommended. Biasing THM midway between V<sub>L</sub> and AGND bypasses this function.

| THERMISTOR BETA (ß [K])               | 3000  | 3250  | 3500  | 3750  | 4250  | 4250  |

|---------------------------------------|-------|-------|-------|-------|-------|-------|

| R <sub>TB</sub> (kΩ)                  | 10    | 10    | 10    | 10    | 10    | 10    |

| R <sub>TP</sub> (kΩ)                  | Open  | Open  | Open  | Open  | Open  | 120   |

| R <sub>TS</sub> (kΩ)                  | Short | Short | Short | Short | Short | Short |

| Resistance at +25°C [k $\Omega$ ]     | 10    | 10    | 10    | 10    | 10    | 10    |

| Resistance at +50°C [k $\Omega$ ]     | 4.59  | 4.30  | 4.03  | 3.78  | 3.32  | 3.32  |

| Resistance at 0°C [k $\Omega$ ]       | 25.14 | 27.15 | 29.32 | 31.66 | 36.91 | 36.91 |

| Nominal Hot Trip<br>Temperature [°C]  | 55    | 53    | 51    | 49    | 46    | 45    |

| Nominal Cold Trip<br>Temperature [°C] | -3    | -1    | 0     | 2     | 5     | 0     |

# **Table 8. Trip Temperatures for Different Thermistors**

Figure 14. Thermistor Input

Since the thermistor monitoring circuit employs an external bias resistor from THM to VL (RTB in Figure 14), any resistance thermistor can be used as long as the value of RTB is equivalent to the thermistor's +25°C resistance. For example, with a 10k $\Omega$  at +25°C thermistor, use 10k $\Omega$  at RTB, and with a 100k $\Omega$  at +25°C thermistor, use 100k $\Omega$  at RTB. The general relation of thermistor resistance to temperature is defined by the following equation:

$$R_{T} = R_{25} \times e \left\{ \beta \left( \frac{1}{T + 273} - \frac{1}{298} \right) \right\}$$

where:

$\mathsf{R}_\mathsf{T}=\mathsf{The}$  resistance in ohms of the thermistor at temperature T in Celsius

$R_{25}$  = The resistance in ohms of the thermistor at +25°C

$\beta$  = The material constant of the thermistor that typically ranges from 3000K to 5000K

T = The temperature of the thermistor in  $^\circ C$  that corresponds to  $R_T$

THM threshold adjustment can be accommodated by changing RTB, connecting a resistor in series and/or in parallel with the thermistor, or using a thermistor with different material constant ( $\beta$ ). For example, a +45°C hot threshold and 0°C cold threshold can be realized by using a 10k $\Omega$  thermistor with a  $\beta$  of 4250K and connecting 120k $\Omega$  in parallel. Since the thermistor resistance near 0°C is much higher than it is near +50°C, a large parallel resistance lowers the cold threshold, while only slightly lowering the hot threshold. Conversely, a small series resistance raises the cold threshold, while only slightly raising the hot threshold. Raising RTB lowers both the hot and cold thresholds, while lowering RTB raises both thresholds.

### **PCB Layout and Routing**

Good printed circuit board (PCB) layout is necessary to achieve optimal performance. Refer to the MAX8671 evaluation kit for Maxim's recommended layout.

Use the following guidelines for the best results:

- Use short and wide traces for high-current and discontinuous current paths.

- The step-down regulator power inputs are critical discontinuous current paths that require careful bypassing. Place the step-down regulator input bypass capacitors as close as possible to each switching regulator power input pair (PV\_ to PG\_).

- Minimize the area of the loops formed by the stepdown converters' dynamic switching currents.

- The exposed paddle (EP) is the main path for heat to exit the IC. Connect EP to the ground plane with thermal vias to allow heat to dissipate from the device.

- The MAX8671X regulator feedback nodes are sensitive high-impedance nodes. Keep these nodes as short as possible and away from the inductors.

- The thermistor node is high impedance and should be routed with care.

- Make power ground connections to a power ground plane. Make analog ground connections to an analog ground plane. Connect the ground planes at a single point.

Figure 15. Package Marking Example

- The REG4 LDO is a high-performance LDO with high PSRR and low noise and care should be used in the layout to obtain the high performance. Generally, the REG4 LDO is powered from a stepdown regulator output, and therefore, its input capacitor should be bypassed to the power ground plane. However, its output capacitor should be bypassed to the analog ground plane.

- BP is a high impedance node and leakage current into or out of BP can affect the LDO output accuracy.

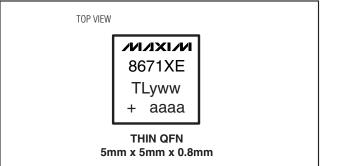

# \_Package Marking

The top of the MAX8671X package is laser etched as shown in Figure 15:

- "8671XETL" is the product identification code. The full part number is MAX8671XETL; however, in this case, the "MAX" prefix is omitted due to space limitations.

- "yww" is a date code. "y" is the last number in the Gregorian calendar year. "ww" is the week number in the Gregorian calendar. For example:

"801" is the first week of 2008; the week of January 1st, 2008

"052" is the fifty-second week of 2010; the week of December 27th, 2010.

"aaaa" is an assembly code and lot code.

"+" denotes lead-free packaging and marks the pin 1 location.

**Chip Information**

PROCESS: BICMOS

**MAX8671X**

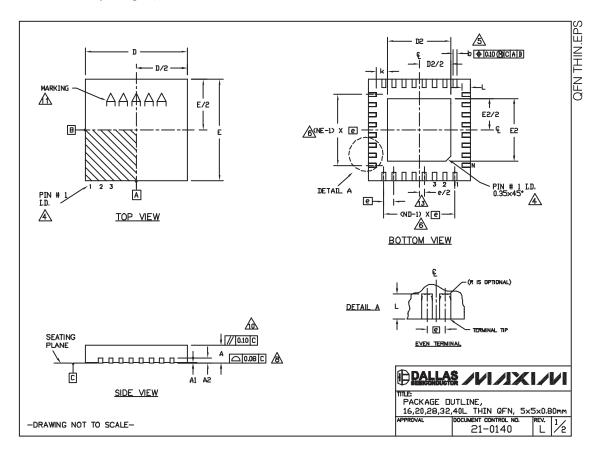

# **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <u>www.maxim-ic.com/packages</u>.)

# **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to www.maxim-ic.com/packages.)

| COMMON DIMENSIONS                                                   |              |             |          |       |       |       |        |       |             |       |                                                     |               |     |                  |      |       |

|---------------------------------------------------------------------|--------------|-------------|----------|-------|-------|-------|--------|-------|-------------|-------|-----------------------------------------------------|---------------|-----|------------------|------|-------|

| (G.                                                                 |              | L 5         |          |       |       | i×5   |        | BL 5  |             |       | 2L 5                                                |               |     | 40L              |      |       |

| BOL                                                                 |              |             |          |       |       |       |        |       |             |       |                                                     |               | -   | N. NO            |      |       |

| •                                                                   | 1            |             |          |       |       |       |        |       |             |       |                                                     |               | +   | 70 0.7           | _    |       |

| 1                                                                   | 0            | 0.02        |          |       |       | 0.05  |        | 0.02  |             |       |                                                     |               |     | _                |      |       |

| 2                                                                   |              | 20 RE       | <u> </u> | -     | 20 RE |       | -      | 20 RE |             | -     | 20 RE                                               | EF. 0.20 REF. |     |                  |      |       |

|                                                                     |              |             |          |       |       |       |        |       |             |       |                                                     |               |     | 15 0.2<br>30 5.0 |      |       |

| )                                                                   |              |             |          |       |       |       |        |       |             |       |                                                     |               |     |                  |      |       |

| •                                                                   |              | 80 B        |          |       | 65 B  |       |        | 50 BS |             |       | .90 5.00 5.10 4.90 5.00 5.10<br>0.50 BSC. 0.40 BSC. |               |     |                  |      |       |

|                                                                     | 0.25         |             | -        | 0.25  |       |       | 0.25   |       |             | 0.25  |                                                     | -             | 0.8 | _                |      | -     |

|                                                                     | 0.30         | 0.40        | 0.50     | 0.45  | 0.55  | 0.65  | 0.45   | 0.55  | 0.65        | 0.30  | 0.40                                                | 0.50          | 0.3 | 30 0.4           | 40 I | .50   |

|                                                                     |              | 16          |          |       | 20    |       |        | 28    |             |       | 32                                                  |               |     | 40               | )    |       |

|                                                                     |              | 4           |          |       | 5     |       |        | 7     |             |       | 8                                                   |               |     | 10               | )    |       |

|                                                                     |              | 4           |          |       | 5     |       |        | 7     |             |       | 8                                                   |               |     | 10               |      |       |

| DEC                                                                 |              | <b>WHHB</b> |          | ۱     | VHHC  |       | \<br>\ | /HHD- | 1           | \v    | 'HHD-                                               | 2             |     |                  |      |       |

|                                                                     |              |             |          |       |       |       |        |       |             |       |                                                     |               |     |                  |      |       |

| TE S:                                                               |              |             |          |       |       |       |        |       |             |       |                                                     |               |     |                  |      |       |

|                                                                     | <b>IENSI</b> |             | i & 1    | OLER  | ANCI  | NG CI | ONFOR  | RM ТС | ase I       | IE YI | 4.5M-                                               | -1994         | ۱.  |                  |      |       |

| AL                                                                  | L DIM        | ENSI        | INS (    | ARE I | N MI  |       | TERS   | . ANG | <b>SLES</b> | ARE   | IN D                                                | EGRE          | ES. |                  |      |       |

| N N                                                                 | IS TH        | IE TO       | TAL      | NUMB  | ER D  | f tei | rmina  | LS.   |             |       |                                                     |               |     |                  |      |       |

|                                                                     |              |             |          |       |       |       |        |       |             |       |                                                     |               |     | ITION            |      |       |

|                                                                     |              |             |          |       |       |       |        |       |             |       |                                                     |               |     | ENTIF            |      |       |

|                                                                     |              |             |          |       |       |       |        |       |             |       |                                                     |               | ED. | THE              | TE   | RWI   |

|                                                                     |              |             |          |       |       |       |        |       |             |       |                                                     |               | 200 |                  | с т. | /F F1 |

| △ DIMENSION № APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEE |              |             |          |       |       |       |        |       |             |       |                                                     |               |     |                  |      |       |

- 🖄 DIMENSION 10 APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN

- 0.25 mm and 0.30 mm from terminal tip.

- DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

- Coplanarity applies to the exposed heat sink slug as well as the terninals. Drawing conforms to jedec MD220, except exposed pad dimension for ∕& T2855-3, T2855-6, T4055-1 AND T4055-2.

- WARPAGE SHALL NOT EXCEED 0.10 mm.

MARKING IS FOR PACKAGE ORIENTATION REFERENCE ONLY.

- NUMBER OF LEADS SHOWN ARE FOR REFERENCE ONLY.

- 12. NUMBER OF LEADS SHOWN ARE FUR METEREINLE UNLT. 23. LEAD CENTERLINES TO BE AT TRUE POSITION AS DEFINED BY BASIC DIMENSION 'e', ±0.05. 14. ALL DIMENSIONS APPLY TO BOTH LEADED AND POFREE PARTS.

-DRAWING NOT TO SCALE-

DALLAS /VI/IXI/VI IT E PACKAGE DUTLINE, 16,20,28,32,40L THIN QFN, 5x5x0.80mm PROVAL DOCUMENT CONTROL NO. REV. 10 21-0140 1

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

### 44

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

# **MAX8671X**