## MIC705/6/7/8

μP Supervisory Circuits

## **Description**

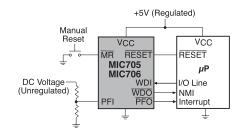

The MIC705/MIC706/MIC707/MIC708 are inexpensive microprocessor supervisory circuits that monitor power supplies in microprocessor based systems. The circuit functions include a watchdog timer, microprocessor reset, power failure warning and a debounced manual reset input.

The MIC705 and MIC706 offer a watchdog timer function while the MIC707 and MIC708 have an active high reset output in addition to the active low reset output.

Supply voltage monitor levels of 4.65V and 4.4V are available. The MIC705/MIC707 have a nominal reset threshold level of 4.65V while the MIC706 and MIC708 have a 4.4V nominal reset threshold level. When the supply voltage drops below the respective reset threshold level, RESET is asserted.

## **Typical Applications**

- Automotive Systems

- Intelligent Instruments

- Critical Microprocessor Power Monitoring

- Printers

- Computers

- Controllers

## **Ordering Information**

| <u>Part</u> | <u>Package</u> | Temp. Range    |

|-------------|----------------|----------------|

| MIC70_N     | 8-Lead PDIP    | -40°C to +85°C |

| MIC70 M     | 8-Lead SOIC    | -40°C to +85°C |

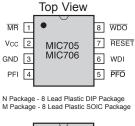

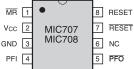

## **Pin Configuration**

#### **Features**

- Debounced Manual Reset Input is TTL/CMOS Compatible

- Reset Pulse Width, 200ms

- Watchdog Timer, 1.6s (MIC705/MIC706)

- 4.4V or 4.65V Precision Voltage Monitor

- Early Power Fail Warning or Low Battery Detect

## **Typical Operating Circuit**

1

## **Absolute Maximum Ratings**

| Terminal Voltage                     | Operating Temperature Range                  |

|--------------------------------------|----------------------------------------------|

| VCC0.3V to 6.0V                      | MIC70_N, MIC70_M40°C to 85°C                 |

| All Other Inputs0.3V to (VCC + 0.3V) | Storage Temperature Range65°C to 150°C       |

| Input Current                        | Lead Temperature (Soldering - 10 sec.) 300°C |

| VCC, Gnd                             | Power Dissipation (PDIP) 475mW               |

| Output Current (all outputs) 20mA    | Power Dissipation (SOIC) 400mW               |

Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent device failure. Functionality at or above these limits is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability. Operating ranges define those limits between which the functionality of the device is guaranteed.

### **Electrical Characteristics**

$V_{CC} = 4.75 \text{V to } 5.5 \text{V for MIC705/MIC707}, \ \ V_{CC} = 4.5 \text{V to } 5.5 \text{V for MIC706/MIC708}, \ T_{A} = -40 ^{\circ} \text{C to } 85 ^{\circ} \text{C unless otherwise noted}.$

| Parameter                                | Conditions                                                               | Min          | Тур         | Max         | Units |

|------------------------------------------|--------------------------------------------------------------------------|--------------|-------------|-------------|-------|

| Operating Voltage Range, VCC             | 1.4                                                                      |              | 5.5         | V           |       |

| Supply Current                           | MIC70                                                                    |              |             | 60          | μА    |

| Reset Voltage Threshold                  | MIC705, MIC707<br>MIC706, MIC708                                         | 4.50<br>4.25 | 4.65<br>4.4 | 4.75<br>4.5 | V     |

| Reset Threshold Hysteresis               |                                                                          |              | 40          |             | mV    |

| Reset Pulse Width, t <sub>RS</sub>       | 140                                                                      | 200          | 280         | ms          |       |

| RESET Output Voltage                     | ISource = 800μA<br>  ISink = 3.2mA<br>  MIC70C, ISink = 50μA, VCC = 1.4V | VCC - 1.5V   |             | 0.4<br>0.3  | V     |

| RESET Output Voltage                     | I <sub>Source</sub> = 800μA<br>I <sub>Sink</sub> = 1.2mA                 | VCC - 1.5V   |             | 0.4         | V     |

| Watchdog Timeout Period, t <sub>WD</sub> |                                                                          | 1.0          | 1.6         | 2.25        | sec   |

| WDI Minimum Input Pulse, t <sub>WP</sub> | V <sub>IL</sub> = 0.4V, V <sub>IH</sub> = 80% of V <sub>CC</sub>         | 50           |             |             | ns    |

| WDI Threshold Voltage                    | VIH, VCC = 5V<br>VIL, VCC = 5V                                           | 3.5          |             | 0.8         | V     |

| WDI Input Current                        | WDI = VCC                                                                | -150         | -50<br>50   | 150         | μА    |

| WDO Output Voltage                       | I <sub>Source</sub> = 800μA<br>I <sub>Sink</sub> = 1.2mA                 | VCC - 1.5V   |             | 0.4         | V     |

# MIC705/6/7/8 μP Supervisory Circuits

## **Electrical Characteristics**

$V_{CC} = 4.75 \text{V to } 5.5 \text{V for MIC705/MIC707}, \ \ V_{CC} = 4.5 \text{V to } 5.5 \text{V for MIC706/MIC708}, \ T_{A} = -40 ^{\circ} \text{C to } 85 ^{\circ} \text{C unless otherwise noted}.$

| Parameter                                                                          | Min                  | Тур        | Max  | Units |    |

|------------------------------------------------------------------------------------|----------------------|------------|------|-------|----|

| MR Pull-Up Current                                                                 | MR = 0V              | 100        | 250  | 600   | μΑ |

| $\overline{\text{MR}}$ Pulse Width, $t_{\text{MR}}$                                |                      | 150        |      |       | nS |

| MR Input Threshold                                                                 | VIL<br>VIH           | 2.0        |      | 0.8   | V  |

| $\overline{\text{MR}}$ to Reset Output Delay, $t_{\text{MD}}$                      |                      |            |      | 250   | nS |

| PFI Input Threshold                                                                | V <sub>CC</sub> = 5V | 1.2        | 1.25 | 1.3   | V  |

| PFI Input Current                                                                  |                      | -25        | 0.01 | +25   | nA |

| PFO Output Voltage I <sub>Sink</sub> = 3.2mA VCC = 5V, I <sub>Source</sub> = 800μA |                      | VCC - 1.5V |      | 0.4   | V  |

## **Pin Functions**

|          | Pin No.          |                  |                                                                                                                                                                                                                                                                                                                                                                                 |

|----------|------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | MIC705<br>MIC706 | MIC707<br>MIC708 |                                                                                                                                                                                                                                                                                                                                                                                 |

| MR       | 1                | 1                | Manual Reset Input forces RESET to assert when pulled below 0.8V. An internal pull-up current of 250μA on this input forces it high when left floating. This input can also be driven from TTL or CMOS logic.                                                                                                                                                                   |

| vcc      | 2                | 2                | Primary supply input, +5V.                                                                                                                                                                                                                                                                                                                                                      |

| GND      | 3                | 3                | IC ground pin, 0V reference.                                                                                                                                                                                                                                                                                                                                                    |

| PFI      | 4                | 4                | Power fail input. Internally connected to the power fail comparator which is referenced to 1.25V. The power fail output (PFO) remains high if PFI is above 1.25V. PFI should be connected to GND or VOUT if the power fail comparator is not used.                                                                                                                              |

| PFO      | 5                | 5                | Power fail output. The power fail comparator is independent of all other functions on this device.                                                                                                                                                                                                                                                                              |

| WDI      | 6                | N/A              | Watchdog input. The WDI input monitors microprocessor activity, an internal watchdog timer resets itself with each transition on the watchdog input. If the WDI pin is held high or low for longer than the watchdog timeout period, WDO is forced to active low. The watchdog function can be disabled by floating the WDI pin.                                                |

| N/C      | N/A              | 6                | No Connect                                                                                                                                                                                                                                                                                                                                                                      |

| RESET    | 7                | 7                | RESET is asserted if either V <sub>CC</sub> goes below the reset threshold or by a low signal on the manual reset input (MR). RESET remains asserted for one reset timeout period (200ms) after V <sub>CC</sub> exceeds the reset threshold or after the manual reset pin transitions from low to high. The watchdog timer will not assert RESET unless WDO is connected to MR. |

| WDO      | 8                | N/A              | Output for the watchdog timer. The watchdog timer resets itself with each transition on the watchdog input. If the WDI pin is held high or low for longer than the watchdog timeout period, WDO is forced low. WDO will also be forced low if VCC is below the reset threshold and will remain low until VCC returns to a valid level.                                          |

| RESET    | N/A              | 8                | RESET is the compliment of RESET and is asserted if either VCC goes below the reset threshold or by a low signal on the manual reset input (MR). RESET is suitable for microprocessors systems that use an active high reset.                                                                                                                                                   |

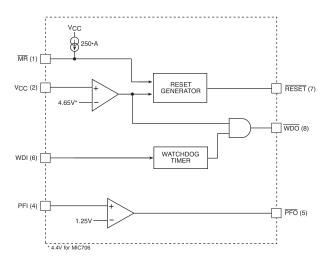

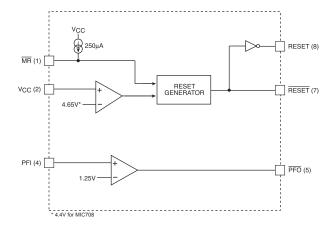

## **Block Diagram**

Figure 1. MIC705/MIC706 Block Diagram

Figure 2. MIC707/MIC708 Block Diagram

## **Circuit Description**

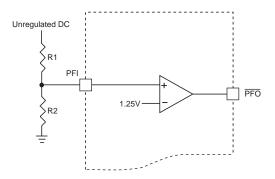

#### **Power Fail Warning**

An additional comparator which is independent of other functions on the MIC705/706/707/708 is provided for early warning of power failure. An external voltage

Figure 3. Power Fail Comparator

divider can be used to compare unregulated DC to an internal 1.25V reference. The voltage divider ratio on the input of the power fail comparator (PFI) can be chosen so as to trip the power fail comparator a few milliseconds before VCC falls below the maximum reset threshold voltage. The output of the power fail comparator  $(\overline{\text{PFO}})$  can be used to interrupt the microprocessor when used in this mode and execute shut-down procedures prior to power loss.

#### **Watchdog Timer**

The microprocessor can be monitored by connecting the WDI pin (watchdog input) to a bus line or I/O line. If a transition doesn't occur on the WDI pin within the watchdog timeout period, then  $\overline{\text{WDO}}$  will go low. A minimum pulse of 50ns or any transition low-to-high or high-to-low on the WDI pin will reset the watchdog timer.

The output of the watchdog timer ( $\overline{WDO}$ ) will remain high if WDI sees a valid transition within the watchdog timeout period or if WDI is left floating. If VCC falls below the reset threshold voltage then  $\overline{WDO}$  goes low immediately regardless of WDI. Thus, if WDI is left floating, then  $\overline{WDO}$  can be used as a low line indicator.

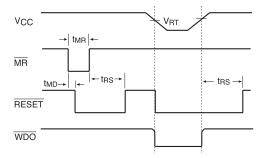

#### Microprocessor Reset

The  $\overline{\text{RESET}}$  pin is asserted whenever V<sub>CC</sub> falls below the reset threshold voltage or when  $\overline{\text{MR}}$  goes low. The reset pin remains asserted for a period of 200ms after V<sub>CC</sub> has risen above the reset threshold voltage and  $\overline{\text{MR}}$  goes high. The reset function ensures the

Figure 4. Reset Timing Diagram

microprocessor is properly reset and powers up into a known condition after a power failure. RESET will remain valid with VCC as low as 1.4V.

## Alternate Source Cross Reference Guide

|              | MIC Direct         |

|--------------|--------------------|

| Industry P/N | <u>Replacement</u> |

| MAX705CPA    | MIC705N            |

| MAX705CSA    | MIC705M            |

| MAX705EPA    | MIC705N            |

| MAX705ESA    | MIC705M            |

| ADM705AN     | MIC705N            |

| DS1705EPA    | MIC705N            |

| DS1705ESA    | MIC705M            |

| MAX706CPA    | MIC706N            |

| MAX706CSA    | MIC706M            |

| MAX706EPA    | MIC706N            |

| ADM706AN     | MIC706N            |

| DS1706EPA    | MIC706N            |

| DS1706ESA    | MIC706M            |

| MAX707CPA    | MIC707N            |

| MAX707CSA    | MIC707M            |

| MAX707EPA    | MIC707N            |

| MAX707ESA    | MIC707M            |

| ADM707AN     | MIC707N            |

| DS1707EPA    | MIC707N            |

| DS1707ESA    | MIC707M            |

| MAX708CPA    | MIC708N            |

| MAX708CSA    | MIC708M            |

| MAX708EPA    | MIC708N            |

| MAX708ESA    | MIC708M            |

| ADM708AN     | MIC708N            |

| DS1708EPA    | MIC708N            |

| DS1708ESA    | MIC708M            |

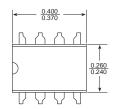

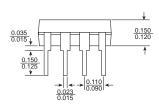

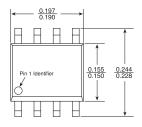

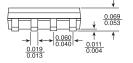

## **Packaging Information**

### M Package, 8-Pin Small Outline

### N Package, 8-Pin Plastic Dual-In-Line