# **BG2A – Universal Gate Drive Prototype Board**

Description: BG2A is a fully isolated two channel gate drive circuit designed for use with dual IGBT modules. The BG2A utilizes Powerex VLA500-01 or VLA502-01 hybrid gate drivers to provide efficient switching of modules rated up to 1400A. The hybrid gate drivers also provide protection against unexpected short circuit conditions using desaturation detection. The VLA500-01 and VLA502-01 hybrid gate drivers have an integrated DC-to-DC converter with 2500VRMS isolation to provide isolated gate drive power. Control signals are isolated using high speed optocouplers with 15kV/µs common mode noise immunity. The BG2A provides an isolated fault feedback signal if a short circuit condition is detected.

#### Features:

- Up to 12A Peak Output Current

- 2500VRMS isolation for control power and signals

- Standard AMP MTA .100" Connectors

- Operates from a single 15VDC supply

- Wide output voltage swing +15V/-8V

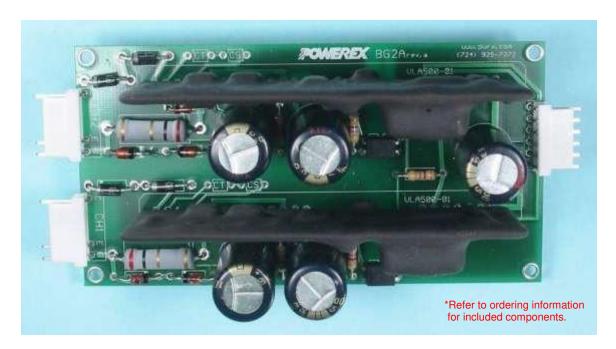

- Compact Size 4" x 2.1" (101mm x 53mm)

## Applications:

BG2A is designed for use with all Powerex NF, A, S and NFH series IGBT modules.

- Use VLA500-01 hybrid gate drivers for Powerex NF, A and S-Series IGBT modules

- Use VLA502-01 hybrid gate drivers for **Powerex NFH Series IGBT modules**

- Use VLA500K-01R hybrid gate drivers for **Series modules**

Ordering Information: BG2A-NF is a kit that includes a bare PCB with two VLA500-01 drivers

(For use with NF, A and S-Series IGBT modules)

**BG2A-NFH** is a kit that includes a bare PCB with two VLA502-01 gate drivers

(For use with NFH-Series IGBT modules)

**BG2A-K** is a kit that includes a bare PCB with two VLA500K-01R gate drivers (For use with 1700V IGBT modules)

Publication Date: 09-12-2014 Rev. 5

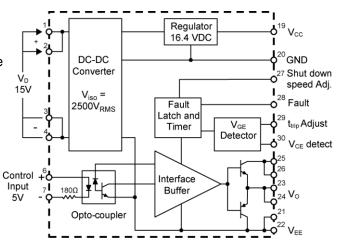

**Circuit Explanation:** The BG2A is a basic two channel gate driver designed around the recommended application circuit for the Powerex VLA500 series hybrid gate drivers. A functional block diagram of the VLA500 series hybrid gate driver is shown for reference in Figure 1. The VLA500-01 and VLA500K-01R use a standard high speed open collector type opto-coupler with a maximum turn-off propagation delay of 1.3µs. This makes it suitable for industrial applications with operating frequencies of up to 20kHz. The VLA500-01 is recommended for use with Powerex NF-Series and A-Series IGBT modules. The VLA502-01 uses a high speed buffered output type optocoupler which provides a maximum propagation delay of 0.7µs. This makes it suitable for use in high frequency applications operating at more than 20kHz. The VLA502-01 is recommended for use with Powerex NFH-Series IGBT modules. For additional detailed information on the operation of the hybrid gate drivers please see the individual datasheets.

Figure 1: VLA500 Series Block Diagram

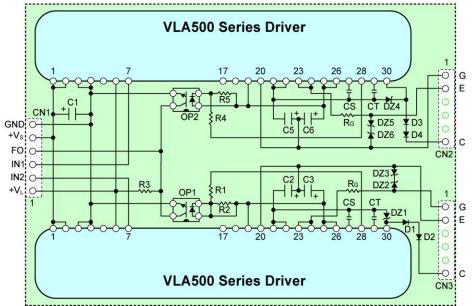

A complete schematic and component selection guide for the BG2A is shown in Figure 2. The board will normally be operated with two input voltage sources. A 5V logic source (+VL) provides drive for the high speed opto-couplers inside the hybrid gate drivers and pull-up voltage for the fault signal isolation optos OP1 and OP2. A 15V power supply (+VS) provides power for the gate driver and is connected to the primary side of the hybrid gate driver's built in DC-to-DC converter at Pins 1, 2 and 3, 4. The +15V source is decoupled with the low impedance electrolytic capacitor C1. In the BG2A circuit a 1000uF capacitor was selected for C1 so that the same capacitor could be used for C1, C2. C3, C5 and C6. In most applications this will be much larger than necessary to support the drivers ripple current. Typical applications will be able to use 100µF or less depending on the load current and the distance from the main 15V supply filter capacitors. The hybrid's built in DC-to-DC converter provides isolated gate drive power which consists of +16.4V (VCC) at Pin 19 and -9V (VEE) at Pins 21 and 22. These supplies share a common ground at Pin 20. The gate drive power supplies are decoupled using the low impedance electrolytic capacitors C2, C3, C5 and C6. It is very important that these capacitors have low enough impedance and sufficient ripple current capability to provide the required high current gate drive pulses. The 1000uF capacitors used on the BG2A are sized to supply 12A gate pulses at a 20kHz rate. If the application is operating at lower frequency or lower peak current it may be possible to reduce the size of these capacitors. Consult the hybrid gate driver individual datasheets for details on selecting the decoupling capacitors.

The VEE and VCC supplies are connected to the driver's output stage to produce gate drive at Pins 23 and 24. The gate drive current is adjusted by selecting the appropriate series gate resistance (RG). RG will normally be adjusted to provide suitable drive for the module being used. For more information see Powerex IGBT module application notes. Protection against gate voltage surges is provided by DZ2, DZ3, DZ5, and DZ6. These zener diodes also help to control short circuit currents by shunting miller current away from the gate. Short circuit protection is provided by means of desaturation detection. For details on the operation of this circuit consult the specific datasheet. The collector voltage of each IGBT is detected through the series connected high voltage blocking diodes D1, D2 and D3, D4. The combined blocking voltage of the series connected diodes must be equal to or greater than the VCES rating of the IGBT. For applications using lower voltage devices it may be possible to use a single detection diode. DZ1 and DZ4 protect the gate driver's detect input (Pin 30) from voltage surges during reverse recovery of the high voltage blocking diodes. The CS and CT capacitors are used to adjust the drivers protection circuit trip time and slow shut-down speed. The driver's default settings are sufficient for many applications and therefore these capacitors can be omitted. For details on the use of CT and CS consult the specific datasheet.

If the gate driver's short circuit protection is activated it immediately shuts down the gate drive and pulls Pin 28 low to indicate a fault. Current flows from Vcc (Pin 19) through the LED in fault isolation opto (OP1, OP2) to Pin 28. The transistor in the fault isolation opto turns on and pulls the fault signal line (FO) at Pin 4 of CN1 low. This opto isolated signal can now be used by the controller to detect the fault condition.

#### **Component Selection:**

| <u>Designation</u> | Typical Value | <u>Description</u>                                | Example: Mfg./PN      |

|--------------------|---------------|---------------------------------------------------|-----------------------|

| D1,D2,D3,D4        | 0.5 A, 1000V  | VCE detection diode – ultra fast recovery         | ON Semi/MUR1100E      |

| DZ2, DZ3, DZ5, DZ6 | 16V, 1W       | Gate Voltage Surge Protection                     | 1N4745                |

| DZ1, DZ4           | 30V, 1W       | Detect input pin surge voltage protection         | 1N4751                |

| C1, C2, C3. C5, C6 | 1000 μF, 35V  | Power supply filter – Electrolytic, low Impedance | Panasonic EEU-FC1V102 |

| CS                 | 0-1000 pF     | Adj. soft shutdown – Multilayer ceramic or film** | EPCOS B37979          |

| CT                 | 0-200 pF      | Adj. trip time - Multilayer ceramic or film**     | EPCOS B37979          |

| R1, R4             | 4.7kΩ, 0.25W  | Fault sink current limiting resistor              |                       |

| R2, R5             | 3.3kΩ, 0.25W  | Fault signal noise suppression resistor           |                       |

| R3                 | 4.7KΩ, 0.25W  | Fault feedback pull-up resistor                   |                       |

| OP1, OP2           | NEC PS2501    | Opto-coupler for fault signal isolation           | NEC/ PS2501           |

| CN1, CN2, CN3      | MTA .100"     | Input and gate drive connectors*                  | AMP 641216-6          |

<sup>\*</sup> Remove the three unused pins on CN2 and CN3 to maintain appropriate high voltage spacing. Recommended mating connector AMP CST-100 Housing P/N 770602-6 with crimp contact 770666-2.

## Figure 2: BG2A Schematic and Component Selection Guide

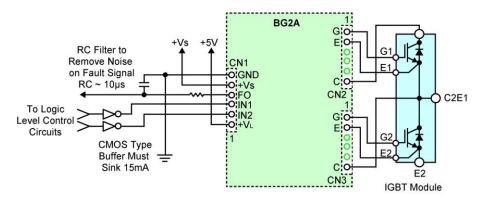

Interface Circuit Requirements: A typical interface circuit for the BG2A is shown in Figure 3. A single +15V control power supply (+Vs) is connected to Pin 5 of CN1 with its ground at Pin 6. This supply provides all of the gate drive power for both channels via the hybrid gate drivers' built in DC-to-DC converters. The current drawn from the 15V supply will vary from less than 200mA to more than 1A depending on the switching frequency and size of IGBT being driven. Consult the hybrid gate driver individual datasheets for details on determining the required supply current. A 5V logic supply is connected at Pin 1 of CN1 and shares the same common ground at Pin 6 of CN1 as the 15V control supply. The 5V supply is directly connected to Pin 6 of the hybrid gate driver which is internally connected to the anode of the LED in the high speed opto-coupler. The 5V supply is also used to pull the output side of the fault isolation opto-couplers high.

Figure 3: BG2A External Wiring Diagram

Publication Date: 09-12-2014 Rev. 5 3

<sup>\*\*</sup> CS, CT are only required in certain special applications. Please see VLA500/VLA502 application notes for details.

The control signal interface is designed for use with standard 5V CMOS logic. The control input signals at Pins 2 and 3 of connector CN1 are used to turn the IGBTs on and off. These signals are active low which means that the gate driver output will be high (IGBT on) when they are pulled low. These control pins are connected directly to Pin 7 of the hybrid gate driver which is connected internally through a limiting resistor to the cathode of the LED in the high speed opto-coupler (see Figure 1). When the control signal is pulled low current flows from the 5V logic supply through the LED to turn the gate driver's output on. The control pins must be pulled low with a buffer that is capable of sinking 15mA in order to turn on the high speed opto-coupler inside the VLA500 series driver. A CMOS buffer that actively pulls its output high is recommended for maintaining good common mode noise immunity in the off state. Open collector type drive is not recommended.

The fault signal line on Pin 4 of CN1 is active low which means that a fault condition will be indicated by a low level signal. During normal operation Pin 4 is pulled high to the +5V supply (+VL) by the 4.7K resistor R3. If either of the VLA500 series gate drivers detects a short circuit condition the fault isolation optos (OP1, OP2) turn on and pull Pin 4 of CN1 low. When a fault is detected the hybrid gate drivers disable the output and produce a fault signal for a minimum of 1ms. Any signal on the fault line that is significantly shorter than 1ms cannot be a legitimate fault so it should be ignored. Therefore, for a robust noise immune design, it is recommended that an RC filter with a time constant of approximately 10µs be added between Pin 4 and the controller as shown in Figure 3.

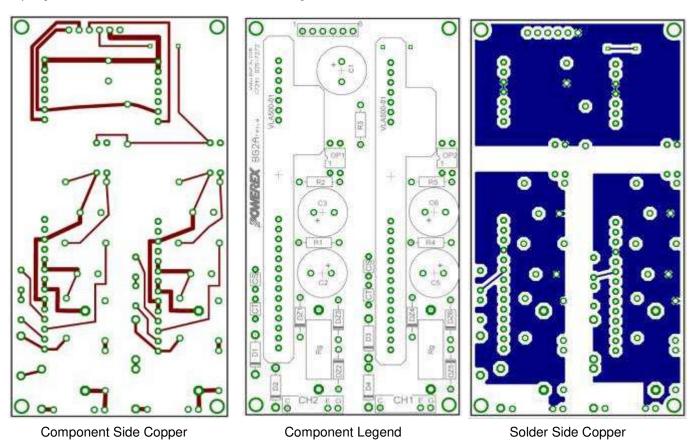

**Printed Circuit Layout:** Figure 4 shows the layout of the BG2A two channel gate driver board. The compact 4" x 2.1" circuit board with only 24 components clearly demonstrates the advantage of using the VLA500 series hybrid gate drivers. One important feature is the use of three ground plane islands for the regions of the PCB having high voltage differences. Two of the islands are tied to the emitter/circuit common (Pin 20) of each output channel. The third island is connected to logic interface common at Pin 6 of CN1. This layout prevents undesirable coupling of noise between the control side and the gate drive channels.

Figure 4: BG2A Printed Circuit Board Layout

Publication Date: 09-12-2014 Rev. 5 4