### **MAX22502E**

# 100Mbps Full-Duplex RS-485/RS-422 Transceiver for Long Cables

### **General Description**

The MAX22502E full-duplex, ESD-protected, RS-485/RS-422 transceiver is optimized for high-speed (up to 100Mbps) communication over long cables. This transceiver features larger receiver hysteresis for high noise rejection and improved signal integrity. Integrated preemphasis circuitry extends the distance, and increases the data rate, of reliable communication by reducing inter-symbol interference (ISI) caused by long cables when supplied with 5V. Integrated hot-swap protection and a fail-safe receiver ensure a logic-high on the receiver output when input signals are shorted or open for longer than 10µs (typ).

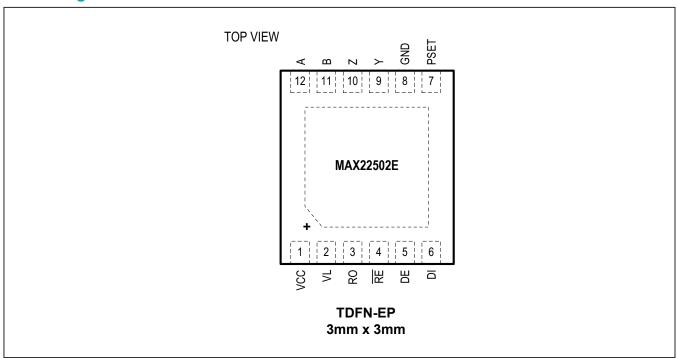

The MAX22502E is available in a 12-pin TDFN-EP (3mm x 3mm) package and operates over the -40°C to +125°C ambient temperature range.

### **Applications**

- Motion Control

- Encoder Interfaces

- Field Bus Networks

- Industrial Control Systems

- Backplane Busses

#### **Benefits and Features**

- High-Speed Operation Over Long Distances

- Up to 100Mbps Data Rate

- Integrated Preemphasis Extends Cable Length

- · High Receiver Sensitivity

- · Wide Receiver Bandwidth

- · Symmetrical Receiver Thresholds

- Integrated Protection Increases Robustness

- -15V to +15V Common Mode Range

- ±15kV ESD Protection (Human Body Model)

- ±7kV IEC61000-4-2 Air-Gap ESD Protection

- ±6kV IEC61000-4-2 Contact Discharge ESD Protection

- · Driver Outputs are Short-Circuit Protected

- Flexibility for Many Different Applications

- 3V to 5.5V Supply Range

- · Low Voltage Logic Supply Down to 1.6V

- Low 5µA (max) Shutdown Current

- Available in 12-pin TDFN (3mm x 3mm) Package

- -40°C to +125°C Operating Temperature Range

Ordering Information appears at end of data sheet.

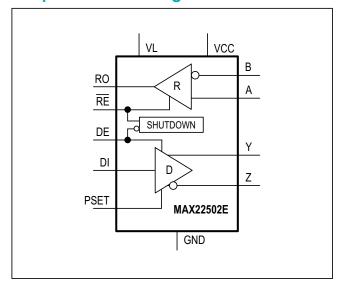

### **Simplified Block Diagram**

### MAX22502E

# 100Mbps Full-Duplex RS-485/RS-422 Transceiver for Long Cables

## **Absolute Maximum Ratings**

| V <sub>CC</sub> 0.3 V to +6 V                    | Continuous Power Dissipation (Multilayer Board (derate |

|--------------------------------------------------|--------------------------------------------------------|

| RE, DE, DI, VL0.3 V to +6 V                      | 24.4mW/°C above +70°C))1951mW                          |

| RO0.3 V to (V <sub>L</sub> + 0.3) V              | Operating Temperature Range40°C to +125°C              |

| PSET0.3 V to (V <sub>CC</sub> + 0.3) V           | Junction Temperature+150°C                             |

| A, B, Y, Z15V to +15V                            | Storage Temperature Range65°C to +150°C                |

| Short-Circuit Duration (RO, Y, Z) to GND         | Reflow Temperature+300°C                               |

| Continuous Power Dissipation (Single Layer Board |                                                        |

| (derate 15.9mW/°C above +70°C))1269mW            |                                                        |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Package Information**

### 12 TDFN-EP

| PACKAGE CODE                            | TD1233+1C |

|-----------------------------------------|-----------|

| Outline Number                          | 21-0664   |

| Land Pattern Number                     | 90-0397   |

| Thermal Resistance, Single-Layer Board: |           |

| Junction to Ambient (θ <sub>JA</sub> )  | 63°C/W    |

| Junction to Case (θ <sub>JC</sub> )     | 8°C/W     |

| Thermal Resistance, Four-Layer Board:   |           |

| Junction to Ambient (θ <sub>JA</sub> )  | 41°C/W    |

| Junction to Case (θ <sub>JC</sub> )     | 8°C/W     |

For the latest package outline information and land patterns (footprints), go to <u>www.maximintegrated.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

## **Electrical Characteristics**

(V<sub>CC</sub> = 3V to 5.5V, V<sub>L</sub> = 1.6V to V<sub>CC</sub>, V<sub>L</sub>  $\leq$  V<sub>CC</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted (Notes 1, 2) )

| PARAMETER                                          | SYMBOL             | CONDITIONS                                                    |                              | MIN   | TYP                | MAX             | UNITS |

|----------------------------------------------------|--------------------|---------------------------------------------------------------|------------------------------|-------|--------------------|-----------------|-------|

| POWER                                              |                    | I                                                             |                              |       |                    |                 |       |

| O                                                  |                    | Preemphasis disabled                                          |                              | 3.0   |                    | 5.5             |       |

| Supply Voltage                                     | V <sub>CC</sub>    | Preemphasis enabled                                           |                              | 4.5   | 5                  | 5.5             | V     |

| Supply Current                                     | Icc                | DE = high, RE = low, no                                       | DE = high, RE = low, no load |       | 12.7               | 16.5            | mA    |

| Shutdown Supply Current                            | I <sub>SHDN</sub>  | DE = low, RE = high                                           |                              |       |                    | 5               | μA    |

| Logic Supply Voltage                               | VL                 |                                                               |                              | 1.6   |                    | V <sub>CC</sub> | V     |

| Logic Supply Current                               | ΙL                 | No load on RO                                                 |                              |       | 16.4               | 23              | μA    |

| DRIVER                                             |                    |                                                               |                              |       |                    |                 |       |

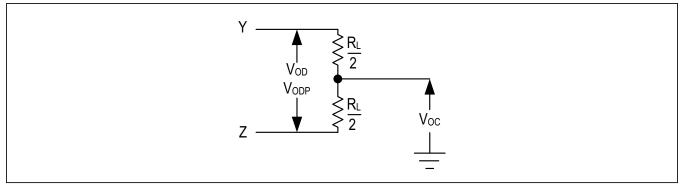

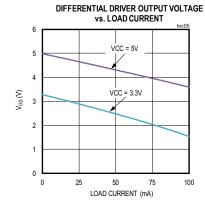

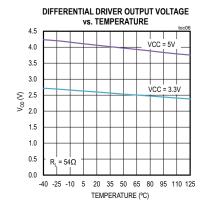

| Differential Driver Output                         | \/                 | Figure 1, Figure 2                                            | $R_L = 54\Omega$             | 1.5   |                    |                 | V     |

| Differential Driver Output                         | V <sub>OD</sub>    |                                                               | R <sub>L</sub> = 100Ω        | 2.0   |                    |                 | ]     |

| Differential Driver Preemphasis                    |                    | Preemphasis                                                   | $R_L = 54\Omega$             | 1.33  | 1.37               | 1.41            |       |

| Ratio                                              | D <sub>PRE</sub>   | PRE enabled, $4.5V \le V_{CC} \le 5.5V$ (Note 3) $R_L = 100Ω$ |                              | 1.33  | 1.37               | 1.41            | V/V   |

| Change in Magnitude of Differential Output Voltage | ΔV <sub>OD</sub>   | $R_L$ = 54Ω, Figure 1 (Note 4)                                |                              |       |                    | 0.2             | V     |

| Driver Common-Mode Output<br>Voltage               | V <sub>OC</sub>    | $R_L$ = 54Ω, Normal mode and preemphasis, Figure 1            |                              |       | V <sub>CC</sub> /2 | 3               | V     |

| Change In Magnitude of Common-Mode Voltage         | ΔV <sub>OC</sub>   | $R_L$ = 100Ω or 54Ω, Figure 1 (Note 4)                        |                              |       |                    | 0.2             | V     |

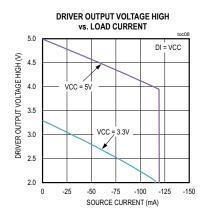

| Single-Ended Driver Output High                    | V <sub>OH</sub>    | Y or Z output                                                 | I <sub>OUT</sub> = -20mA     | 2.2   |                    |                 | V     |

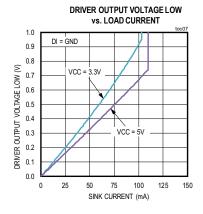

| Single-Ended Driver Output Low                     | V <sub>OL</sub>    | Y or Z output                                                 | I <sub>OUT</sub> = +20mA     |       |                    | 0.8             | V     |

| Differential Output Capacitance                    | C <sub>OD</sub>    | $DE = \overline{RE} = high, f = 4MH$                          | -lz                          |       | 50                 |                 | pF    |

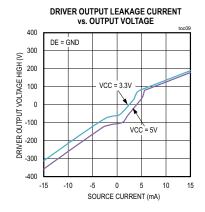

| Driver Short-Circuit Output<br>Current             | llostl             | -15V ≤ V <sub>OUT</sub> ≤ +15V                                |                              |       |                    | 250             | mA    |

| RECEIVER                                           |                    |                                                               |                              |       |                    |                 |       |

| Input Current (A and P)                            | I <sub>A,B</sub>   | DE = GND, V <sub>CC</sub> =                                   | V <sub>IN</sub> = +12V       |       |                    | +1100           |       |

| Input Current (A and B)                            |                    | GND, +3.6V or 5.5V                                            | V <sub>IN</sub> = -7V        | -1000 |                    |                 | μA    |

| Differential Input Capacitance                     | C <sub>A,B</sub>   | Between A and B, DE = GND,<br>f = 2MHz                        |                              |       | 50                 |                 | pF    |

| Common Mode Voltage Range                          | V <sub>CM</sub>    |                                                               |                              | -15   |                    | +15             | V     |

| Receiver Differential Threshold<br>High            | V <sub>TH_H</sub>  | -15V ≤ V <sub>CM</sub> ≤ +15V                                 |                              | +50   |                    | +200            | mV    |

| Receiver Differential Threshold<br>Low             | V <sub>TH_L</sub>  | -15V ≤ V <sub>CM</sub> ≤ +15V                                 |                              | -200  |                    | -50             | mV    |

| Receiver Input Hysteresis                          | ΔV <sub>TH</sub>   | V <sub>CM</sub> = 0V, time from las < t <sub>D_FS</sub>       | t transition is              |       | 250                |                 | mV    |

| Differential Input Fail-Safe Level                 | V <sub>TH</sub> FS | -15V ≤ V <sub>CM</sub> ≤ +15V                                 |                              | -50   |                    | +50             | mV    |

# **Electrical Characteristics (continued)**

(V<sub>CC</sub> = 3V to 5.5V, V<sub>L</sub> = 1.6V to V<sub>CC</sub>, V<sub>L</sub>  $\leq$  V<sub>CC</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted (Notes 1, 2) )

| PARAMETER                              | SYMBOL              | CONDITIONS                                                                                    | MIN                     | TYP  | MAX                  | UNITS |

|----------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|-------------------------|------|----------------------|-------|

| LOGIC INTERFACE (RE, RO, DE,           | DI)                 |                                                                                               |                         |      |                      |       |

| Input Voltage High                     | V <sub>IH</sub>     | DE, DI, RE                                                                                    | 2/3 x<br>V <sub>L</sub> |      |                      | V     |

| Input Voltage Low                      | V <sub>IL</sub>     | DE, DI, RE                                                                                    |                         |      | 1/3 x V <sub>L</sub> | V     |

| Input Current                          | I <sub>IN</sub>     | DI and DE, RE (after first transition)                                                        | -2                      |      | +2                   | μA    |

| Input Impedance on First Transition    | R <sub>IN_FT</sub>  | DE, RE                                                                                        |                         |      | 10                   | kΩ    |

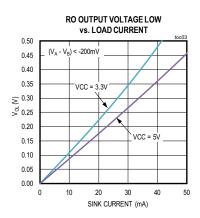

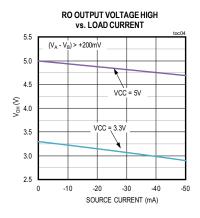

| RO Output Voltage High                 | V <sub>OH</sub>     | $\overline{RE}$ = GND, (V <sub>A</sub> - V <sub>B</sub> ) > 200mV,<br>I <sub>OUT</sub> = -1mA | V <sub>L</sub> - 0.4    |      |                      | V     |

| RO Output Low Voltage                  | V <sub>OL</sub>     | $\overline{RE}$ = GND, $(V_A - V_B) < -200$ mV,<br>$I_{OUT}$ = +1mA                           |                         |      | 0.4                  | V     |

| Three-State Output Current at Receiver | I <sub>OZR</sub>    | $\overline{RE}$ = high, $0 \le V_{RO} \le V_{L}$                                              | -1                      |      | +1                   | μA    |

| PROTECTION                             |                     |                                                                                               |                         |      |                      |       |

| Thermal Shutdown Threshold             | T <sub>SH</sub>     |                                                                                               |                         | +160 |                      | °C    |

| Thermal Shutdown Hysteresis            | T <sub>SH_HYS</sub> |                                                                                               |                         | 10   |                      | °C    |

|                                        |                     | Human Body Model                                                                              |                         | ±15  |                      |       |

| ESD Protection (A and B Pins)          |                     | IEC61000-4-2 Air Gap Discharge to GND                                                         |                         | ±7   |                      | kV    |

|                                        |                     | IEC61000-4-2 Contact Discharge to GND                                                         |                         | ±6   |                      |       |

| ESD Protection (All Other Pins)        |                     | Human Body Model                                                                              |                         | ±2   |                      | kV    |

# **Electrical Characteristics - Switching**

(V<sub>CC</sub> = 3V to 5.5V, V<sub>L</sub> = 1.6V to V<sub>CC</sub>, V<sub>L</sub>  $\leq$  V<sub>CC</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted (Note 1, 2) )

| PARAMETER                                     | SYMBOL                            | CONDITIONS                                                                                         |                                                           | MIN | TYP | MAX | UNITS |

|-----------------------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|-------|

| DRIVER (Note 5)                               |                                   | •                                                                                                  |                                                           | ,   |     |     |       |

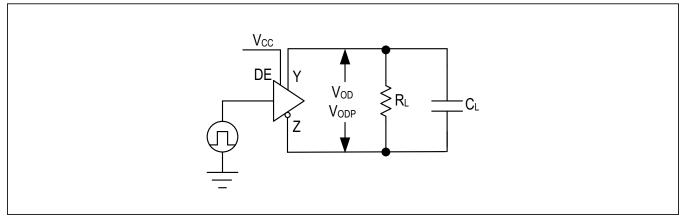

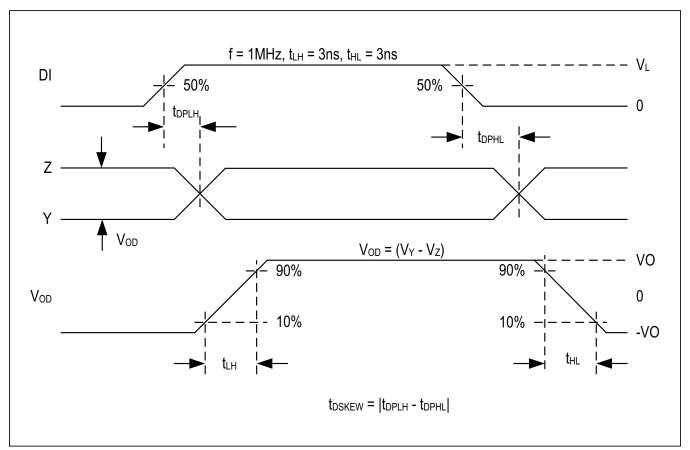

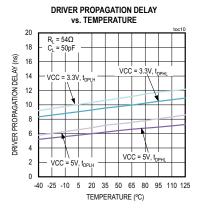

| Driver Brancastian Dalay                      | t <sub>DPLH</sub>                 | $R_L = 54\Omega$ , $C_L = 50$ pF, F                                                                | R <sub>L</sub> = 54Ω, C <sub>L</sub> = 50pF, Figures 3, 4 |     |     | 20  |       |

| Driver Propagation Delay                      | t <sub>DPHL</sub>                 | $R_L = 54\Omega, C_L = 50pF, F$                                                                    | igures 3, 4                                               |     |     | 20  | ns    |

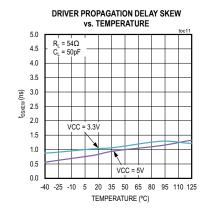

| Differential Driver Output Clean              |                                   | $ t_{DPLH} - t_{DPHL} ,$<br>$R_L = 54\Omega, C_L = 50pF,$<br><u>Figure 3, Figure 4</u><br>(Note 6) | $V_L = V_{CC},$<br>$V_{CC} \ge 3V$                        |     |     | 1.2 |       |

| Differential Driver Output Skew               | <sup>†</sup> DSKEW                | $ t_{DPLH} - t_{DPHL} ,$ $R_L = 54\Omega, C_L = 50pF,$ <u>Figure 3, Figure 4</u> (Note 6)          | V <sub>L</sub> does not equal V <sub>CC</sub>             |     |     | 1.6 | - ns  |

| Driver Differential Output Rise and Fall Time | t <sub>HL</sub> , t <sub>LH</sub> | $R_L = 54\Omega$ , $C_L = 50pF$ , Figure 4 (Note 6)                                                |                                                           |     |     | 3   | ns    |

| Data Rate                                     | DR                                |                                                                                                    |                                                           |     |     | 100 | Mbps  |

### **Electrical Characteristics - Switching (continued)**

(V<sub>CC</sub> = 3V to 5.5V, V<sub>L</sub> = 1.6V to V<sub>CC</sub>, V<sub>L</sub>  $\leq$  V<sub>CC</sub>, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted (Note 1, 2) )

| PARAMETER                                    | SYMBOL                  | CONDITIO                                                                   | ONS                       | MIN | TYP | MAX | UNITS |

|----------------------------------------------|-------------------------|----------------------------------------------------------------------------|---------------------------|-----|-----|-----|-------|

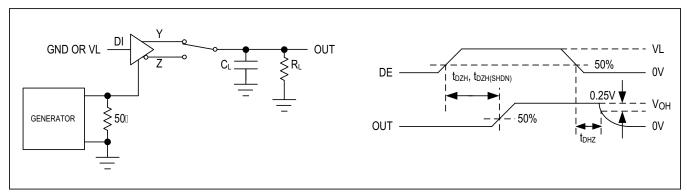

| Driver Enable to Output High                 | t <sub>DZH</sub>        | $R_L = 500\Omega$ , $C_L = 50pF$ ,                                         |                           |     | 30  | ns  |       |

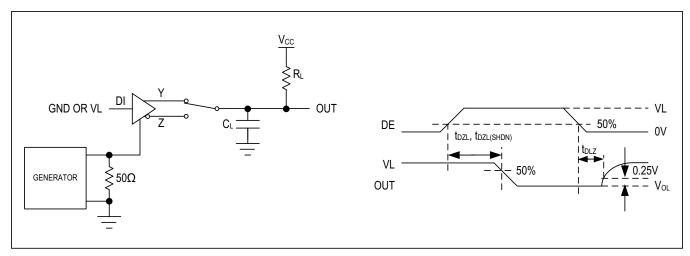

| Driver Enable to Output Low                  | t <sub>DZL</sub>        | R <sub>L</sub> = 500Ω, C <sub>L</sub> = 50pF, <u>F</u>                     | igure 5, Figure 6         |     |     | 30  | ns    |

| Driver Disable Time from Low                 | t <sub>DLZ</sub>        | $R_L = 500\Omega$ , $C_L = 50pF$ ,                                         | Figure 5, Figure 6        |     |     | 30  | ns    |

| Driver Disable Time from High                | t <sub>DHZ</sub>        | $R_L = 500\Omega$ , $C_L = 50pF$ ,                                         | Figure 5, Figure 6        |     |     | 30  | ns    |

| Driver Enable from Shutdown to Output High   | <sup>t</sup> DZH(SHDN)  | $R_L$ = 1kΩ, $C_L$ = 15pF, $F_1$                                           | gure 5, Figure 6          |     |     | 100 | μs    |

| Driver Enable from Shutdown to Output Low    | t <sub>DZL</sub> (SHDN) | $R_L = 1k\Omega$ , $C_L = 15pF$ , Fi                                       | gure 5, Figure 6          |     |     | 100 | μs    |

| Time to Shutdown                             | tshdn                   | (Note 7, Note 8)                                                           |                           | 50  |     | 800 | ns    |

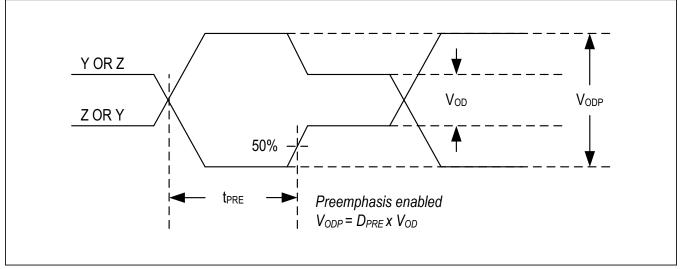

| Deiter Berner Letter et                      | 4                       | $4.5V \le V_{CC} \le 5.5V$ ,                                               | $R_{PSET} = 4k\Omega$     | 10  | 13  | 16  | ns    |

| Driver Preemphasis Interval                  | t <sub>PRE</sub>        | Figure 2                                                                   | R <sub>PSET</sub> = 400kΩ | 0.8 | 1   | 1.2 | μs    |

| RECEIVER (Note 5)                            |                         |                                                                            |                           |     |     |     |       |

| Delay to Fail-Safe Operation                 | t <sub>D FS</sub>       |                                                                            |                           |     | 10  |     | μs    |

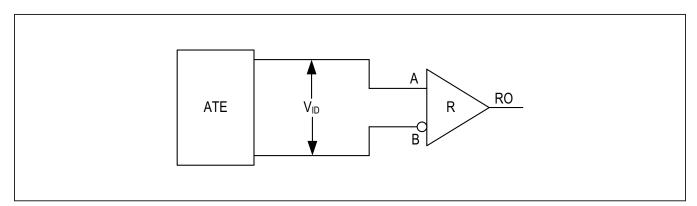

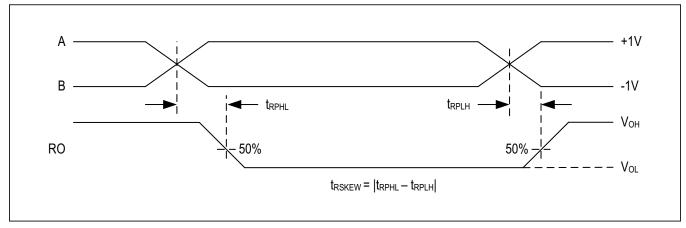

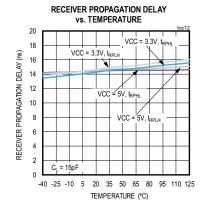

| B B                                          | t <sub>RPLH</sub>       | C <sub>L</sub> = 15pF, <u>Figure 7</u> , <u>Figure 8</u>                   |                           |     |     | 20  |       |

| Receiver Propagation Delay                   | t <sub>RPHL</sub>       | C <sub>L</sub> = 15pF, <u>Figure 7</u> , <u>Figure 8</u>                   |                           |     |     | 20  | ns    |

| Receiver Output Skew                         | t <sub>RSKEW</sub>      | t <sub>RPHL</sub> - t <sub>RPLH</sub>  , C <sub>L</sub> = 15<br>  Figure 8 | pF, <u>Figure 7</u> ,     |     |     | 2.5 | ns    |

| Data Rate                                    | DR                      |                                                                            |                           |     |     | 100 | Mbps  |

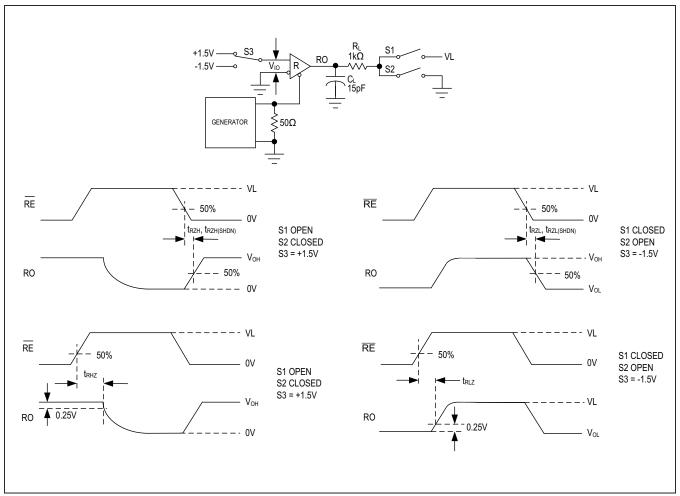

| Receiver Enable to Output High               | t <sub>RZH</sub>        | $R_L = 1k\Omega$ , $C_L = 15pF$ , Fi                                       | gure 9                    |     |     | 30  | ns    |

| Receiver Enable to Output Low                | t <sub>RZL</sub>        | $R_L = 1k\Omega$ , $C_L = 15pF$ , Fi                                       | gure 9                    |     |     | 30  | ns    |

| Receiver Disable Time from Low               | t <sub>RLZ</sub>        | $R_L = 1k\Omega$ , $C_L = 15pF$ , Fi                                       | gure 9                    |     |     | 30  | ns    |

| Receiver Disable Time from High              | t <sub>RHZ</sub>        | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 9                                 |                           |     |     | 30  | ns    |

| Receiver Enable from Shutdown to Output High | t <sub>RZH</sub> (SHDN) | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 9                                 |                           |     |     | 100 | μs    |

| Receiver Enable from Shutdown to Output Low  | t <sub>RZL</sub> (SHDN) | $R_L = 1k\Omega$ , $C_L = 15pF$ , Figure 9                                 |                           |     |     | 100 | μs    |

| Time to Shutdown                             | tshdn                   | (Note 7, Note 8)                                                           |                           | 50  |     | 800 | ns    |

- Note 1: All devices are 100% production tested at  $T_A = +25$ °C. Specifications for all temperature limits are guaranteed by design.

- **Note 2:** All currents into the device are positive; all currents out of the device are negative. All voltages are referenced to device ground, unless otherwise noted.

- Note 3: V<sub>ODP</sub> is the differential voltage between Y and Z during the preemphasis interval and is the differential voltage when preemphasis is disabled. V<sub>ODP</sub> = D<sub>PRE</sub> x V<sub>OD</sub>.

- Note 4:  $\Delta V_{OD}$  and  $\Delta V_{OC}$  are the changes in  $V_{OD}$  and  $V_{OC}$ , respectively, when the DI input changes state.

- Note 5: Capacitive load includes test probe and fixture capacitance.

- Note 6: Not production tested. Guaranteed by design.

- Note 7: Shutdown is enabled by driving RE high and DE low. The device is guaranteed to have entered shutdown after t<sub>SHDN</sub> has elapsed.

- **Note 8:** The timing parameter refers to the driver or receiver enable delay, when the device has exited the initial hot-swap protect state and is in normal operating mode.

Figure 1. Driver DC Test Load

Figure 2. Driver Preemphasis Timing

Figure 3. Driver Timing Test Circuit

Figure 4. Driver Propagation Delays

Figure 5. Driver Enable and Disable Times (t<sub>DZH</sub>, t<sub>DHZ</sub>)

Figure 6. Driver Enable and Disable Times ( $t_{\rm DZL},\,t_{\rm DLZ}$ )

Figure 7. Receiver Propagation Delay Test Circuit

Figure 8. Receiver Propagation Delays

Figure 9. Receiver Enable and Disable Times

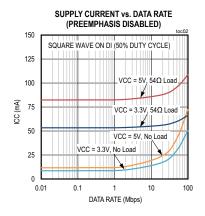

# **Typical Operating Characteristics**

$V_{CC}$  = 5V, VL =  $V_{CC}$ ,  $60\Omega$  termination between Y and Z,  $T_A$  = 25°C, unless otherwise noted.

#### SUPPLY CURRENT vs. DATA RATE (PREEMPHASIS ENABLED) 150 SQUARE WAVE ON DI (50% DUTY CYCLE) PSET RESISTOR ADJUSTED FOR EACH DATA RATE 125 100 54Ω Load ICC (mA) 75 50 25 No Load 0.1 100 DATA RATE (Mbps)

# **Typical Operating Characteristics (continued)**

$V_{CC}$  = 5V, VL =  $V_{CC}$ , 60 $\Omega$  termination between Y and Z,  $T_A$  = 25°C, unless otherwise noted.

# **Pin Configuration**

# **Pin Description**

### MAX22502E

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                              |

|-----|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>CC</sub> | Supply Input. Bypass V <sub>CC</sub> to ground with a 0.1µF ceramic capacitor as close to the device as possible.                                                                                                                                                                     |

| 2   | VL              | Logic Supply Input. $V_L$ defines the interface logic levels on DE, DI, and RO. Apply a voltage between 1.6V to 5.5V to $V_L$ . Ensure that $V_L \le V_{CC}$ for normal operation. Bypass $V_L$ to ground with a 0.1 $\mu$ F capacitor as close to the device as possible.            |

| 3   | RO              | Receiver Output. See the <u>Receiving Function Table</u> for more information.                                                                                                                                                                                                        |

| 4   | RE              | Receiver Enable. Set $\overline{RE}$ high to disable the receiver and tri-state RO. The device is in low-power shutdown when $\overline{RE}$ = high and DE = low.                                                                                                                     |

| 5   | DE              | Driver Output Enable. Set DE high to enable driver. Set DE low to three-state the driver output.                                                                                                                                                                                      |

| 6   | DI              | Driver Input. See the <u>Transmitting Function Table</u> for more information.                                                                                                                                                                                                        |

| 7   | PSET            | Preemphasis Select Control Input. Connect a resistor from PSET to GND to select the preemphasis duration. See the <u>Layout Recommendations</u> in the <u>Applications Information</u> section for more information. To disable preemphasis, connect PSET to GND or V <sub>CC</sub> . |

| 8   | GND             | Ground                                                                                                                                                                                                                                                                                |

| 9   | Y               | Noninverting Driver Output                                                                                                                                                                                                                                                            |

| 10  | Z               | Inverting Driver Output                                                                                                                                                                                                                                                               |

| 11  | В               | Inverting Receiver Input                                                                                                                                                                                                                                                              |

| 12  | А               | Noninverting Receiver Input                                                                                                                                                                                                                                                           |

# **Functional Diagrams**

## **Transmitting Function Table**

| INPUTS |    |    | OUTPUTS                              |                |  |  |

|--------|----|----|--------------------------------------|----------------|--|--|

| RE     | DE | DI | Y                                    | z              |  |  |

| Х      | 1  | 1  | 1                                    | 0              |  |  |

| Х      | 1  | 0  | 0                                    | 1              |  |  |

| 0      | 0  | Х  | High Impedance                       | High Impedance |  |  |

| 1      | 0  | Х  | Shutdown. Y and Z are high-impedance |                |  |  |

X = Don't care

## **Receiving Function Table**

|    |    |                                                                            | _                             |                                                  |

|----|----|----------------------------------------------------------------------------|-------------------------------|--------------------------------------------------|

|    |    | INPUTS                                                                     |                               | OUTPUTS                                          |

| RE | DE | (V <sub>A</sub> - V <sub>B</sub> )                                         | Time from Last A-B Transition | RO                                               |

| 0  | Х  | ≥ V <sub>TH_H</sub>                                                        | Always                        | 1                                                |

| 0  | X  | V <sub>TH_L</sub> < (V <sub>A</sub> - V <sub>B</sub> ) < V <sub>TH_H</sub> | < t <sub>D_FS</sub>           | Indeterminate<br>RO is latched to previous value |

| 0  | Х  | -50mV < (V <sub>A</sub> - V <sub>B</sub> ) < +50mV                         | > t <sub>D_FS</sub>           | 1                                                |

| 0  | Х  | ≤ V <sub>TH_L</sub>                                                        | Always                        | 0                                                |

| 0  | Х  | Open/Shorted                                                               | > t <sub>D_FS</sub>           | 1                                                |

| 1  | 1  | X                                                                          | X                             | High Impedance                                   |

| 1  | 0  | X                                                                          | X                             | Shutdown. RO is high-impedance                   |

|    |    |                                                                            |                               |                                                  |

X = Don't care

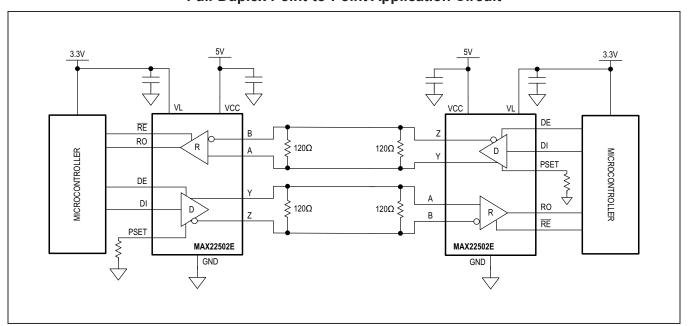

# **Full-Duplex Point-to-Point Application Circuit**

# 100Mbps Full-Duplex RS-485/RS-422 Transceiver for Long Cables

### **Detailed Description**

The MAX22502E ESD-protected RS-485/RS-422 transceiver is optimized for high-speed, full-duplex communications over long cables. This transceiver features integrated hot-swap functionality to eliminate false transitions on the driver during power-up or during a hot-plug event. Fail-safe receiver inputs guarantee a logic-high on the receiver output when inputs are shorted or open for longer than 10µs (typ).

### **Receiver Threshold Voltages**

The MAX22502E receiver features a large threshold hysteresis of 250mV (typ) for increased differential noise rejection.

Additionally, the receiver features symmetrical threshold voltages. Symmetric thresholds have the advantage that recovered data at the RO output does not have duty cycle distortion. Typically, fail-safe receivers, which have unipolar (non-symmetric) thresholds, show some duty cycle distortion at high signal attenuation due to long cable lengths.

#### **Preemphasis**

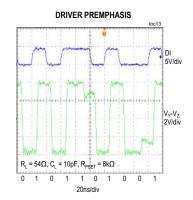

When powered by 5V, the MAX22502E features integrated driver preemphasis circuitry, which strongly improves signal integrity at high data rates over long distances by reducing intersymbol interference (ISI) caused by long cables. Preemphasis is set by connecting a resistor (RPSET) between PSET and ground.

Long cables attenuate the high-frequency content of transmitted signals due to the cable's limited bandwidth. This causes signal/pulse distortion at the receiving end, resulting in ISI. ISI causes jitter in data and clock recovery circuits. ISI can be visualized by considering the following cases: If a series of ones (1s) is transmitted, followed by a zero (0), the transmission-line voltage has risen to a high value by the end of the string of ones. It takes longer for the signal to move toward the '0' state because the starting voltage on the line is so far from the zero crossing. Similarly, if a data pattern has a string of zeros followed by a one and then another zero, the one-to-zero transition starts from a voltage that is much closer to the zero crossing (V<sub>Y</sub> - V<sub>Z</sub> = 0) and it takes much less time for the signal to reach the zero crossing.

Preemphasis reduces ISI by boosting the differential signal amplitude at every transition edge, counteracting the high frequency attenuation of the cable. When the DI input changes from a logic low to a logic high, the differential output ( $V_Y$  -  $V_Z$ ) is driven high to  $V_{ODP}$ . At the end of the preemphasis interval, the differential voltage returns to a lower level ( $V_{OD}$ ). The preemphasis differential high voltage ( $V_{ODP}$ ) is typically 1.37 times the  $V_{OD}$  voltage.

If DI switches back to a logic-low state before the preemphasis interval ends, the differential output switches directly from the 'strong'  $V_{ODP}$  high to a 'strong' low  $(-V_{ODP})$ .

Driver behavior is similar when the DI input changes from a logic-high to a logic-low. When this occurs, the differential output is pulled low to - $V_{ODP}$  until the end of the preemphasis interval, at which point  $V_Y$  -  $V_Z$  = - $V_{ODP}$ .

#### **Preemphasis Setting**

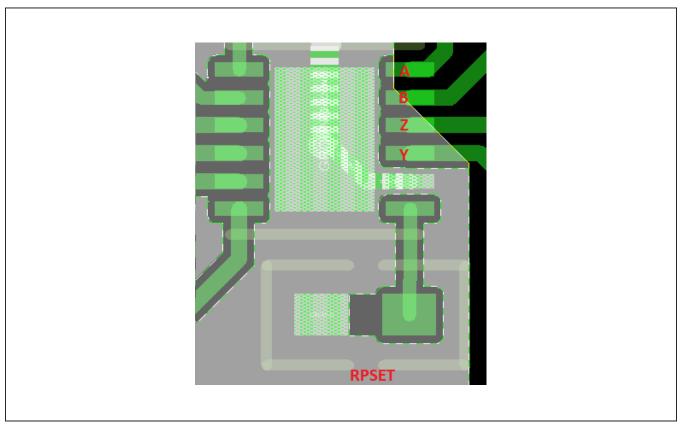

Connect a resistor (R<sub>PSET</sub>) between PSET and GND to set the preemphasis time interval on the MAX22502E. An optimum preemphasis interval ranges from 1 to 1.5 unit intervals (bit time). Use the following equation to calculate the resistance needed on PSET to achieve a 1.2 preemphasis interval:

$$R_{PSFT} = 400x109/DR$$

where DR is the data rate and 1Mbps  $\leq$  DR  $\leq$  100Mbps.

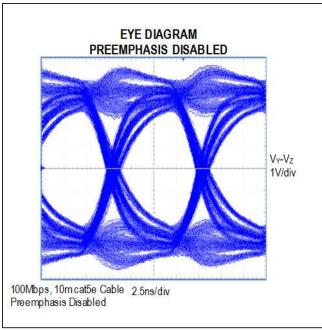

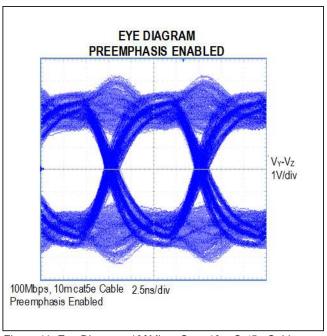

Preemphasis only minimally degrades the jitter on the eye diagram when using short cables, making it reasonable to permanently enable preemphasis on systems where cable lengths may vary or change. Figure 10 and Figure 11 are eye diagrams taken at 100Mbps over a 10m cat5e cable. Note that the eye varies only slightly as preemphasis is enabled or disabled.

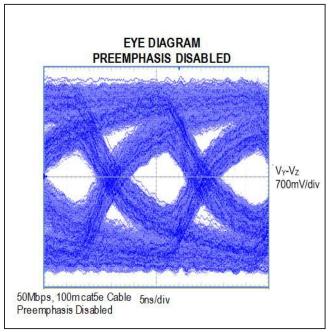

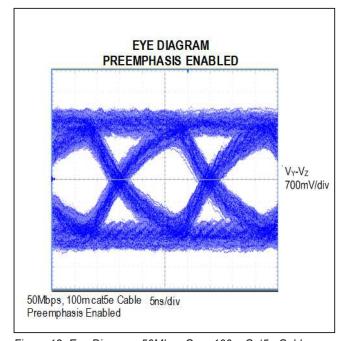

Figure 12 and Figure 13 show the driver eye diagrams over a long cable length. The MAX22502E was used as the driver and the eye diagrams were taken at the receiver input after a length of 100m cat5e cable. Figure 12 shows the signal at the receiver when the driver preemphasis is disabled. Figure 13 shows the receiver signal when preemphasis is enabled.

#### **Fail-Safe Functionality**

The MAX22502E features fail-safe receiver inputs, guaranteeing a logic-high on the receiver output (RO) when the receiver inputs are shorted or open for longer than 10µs (typ). When the differential receiver input voltage is less than 50mV for more than 10µs (typ), RO is logic-high. For example, in the case of a terminated bus with all transmitters disabled, the receiver's differential input voltage is pulled to 0V by the termination resistor, so ( $V_A - V_B = 0V$ ) > -50mV and RO is guaranteed to be a logic-high after 10µs (typ).

#### **Driver Single-Ended Operation**

The Y and Z outputs on the MAX22502E can be used in the standard differential operating mode or as single-ended outputs. Because the driver outputs swing rail-to-rail, they can also be used as individual standard TTL logic outputs.

Figure 10. Eye Diagram, 100Mbps Over 10m Cat5e Cable, Preemphasis Disabled,  $V_{CC} = V_L = 5V$

Figure 11. Eye Diagram, 100Mbps Over 10m Cat5e Cable, Preemphasis Enabled,  $V_{CC} = V_L = 5V$

Figure 12. Eye Diagram, 50Mbps Over 100m Cat5e Cable, Preemphasis Disabled,  $V_{\rm CC}$  =  $V_{\rm L}$  = 5V

Figure 13. Eye Diagram, 50Mbps Over 100m Cat5e Cable, Preemphasis Enabled,  $V_{\rm CC}$  =  $V_{\rm L}$  = 5V

# 100Mbps Full-Duplex RS-485/RS-422 Transceiver for Long Cables

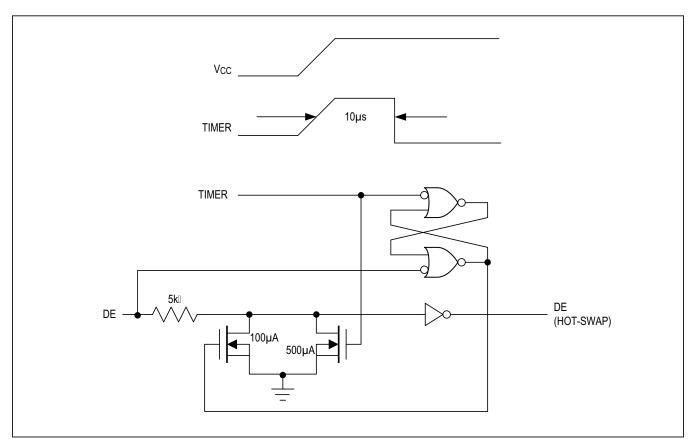

### **Hot-Swap Capability**

The DE and RE enable inputs feature hot-swap functionality. At each input there are two NMOS devices, M1 and M2 (Figure 14). When V<sub>CC</sub> ramps from zero, an internal 10ms timer turns on M2 and sets the SR latch, which also turns on M1. Transistors M2, a 500µA current sink, and M1, a 100 $\mu$ A current sink, pull DE to GND through a 5k $\Omega$ resistor. M2 is designed to pull DE to the disabled state against an external parasitic capacitance up to 100pF that can drive DE high. After 10µs, the timer deactivates M2 while M1 remains on, holding DE low against three-state leakages that can drive DE high. M1 remains on until an external source overcomes the required input current. At this time, the SR latch resets and M1 turns off. When M1 turns off, DE reverts to a standard, high-impedance CMOS input. Whenever V<sub>CC</sub> drops below 1V, the hotswap input is reset.

There is a complimentary circuit for  $\overline{RE}$  that uses two PMOS devices to pull  $\overline{RE}$  to  $V_{CC}$ .

#### **Driver Output Protection**

Two mechanisms prevent excessive output current and power dissipation caused by faults or by bus contention. The first, a current limit on the output stage provides immediate protection against short circuits over the whole common-mode voltage range. The second, a thermal-shutdown circuit, forces the driver outputs into a high-impedance state if the die temperature exceeds +160°C (typ).

#### Low-Power Shutdown Mode

The MAX22502E features low-power shutdown mode to reduce supply current when the transceiver is not needed. Pull the  $\overline{RE}$  input high and the DE input low to put the device in low-power shutdown mode. If the inputs are in this state for at least 800ns, the part is guaranteed to enter shutdown. The MAX22502E draws  $5\mu A$  (max) of supply current when the device is in shutdown.

The  $\overline{\text{RE}}$  and DE inputs can be driven simultaneously. The MAX22502E is guaranteed not to enter shutdown if  $\overline{\text{RE}}$  is high and DE is low for less than 50ns.

Figure 14. Simplified Structure of the Driver Enable (DE) Pin

# 100Mbps Full-Duplex RS-485/RS-422 Transceiver for Long Cables

### **Applications Information**

#### Powering the MAX22502E

No particular power supply sequencing is required for the MAX22502 V<sub>CC</sub> and V<sub>L</sub> supplies during power-up. However, ensure that V<sub>L</sub>  $\leq$  V<sub>CC</sub> for normal operation.

#### **Layout Recommendations**

Ensure that the preemphasis set resistor ( $R_{PSET}$ ) is located close to the PSET and GND pins in order to minimize interference by other signals. Minimize the trace length to the PSET resistor. Additionally, place a ground plane under  $R_{PSET}$  and surround it with ground connections/ traces to minimize interference from the A and B switching signals. See Figure 15.

#### **Network Topology**

The MAX22502E transceiver is designed for high-speed bidirectional RS-485/RS-422 data communications. Multidrop networks can cause impedance discontinuities which affect signal integrity. Maxim recommends using a point-to-point network topology, instead of a multidrop topology, when communicating with high data rates. Terminate the transmission line at both ends with the cable's characteristic impedance to reduce reflections.

Figure 15. Sample PSET Resistor Placement

# **Ordering Information**

| PART           | PREEMPHASIS | LOGIC SUPPLY | PIN-PACKAGE | PACKAGE<br>CODE |

|----------------|-------------|--------------|-------------|-----------------|

| MAX22502EATC+  | Υ           | Υ            | TDFN12-EP*  | TD1233+1C       |

| MAX22502EATC+T | Υ           | Υ            | TDFN12-EP*  | TD1233+1C       |

<sup>+</sup>Denotes a lead (Pb)-free/RoHS-compliant package.

<sup>\*</sup>EP = Exposed Pad

### MAX22502E

# 100Mbps Full-Duplex RS-485/RS-422 Transceiver for Long Cables

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                           | PAGES<br>CHANGED |

|--------------------|------------------|---------------------------------------|------------------|

| 0                  | 8/17             | Initial release                       | _                |

| 1                  | 4/19             | Corrected part references in the text | 14, 17           |

| .1                 |                  | Corrected typo in Figure 8            | 8                |

For pricing, delivery, and ordering information, please visit Maxim Integrated's online storefront at https://www.maximintegrated.com/en/storefront/storefront.html.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.