Freescale Semiconductor Advance Information

System Basis Chip with Low Speed Fault Tolerant CAN

The 33389 is a monolithic integrated circuit combining many functions frequently used by automotive Engine Control Units (ECUs). It incorporates a low speed fault tolerant CAN transceiver.

#### Features

- Dual Low Drop Voltage Regulators, with Respectively 100 mA and 200 mA Current Capabilities, Current Limitation, and Over Temperature Detection with Pre-warning

- 5.0 V Output Voltage for V1 Regulator

- Three Operational Modes (Normal, Stand-by, and Sleep Modes) Separated from the CAN Interface Operating Modes

- Low Speed 125 kBaud Fault Tolerant CAN Interface, Compatible with 33388 Stand Alone Physical Interface

- V1 Regulator Monitoring and Reset Function

- Three External High Voltage Wake-Up Inputs, Associated with V3  $\rm V_{BAT}$  Switch

- 100 mA Output Current Capability for V3 V<sub>BAT</sub> Switch Allowing Drive of External Switches or Relays

- · Low Stand-by and Sleep Current Consumption

- V<sub>BAT</sub> Monitoring and V<sub>BAT</sub> Failure Detection Capabilities

- DC Operating Voltage up to 27 V

- 40 V Maximum Transient Voltage

- · Programmable Software Window Watchdog and Reset

- Wake-Up Capabilities (CAN Interface, Local Programmable Cycle Wake

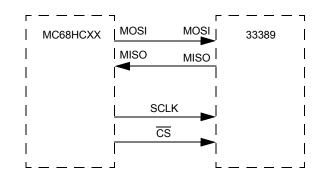

- · INterface with the MCU through the SPI

- · Pb-Free Packaging Designated by Suffix Codes VW and EG

| ORDERING INFORMATION |                                        |         |  |  |

|----------------------|----------------------------------------|---------|--|--|

| Device               | Temperature<br>Range (T <sub>A</sub> ) | Package |  |  |

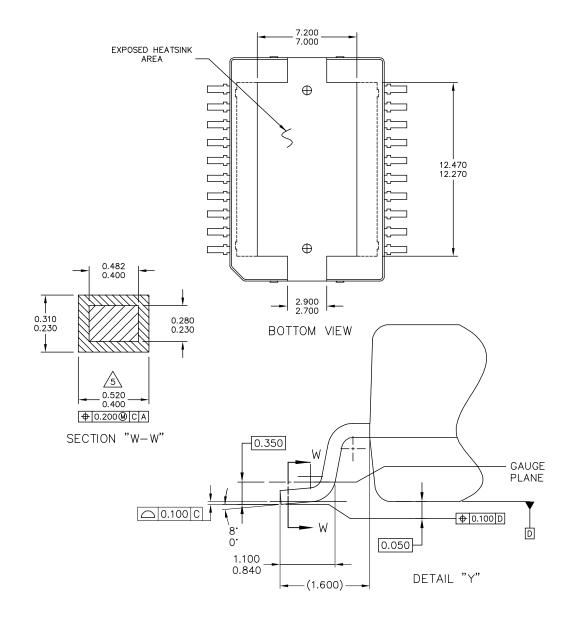

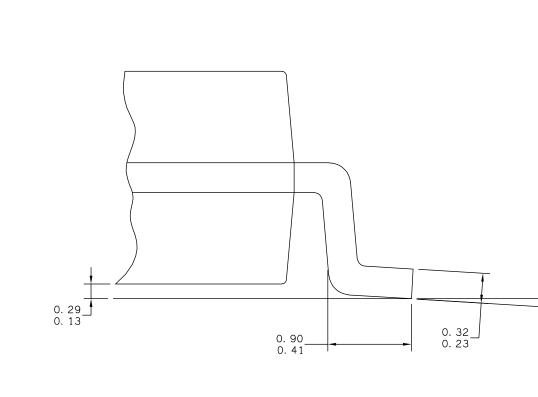

| MC33389CDH/R2        |                                        | HSOP-20 |  |  |

| MC33389CVW/R2        | -40 to 125°C                           | H30F-20 |  |  |

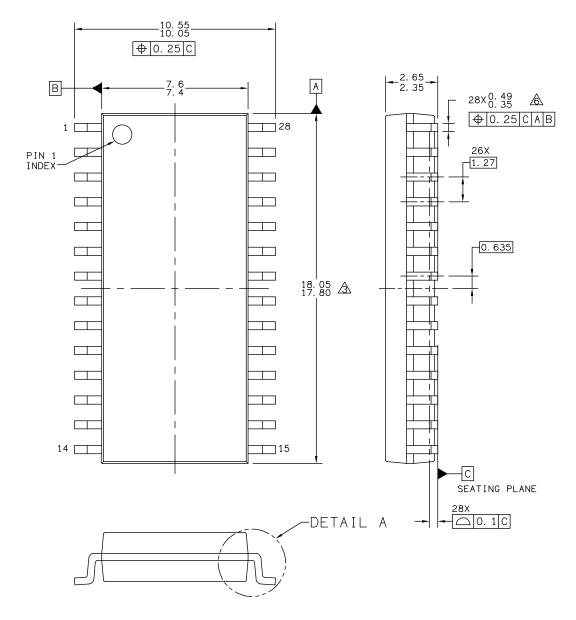

| MC33389CDW/R2        | -40 10 125 C                           | SO-28   |  |  |

| MC33389DDW/R2        |                                        | 30-28   |  |  |

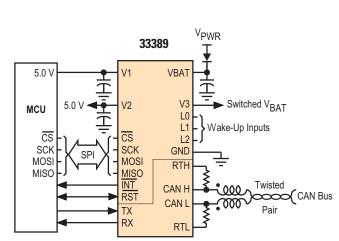

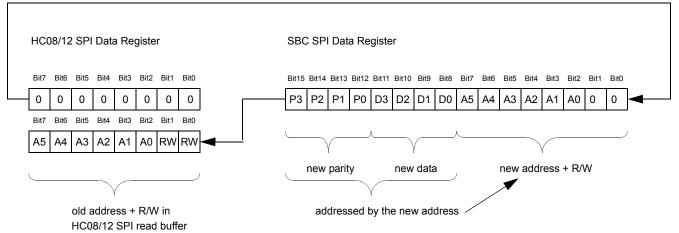

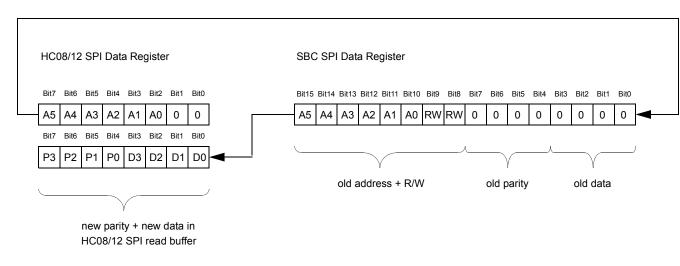

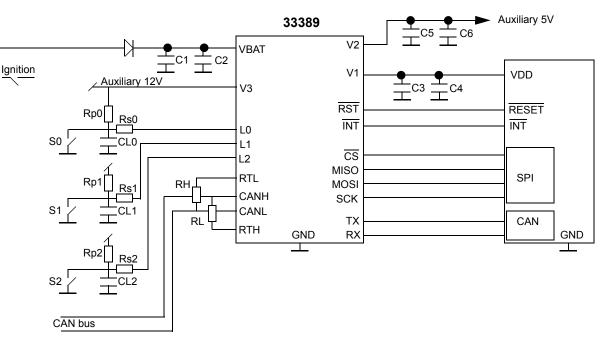

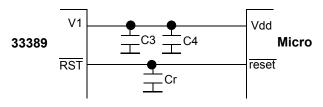

Figure 1. 33389 Simplified Application Diagram

\* This document contains certain information on a new product. Specifications and information herein are subject to change without notice.

© Freescale Semiconductor, Inc., 2007. All rights reserved.

Document Number: MC33389 Rev. 5.0, 3/2007

## **DEVICE VARIATIONS**

#### Table 1. Device Variations

| Freescale Part No.                     | V1 Undervoltage                                                                                                                                                            |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MC33389CDH<br>MC33389CVW<br>MC33389CDW | In V1 undervoltage condition, device remains in permanent reset state until V1 returns to normal conditions. V1 is protected by overcurrent and overtemperature functions. |

| MC33389DDW                             | The sole difference between the C version and the D version is V1 Reset Threshold.<br>Reference V1 Reset Threshold on V1 on page 9.                                        |

Archived Archived Archiver Arc

**RCHIVE INFORMATION**

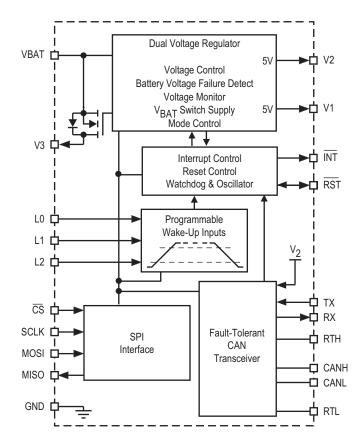

## INTERNAL BLOCK DIAGRAM

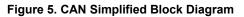

## **PIN CONNECTIONS**

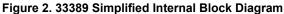

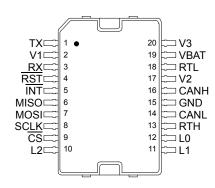

#### Figure 3. 33389 Pin Connections

#### Table 1. 33389 Pin Definitions: HSOSP 20-Lead

A functional description of each pin can be found in the Functional Pin Description section beginning on page 17.

| Pin Number | Pin Name | Formal Name                    | Definition                                                                                                                                                 |

|------------|----------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | ТХ       | Transmitter Data               | Transmitter input of the LS CAN interface                                                                                                                  |

| 2          | V1       | Voltage Regulator One          | This 5.0 V pin is a 3% low drop voltage regulator dedicated to the microcontroller supply.                                                                 |

| 3          | RX       | Receiver Data                  | Receiver output of the LS CAN interface                                                                                                                    |

| 4          | RST      | Reset                          | This is an Input/Output pin.                                                                                                                               |

| 5          | INT      | Interrupt Output               | This output is asserted LOW when an enabled interrupt condition occurs.                                                                                    |

| 6          | MISO     | Master In/Slave Out            | This pin is the tri-state output from the shift register.                                                                                                  |

| 7          | MOSI     | Master Out/Slave In            | This pin is for the input of serial instruction data.                                                                                                      |

| 8          | SCLK     | System Clock                   | This pin clocks the internal shift registers.                                                                                                              |

| 9          | CS       | Chip Select                    | This pin communicates with the system MCU and enables SPI communication.                                                                                   |

| 10 - 12    | L0 - L2  | Level 0 - 2 inputs<br>(L0: L2) | Input interfaces to external circuitry. Levels at these pins can be read by SPI and input can be used as programmable wake-up input in Sleep or Stop mode. |

| 13         | RTH      | RTH                            | Pin for the connection of the bus termination to CANH                                                                                                      |

| 14         | CANL     | CAN Low                        | CAN low input/output                                                                                                                                       |

| 15         | GND      | Ground                         | This pin is the ground of the integrated circuit.                                                                                                          |

| 16         | CANH     | CAN High                       | CAN high input/output                                                                                                                                      |

| 17         | V2       | Voltage Regulator Two          | This 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.                                                                        |

| 18         | RTL      | RTL                            | Pin for the connection of the bus termination to CANL                                                                                                      |

| 19         | VBAT     | Voltage Battery                | This pin is voltage supply from the battery.                                                                                                               |

| 20         | V3       | Voltage Regulator<br>Three     | This pin is a 10 $\Omega$ switch to $V_{\text{BAT}}$ , used to supply external contacts or relays.                                                         |

RCHIVE

NFORMATION

| TX 📼   | 1 • | 28 | V3     |

|--------|-----|----|--------|

| V1 🞞   | 2   | 27 | D VBAT |

| RX 💷   | 3   | 26 | 💷 RTL  |

| RST 📖  | 4   | 25 | V2     |

|        | 5   | 24 | CANH   |

| GND 📼  | 6   | 23 | 💷 GND  |

| GND 📼  | 7   | 22 | 💷 GND  |

| GND 📼  | 8   | 21 | 💷 GND  |

| GND 📼  | 9   | 20 | 💷 GND  |

| MISO 📼 | 10  | 19 |        |

| MOSI 📼 | 11  | 18 | 💷 RTH  |

| SCLK 🖂 | 12  | 17 | D NC   |

| CS     | 13  | 16 | L0     |

| L2 📼   | 14  | 15 | □ L1   |

|        |     |    |        |

#### Table 2. 33389 Pin Definitions: SOICW 28-Lead

A functional description of each pin can be found in the Functional Pin Description section beginning on page 17.

| Pin Number   | Pin<br>Name | Formal Name                | Definition                                                                                                                                                 |

|--------------|-------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1            | ТХ          | Transmitter Data           | Transmitter input of the LS CAN interface                                                                                                                  |

| 2            | V1          | Voltage Regulator<br>One   | This 5.0 V pin is a 3% low drop voltage regulator dedicated to the microcontroller supply.                                                                 |

| 3            | RX          | Receiver Data              | Receiver output of the LS CAN interface                                                                                                                    |

| 4            | RST         | Reset                      | This is an Input/Output pin.                                                                                                                               |

| 5            | INT         | Interrupt                  | This output is asserted LOW when an enabled interrupt condition occurs.                                                                                    |

| 6 -9 20 - 23 | GND         | Ground                     | These device ground pins are internally connected to the package lead frame to provide a 33389-to-PCB thermal path.                                        |

| 10           | MISO        | Master In/Slave Out        | This pin is the tri-state output from the shift register.                                                                                                  |

| 11           | MOSI        | Master Out/Slave In        | This pin is for the input of serial instruction data.                                                                                                      |

| 12           | SCLK        | System Clock               | This pin clocks the internal shift registers.                                                                                                              |

| 13           | CS          | Chip Select                | This pin communicates with the system MCU and enables SPI communication.                                                                                   |

| 14, 15, 16   | L0: L2      | Wake-up Input<br>(L0: L2)  | Input interfaces to external circuitry. Levels at these pins can be read by SPI and input can be used as programmable wake-up input in Sleep or Stop mode. |

| 17           | NC          | No Connect                 | This pin does not connect.                                                                                                                                 |

| 18           | RTH         | Thermal Resistance<br>High | Pin for the connection of the bus termination to CANH                                                                                                      |

| 19           | CANL        | CAN Low                    | CAN low input/output                                                                                                                                       |

| 24           | CANH        | CAN High                   | CAN high input/output                                                                                                                                      |

| 25           | V2          | Voltage Regulator<br>Two   | This 5.0 V pin is a low drop voltage regulator dedicated to the peripherals supply.                                                                        |

| 26           | RTL         | Thermal Resistance<br>Low  | Pin for the connection of the bus termination to CANL                                                                                                      |

| 27           | VBAT        | Voltage Battery            | This pin is voltage supply from the battery.                                                                                                               |

| 28           | V3          | Voltage Regulator<br>Three | This pin is a 10 $\Omega$ switch to $V_{BAT},$ used to supply external contacts or relays.                                                                 |

## **ELECTRICAL CHARACTERISTICS**

### **MAXIMUM RATINGS**

### Table 3. Maximum Ratings

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                  | Symbol           | Value       | Unit |

|--------------------------------------------------------------------------|------------------|-------------|------|

| ELECTRICAL RATINGS                                                       |                  |             | •    |

| DC Voltage at VBAT Pin                                                   | V <sub>BAT</sub> | -0.3 to 27  | V    |

| Transient Voltage at VBAT Pin                                            | V <sub>BAT</sub> | 40          | V    |

| t < 500 ms (load dump)                                                   |                  |             |      |

| DC Voltage at Pins CANH and CANL                                         | V <sub>BAT</sub> | -20 to 27   | V    |

| Transient Voltage at Pins CANH and CANL                                  | V <sub>BAT</sub> | -40 to 40   | V    |

| 0.0 < V2 < 5.5, V <sub>BAT</sub> > 0.0, t < 500 ms                       |                  |             |      |

| Coupled Transient Voltage at Pins CANH and CANL                          | V <sub>BAT</sub> | -100 to 100 | V    |

| With 100 $\Omega$ Termination Resistors, Coupled Through 1.0 nF $^{(1)}$ |                  |             |      |

| DC Voltage at Pins V1 and V2                                             | V <sub>BAT</sub> | -0.3 to 6.0 | V    |

| DC Current at Output Pins RX, MISO, RST, INT                             | V <sub>BAT</sub> | -20 to 20   | mA   |

| DC Voltage at Input Pins TX, MOSI, CS, RST                               | V <sub>BAT</sub> | -0.3 to 6.0 | V    |

| DC Voltage at Pins L0, L1, L2                                            | V <sub>BAT</sub> | -0.3 to 40  | V    |

| 0.0 < V <sub>BAT</sub> < 40 V                                            |                  |             |      |

| Current at Pins L0, L1, L2                                               | V <sub>BAT</sub> | -15         | mA   |

| Transient Current at Pin V3                                              | V <sub>BAT</sub> | -30 to 20   | mA   |

| DC Voltage at pins RTH and RTL                                           | V <sub>BAT</sub> | -0.3 to 40  | V    |

| ESD Voltage on any Pin (HBM 100 pF, 1.5 K)                               | V <sub>BAT</sub> | -2.0 to 2.0 | kV   |

| ESD Voltage on L0, L1, L2, CANH, CANL, VBAT                              | V <sub>BAT</sub> | -2.0 to 2.0 | kV   |

| ESD Voltage on any Pin (MM 200 pF, 0 $\Omega$ )                          | V <sub>BAT</sub> | -150 to 150 | V    |

| THERMAL RATINGS                                                          | · · ·            |             | •    |

| Operating Junction Temperature                                           | TJ               | -40 to 150  | °C   |

| Ambient Temperature                                                      | T <sub>A</sub>   | -40 to 125  | °C   |

| Storage Temperature                                                      | T <sub>S</sub>   | -55 to 165  | °C   |

|                                                                          |                  |             |      |

Notes

Archived Archived Archiver Archiver Archived NGM Arthon No. 2010 No. 2010

1. Pulses 1, 2, 3a, and 3b according to ISO7637.

## Table 3. Maximum Ratings (continued)

All voltages are with respect to ground unless otherwise noted. Exceeding these ratings may cause a malfunction or permanent damage to the device.

| Ratings                                                                       | Symbol              | Value       | Unit |

|-------------------------------------------------------------------------------|---------------------|-------------|------|

| THERMAL RESISTANCE                                                            |                     |             |      |

| RTH, RTL Termination Resistance                                               | R <sub>RTHRTL</sub> | 500 to 16 k | Ω    |

| Junction to Heatsink Thermal Resistance for HSOP-20                           | R <sub>AJC</sub>    | 3.1         | °C/W |

| 33% Power on V1, 66% on V2 (including CAN) $^{(2)}$                           |                     |             |      |

| Junction to Pin Thermal Resistance for SO-28WD <sup>(3)</sup>                 | R <sub>AS/P</sub>   | 17          | °C/W |

| Thermal Shutdown Temperature                                                  | T <sub>SD</sub>     | 165         | °C   |

| Peak Package Reflow Temperature During Reflow <sup>(4)</sup> , <sup>(5)</sup> | T <sub>PPRT</sub>   | Note 5      | °C   |

Notes

Archived Archived Archiver Archiver Archiver Archived Archived Archived Archiver Arc

- 2. Refer to thermal management in device description section.

- 3. Refer to thermal management in device section. Ground pins 6, 7, 8, 9, 20, 21, 22, and 23 of SO28WB package.

- 4. Pin soldering temperature limit is for 10 seconds maximum duration. Not designed for immersion soldering. Exceeding these limits may cause malfunction or permanent damage to the device.

5. Freescale's Package Reflow capability meets Pb-free requirements for JEDEC standard J-STD-020C. For Peak Package Reflow Temperature and Moisture Sensitivity Levels (MSL),

Go to www.freescale.com, search by part number [e.g. remove prefixes/suffixes and enter the core ID to view all orderable parts. (i.e. MC33xxxD enter 33xxx), and review parametrics.

## STATIC ELECTRICAL CHARACTERISTICS

#### **Table 4. Static Electrical Characteristics**

Characteristics noted under conditions  $V_{BAT}$ , -40°C  $\leq T_A \leq 125$ °C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$ °C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                               | Symbol              | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------|---------------------|-----|-----|-----|------|

| POWER INPUT (VBAT)                                                                                                           | Ι                   |     | 1   | 1   |      |

| Nominal VBAT Operating Range                                                                                                 | V <sub>BAT</sub>    | 5.5 | _   | 18  | V    |

| Functional VBAT Operating Range                                                                                              | V <sub>BAT</sub>    | 5.5 | _   | 27  | V    |

| V <sub>BAT</sub> Threshold for BAT <sub>FAIL</sub> Flag                                                                      | BAT <sub>FAIL</sub> | 2.0 | _   | 4.0 | V    |

| Delay for Signalling BAT <sub>FAIL</sub>                                                                                     | TFAIL               | _   | 150 | 400 | μs   |

| Overvoltage V <sub>BAT</sub> Threshold                                                                                       | BAT <sub>HIGH</sub> | 18  | 20  | 22  | V    |

| Delay for Setting BAT <sub>HIGH</sub> Flag                                                                                   | T <sub>HIGH</sub>   | 4.0 | 18  | 50  | μs   |

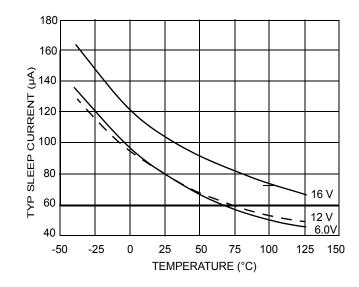

| Supply Current in Sleep Mode<br>Forced Wake-Up and Cyclic Sense Disabled<br>$V_{BAT}$ = 12 V, T <sub>J</sub> = 25°C to 150°C | I <sub>SLEEP1</sub> | _   | 75  | 125 | μA   |

| Supply Current in Sleep Mode<br>Forced Wake-Up and Cyclic Sense Disabled<br>$V_{BAT}$ = 12 V, T <sub>J</sub> = -40°C to 25°C | I <sub>SLEEP2</sub> | _   | -   | 210 | μA   |

| Supply Current in Sleep Mode<br>Forced Wake-Up and Cyclic Sense Enabled<br>$V_{BAT}$ = 12 V, T <sub>J</sub> = 25°C to 150°C  | I <sub>SLEEP3</sub> | _   | 105 | 155 | μA   |

| Supply Current in Sleep Mode<br>Forced Wake-Up and Cyclic Sense Enabled<br>$V_{BAT}$ = 12 V, T <sub>J</sub> = -40°C to 25°C  | I <sub>SLEEP4</sub> | _   | _   | 250 | μA   |

| Supply Current in Sleep Mode<br>Forced Wake-Up and Cyclic Sense Disabled<br>$V_{BAT}$ = 12 V, T <sub>J</sub> = 25°C to 150°C | I <sub>SLEEP5</sub> | _   | _   | 300 | μA   |

| Supply Current in Stand-by Mode                                                                                              | I <sub>STB2</sub>   | —   | 0.5 | 1.0 | mA   |

| Supply Current in Normal Mode<br>Normal Mode with I(V1) = 1 I(V2) = 0<br>Bus in Recessive State                              | INREC               | _   | 3.5 | 7.0 | mA   |

Archived Archived Archiver Archiver Archived NGMANVEDN

| V1 Output Voltage<br>0 mA < $I_{OUT}$ < 100 mA<br>5.5 V < $V_{BAT}$ < 27 V        | V1 <sub>NOM</sub> | 4.85 | 5.0  | 5.15 | V |

|-----------------------------------------------------------------------------------|-------------------|------|------|------|---|

| V1 Output Voltage<br>I <sub>OUT</sub> =< 100 mA<br>27 V < V <sub>BAT</sub> < 40 V | V1                | 4.8  | 5.0  | 5.2  | V |

| V1 Drop Voltage<br>I <sub>OUT</sub> =< 100 mA <sup>(6)</sup>                      | V1DROP            | —    | 0.35 | 0.5  | V |

Notes

6. Measured when V1 has dropped 100mV below its nominal value

Characteristics noted under conditions  $V_{BAT}$ , -40°C  $\leq T_A \leq 125$ °C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$ °C under nominal conditions unless otherwise noted.

| Characteristic                                                                                  |                            | Symbol            | Min             | Тур              | Max             | Unit |

|-------------------------------------------------------------------------------------------------|----------------------------|-------------------|-----------------|------------------|-----------------|------|

| POWER OUTPUT (CONTINUED)                                                                        |                            |                   |                 | 1                |                 |      |

| V1 Output Current Limitation<br>V1 <sub>NOM</sub> - 100 mV                                      |                            | I1MAX             | 130             | 170              | 200             | mA   |

| V1 Overtemperature Shut OFF Threshold<br>Junction Temperature                                   |                            | TV1H              | 160             | _                | 190             | °C   |

| V1 Pre-Warning Temperature Threshold<br>Junction Temperature                                    |                            | TV1L              | 130             | —                | 160             | °C   |

| V1 Temperature Threshold Difference                                                             |                            | TV1H-TV1L         | 20              | —                | 40              | °C   |

| V1 Reset Threshold on V1<br>5.5 V < V <sub>BAT</sub> < 27 V                                     | (C Version)<br>(D Version) | VR1               | 4.1<br>V2 - 0.4 | 4.3<br>V1 - 0.28 | 4.8<br>V1 - 0.1 | V    |

| V1 Reset Active V1 Range                                                                        |                            | V1R               | 1.0             | VR1              | —               | V    |

| V1 Reverse Current from V1 to V <sub>BAT</sub> and GND V1 = 4.9 V, 0 < V <sub>BAT</sub> < 4.9 V |                            | IREV              | _               | —                | 1.0             | mA   |

| V2 Output Voltage<br>0 mA < I <sub>OUT</sub> < 200 mA 5.5 V < V <sub>BAT</sub> < 40 V           |                            | V2NOM             | 4.75            | 5.0              | 5.25            | V    |

| V2 Drop Voltage<br>I <sub>OUT</sub> = 200 mA <sup>(7)</sup>                                     |                            | V2DROP            | —               | 0.2              | 0.5             | V    |

| V2 Drop Voltage<br>I <sub>OUT</sub> = 20 mA <sup>(7)</sup>                                      |                            | V2DROP            | —               | 0.05             | 0.15            | V    |

| V2 Output Current Limitation<br>V2 <sub>NOM</sub> -100 mV                                       |                            | I1 <sub>MAX</sub> | 220             | 280              | 350             | mA   |

| V2 Threshold on V2 to Report V2 OFF<br>V2 Nominal                                               |                            | V <sub>R2</sub>   | 4.1             | 4.55             | 4.75            | V    |

| V <sub>R2</sub> Delay Time                                                                      |                            | V <sub>R2</sub>   | 20              | —                | 70              | μs   |

| V2 Overtemperature Pre-Warning Threshold<br>V2 Junction Temperature                             |                            | T <sub>V2L</sub>  | 130             | —                | 160             | °C   |

| V2 Overtemperature Switch-OFF Threshold<br>V2 Junction Temperature                              |                            | T <sub>V2H</sub>  | 155             | _                | 185             | °C   |

| V2 Line Regulation<br>9.0 V < V <sub>BAT</sub> < 16.5                                           |                            | V2 <sub>LR1</sub> | -15             | —                | +15             | mV   |

| V2 Load Regulation<br>4.0 mA < I <sub>LOAD</sub> < 200 mA                                       |                            | V2 <sub>LR2</sub> | -75             | -                | +75             | mV   |

| V2 Line Ripple Rejection<br>100 Hz, 1.0 V <sub>PP</sub> on V <sub>BAT</sub> <sup>(8)</sup>      |                            | V2 <sub>LRR</sub> | 30              | 55               | _               | dB   |

Notes

Archived Archived Archiver Archiver Archived NGMANAMON

7. Measured when V1 has dropped 100mV below its nominal value

8. Guaranteed by design; however, it is not production tested

Characteristics noted under conditions  $V_{BAT}$ , -40°C  $\leq T_A \leq 125$ °C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$ °C under nominal conditions unless otherwise noted.

| Characteristic                                                                                               | Symbol                               | Min                   | Тур | Мах                   | Unit |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------|-----|-----------------------|------|

| POWER OUTPUT (CONTINUED)                                                                                     |                                      | 11                    |     |                       |      |

| V2 Percentage Difference V2-V1 $V_{BAT} > 9.0, I_{V1} = 20 \text{ mA}, I_{V2} = 40 \text{ mA}$               | V2 <sub>V2-V1</sub>                  | -3.0                  | _   | 3.0                   | %    |

| V3 High Level Voltage Drop $I_{V3}$ = -50 mA, 9.0 V < V <sub>BAT</sub> < 40 V                                | V3 <sub>DROP</sub>                   | —                     | 0.4 | 1.0                   | V    |

| V3 High Level Voltage Drop $I_{V3}$ = -50 mA, 6.0 V < V <sub>BAT</sub> < 9.0 V                               | V3 <sub>DROP</sub>                   | —                     | _   | 1.5                   | V    |

| V3 Leakage Output Limitation<br>5.5 V < V <sub>BAT</sub> < 27 V                                              | I3 <sub>LIM</sub>                    | 100                   | 150 | 250                   | mA   |

| V3 Leakage Current<br>V3 = 0 (V3 OFF)                                                                        | I3 <sub>LEAK</sub>                   | —                     | —   | 15                    | μA   |

| V3 Overtemperature Detection<br>Junction Temperature                                                         | T <sub>V3</sub>                      | 155                   | —   | 185                   | °C   |

| V3 Voltage with -30 mA (negative current for Relay Switch OFF)<br>No Functional Error Allowed for t ≤ 100 ms | V <sub>V3</sub>                      | 0.3                   | —   | 0.5                   | V    |

| CAN Transceiver V2 for Forced Bus Stand-by Mode (Fail Safe)                                                  | VRC2                                 | 3.0                   | 3.9 | 4.7                   | V    |

| CANH/L Differential Receiver, Threshold Voltage                                                              | V <sub>CANTH</sub>                   | -3.2                  | _   | -2.5                  | V    |

| CANH/L Differential Receiver, Dominant to Recessive Threshold<br>(Bus Failures 1, 2, and 5)                  | V <sub>CANDRTH</sub>                 | -3.2                  | _   | -2.5                  | V    |

| CANH Recessive Output Voltage<br>TX = High, R(RTH) < 4.0 k                                                   | V <sub>CANH</sub>                    | —                     |     | 0.2                   | V    |

| CANL Recessive Output Voltage<br>TX = High, R(RTH) < 4.0 k                                                   | V <sub>CANL</sub>                    | V2-0.2                | —   | -                     | V    |

| CANH Output Voltage, Dominant<br>TX = 0 V, BusNormal Mode, I <sub>CANH</sub> = - 40 mA                       | V <sub>CANH</sub>                    | V2-1.4                | _   | -                     | V    |

| CANL Output Voltage, Dominant<br>TX = 0 V, Bus Normal Mode, I <sub>CANL</sub> = - 40 mA                      | V <sub>CANL</sub>                    | —                     | —   | 1.4                   | V    |

| CANH Output Current Limit<br>( $V_{CANH} = 0.0 V, TX = 0$ )                                                  | ICANH                                | 50                    | 75  | 100                   | mA   |

| CANL Output Current Limit<br>(V <sub>CANL</sub> = 14 V, TX = 0)                                              | ICANL                                | 50                    | 95  | 130                   | mA   |

| Detection Threshold for Short Circuit to Battery Voltage<br>Bus Normal Mode                                  | V <sub>CANH</sub> -V <sub>CANL</sub> | 7.3                   | 7.9 | 8.9                   | V    |

| Detection Threshold for Short Circuit to Battery Voltage<br>Bus Stand-by Mode                                | V <sub>CANH</sub>                    | V <sub>BAT</sub> /2+3 | —   | V <sub>BAT</sub> /2+5 | V    |

| CANH Output Current, Failure 3<br>Bus Stand-by Mode V <sub>CANH</sub> = 12 V                                 | I <sub>CANHF3</sub>                  | —                     | 5.0 | 10                    | μA   |

| CANL Output Current, Failure 4<br>Bus Stand-by Mode, V <sub>CANL</sub> = 0.0 V, V <sub>BAT</sub> = 12 V      | ICANLF4                              | -                     | 0.0 | 2.0                   | μA   |

Archived Archived Archiver Archiver Archived NGMANAMON

Characteristics noted under conditions  $V_{BAT}$ , -40°C  $\leq T_A \leq 125$ °C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$ °C under nominal conditions unless otherwise noted.

| Characteristic                                       | Symbol                                     | Min    | Тур  | Max        | Unit |

|------------------------------------------------------|--------------------------------------------|--------|------|------------|------|

| POWER OUTPUT (CONTINUED)                             | I                                          |        |      |            |      |

| CANL Wake-Up Voltage Threshold                       | V <sub>WAKEL</sub>                         | 2.5    | 3.3  | 3.9        | V    |

| Bus Stand-by Mode                                    |                                            |        |      |            |      |

| CANH Wake-Up Voltage Threshold                       | V <sub>WAKEH</sub>                         | 1.2    | 2.0  | 2.7        | V    |

| Bus Stand-by Mode                                    |                                            |        |      |            |      |

| Wake-Up Threshold Difference                         | V <sub>WAKEL</sub> -<br>V <sub>WAKEH</sub> | 0.2    | —    | _          | V    |

| CANH Single Ended Receiver Threshold                 | V <sub>CANH</sub>                          | 1.5    | 1.85 | 2.15       | V    |

| Failures 4, 6, and 7                                 |                                            |        |      |            |      |

| CANL Single Ended Receiver Threshold                 | V <sub>CANL</sub>                          | 2.8    | 3.05 | 3.4        | V    |

| Failures 3 and 8                                     |                                            |        |      |            |      |

| CANL Pull-Up Current                                 | I <sub>CANLPU</sub>                        | 45     | 75   | 90         | μA   |

| Bus Normal Mode                                      |                                            |        |      |            |      |

| CANH Pull Down Current                               | I <sub>CANLPD</sub>                        | 45     | 75   | 90         | μA   |

| Bus Normal Mode                                      |                                            |        |      |            |      |

| Receiver Differential Input Impedance CANH/CANL      | R <sub>DIFF</sub>                          | 100    | _    | 180        | kΩ   |

| Differential Receiver Common Mode Voltage Range      | V <sub>COM</sub>                           | -8.0   | _    | 8.0        | V    |

| RTL to V2 Switch on Resistance                       | R <sub>RTL</sub>                           | 10     | 25   | 70         | Ω    |

| I <sub>OUT</sub> < -10 mA, Bus Normal Operating Mode |                                            |        |      |            |      |

| RTL to Battery Switch Series Resistance              | R <sub>RTL</sub>                           | 8.0    | 12.5 | 20         | kΩ   |

| Bus Stand-by Mode                                    |                                            |        | -    |            |      |

| RTH to Ground Switch on Resistance                   | R <sub>RTH</sub>                           | _      | 25   | 70         | Ω    |

| I <sub>OUT</sub> < 10 mA, All Modes                  |                                            |        |      |            |      |

| CONTROL INTERFACE                                    |                                            |        | I    |            |      |

| High Level Input Voltage                             | V <sub>IH</sub>                            | 0.7 V1 | _    | V1 + 0.3 V | V    |

| CS Threshold for SPI Wake-Up                         | V <sub>CSTH</sub>                          | _      | 2.2  | _          | V    |

| SBC in Sleep Mode, V1 < 1.5 V                        | 00111                                      |        |      |            |      |

| CS Filter Time for SPI Wake-Up                       | t <sub>CSFT</sub>                          | _      | _    | 3.0        | μs   |

| SBC in Sleep Mode, V1 < 1.0 V                        |                                            |        |      |            |      |

| Low Level Input Voltage                              | V <sub>IL</sub>                            | -0.3   |      | 0.3 V1     | V    |

| High Level Input Current on CS                       | I <sub>CSH</sub>                           | -100   | _    | -20        | μA   |

| V <sub>1</sub> = 4.0 V                               | CON                                        |        |      |            |      |

| Low Level Input Current on CS                        | I <sub>CSL</sub>                           | -100   |      | -20        | μA   |

| V <sub>I</sub> = 1.0 V                               | -CSL                                       |        |      |            | •    |

| TX High Level Input Current                          | I <sub>TXH</sub>                           | -200   | -80  | -25        | μA   |

| $V_1 = 4.0 V$                                        | 'IXH                                       |        |      | 20         | Pr   |

| TX Low Level Input Current                           |                                            | -800   | -320 | -100       | μA   |

| $V_{\rm I} = 1.0 V$                                  | ITXL                                       | -000   | -320 | -100       | μ~   |

| -                                                    |                                            | 40     |      |            |      |

| SI, SCLK Input Current<br>0 < V <sub>IN</sub> < V1   | I <sub>SISLK</sub>                         | -10    | —    | +10        | μA   |

Characteristics noted under conditions  $V_{BAT}$ , -40°C  $\leq T_A \leq 125$ °C unless otherwise noted. Typical values noted reflect the approximate parameter means at  $T_A = 25$ °C under nominal conditions unless otherwise noted.

| Characteristic                                                                         | Symbol             | Min      | Тур  | Max        | Unit |

|----------------------------------------------------------------------------------------|--------------------|----------|------|------------|------|

| CONTROL INTERFACE (CONTINUED)                                                          |                    |          | 1    |            |      |

| RX, $\overline{INT}$ , MISO High Level Output Voltage<br>I <sub>0</sub> = -250 $\mu$ A | V <sub>OH</sub>    | V1 - 0.9 | _    | V1         | V    |

| RX, INT, MISO Low Level Output Voltage<br>I <sub>0</sub> = -1.5 mA                     | V <sub>OL</sub>    | 0.0      | _    | 0.9        | V    |

| RX, INT, MISO Tri-Stated SO Output Current<br>0 V < V <sub>SO</sub> < V1               | Ι <sub>Ζ</sub>     | -2.0     | _    | +2.0       | μA   |

| RST High Level Input Voltage                                                           | V <sub>IH</sub>    | 0.7 V1   | —    | V1 + 0.3 V | _    |

| RST Low Level Input Voltage                                                            | V <sub>IL</sub>    | -0.3     | _    | -0.3 V1    | V    |

| RST High Level Output Current 1<br>0.0 < V <sub>OUT</sub> < 0.5 V1                     | I <sub>RSTH1</sub> | -50      | -30  | -10        | μA   |

| RST High Level Output Current 2<br>0.5 < V <sub>OUT</sub> < V1                         | I <sub>RSTH2</sub> | -        | -300 | -          | μA   |

| RSTLow Level Output Voltage (I0 = 1.5 mA)1.0 V < VBAT < 27 V                           | V <sub>RST</sub>   | 0.0      | _    | 0.9        | V    |

| LX/Wake-Up Positive Switching Threshold<br>6.0 V <v<sub>BAT &lt; 16 V</v<sub>          | V <sub>WUP</sub>   | 3.0      | 3.7  | 4.5        | V    |

| LX/Wake-Up Negative Switching Threshold<br>6.0 V <v<sub>BAT &lt; 16 V</v<sub>          | V <sub>WUN</sub>   | 2.5      | 3.0  | 3.8        | V    |

| LX/Wake-Up Hysteresis<br>6.0 V <v<sub>BAT &lt; 16 V</v<sub>                            | V <sub>HYS</sub>   | -        | 700  | -          | mA   |

| LX/Wake-Up Leakage Current 0 < V <sub>WU</sub> < V <sub>BAT</sub>                      | I <sub>LXWU</sub>  | -5.0     | _    | +5.0       | μA   |

| LX Input Current at 40 V                                                               | V <sub>IN</sub>    | —        | 350  | 600        | μA   |

Archived Archived Archiver Archiver Archived NGMANAPON

RCHIVE

NFORMATION

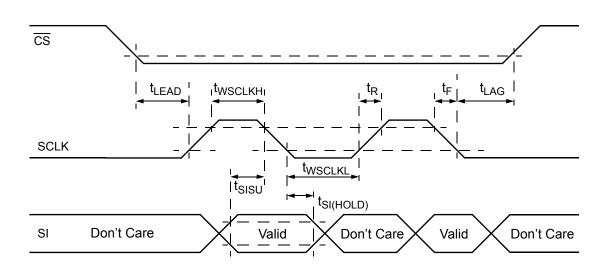

## **DYNAMIC ELECTRICAL CHARACTERISTICS**

#### Table 5. Dynamic Electrical Characteristics

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                             | Symbol                | Min  | Тур | Max  | Unit |

|--------------------------------------------------------------------------------------------|-----------------------|------|-----|------|------|

| MICROCONTROLLER INTERFACE                                                                  | •                     | L    |     |      | L    |

| AC CANL/CANH Slew Rates, Rising or Falling Edges, TX from Recessive to Dominant State      | t <sub>CANRD</sub>    | 3.5  | 5.0 | 10   | V/µs |

| $C_{LOAD}$ - 10 nF, 133 $\Omega$ Termination Resistors                                     |                       |      |     |      |      |

| AC CANL/CANH Slew Rates, Rising or Falling Edges, TX from Dominant to Recessive State      | t <sub>CANDR</sub>    | 2.0  | 3.5 | 10   | V/µs |

| $C_{LOAD}$ - 10 nF, 133 $\Omega$ Termination Resistors                                     |                       |      |     |      |      |

| AC Propagation Delay TX to RX Low                                                          | t <sub>DH</sub>       | _    | 1.2 | 2.0  | μs   |

| $C_{LOAD}$ - 10 nF, 133 $\Omega$ Termination Resistors                                     |                       |      |     |      |      |

| AC Propagation Delay TX to RX High                                                         | t <sub>DL</sub>       | —    | 2.0 | 3.0  | μs   |

| $C_{LOAD}$ - 10 nF, 133 $\Omega$ Termination Resistors                                     |                       |      |     |      |      |

| Wake-Up Filter Time                                                                        | t <sub>WUFT</sub>     | 8.0  | 20  | 38   | μs   |

| RST Duration after V1 High                                                                 | t <sub>RES</sub>      | _    | 1.0 | —    | ms   |

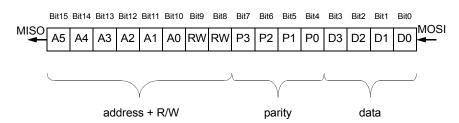

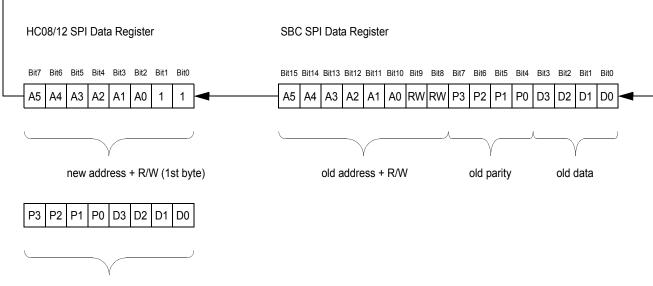

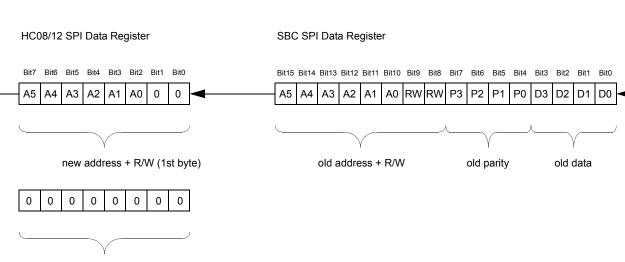

| SCLK Clock Period                                                                          | t <sub>PSCLK</sub>    | 500  | —   | —    | ns   |

| SCLK Clock High Time                                                                       | twsclkh               | 175  | —   | —    | ns   |

| SCLK Clock Low Time                                                                        | twsclkl               | 175  | —   | —    | ns   |

| Falling Edge of CS to Rising Edge of SCLK                                                  | t <sub>LEAD</sub>     | 250  | 50  | _    | ns   |

| Falling Edge of SCLK to Rising Edge of $\overline{CS}$                                     | t <sub>LEAD</sub>     | 250  | 50  | _    | ns   |

| SI to Falling Edge of SCLK                                                                 | t <sub>SISU</sub>     | 125  | 25  | —    | ns   |

| Falling Edge of SCLK to SI                                                                 | t <sub>SI(HOLD)</sub> | 125  | 25  | —    | ns   |

| SO Rise Time (C <sub>L</sub> = 200 pF)                                                     | t <sub>RSO</sub>      | _    | 25  | 75   | ns   |

| SO Fall Time (C <sub>L</sub> = 200 pF)                                                     | t <sub>FSO</sub>      | —    | 25  | 75   | ns   |

| SI, CS, SCLK Incoming Signal Rise Time                                                     | t <sub>RSI</sub>      | —    | —   | 200  | ns   |

| SI, CS, SCLK Incoming Signal Fall Time                                                     | t <sub>FSI</sub>      | —    | —   | 200  | —    |

| Time from Falling Edge of CS to SO                                                         |                       | _    | _   |      | ns   |

| Low Impedance                                                                              | t <sub>SO(EN)</sub>   |      |     | 200  |      |

| High Impedance                                                                             | t <sub>SO(DIS)</sub>  |      |     | 200  |      |

| Time from Rising Edge of SCLK to SO Data Valid                                             | t <sub>VALID</sub>    | —    | 50  | 125  | —    |

| 0.2 V1 or V2 $\leq$ SO $\geq$ 0.8 V1 or V2, C <sub>L</sub> = 200 pF                        |                       |      |     |      |      |

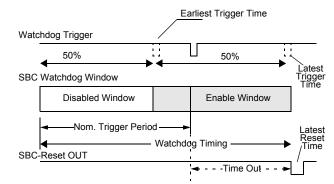

| Running Mode Oscillator Tolerance (Normal Request, Normal and Stand-by Modes $^{\rm (9)})$ | RMOT                  | -12  | —   | +12  | %    |

| Software Watchdog Timing 1 <sup>(9)</sup>                                                  | t <sub>SW1</sub>      | 4.4  | 5.0 | 5.6  | ms   |

| Software Watchdog Timing 2 <sup>(9)</sup>                                                  | t <sub>SW2</sub>      | 8.8  | 10  | 11.2 | ms   |

| Software Watchdog Timing 3 <sup>(9)</sup>                                                  | t <sub>SW3</sub>      | 17.6 | 20  | 22.4 | ms   |

| Software Watchdog Timing 4 <sup>(9)</sup>                                                  | t <sub>SW4</sub>      | 28   | 32  | 36   | ms   |

9. Software watchdog timing accuracy is based on the running mode oscillator tolerance

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                         | Symbol            | Min  | Тур  | Max   | Unit |

|--------------------------------------------------------|-------------------|------|------|-------|------|

| MICROCONTROLLER INTERFACE (CONTINUED)                  |                   | 1    | 1    | 1     | 1    |

| Software Watchdog Timing 5 <sup>(10)</sup>             | t <sub>SW5</sub>  | 44.8 | 51   | 58    | ms   |

| Software Watchdog Timing 6 <sup>(10)</sup>             | t <sub>SW6</sub>  | 65   | 74   | 83    | ms   |

| Software Watchdog Timing 7 <sup>(10)</sup>             | t <sub>SW7</sub>  | 88   | 100  | 112   | ms   |

| Software Watchdog Timing 8 <sup>(10)</sup> .           | t <sub>SW8</sub>  | 167  | 190  | 213   | ms   |

| Sleep Mode Oscillator Tolerance (10)                   | SMOT              | -30  | —    | +30   | %    |

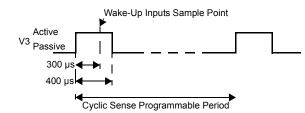

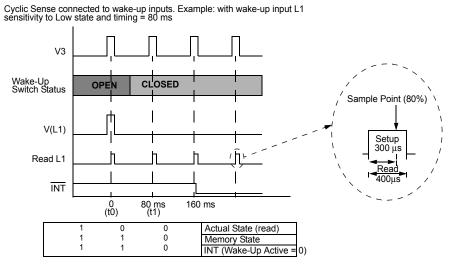

| Cyclic Sense/FWU Timing 1 Sleep Mode (10)              | t <sub>CY1</sub>  | 22.4 | 32   | 46.6  | ms   |

| Cyclic Sense/FWU Timing 2 Sleep Mode (10)              | t <sub>CY2</sub>  | 44.8 | 64   | 83.2  | ms   |

| Cyclic Sense/FWU Timing 3 Sleep Mode (10)              | t <sub>CY3</sub>  | 89.6 | 128  | 166.4 | ms   |

| Cyclic Sense/FWU Timing 4 Sleep Mode (10)              | t <sub>CY4</sub>  | 179  | 256  | 333   | ms   |

| Cyclic Sense/FWU Timing 5 Sleep Mode (10)              | t <sub>CY5</sub>  | 358  | 512  | 665   | ms   |

| Cyclic Sense/FWU Timing 6 Sleep Mode <sup>(10)</sup> . | t <sub>CY6</sub>  | 717  | 1024 | 1331  | ms   |

| Cyclic Sense/FWU Timing 7 Sleep Mode (10)              | t <sub>CY7</sub>  | 1434 | 2048 | 2662  | ms   |

| Cyclic Sense/FWU Timing 8 Sleep Mode (10)              | t <sub>CY8</sub>  | 5734 | 8192 | 10650 | ms   |

| Ground Shift Threshold 1 (11)                          | GS1               | -1.0 | -0.7 | -0.3  | V    |

| CAN Transceiver Active in Two Wire Operation           |                   |      |      |       |      |

| Ground Shift Threshold 2 <sup>(11)</sup>               | GS2               | -1.5 | -1.2 | -0.8  | V    |

| CAN Transceiver Active in Two Wire Operation           |                   |      |      |       |      |

| Ground Shift Threshold 3 (11)                          | GS3               | -2.0 | -1.7 | -1.3  | V    |

| CAN Transceiver Active in Two Wire Operation           |                   |      |      |       |      |

| Ground Shift Threshold 4 (11)                          | GS4               | -2.6 | -2.2 | -1.7  | V    |

| CAN Transceiver Active in Two Wire Operation           |                   |      |      |       |      |

| BUS TRANSMITTER                                        |                   | L    |      |       | L    |

| AC Minimum Dominant Time for Wake-Up on CANL or CANH   | t <sub>WAKE</sub> | 4.0  | _    | 40    | μs   |

| Bus Stand-by Mode, V <sub>BAT</sub> = 12 V             |                   |      |      |       |      |

| AC Failure 3 Detection Time                            | t <sub>AC3D</sub> | 10   | —    | 60    | μs   |

| Bus Normal Mode                                        |                   |      |      |       |      |

| BUS TRANSMITTER                                      |                     |      |   |      |    |

|------------------------------------------------------|---------------------|------|---|------|----|

| AC Minimum Dominant Time for Wake-Up on CANL or CANH | t <sub>WAKE</sub>   | 4.0  | — | 40   | μs |

| Bus Stand-by Mode, V <sub>BAT</sub> = 12 V           |                     |      |   |      |    |

| AC Failure 3 Detection Time                          | t <sub>AC3D</sub>   | 10   | — | 60   | μs |

| Bus Normal Mode                                      |                     |      |   |      |    |

| AC Failure 3 Recovery Time                           | t <sub>AC3R</sub>   | 10   | — | 60   | μs |

| Bus Normal Mode                                      |                     |      |   |      |    |

| AC Failure 6 Detection Time                          | t <sub>AC6D</sub>   | 50   | — | 400  | μs |

| Bus Normal Mode                                      |                     |      |   |      |    |

| AC Failure 6 Recovery Time                           | t <sub>AC6R</sub>   | 150  | — | 1000 | μs |

| Bus Normal Mode                                      |                     |      |   |      |    |

| AC Failure 4, 7, and 8 Detection Time                | t <sub>AC478D</sub> | 0.75 | — | 4.0  | ms |

| Bus Normal Mode                                      |                     |      |   |      |    |

Notes

10. Cyclic sense and forced wake-up timing accuracy are based on the Sleep mode oscillator tolerance.

11. No overlap between two adjacent thresholds.

RCHIVE

NFORMATION

## Table 5. Dynamic Electrical Characteristics (continued)

Characteristics noted under conditions 7.0 V  $\leq$  V<sub>SUP</sub>  $\leq$  18 V, -40°C  $\leq$  T<sub>A</sub>  $\leq$  125°C, GND = 0 V unless otherwise noted. Typical values noted reflect the approximate parameter means at T<sub>A</sub> = 25°C under nominal conditions unless otherwise noted.

| Characteristic                                                                                                                 | Symbol              | Min  | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-----|-----|------|

| BUS TRANSMITTER (CONTINUED)                                                                                                    |                     |      |     |     |      |

| AC Failure 4, 7, and 8 Recovery Time<br>Bus Normal Mode                                                                        | t <sub>AC478R</sub> | 10   | —   | 60  | μs   |

| AC Failure 3, 4, and 7 Detection Time<br>Bus Stand-by Mode, V <sub>BAT</sub> = 12 V                                            | t <sub>AC347D</sub> | 0.8  | _   | 8.0 | ms   |

| AC Failure 3, 4 and 7 Recovery Time<br>Bus Stand-by Mode, V <sub>BAT</sub> = 12 V                                              | t <sub>AC347R</sub> | _    | 2.5 | _   | ms   |

| AC Edge Count Difference Between CANH/CANL for Failures 1, 2, 5 Detection<br>Bus Normal Mode                                   | CAN <sub>125D</sub> | _    | 3.0 | —   | _    |

| AC Edge Count Difference Between CANH/CANL for Failures 1, 2, 5 Recovery<br>Bus Normal Mode                                    | CAN <sub>125R</sub> | _    | 3.0 | _   | _    |

| TX Permanent Dominant Timer Disable Time<br>Bus Normal and Failure Modes                                                       | t <sub>TXD</sub>    | 0.75 | —   | 4.0 | ms   |

| POWER INPUT TIMING                                                                                                             |                     |      |     |     |      |

| V1 Reset Delay Time                                                                                                            | t <sub>D</sub>      | 2.0  | _   | 20  | μs   |

| V1 Line Regulation<br>9.0 V < V <sub>BAT</sub> < 16.5, I <sub>LOAD</sub> = 10 mA                                               | t <sub>D</sub>      | -15  | 2.0 | +15 | mV   |

| V1 Line Regulation 5.5 V < $V_{BAT}$ < 27 V I <sub>LOAD</sub> = 10 mA                                                          | t <sub>D</sub>      | -50  | 10  | +50 | mV   |

| V1 Load Regulation<br>1.0 mA < I <sub>LOAD</sub> < 100 mA                                                                      | t <sub>D</sub>      | -50  | —   | +50 | mV   |

| V1 Line Ripple Rejection<br>100 Hz, 1.0 V <sub>PP</sub> on V <sub>BAT</sub> = 12 V, $I_{LOAD}$ = 100 mA (12)                   | t <sub>D</sub>      | 30   | 55  | -   | dB   |

| V1 Line Transient Response $V_{BAT}$ from 12 V to 40 V in 1.0 µs, (10 µF, ESR = 3 $\Omega$ )                                   | t <sub>D</sub>      | —    | 27  | -   | mV   |

| V1 Load Transient Response $I_{LOAD}$ from 10 µA to 100 mA in 1.0 µs (CLOAD = 10 µF, ESR = 3 $\Omega$ ) (13)                   | t <sub>D</sub>      | _    | 400 | —   | mV   |

| V1 Load Transient Response I <sub>LOAD</sub> from 10 $\mu$ A to 100 mA in 1.0 $\mu$ s (CLOAD = 10 $\mu$ F, ESR= 0.1 $\Omega$ ) | t <sub>D</sub>      | —    | 16  | —   | mV   |

Notes 12.

13.

Guaranteed by design. Not production tested. This condition does not produce a reset

## TIMING DIAGRAMS

Figure 4. Input Timing Switch Characteristics

Archived Archived Archiver Archiver Archived NGMINEORMAN

RCHIVE

INFORMATION

## FUNCTIONAL DESCRIPTION

## INTRODUCTION

The System Basis Chip (SBC) is an integrated circuit dedicated to car body applications. It includes three main blocks:

- 1. A dual voltage regulator

- 2. Reset, watchdog, wake-up inputs, cyclic wake-up

## TRANSMIT AND RECEIVE DATA (TX AND RX)

The RX and TX pins (receive data and transmit data pins, respectively) are connected to a microcontroller's CAN protocol handler. TX is an input and controls the CANH and CANL line state (dominant when TX is LOW, recessive when TX is HIGH). RX is an output and reports the bus state.

# VOLTAGE REGULATOR ONE AND TWO (V1 AND V2)

The V1 pin is a 3% low drop voltage regulator dedicated to the microcontroller supply (nominal 5V supply).

The V2 pin is a low drop voltage regulator dedicated to the peripherals supply (nominal 5V supply).

## RESET (RST)

The  $\overline{\text{RST}}$  (reset) pin is an input/output pin. The typical reset duration from SBC to microcontroller is 1ms. If longer times are required, an external capacitor can be used. SBC provides two RST output pull-up currents. A typical 30µA pull up when Vreset is below 2.5V and a 300uA pull up when reset voltage is higher than 2.5V. RST is also an input for the SBC. It means the MC33389 is forced to Normal Request mode after  $\overline{\text{RST}}$  is released by the microcontroller

## INTERRUPT (INT)

The Interrupt pin INT is an output that is set LOW when an interrupt occurs. INT is enabled using the Interrupt Register (INTR). When an interrupt occurs, INT stays LOW until the interrupt source is cleared.

INT output also reports a wake-up event.

## **GROUND (GND)**

This pin is the ground of the integrated circuit.

## MASTER IN/ SLAVE OUT (MISO)

MISO is the Master In Slave Out pin of the serial peripheral interface. Data is sent from the SBC to the microcontroller through the MISO pin.

3. CAN low speed fault tolerant physical interface

#### Supplies

Two low drop regulators and one switch to  $V_{BAT}$  are provided to supply the **ECU** microcontroller or peripherals, with independent control and monitoring through SPI.

## FUNCTIONAL PIN DESCRIPTION

### MASTER OUT/ SLAVE IN (MOSI)

MOSI is the Master Out Slave In pin of the serial peripheral interface. Control data from a microcontroller is received through this pin.

## SYSTEM CLOCK (SCLK)

This pin clocks the internal shift registers for SPI communication.

## CHIP SELECT (CS)

$\overline{\text{CS}}$  is the Chip Select pin of the serial peripheral interface (SPI). When this pin is LOW, the SPI port of the device is selected.

## LEVEL 0-2 INPUTS (L0: L2)

The L0: L2 pins can be connected to contact switches or the output of other ICs for external inputs. The input states can be read by the SPI. These inputs can be used as wakeup events for the SBC.

## NO CONNECT (NC)

No pin connection.

## TERMINATION RESISTANCE (HIGH AND LOW?) (RTH AND RTL)

External CAN bus high and low termination resistance pins are connected to these pins.

## CAN HIGH AND CAN LOW OUTPUTS (CANH AND CANL)

The CAN High and CAN Low pins are the interfaces to the CAN bus lines. They are controlled by TX input level, and the state of CANH and CANL is reported through RX output.

## **VOLTAGE BATTERY (VBAT)**

This pin is the voltage supply from the battery.

## **VOLTAGE REGULATOR THREE (V3)**

This pin is a 10  $\Omega$  switch to VBAT, which is used to supply external contacts or relays.

## FUNCTIONAL DEVICE OPERATION

#### Voltage Regulator V1

V1 is a 5.0 V, three percent low drop voltage regulator dedicated to the microcontroller supply. It can deliver up to 100 mA. It is totally protected against short-to-ground (current limitation) and over temperature. V1 is active in Normal Request, Normal, and Stand-by modes.

No forward parasitic diode exists from V1 to  $V_{BAT}$ . This means if V<sub>BAT</sub> voltage drops below V1, high current flowing from V1 to V<sub>BAT</sub> will not discharge the capacitor connected to V1. Its stored energy will only be used to supply the microcontroller and gives time to save all relevant data.

- Under Voltage Reset—V1 is monitored for under voltage (power-up, power down) and a reset is provided at RST output for 1 ms. This ensures proper initialization of the microcontroller at power-on or after supply is lost. Furthermore, a flag is set in the Reset Source Register (RSR) and can be read via the SPI.

- Over Temperature Protection-V1 internal ballast transistor is monitored for over temperature. Two detection thresholds are provided. A pre-warning threshold at 145°C and a shut-off threshold at 175°C. Once the first threshold is reached, a flag is set in the Over Temperature Status Register (OTSR). A maskable interrupt can be sent to the microcontroller. Once the second threshold is reached, a flag is set in the OTSR, a maskable interrupt is sent to the microcontroller and V1 is switched OFF.

Once the junction temperature is back to the pre-warning threshold, V1 regulator will be automatically switched ON.

#### Table 6. V1 Control

Archived Archived Archiver RIGHIVENIN FORMAN ON

| Conditions for V1 ON                          | Conditions for V1 OFF                            |

|-----------------------------------------------|--------------------------------------------------|

| Normal Request Mode<br>(at V1 Power ON)       | Sleep Mode (via SPI)                             |

| Normal Mode (via SPI)                         | Shut-Off Temperature Threshold<br>Reached        |

| Stand-by Mode (via SPI)                       | No V <sub>BAT</sub> Power Supply<br>(cold start) |

| V1 Below Pre-Warning<br>Temperature Threshold | Emergency Mode                                   |

| During Rest                                   | —                                                |

Note: Current capability of V1, V2 and V3 depends upon the thermal management. Over temperature shutdown might be reached and lead to turn OFF of V1, V2, and V3 for output current below their maximum current capability.

#### Voltage Regulator V2

V2 is a 5.0 V low drop voltage regulator dedicated to peripherals supply. It can deliver up to 200 mA and is protected against short to ground (current limitation) and over temperature. V2 is active in Normal mode.

- Under Voltage Detection—V2 is monitored for under voltage and a flag is set in the Voltage Supply Status Register (VSSR).

- Over Temperature Protection—V2 internal ballast transistor is monitored for overtemperature. Two detection thresholds are provided. A pre-warning threshold at 140°C and a shut-off threshold at 165°C. Once the first threshold is reached, a flag is set in the readable OTSR register. A maskable interrupt can be sent to microcontroller.

Once the second threshold is reached, a flag is set in the OTSR register, V2 is switched OFF. It can only be switched on again via the SPI.

#### Table 7. V2 Control

| Conditions for V2 ON                                                    | Conditions for V2 OFF                                               |

|-------------------------------------------------------------------------|---------------------------------------------------------------------|

| Normal Mode (via SPI) and V2<br>Below Shut-Off Temperature<br>Threshold | Sleep, Stand-by, Normal<br>Request, or Emergency Modes<br>(via SPI) |

| _                                                                       | Shut-Off Temperature Threshold<br>Reached                           |

| -                                                                       | V1 Disabled (for any reason)                                        |

#### Switch V3

V3 is a 10  $\Omega$  switch to V<sub>BAT</sub>. It can be used to supply external contacts or relays. A great flexibility is given for the different possible ways for its control. It is protected against short to ground (current limitation).

Over Temperature Protection—V3 output transistor is monitored for over temperature. Once the threshold is reached, a flag is set in the VSSR register, V3 is switched OFF. It will be automatically switched ON once the junction temperature is back to the pre-warning threshold.

#### Table 8. V3 Control

| Conditions For V3 ON                                                  | Conditions For V3 OFF                         |

|-----------------------------------------------------------------------|-----------------------------------------------|

| Permanently in Normal Mode<br>if Configured via SPI                   | Permanently in Normal<br>Mode if Configured   |

| Permanently in Stand-by<br>Mode if Configured via SPI                 | Normal Request Mode                           |

| In Sleep Mode, During<br>Enable Time of Cyclic<br>Sense if Configured | Permanently in Stand-by<br>Mode if Configured |

| _                                                                     | Permanently in Sleep<br>Mode if Configured    |

### Table 8. V3 Control

|   | In Sleep Mode, During        |

|---|------------------------------|

| — | Disable Time of Cyclic       |

|   | Sense if Configured          |

| — | Over Temp Threshold Reached  |

| _ | V1 Disabled (for any reason) |

| — | V2 Over Temperature Shutdown |

|   |                              |

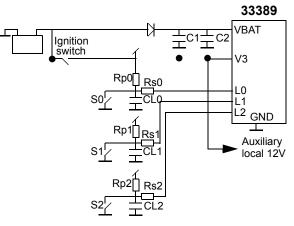

#### Supply and VBAT Block

- V<sub>BAT</sub> Monitoring—V<sub>BAT</sub> is the main power supply coming from the battery voltage after an external protection diode (for reverse battery). V<sub>BAT</sub> is monitored for under voltage and over voltage.

- V<sub>BAT</sub> Under Voltage—V<sub>BAT</sub> is monitored for under voltage if it is below 4.0 V the BatFail flag is set in the VSSR register and a maskable interrupt is sent to the microcontroller.

- V<sub>BAT</sub> Over Voltage— When V<sub>BAT</sub> is > 20 V, the BatHigh flag is set in the VSSR register. A maskable interrupt is sent to the microcontroller. No specific action is taken to reduce current consumption (to limit power dissipation). This is to allow the entire flexibility to the microcontroller for a decision.

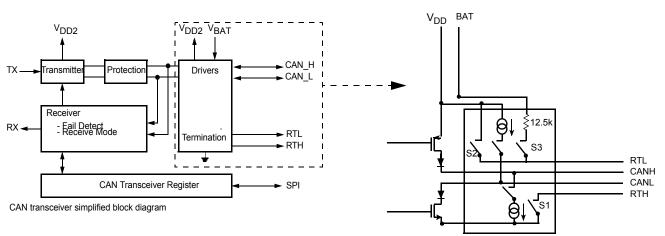

#### **CAN Transceiver**

Archived ArchivARGHIVEnINFORMATVIO

Archived

The device incorporates a low speed 125 kBaud CAN physical interface. Its electrical parameters for the CANL,

CANH, RTL,RTH, RX, and TX pins are identical to the 33388, stand alone CAN physical interface.

The mode control for the CAN transceiver (Normal,  $V_{BAT}$  Stand-by, Sleep, etc.) are selectable through the 33389 SPI interface.

- · Baud Rate up to 125 kBit/s

- · Supports unshielded bus wires

- Short-circuit proof to battery and ground in 12 V powered systems

- Supports single-wire transmission modes with ground offset voltages up to 1.5 V

- Automatic switching to single wire mode in case of bus failures

- Automatic reset to differential mode if bus failure is removed

- Low Electromagnetic Interference (EMI) due to built-in slope control and signal symmetry

- · Fully integrated receiver filters

- · Thermally protected

- Bus lines protected against automotive transients

- Low current Bus Stand-by mode with wake-up capability via the bus

- · An unpowered node does not disturb the bus lines

#### **CONSEQUENCE OF FAILURE DETECTIONS**

- S1 is the switch from RTH to Ground

- S2 is the switch from RTL to V2 and

- S3 is the switch from RTL to  $\mathrm{V}_{\mathrm{BAT}}$

- Each failure type provides data concerning which switch is open and which driver is disabled.

- Failure 1: Nothing done

- Failure 2: Nothing done

- Failure3: S1 open. Driver CANH is disabled

Failure4: S2 and S3 open. Driver CANL is disabled Failure5: Nothing done

Failure6: S2 and S3 open. Driver CANL disabled Failure7: S2 and S3 open. Driver CANL disabled

Failure8: S1 Open. CANH driver disable

#### **CAN Transceiver Description**

The CAN transceiver is an interface between CAN protocol controller and the physical bus. It is intended for low

speed applications up to 125 kBit/s in passenger cars. It provides differential transmission capability, but will switch in error condition to single wire transmitter and/or receiver.

The rise and fall slopes are limited to reduce radio frequency interference (RFI). This provides use of an unshielded twisted pair or a parallel pair of wires for the bus. It supports transmission capability on either bus wire if one of the bus wire is corrupted. The logic failure detection automatically selects a suitable transmission mode.

In a normal operation (no wiring failures), the differential bus state is the output to RX. The differential receiver inputs are connected to CANH and CANL through integrated filters. The filtered inputs signals are also used for the single wire receivers. The CANH and CANL receivers have threshold voltages, assuring maximum noise margin in single wire modes. In the RX Only mode, the transmitter is disabled; however, the receive part of the transceiver remains active. In this mode, RX reports bus and TX activity (RX = TX or Bus dominant). Failure detection and management is the same as the Bus Normal mode.

#### **Failure Detector**

Archived Archived Archiver RGMIVEnIN FORMAND

The failure detector is active in RXTX and RX Only operation modes. The detector recognizes the following single bus failures and switches to an appropriate mode.

- 1. CANH wire interrupted

- 2. CANL wire interrupted or shorted to 5.0 V

- 3. CANH short-circuit to battery

- 4. CANL short-circuit to ground

- 5. CANH short-circuit to ground

- 6. CANL short-circuit to battery

- 7. CANL mutually shorted to CANH

- 8. CANH to V2 (5.0 V)

Note: Shorts-circuit failures are detected for 0 to 50  $\Omega$  shorts.

The differential receiver (CANH-CANL) threshold is set at -2.8 V, this assures a proper reception in the normal operating modes. In case of failures 1, 2, and 5 the on-going message is not destroyed due to noise margin.

Failures 3 and 6 are detected by comparators respectively connected to CANH and CANL. If the comparator threshold is exceeded for a <u>certain</u> time ( $T_{AC3D}$ ,  $T_{AC6D}$ ), the reception is switched to single wire mode. This time is required to avoid false triggering by external RF fields. Recovery from these failures is detected automatically after a <u>certain</u> ( $T_{AC3R}$ ,  $T_{AC6R}$ ) time-out (filtering).

Failures 4 and 7 initially result in a permanent dominant level at RX. After a time-out, the CANL driver and the RTL pins are switched OFF. Only a weak pull-up at CANL remains. Reception continues by switching to Single Wire mode through CANH. When Failures 4 or 7 are removed, the recessive bus levels are restored. If the differential voltage remains below the recessive threshold for a <u>certain</u> (**T**<sub>AC478R</sub>) time, reception and transmission switch back to the Differential mode.

If any of the eight wiring failure occurs, a flag is set in the TESRH and TESRL Status registers. Eight different types of errors are distinguished out of these eight errors. They are separately stored in these register. Please refer to the <u>Tables 35</u> and <u>36</u>. A maskable interrupt is sent to the microcontroller. On error recovery, the corresponding flag is reset after read-out operation.

During all single wire transmissions, the EMC performance (both immunity and emission) is worse than in the Differential mode. Integrated receiver filters suppress any high frequency noise induced into the bus wires. The cut-off frequency of these filters is a compromise between propagation delay and high frequency suppression. In the Single Wire mode, low frequency noise can not be distinguished from the expected signal.

In the event of a permanent dominant TX state (for more than 2.0 ms) the output drivers are disabled. That assures the operation of the complete system in case of a permanent dominant TX state of one control unit. The CAN interface of a defective ECU, which has TX permanently low, will automatically be set to the receive only mode and therefore will not lock the complete CAN bus.

#### Protection

A current limiting circuit protects the transmitter output stages against short-circuit to positive and negative battery voltage. If the junction temperature exceeds a maximum value, the transmitter output stages are disabled. Because the transmitter is responsible for a part of the power dissipation, this results in a reduced power dissipation resulting in a lower chip temperature. All other parts of the transceiver will remain operating. The CANH and CANL inputs are protected against electrical transients, and may occur in an automotive environment.

#### **Thermal Management**

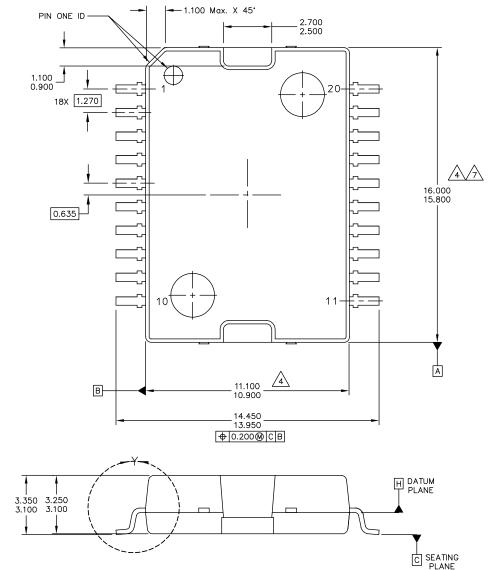

The 33389 is proposed in two different packages:

- 1. HSOP-20 for high power applications

- 2. SO28WB with eight pins to the lead frame for medium power applications

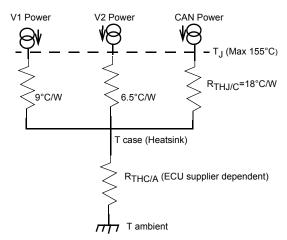

#### HSOP20 Package

For such a package, the heat flow is mainly vertical and each heat source (dissipating element) can be seen as an independent thermal resistance to the Heatsink. The thermal network can be roughly depicted in Figure 6.

Figure 6. HSOP-20 Simplified Thermal Model

#### Example

Assuming  $I_{V1}$  = 100 mA at  $V_{BAT}$  = 16 V,  $I_{V2}$  =150 mA at  $V_{BAT}$  = 16 V (Excluding CAN consumption).

$I_{CAN} = 50 \text{ mA at } V_{BAT} = 16 \text{ V}, \text{ we have:}$  $P_{V1} = 1.1 \text{ W}, P_{V2} = 1.65 \text{ W}, P_{CAN} = 0.55 \text{ W}$

System assumptions:

If  $T_{AMB}$ = 85°C and  $R_{THC/A}$  = 18°C/W, this gives:  $T_{CASE}$  =  $T_{AMB}$ + $R_{THC/A}$  x 3.3 W = 85 + 18 x 3.3 = 145°C and  $T_JV1$  =  $T_JV2$  =  $T_{JCAN}$ =155°C.

This example represents the limit for the maximum power dissipation with a HSOP20.

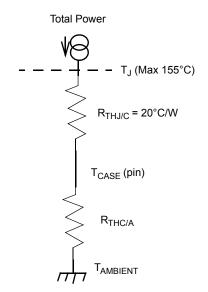

#### SO28WB Package

The case (pin) to junction  $R_{TH}$  is represented here by only one thermal resistance for the total power because the three power sources strongly interact on the silicon for such a package.

## Figure 7. SO28WB Simplified Thermal Model Example

Assuming  $I_{V1} = 45$  mA at  $V_{BAT} = 16$  V,  $I_{V2} = 45$  mA at  $V_{BAT} = 16$  V (Excluding CAN consumption).  $I_{CAN} = 50$  mA at  $V_{PAT} = 16$  V, we have:

$I_{CAN} = 50 \text{ mA at } V_{BAT} = 16 \text{ V}$ , we have:  $P_{V1} = 0.5 \text{ W}$ ,  $P_{V2} = 0.5 \text{ W}$ ,  $P_{CAN} = 0.55 \text{ W}$  thus  $P_{TOTAL} = 1.55 \text{W}$

System assumptions:

If  $T_{AMB}$  = 85°C and  $R_{THC/A}$  = 25°C/W, this gives:  $T_{CASE} = T_{AMB} + R_{THC/A} \times 1.55 W = 85+25 \times 1.55 = 124°C$ and  $T_JV1 = 124 + 20 \times 1.55 = 155°C$ .

#### DIFFERENT DEVICE VERSIONS

The MC33389 is proposed in several package versions, and also offers slight differences in term of functionalities. The device version is identified in the device part number by the first letter after the 389 number. The package identification is done by the last two letters of the part number (DW for SO28 wide body, DH for power SO20).

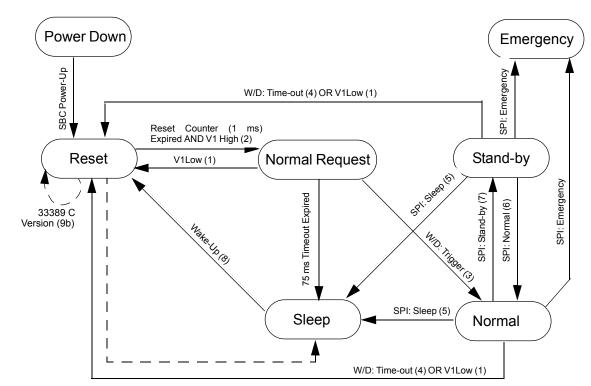

## **OPERATIONAL MODES**

#### **CAN Transceiver Modes**

The CAN transceiver has its own functioning modes: RXTX mode, Term  $V_{BAT}$ /Term  $V_{CC}$  mode, and RX Only mode. They are controlled by the Transceiver Control/Status Register (TCR).

• RXTX mode—Full transmitting and receiving capabilities are enabled. Full failure detection is enabled.

Note: Standard/RXTX and Extended/RXTX are equivalent.

• RX Only mode—The transmitter is disabled but the receive portion of the transceiver remains active. In this mode, RX reports bus and TX activity ( $\overline{RX} = \overline{TX}$  or Bus dominant).

Note: Standard/RX Only and Extended/RX Only are equivalent.

Bus Stand-by mode—Is the Low Power mode for the CAN transceiver. The driver and receivers are disabled. Wake-up capability on both bus lines as well as Failure 3, 4, 7, and 8 detection are enabled. RTL termination is set to V<sub>BAT</sub> in the Bus Stand-by mode.

#### Low Power Modes

The transceiver provides a Low Power mode, entered and exited by a SPI command. This is the Bus Stand-by mode having the lowest power consumption for the transceiver. CANL is biased to the battery voltage via the RTL output and the pull-up current source on CANL and pull down current source on CANH are disabled. Wake-up requests are recognized by the transceiver when a dominant state is detected on either bus wake-up lines. On a Bus wake-up request, the SBC will activate the INT output or, if it is in the Sleep mode, switch to the Normal Request mode. This event is stored in the Wake-Up Input Status Register (WUISR).

To prevent a false wake-up resulting from transients or (RF) fields, wake-up threshold levels have to be maintained for a certain time. While in the Transceiver Low Power mode, failure detection circuit remains partly active preventing increased power consumption in cases of error 3, 4, 7, and 8.

#### Power-On

After the VBAT supply is switched ON, the SBC is in Normal Request mode. Bus Stand-by is the corresponding mode for the CAN transceiver.

The CAN transceiver is supplied by V2. As long as V2 is below its under voltage threshold, the transceiver is forced to Bus Stand-by mode (fail safe property).

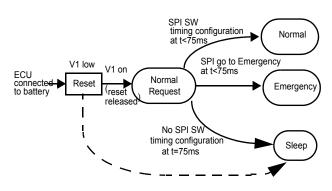

#### SBC MODES

#### **Global Power Save Concept**

The SBC minimizes power consumption of the ECU. Several operating modes are available to go to low power