Communication Solutions

Edition 2006-03-24

Published by Infineon Technologies AG 81726 München, Germany © Infineon Technologies AG 2006. All Rights Reserved.

#### **Legal Disclaimer**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie"). With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office (www.infineon.com).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# ADM6996M/MX, 6 Port 10/100 Mbit/s Single Chip Ethernet Switch Controller (ADM6996MX - Green Package Version)

Revision History: 2006-03-24, Revision 1.4

| Previous Ve                                                                     | Previous Version: Rev. 1.23                                                            |  |  |  |  |  |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|--|

| Page/Date                                                                       | Subjects (major changes since last revision)                                           |  |  |  |  |  |

| Page 15 Rev. 1.2: Modify analog pins number (RXP4-0, RXN4-0, TXP4-0 and TXN4-0) |                                                                                        |  |  |  |  |  |

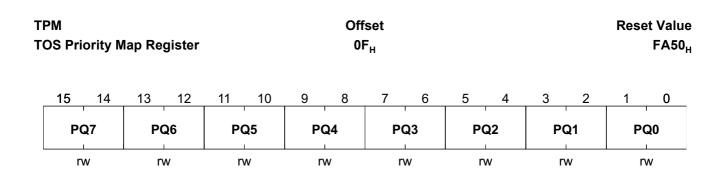

| Page 81-82                                                                      | Rev. 1.21: Rearrange 0E <sub>H</sub> and 0F <sub>H</sub> registers map                 |  |  |  |  |  |

| Page 22                                                                         | Rev. 1.22: Modify LNKFP5 pin description/1 <sub>B</sub> , Link Failed                  |  |  |  |  |  |

| 2005-07-04                                                                      | Changed to the new Infineon format                                                     |  |  |  |  |  |

| 2005-07-04                                                                      | Rev. 1.22 changed to Rev. 1.23                                                         |  |  |  |  |  |

| 2005-08-23                                                                      | Rev 1.3: Update in content                                                             |  |  |  |  |  |

| 2005-11-01                                                                      | Revision 1.3 changed to Revision 1.31 Minor change. Included Green package information |  |  |  |  |  |

| 2006-03-04                                                                      |                                                                                        |  |  |  |  |  |

#### **Trademarks**

ABM®, ACE®, AOP®, ARCOFI®, ASM®, ASP®, DigiTape®, DuSLIC®, EPIC®, ELIC®, FALC®, GEMINAX®, IDEC®, INCA®, IOM®, IPAT®-2, ISAC®, ITAC®, IWE®, IWORX®, MUSAC®, MuSLIC®, OCTAT®, OptiPort®, POTSWIRE®, QUAT®, QuadFALC®, SCOUT®, SICAT®, SICOFI®, SIDEC®, SLICOFI®, SMINT®, SOCRATES®, VINETIC®, 10BaseV®, 10BaseVX® are registered trademarks of Infineon Technologies AG. 10BaseS™, EasyPort™, VDSLite™ are trademarks of Infineon Technologies AG. Microsoft® is a registered trademark of Microsoft Corporation, Linux® of Linus Torvalds, Visio® of Visio Corporation, and FrameMaker® of Adobe Systems Incorporated.

### **Table of Contents**

### **Table of Contents**

|                            | Table of Contents                                                   | 4    |

|----------------------------|---------------------------------------------------------------------|------|

|                            | List of Figures                                                     | 7    |

|                            | List of Tables                                                      | 8    |

| I                          | Product Overview                                                    | . 10 |

| 1.1                        | Samurai-6M/6MX (ADM6996M/MX) Overview                               |      |

|                            | Features                                                            |      |

|                            | Applications                                                        |      |

| 1.4                        | Block Diagram                                                       | . 12 |

| 1.5                        | Data Lengths                                                        | . 12 |

| 2                          | Interface Description                                               | . 13 |

|                            | Pin Diagram                                                         |      |

|                            | Abbreviations                                                       |      |

|                            | Pin Description by Function                                         |      |

|                            | Function Description                                                |      |

|                            | Switch Functional Description                                       |      |

| 3.1.1                      | Basic Operation                                                     |      |

| 3.1.2                      | Buffers and Queues                                                  |      |

| 3.1.3                      | Full Duplex Flow Control                                            |      |

| 3.1.4                      | Half Duplex Flow Control                                            |      |

| 3.1.5                      | Back-Off Algorithm                                                  |      |

| 3.1.6                      | Inter-Packet Gap (IPG)                                              |      |

| 3.1.7                      | Trunking Function                                                   |      |

| 3.1.8                      | Illegal Frames                                                      |      |

| 3.1.9                      | Broadcast Storm                                                     | . 30 |

| 3.1.10                     | Bandwidth Control                                                   | . 31 |

| 3.1.11                     | Smart Discard                                                       | . 31 |

| 3.1.12                     | LED Display                                                         | . 32 |

| 3.1.12.1                   | Single Color LED Display                                            | . 32 |

| 3.1.12.2                   | Dual Color LED Display                                              | . 34 |

| 3.1.12.3                   | Circuit for Single LED Mode                                         |      |

| 3.1.12.4                   | Circuit for Dual LED Mode                                           |      |

| 3.1.13                     | Packet Identification                                               |      |

| 3.1.13.1                   | Span Packet                                                         |      |

| 3.1.13.2                   | Management Packet                                                   |      |

| 3.1.13.3                   | Cross_VLAN Packet                                                   |      |

| 3.1.14                     | Tagged VLAN or Port VLAN                                            |      |

| 3.1.14.1                   | VLAN Filters                                                        |      |

| 3.1.14.2                   | Port VLAN                                                           |      |

| 3.1.14.3                   | Tagged VLAN                                                         |      |

| 3.1.14.4                   | VID for Comparison and Carried through Samurai-6M/6MX (ADM6996M/MX) |      |

| 3.1.14.5                   | Admit Only VLAN-Tagged Packets                                      |      |

| 3.1.14.6                   | VID Check                                                           |      |

| 3.1.14.7                   | FID and VLAN Boundary                                               |      |

| 3.1.14.8<br>3.1.14.9       | Ingress Filter                                                      |      |

| 3.1.14.9<br>3.1.14.10      | VLAN Violation                                                      |      |

| 3. 1. 14. 10<br>3.1.14.11  | ·                                                                   |      |

| ,, i, i <del>4</del> , i i | ragged Member Camed through Camural-0101/0101A (ADMO330101/101A)    | . 40 |

### **Table of Contents**

| 3.1.14.12              |                                                          |    |

|------------------------|----------------------------------------------------------|----|

| 3.1.14.13              | <b>0</b>                                                 |    |

| 3.1.14.14              | ,                                                        |    |

| 3.1.14.15              | <b>-9</b>                                                |    |

| 3.1.15                 | Priority Queue                                           |    |

| 3.1.15.1<br>3.1.15.2   | System PRI                                               |    |

| 3.1.15.2<br>3.1.15.3   | Queue Assigned     Configure Samurai QoS Function        |    |

| 3.1.13.3<br>3.1.16     | Address Learning                                         |    |

| 3.1.16<br>3.1.16.1     | Dynamic Learning                                         |    |

| 3.1.16.2               | Manual Learning                                          |    |

| 3.1.16.3               | Learning Table                                           |    |

| 3.1.16.3. <sup>2</sup> | · ·                                                      |    |

| 3.1.16.3.2             | •                                                        |    |

| 3.1.16.3.3             |                                                          |    |

| 3.1.16.3.4             | •                                                        |    |

| 3.1.17                 | Hardware Based IGMP Snooping                             |    |

| 3.1.17.1               | Entry Format of IGMP Membership Table                    |    |

| 3.1.17.2               | The Registers Accessing the IGMP Membership Table        | 52 |

| 3.1.17.3               | IGMP Snooping Introduction                               | 53 |

| 3.1.18                 | Address Aging                                            | 56 |

| 3.1.19                 | Source Violation                                         | 56 |

| 3.1.20                 | Packet Forwarding                                        |    |

| 3.1.20.1               | Control Table                                            |    |

| 3.1.20.2               | Default Output Ports                                     |    |

| 3.1.20.3               | Forwarding Algorithm                                     |    |

| 3.1.21                 | Special TAG                                              |    |

| 3.1.21.1               | Special Tag for the Receive                              |    |

| 3.1.21.2               | Special Tag for the Transmit                             |    |

| 3.2<br>3.3             | 10/100M PHY Block                                        |    |

| 3.3.1                  | Auto Negotiation                                         |    |

| 3.3.2                  | Speed/Duplex Configuration                               |    |

| _                      | Hardware, EEPROM and SMI Interface for Configuration     |    |

| 3.4.1                  | Hardware Setting                                         |    |

| 3.4.2                  | EEPROM Interface                                         |    |

| 3.4.3                  | SMI Interface                                            |    |

| 3.5                    | The Hardware Difference between ADM6996M/MX and ADM6996F | 79 |

| 1                      | Registers Description                                    | 80 |

|                        | EEPROM Basic Registers                                   |    |

|                        | EEPROM Extended Registers                                |    |

|                        | Counter and Switch Status Registers                      |    |

|                        | PHY Registers                                            |    |

|                        | Electrical Specification                                 |    |

| <b>)</b><br>5.1        | TX/FX Interface                                          |    |

| 5.1.1                  | TP Interface                                             |    |

| 5.1.2                  | FX Interface                                             |    |

|                        | DC Characterization                                      |    |

|                        | AC Characterization                                      |    |

| 5.3.1                  | XTAL/OSC Timing                                          |    |

|                        |                                                          | 1  |

### **Table of Contents**

| 100Base-TX MII Output Timing       2         RMII REFCLK Input Timing       2         RMII REFCLK Output Timing       2         Reduce MII Timing       2         GPSI (7-wire) Input Timing       2         GPSI (7-wire) Output Timing       2         SDC/SDIO Timing       2         MDC/MDIO Timing       2         Package Outlines       2         Package Information       2 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RMII REFCLK Input Timing 2 RMII REFCLK Output Timing 2 Reduce MII Timing 2 GPSI (7-wire) Input Timing 2 GPSI (7-wire) Output Timing 2 SDC/SDIO Timing 2 MDC/MDIO Timing 2 2                                                                                                                                                                                                           |

| RMII REFCLK Input Timing                                                                                                                                                                                                                                                                                                                                                              |

| RMII REFCLK Input Timing 2 RMII REFCLK Output Timing 2 Reduce MII Timing 2 GPSI (7-wire) Input Timing 2 GPSI (7-wire) Output Timing 2                                                                                                                                                                                                                                                 |

| RMII REFCLK Input Timing                                                                                                                                                                                                                                                                                                                                                              |

| RMII REFCLK Input Timing                                                                                                                                                                                                                                                                                                                                                              |

| RMII REFCLK Input Timing                                                                                                                                                                                                                                                                                                                                                              |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                 |

| 100Base-TX MII Output Timing                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                       |

| 100Base-TX MII Input Timing                                                                                                                                                                                                                                                                                                                                                           |

| 10Base-TX MII Output Timing                                                                                                                                                                                                                                                                                                                                                           |

| 10Base-TX MII Input Timing                                                                                                                                                                                                                                                                                                                                                            |

|                                                                                                                                                                                                                                                                                                                                                                                       |

| EEPROM Interface Timing                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                       |

### **List of Figures**

## **List of Figures**

| Figure 1  | Samurai-6M/6MX (ADM6996M/MX) Block Diagram                                    | 12  |

|-----------|-------------------------------------------------------------------------------|-----|

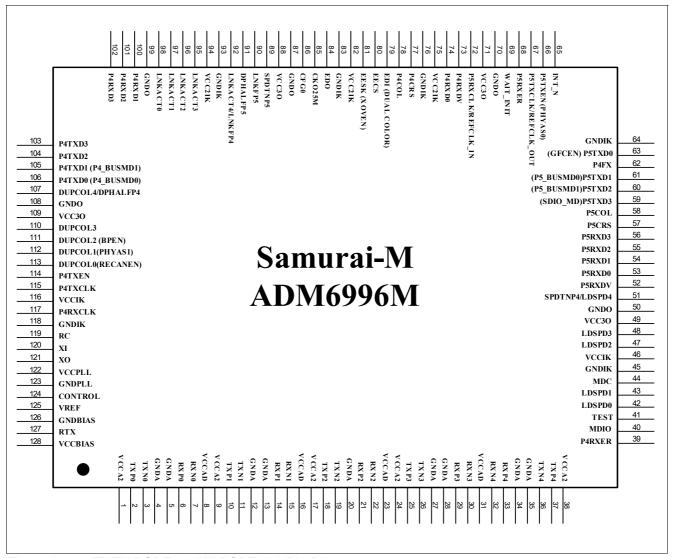

| Figure 2  | 4 TP/FX PORT + 2 MII PORT 128 Pin Diagram                                     | 13  |

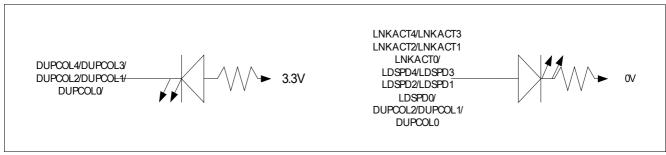

| Figure 3  | Circuit for Single Color LED Mode                                             | 34  |

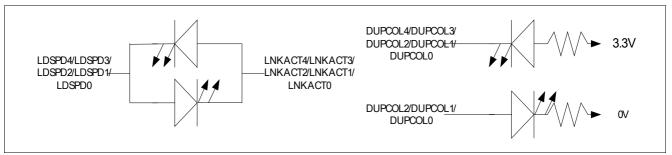

| Figure 4  | Circuit for Dual Color LED Mode                                               | 35  |

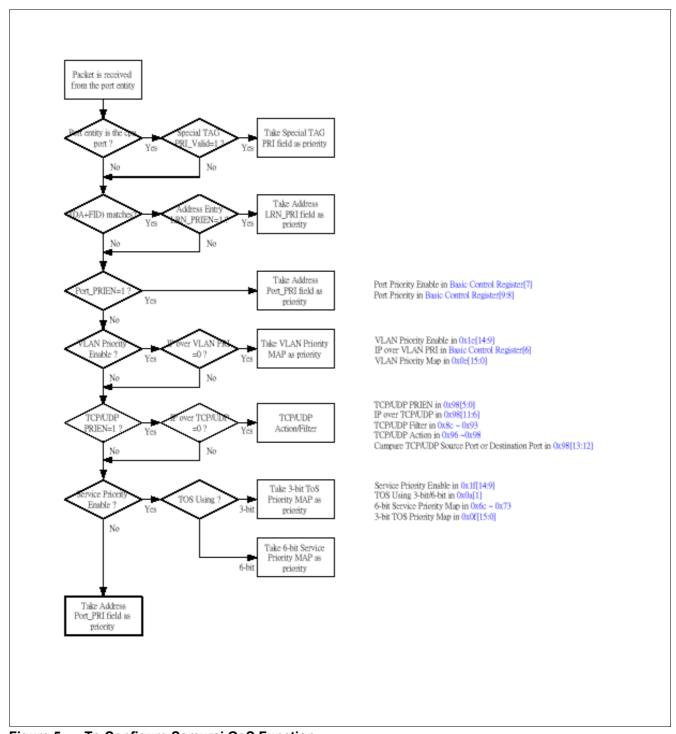

| Figure 5  | To Configure Samurai QoS Function                                             | 46  |

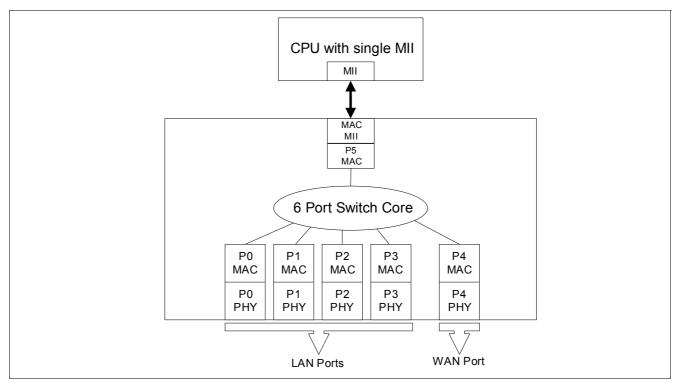

| Figure 6  | ADM6996M/MX to CPU with single MII Connection                                 | 64  |

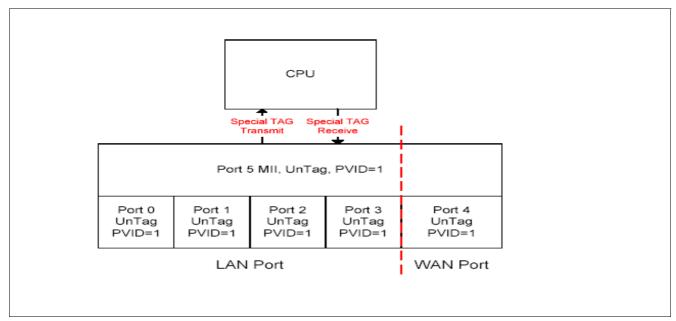

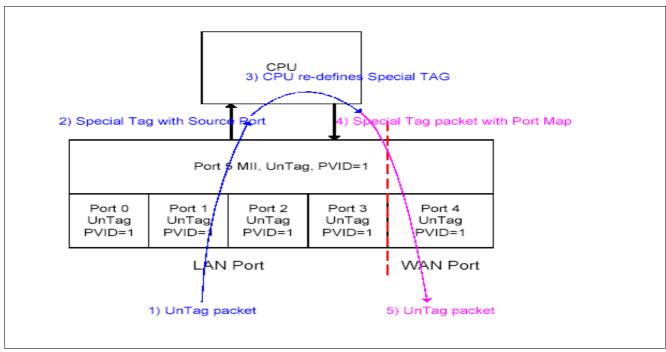

| Figure 7  | The configurations of the implementation by ADM6996M/MX Special TAG functions | 65  |

| Figure 8  | Software Operation                                                            |     |

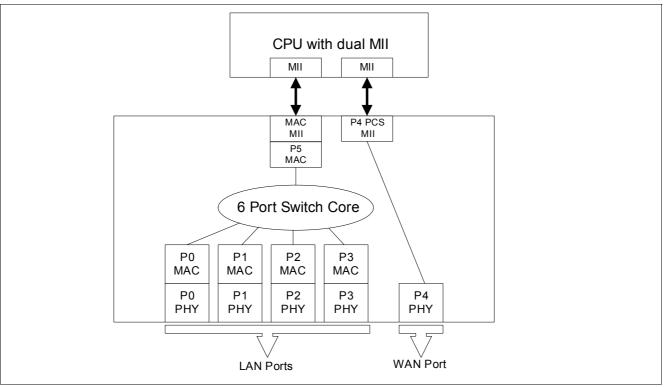

| Figure 9  | ADM6996M/MX to CPU with dual MII Connection                                   | 68  |

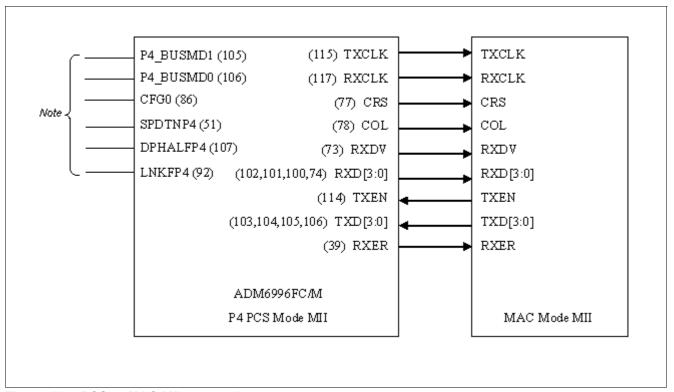

| Figure 10 | 100M Full duplex MAC to MAC MII Connection                                    | 69  |

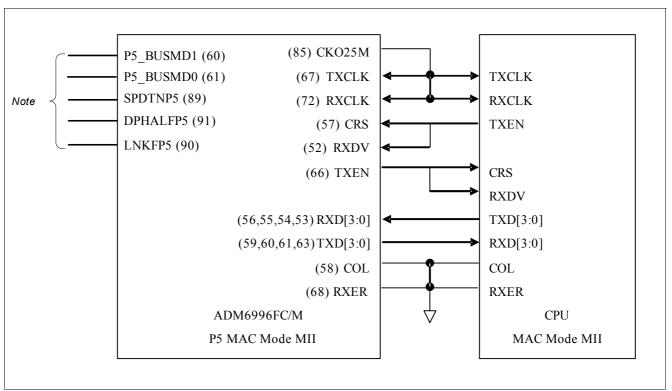

| Figure 11 | PCS to MAC MII connection                                                     | 70  |

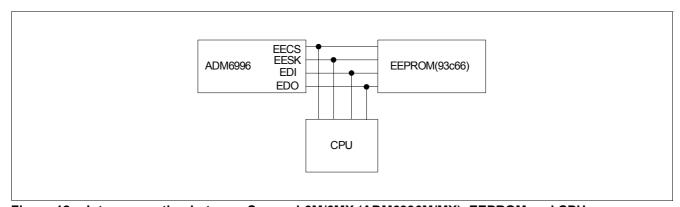

| Figure 12 | Interconnection between Samurai-6M/6MX (ADM6996M/MX), EEPROM and CPU          | 72  |

| Figure 13 | The Power-On-Sequence of Samurai                                              | 75  |

| Figure 14 | Timing Diagram of RC, EECS and EESK (with correct signature EEPROM)           | 76  |

| Figure 15 | Timing Diagram of RC, EECS and EESK (without EEPROM)                          | 77  |

| Figure 16 | SMI Interface                                                                 | 78  |

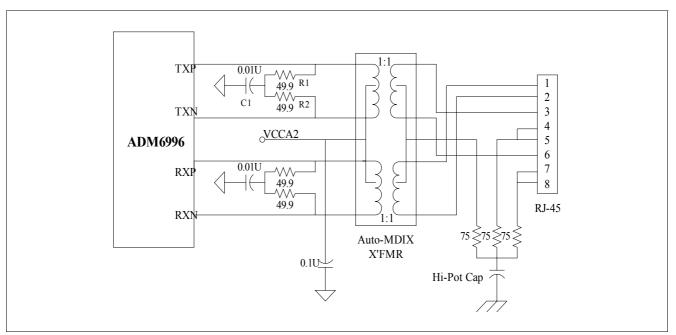

| Figure 17 | TP Interface                                                                  | 198 |

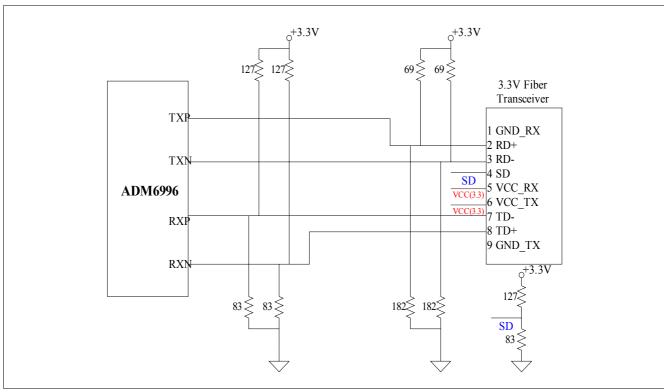

| Figure 18 | FX Interface                                                                  | 199 |

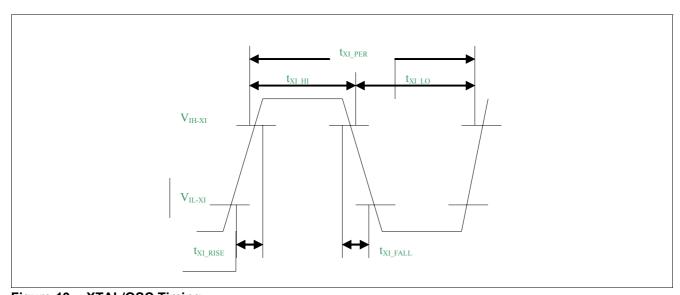

| Figure 19 | XTAL/OSC Timing                                                               | 201 |

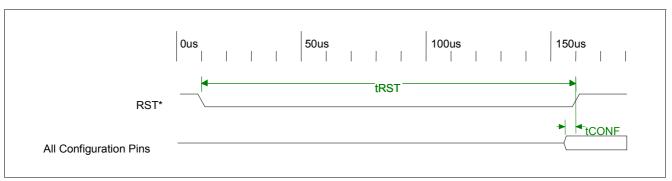

| Figure 20 | Power On Reset Timing                                                         | 202 |

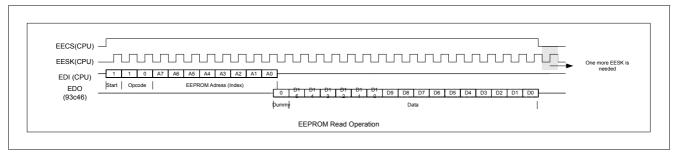

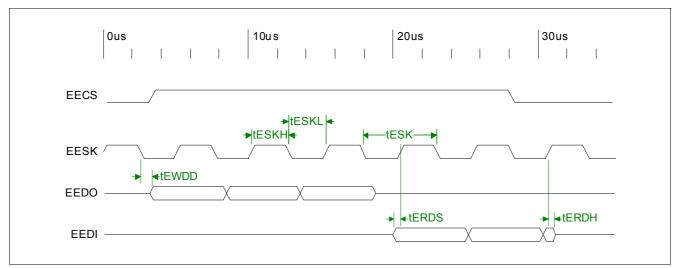

| Figure 21 | EEPROM Interface Timing                                                       | 203 |

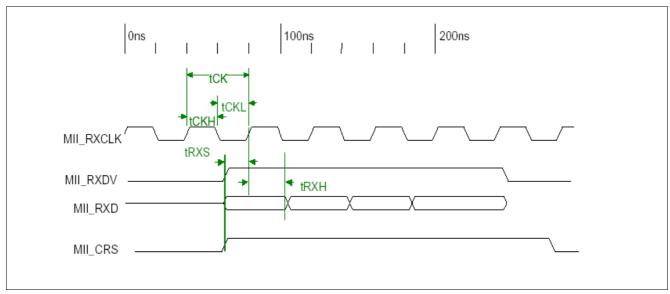

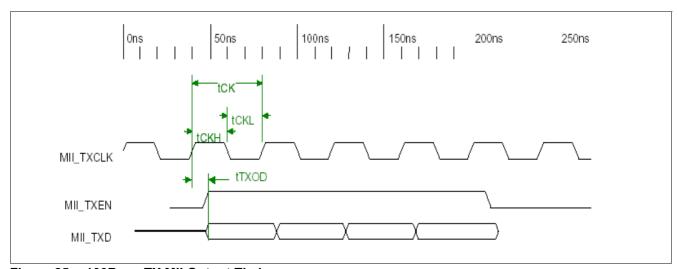

| Figure 22 | 10Base-TX MII Input Timing                                                    | 204 |

| Figure 23 | 10Base-TX MII Output Timing                                                   | 205 |

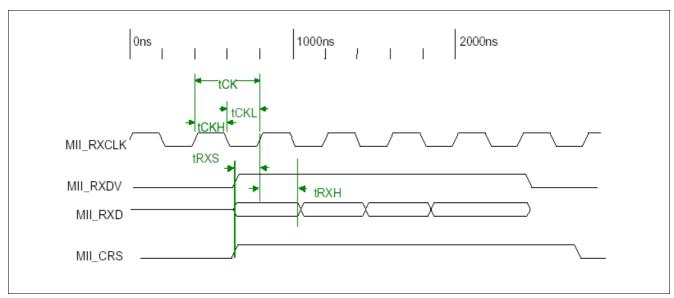

| Figure 24 | 100Base-TX MII Input Timing                                                   | 206 |

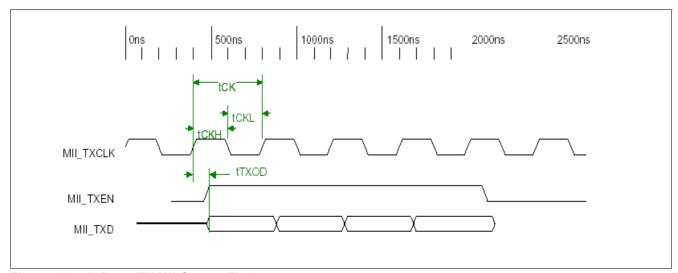

| Figure 25 | 100Base-TX MII Output Timing                                                  | 207 |

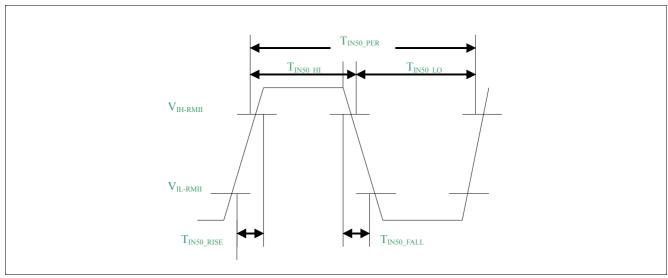

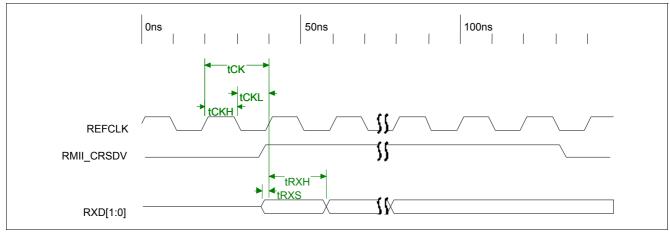

| Figure 26 | RMII REFCLK Input Timing                                                      | 207 |

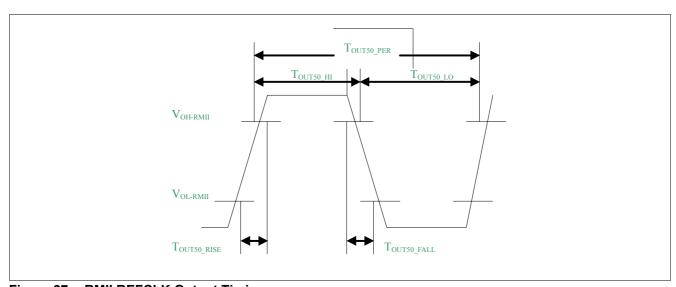

| Figure 27 | RMII REFCLK Output Timing                                                     | 208 |

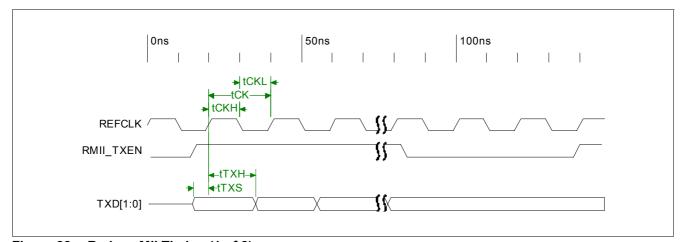

| Figure 28 | Reduce MII Timing (1 of 2)                                                    | 209 |

| Figure 29 | Reduce MII Timing (2 of 2)                                                    | 209 |

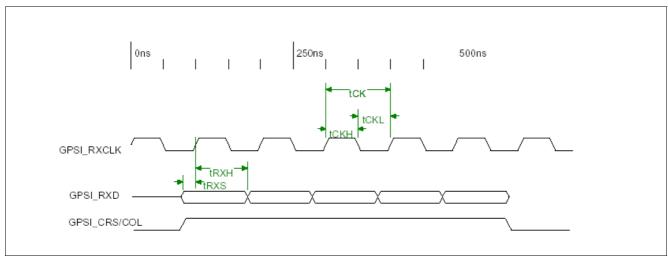

| Figure 30 | GPSI (7-wire) Input Timing                                                    | 210 |

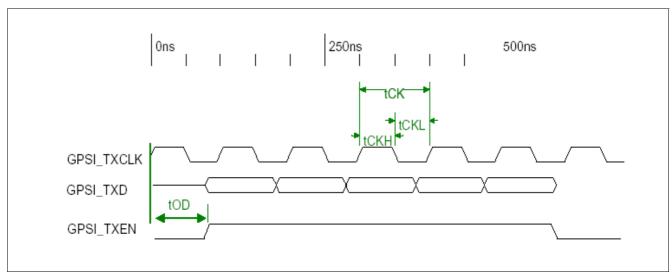

| Figure 31 | GPSI (7-wire) Output Timing                                                   | 211 |

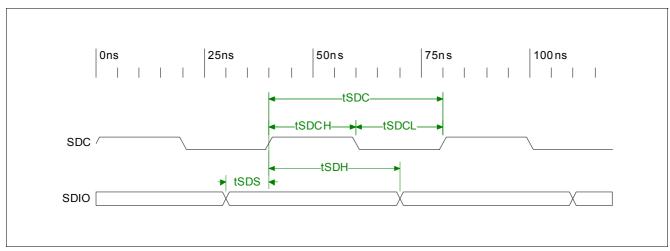

| Figure 32 | SDC/SDIO Timing                                                               | 211 |

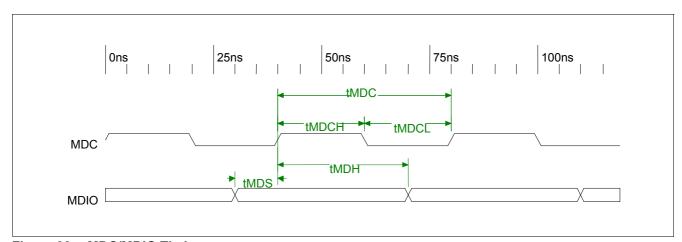

| Figure 33 | MDC/MDIO Timing                                                               | 212 |

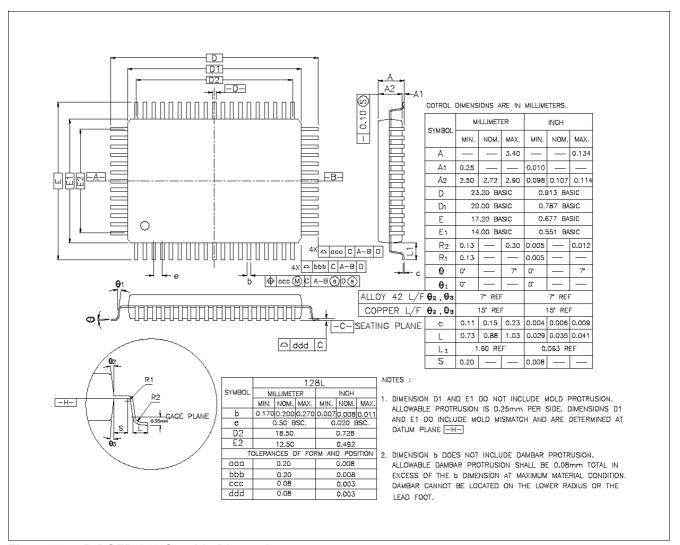

| Fiaure 34 | P-PQFP-128 Outside Dimension                                                  | 213 |

### **List of Tables**

### **List of Tables**

| Table 1  | Abbreviations for Pin Type                                           | 14 |

|----------|----------------------------------------------------------------------|----|

| Table 2  | Abbreviations for Buffer Type                                        | 14 |

| Table 3  | IO Signals                                                           |    |

| Table 4  | Bandwidth Control Timer Select                                       |    |

| Table 5  | Smart Disacrd                                                        |    |

| Table 6  | Discard Ratio                                                        |    |

| Table 7  | Single Color LED Display                                             | 32 |

| Table 8  | Dual Color LED Display                                               |    |

| Table 9  | Packet Identification                                                |    |

| Table 10 | Packet Identification Groups                                         |    |

| Table 11 | Span Packet                                                          |    |

| Table 12 | Management Packet                                                    |    |

| Table 13 | Cross_VLAN Packet                                                    |    |

| Table 14 | VLAN Filters                                                         |    |

| Table 15 | VID Comparison                                                       |    |

| Table 16 | FID Search Algorithm                                                 |    |

| Table 17 | VLAN Boundary Search Algorithm                                       |    |

| Table 18 | TXTAG Carried through Samurai-6M/6MX (ADM6996M/MX)                   |    |

| Table 19 | Egress Tag Result                                                    |    |

| Table 20 | Tagged PRI Carried                                                   |    |

| Table 21 | CFI Carried                                                          | 43 |

| Table 22 | Priority Queue                                                       |    |

| Table 23 | Queue Assigned                                                       |    |

| Table 24 | Control Register Description for Accessing the Address Table         |    |

| Table 25 | Description for Command and Access Control                           |    |

| Table 26 | Status Register Description                                          |    |

| Table 27 | Description for the Status Register                                  |    |

| Table 28 | Control Register Description for Accessing the IGMP Membership Table |    |

| Table 29 | Description for Command and Access Control                           |    |

| Table 30 | Entry Format of IGMP Membership Table                                |    |

| Table 31 | IPV4/IGMP/General Query                                              |    |

| Table 32 | IPV4/IGMP/V1 Report                                                  |    |

| Table 33 | IPV4/IGMP/General Query                                              |    |

| Table 34 | IPV4/IGMP/V1 Report                                                  |    |

| Table 35 | IPV4/IGMP/V2 Report                                                  |    |

| Table 36 | IPV4/IGMP/V2 Leave                                                   |    |

| Table 37 | IPV4/IGMP/Group-Specific Query                                       |    |

| Table 38 | IGMP Membership Table                                                |    |

| Table 39 | Forwarding Algorithm                                                 |    |

| Table 40 | Special Tag for the Receive                                          |    |

| Table 41 | Option for Special Tag Transmit                                      |    |

| Table 42 | Special Tag for the Transmit                                         |    |

| Table 43 | Special Tag                                                          |    |

| Table 44 | Set WAN/LAN Group                                                    |    |

| Table 45 | Packets Identified by ADM6996M/MX                                    |    |

| Table 46 | Speed/Duplex Configuration                                           |    |

| Table 47 | Hardware Setting                                                     |    |

| Table 48 | (D) The Pin Type of EECS, EESK, EDI and EDO during the Operation     |    |

| Table 49 | Memory Map                                                           | 79 |

### **List of Tables**

| Table 50 | Pin Description(QFP128)                           | . 79 |

|----------|---------------------------------------------------|------|

| Table 51 | Registers Address Space                           | . 80 |

| Table 52 | Registers Overview                                | . 80 |

| Table 53 | Register Access Types                             | . 89 |

| Table 54 | Registers Clock Domains                           | . 89 |

| Table 55 | P1~P5 Basic Control Registers                     | . 92 |

| Table 56 | Px_EC Registers                                   | . 93 |

| Table 57 | PxSO Registers                                    | 107  |

| Table 58 | VFxL Registers                                    | 140  |

| Table 59 | VFxH Registers                                    | 141  |

| Table 60 | TFx Registers                                     | 142  |

| Table 61 | PFx Registers                                     | 143  |

| Table 62 | RAx Registers                                     | 152  |

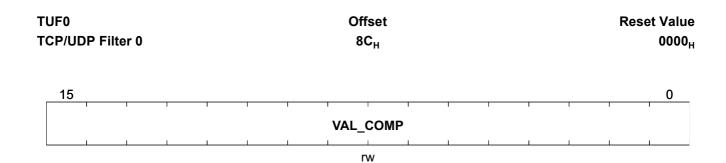

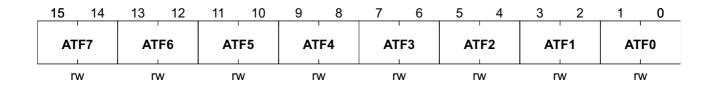

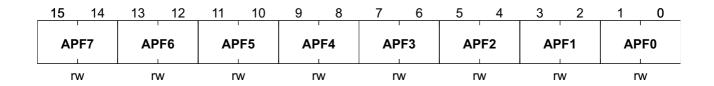

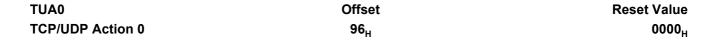

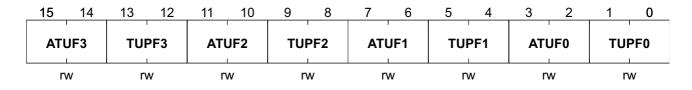

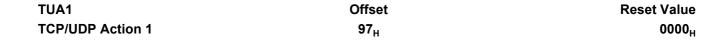

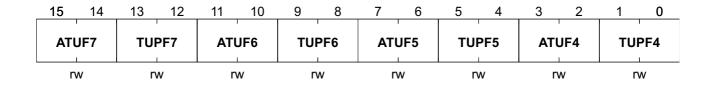

| Table 63 | TUFx Registers                                    | 153  |

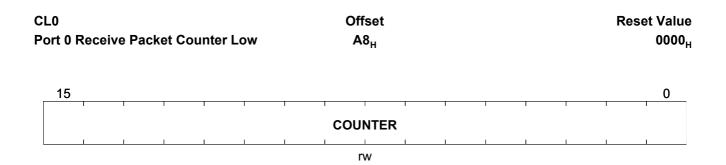

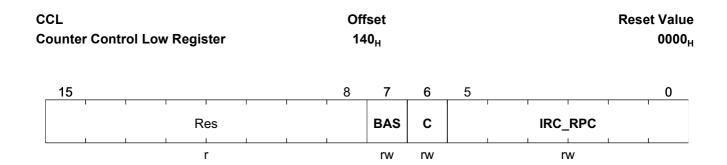

| Table 64 | CLx Registers                                     | 166  |

| Table 65 | CHx Registers                                     | 167  |

| Table 66 | PHY_Cx Registers                                  | 188  |

| Table 67 | PHY_Sx Registers                                  | 190  |

| Table 68 | PHY_Ix_A Registers                                | 191  |

| Table 69 | PHY_Ix_B Registers                                | 192  |

| Table 70 | ANAPx Registers                                   | 193  |

| Table 71 | ANLPAx Registers                                  | 194  |

| Table 72 | ANEx Registers                                    | 195  |

| Table 73 | NPTx Registers                                    | 196  |

| Table 74 | LPNPx Registers                                   | 197  |

| Table 75 | Power Consumption                                 | 199  |

| Table 76 | Absolute Maximum Ratings                          | 200  |

| Table 77 | Recommended Operating Conditions                  | 200  |

| Table 78 | DC Electrical Characteristics for 3.3 V Operation |      |

| Table 79 | XTAL/OSC Timing                                   |      |

| Table 80 | Power On Reset Timing                             |      |

| Table 81 | EEPROM Interface Timing                           |      |

| Table 82 | 10Base-TX MII Input Timing                        |      |

| Table 83 | 10-Base-TX MII Output Timing                      | 205  |

| Table 84 | 100Base-TX MII Input Timing                       | 206  |

| Table 85 | 100Base-TX MII Output Timing                      |      |

| Table 86 | RMII REFCLK Input Timing                          |      |

| Table 87 | RMII REFCLK Output Timing                         |      |

| Table 88 | Reduce MII Timing                                 |      |

| Table 89 | GPSI (7-wire) Input Timing                        | 210  |

| Table 90 | GPSI (7-wire) Output Timing                       |      |

| Table 91 | SDC/SDIO Timing                                   | 212  |

| Table 92 | MDC/MDIO Timing                                   | 212  |

**Product Overview**

### 1 Product Overview

### 1.1 Samurai-6M/6MX (ADM6996M/MX) Overview

The Samurai-6M/6MX (ADM6996M/MX) is a high performance, low cost, highly integrated (Controller, PHY and Memory) four 10M/100M auto-detect Half/Full duplex switch ports with TX/FX interfaces and two MII port with one MII supporting GPSI/RMII. The Samurai-6M/6MX (ADM6996M/MX) is intended for applications such as stand alone bridges for the low cost SOHO markets such as 5-port switches and router applications. The Samurai-6MX (ADM6996MX) is the environmentally friendly "green" package version.

The Samurai-6M/6MX (ADM6996M/MX) provides functions such as: 802.1p(Q.O.S.), 802.1Q(VLAN), Port MAC address locking, management, port status, TP auto-MDIX, 25M crystal & extra MII port functions to meet customer requests on switch demand.

The Samurai-6M/6MX (ADM6996M/MX) also supports back pressure in Half-Duplex mode and the 802.3x Flow Control Pause packet in Full-Duplex mode to prevent packet loss when buffers are full. When Back Pressure is enabled, and there is no receive buffer available for the incoming packet, the Samurai-6M/6MX (ADM6996M/MX) will issue a JAM pattern on the receiving port in Half Duplex mode and issue the 802.3x Pause packet back to the receiving end in Full Duplex mode.

The built-in SRAM used for the packet buffer is divided into 256 bytes per block to achieve the optimized memory utilization through complicated link lists on packets with various lengths.

The Samurai-6M/6MX (ADM6996M/MX) also supports priority features using Port-Based, VLAN and IP TOS field checking. Users can easily set different priority modes in individual ports, through a small low-cost micro controller when initializing or configuring on-the-fly. Each output port supports four queues in the way of fixed N: 1 fairness queuing to fit the bandwidth demand on various types of packets such as Voice, Video and Data. 802.1Q, Tag/Untag, and up to 16 groups of VLAN are also supported.

An intelligent address recognition algorithm allows Samurai-6M/6MX (ADM6996M/MX) to recognize up to 2K different MAC addresses and enables filtering and forwarding at full wire speed.

Port MAC address Locking function is also supported by Samurai-6M/6MX (ADM6996M/MX) to use on building Internet access to prevent multiple users sharing one port.

#### 1.2 Features

- Supports four 10M/100M auto-detect Half/Full duplex switch ports with TX/FX interfaces and two MII port with one MII supporting GPSI/RMII

- Supports four 10M/100M auto-detect Half/Full duplex switch ports with TX/FX interfaces, one MII port (for CPU LAN MII) and one isolated PHY(for CPU WAN MII). Five 10M/100M auto-detect Half/Full duplex switch ports with TX/FX interfaces

- 2K MAC address tables with 4-ways associative hash algorithm

- 6KX64 bits packet buffers are divided into 192 blocks of 256 bytes each

- Four queues for QoS

- Priority features by Port-Based, 802.1p, IP TOS, Diffserv, TCP/UDP Port Application-Based of packets

- Store & Forward architecture and performs forwarding and filtering at non-blocking full wire speed

- Single/Dual color LED mode with Power On auto diagnostic. Collision/Duplex LED can be separated using register setting

- 802.3x Flow Control pause packet for Full Duplex

- Back Pressure function for Half Duplex operation

- Supports packet lengths up to 1518/1522 (Default)/1536/1784 bytes in maximum

- · Scalable Per Port Bandwidth Control (Both Ingress and Egress).

- · Broadcast/Multicast Storm Suppression

**Product Overview**

- 802.1Q VLAN. Up to 16 VLAN groups are implemented by full 12 bits VID matching

- · MAC clone function to enable multiple WAN application

- TP interface Auto MDIX function for auto TX/RX swap by strapping-pin.

- Interrupt pin, Interrupt Register and Interrupt Mask Register. Programmable interrupt polarity (Default active low)

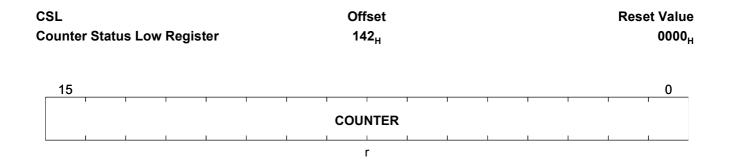

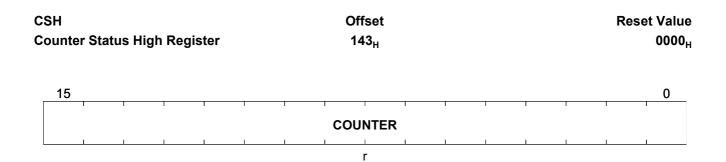

- Easy Management 32-bit smart counter for per port RX/TX byte/packet count, 16-bit smart counter for per port ERROR count and Collision count

- Supports 32 hardware IGMP Table (Multicast Table)

- MAC Address Table is accessible

- Supports 802.1x security function

- · Supports Spanning Tree Protocol

- Supports internal counter/PHY status output for management system

- 25M Crystal

- 128 QFP package with 0.18 μm technology. 1.8 V/3.3 V power supply.

- 1.0 W low power consumption.

### 1.3 Applications

Samurai-6M/6MX (ADM6996M/MX):

- · SOHO 5-port switch

- 5-port switch + Router with 2 MII CPU interface

**Product Overview**

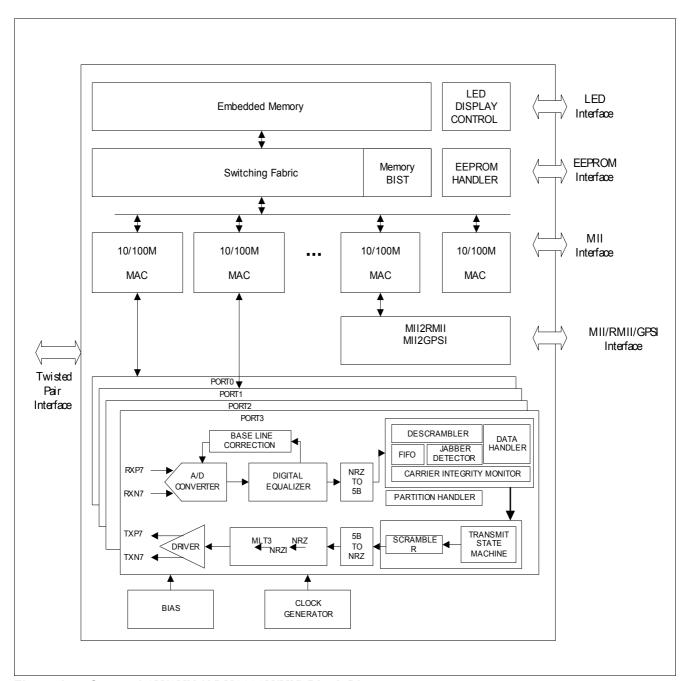

### 1.4 Block Diagram

Figure 1 Samurai-6M/6MX (ADM6996M/MX) Block Diagram

### 1.5 Data Lengths

qword: 64 bits dword: 32 bits word: 16 bits byte: 8 bits nibble: 4 bits

### 2 Interface Description

This chapter describes the interface descriptions for the Samurai-6M/6MX (ADM6996M/MX)

- Pin Diagram

- Abbreviations

- · Pin Description by Function

### 2.1 Pin Diagram

Figure 2 shows the pin diagram for the Samurai-6M/6MX (ADM6996M/MX).

Figure 2 4 TP/FX PORT + 2 MII PORT 128 Pin Diagram

### 2.2 Abbreviations

Standard abbreviations for I/O tables:

Table 1 Abbreviations for Pin Type

| Abbreviations | S Description                               |  |  |  |  |  |

|---------------|---------------------------------------------|--|--|--|--|--|

| I             | Standard input-only pin. Digital levels.    |  |  |  |  |  |

| О             | Output. Digital levels.                     |  |  |  |  |  |

| I/O           | I/O is a bidirectional input/output signal. |  |  |  |  |  |

| Al            | Input. Analog levels.                       |  |  |  |  |  |

| AO            | Output. Analog levels.                      |  |  |  |  |  |

| AI/O          | Input or Output. Analog levels.             |  |  |  |  |  |

| PWR           | Power                                       |  |  |  |  |  |

| GND           | Ground                                      |  |  |  |  |  |

| MCL           | Must be connected to Low (JEDEC Standard)   |  |  |  |  |  |

| MCH           | Must be connected to High (JEDEC Standard)  |  |  |  |  |  |

| NU            | Not Usable (JEDEC Standard)                 |  |  |  |  |  |

| NC            | Not Connected (JEDEC Standard)              |  |  |  |  |  |

### Table 2 Abbreviations for Buffer Type

| <b>Abbreviations</b>                                                                                                                           | Description                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Z                                                                                                                                              | High impedance                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PU                                                                                                                                             | Pull up, 10 kΩ                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PD                                                                                                                                             | Pull down, 10 kΩ                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| TS                                                                                                                                             | Tristate capability: The corresponding pin has 3 operational states: Low, high and high-impedance.                                                                                                                                                                                 |  |  |  |  |  |

| OD                                                                                                                                             | Open Drain. The corresponding pin has 2 operational states, active low and tristate, and allows multiple devices to share as a wire-OR. An external pull-up is required to sustain the inactive state until another agent drives it, and must be provided by the central resource. |  |  |  |  |  |

| OC                                                                                                                                             | Open Collector                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PP                                                                                                                                             | Push-Pull. The corresponding pin has 2 operational states: Active-low and active-hig (identical to output with no type attribute).                                                                                                                                                 |  |  |  |  |  |

| OD/PP Open-Drain or Push-Pull. The corresponding pin can be configured either as an of the OD attribute or as an output with the PP attribute. |                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| ST                                                                                                                                             | Schmitt-Trigger characteristics                                                                                                                                                                                                                                                    |  |  |  |  |  |

| TTL                                                                                                                                            | TTL characteristics                                                                                                                                                                                                                                                                |  |  |  |  |  |

### 2.3 Pin Description by Function

Samurai-6M/6MX (ADM6996M/MX) pins are categorized into one of the following groups:

- Network Media Connection

- Port 4 MII Interface

- Port 5 MII Interface

- LED Interface

- EEPROM Interface

- Power/Ground, 48 pins

- Miscellaneous

Note: Table 1 can be used for reference.

Table 3 IO Signals

| Table 3    | IO Signals       |      |                       |                                                                                                                                                                                       |

|------------|------------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ball No.   | Name             | Pin  | Buffer                | Function                                                                                                                                                                              |

|            |                  | Type | Type                  |                                                                                                                                                                                       |

| Network N  | Media Connection |      |                       |                                                                                                                                                                                       |

| 33         | RXP_4            | AI/O | ANA                   | Receive Pair                                                                                                                                                                          |

| 29         | RXP_3            |      |                       | Differential data is received on this pin.                                                                                                                                            |

| 21         | RXP_2            |      |                       |                                                                                                                                                                                       |

| 14         | RXP_1            |      |                       |                                                                                                                                                                                       |

| 6          | RXP_0            |      |                       |                                                                                                                                                                                       |

| 32         | RXN_4            | AI/O | ANA                   |                                                                                                                                                                                       |

| 30         | RXN_3            |      |                       |                                                                                                                                                                                       |

| 22         | RXN_2            |      |                       |                                                                                                                                                                                       |

| 15         | RXN_1            |      |                       |                                                                                                                                                                                       |

| 7          | RXN_0            |      |                       |                                                                                                                                                                                       |

| 37         | TXP_4            | AI/O | ANA                   | Transmit Pair                                                                                                                                                                         |

| 25         | TXP_3            |      |                       | Differential data is transmitted on this pin.                                                                                                                                         |

| 18         | TXP_2            |      |                       |                                                                                                                                                                                       |

| 10         | TXP_1            |      |                       |                                                                                                                                                                                       |

| 2          | TXP_0            |      |                       |                                                                                                                                                                                       |

| 36         | TXN_4            | AI/O | ANA                   |                                                                                                                                                                                       |

| 26         | TXN_3            |      |                       |                                                                                                                                                                                       |

| 19         | TXN_2            |      |                       |                                                                                                                                                                                       |

| 11         | TXN_1            |      |                       |                                                                                                                                                                                       |

| 3          | TXN_0            |      |                       |                                                                                                                                                                                       |

| Port 4 MII | Interface        |      |                       |                                                                                                                                                                                       |

| 74         | MMII_P4RXD0      | I    | PD,<br>LVTTL          | Port 4 Receive Data Bit 0 in MAC MII Mode In MAC MII mode, the bit is the LSB of MII receive data, synchronous to the rising edge of MMII_P4RXCLK.                                    |

|            | PMII_P4RXD0      | 0    | 8 mA,<br>PD,<br>LVTTL | Port 4 Receive Data Bit 0 in PCS MII Mode When port 4 is operating in PCS MII mode, the bit is the LSB of MII receive data output and synchronous to the rising edge of PMII_P4RXCLK. |

| 102        | MMII_P4RXD3      | I    | PD,<br>LVTTL          | Port 4 Receive Data Bit 3 in MAC MII Mode In MAC MII mode, this bit is bit[3] of MII receive data, and synchronous to the rising edge of MMII_P4RXCLK.                                |

|            | PMII_P4RXD3      | О    | 8 mA,<br>PD,<br>LVTTL | Port 4 Receive Data Bit 3 in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is bit[3] of MII receive data output and synchronous to the rising edge of PMII_P4RXCLK. |

Table 3 IO Signals (cont'd)

| Ball No. | Name        | Pin<br>Type | Buffer<br>Type        | Function                                                                                                                                                                                                           |

|----------|-------------|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 101      | MMII_P4RXD2 | I           | PD,<br>LVTTL          | Port 4 Receive Data Bit 2 in MAC MII Mode In MAC MII mode, this pin is bit[2] of MII receive data, and synchronous to the rising edge of MMII_P4RXCLK.                                                             |

|          | PMII_P4RXD2 | O           | 8 mA,<br>PD,<br>LVTTL | Port 4 Receive Data Bit 2 in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is bit[2] of MII receive data output and synchronous to the rising edge of PMII_P4RXCLK.                              |

| 100      | MMII_P4RXD1 | I           | PD,<br>LVTTL          | Port 4 Receive Data Bit 1 in MAC MII Mode In MAC MII mode, this pin is bit[1] of MII receive data, and synchronous to the rising edge of MMII_P4RXCLK.                                                             |

|          | PMII_P4RXD1 | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Receive Data Bit 1 in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is bit[1] of MII receive data output and synchronous to the rising edge of PMII_P4RXCLK.                              |

| 73       | MMII_P4RXDV | I           | PD,<br>LVTTL          | Port 4 Receive Data Valid in MAC MII Mode  Active high to indicate that the data on MMII_P4RXD[3:0] is valid. Synchronous to the rising edge of MMII_P4RXCLK.                                                      |

|          | PMII_P4RXDV | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Receive Data Valid in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is an active high output signal to indicate PMII_P4RXD[3:0] is valid. Synchronous to the rising edge of PMII_P4RXCLK. |

| 39       | MII_P4RXER  | I           | PD,<br>LVTTL          | Port 4 Receive Error in MAC MII Mode Active high to indicate that there is symbol error on the MII_P4RXD[3:0]. Only valid in 100M operation.                                                                       |

| 77       | MMII_P4CRS  | I           | PD,<br>LVTTL          | Port 4 Carrier Sense in MAC MII Mode In full duplex mode, MMII_P4CRS reflects the receive carrier sense situation on medium only; In Half Duplex, CRS will be high both in receive and transmit condition.         |

|          | PMII_P4CRS  | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Carrier Sense in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is used to output Carrier Sense status.                                                                                    |

| 78       | MMII_P4COL  | I           | PD,<br>LVTTL          | Port 4 Collision input in MAC MII Mode  Active high to indicate that there is collision on the medium.  Stay low in full duplex operation.                                                                         |

|          | PMII_P4COL  | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Collision output in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is used to output collision status.                                                                                     |

Table 3 IO Signals (cont'd)

| Ball No. | Name          | Pin<br>Type | Buffer<br>Type        | Function                                                                                                                                                                                                                                                                                                       |

|----------|---------------|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 106      | P4_BUSMD0     |             | PD,<br>LVTTL          | Port 4 Bus Type Configuration 0  Value on this pin will be latched by Samurai-6M/6MX  (ADM6996M/MX) at the rising edge of RESETL(RC) for Port 4 Configuration Bit 0. Combined with CFG0 and P4_BUSMD1, Samurai-6M/6MX (ADM6996M/MX) provides 4 bus type for port 4. See CFG0 pin description for more details. |

|          | MMII P4TXD0   | 0           | 8 mA,                 | Note: Power On Setting  Port 4 Transmit Data Bit 0 in MAC MII Mode                                                                                                                                                                                                                                             |

|          | MIMIL F 41XD0 |             | PD,<br>LVTTL          | The LSB bit of MAC MII Transmit data of port 4.  Synchronous to the rising edge of MMII_P4TXCLK.                                                                                                                                                                                                               |

|          | PMII_P4TXD0   | I           | PD,<br>LVTTL          | Port 4 Transmit Data Bit 0 in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is the LSB of MII transmit data input and synchronous to the rising edge of PMII_P4TXCLK.                                                                                                                        |

| 105      | P4_BUSMD1     | I           | PD,<br>LVTTL          | Port 4 Bus Type Configuration 1 Value on this pin will be latched by Samurai-6M/6MX (ADM6996M/MX) at the rising edge of RESETL(RC) for Port 4 Configuration Bit 1. Combined with CFG0 and P4_BUSMD0, Samurai-6M/6MX (ADM6996M/MX) provides 4 bus type for port 4. See CFG0 for more details.                   |

|          |               |             |                       | Note: Power On Setting                                                                                                                                                                                                                                                                                         |

|          | MMII_P4TXD1   | О           | 8 mA,<br>PD,<br>LVTTL | Port 4 Transmit Data Bit 1 in MAC MII Mode The bit[1] of MAC MII Transmit data of port 4. Synchronous to the rising edge of MMII_P4TXCLK.                                                                                                                                                                      |

|          | PMII_P4TXD1   | I           | PD,<br>LVTTL          | Port 4 Transmit Data Bit 1 in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is bit[1] of MII transmit data input and synchronous to the rising edge of PMII_P4TXCLK.                                                                                                                         |

| 103      | MMII_P4TXD3   | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Transmit Data Bit 3 in MAC MII Mode The bit[3] of MAC MII Transmit data of port 4. Synchronous to the rising edge of MMII_P4TXCLK.                                                                                                                                                                      |

|          | PMII_P4TXD3   | I           | PD,<br>LVTTL          | Port 4 Transmit Data Bit 3 in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is bit[3] of MII transmit data input and synchronous to the rising edge of PMII_P4TXCLK.                                                                                                                         |

| 104      | MMII_P4TXD2   | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Transmit Data Bit 2 in MAC MII Mode The bit[2] of MAC MII Transmit data of port 4. Synchronous to the rising edge of MMII_P4TXCLK.                                                                                                                                                                      |

|          | PMII_P4TXD2   | I           | PD,<br>LVTTL          | Port 4 Transmit Data Bit 2 in PCS MII Mode When port 4 is operating in PCS MII mode, this pin is bit[2] of MII transmit data input and synchronous to the rising edge of PMII_P4TXCLK.                                                                                                                         |

Table 3 IO Signals (cont'd)

| Ball No. | Name         | Pin<br>Type | Buffer<br>Type        | Function                                                                                                                                                                                                                                          |

|----------|--------------|-------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 114      | MMII_P4TXEN  | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Transmit Enable in MAC MII Mode Output by Samurai-6M/6MX (ADM6996M/MX) at the rising edge of MMII_P4TXCLK when Samurai-6M/6MX (ADM6996M/MX) is programmed to MAC Type MII.                                                                 |

|          | PMII_P4TXEN  | I           | PD,<br>LVTTL          | Port 4 Transmit Enable in PCS MII Mode It is the MII Transmit Enable input to Samurai-6M/6MX (ADM6996M/MX) when programmed to PCS Type MII.                                                                                                       |

| 117      | MMII_P4RXCLK | I           | PD,<br>LVTTL          | Port 4 Receive Clock in MAC MII Mode 25MHz Free Running clock in 100M Mode and 2.5 MHz free running clock in 10M Mode. MMII_P4RXDV and MMII_P4RXD[3:0] should be synchronous to the rising edge of this clock                                     |

|          | PMII_P4RXCLK | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Receive Clock in PCS MII Mode 25MHz Free Running clock in 100M Mode and 2.5 MHz free running clock in 10M Mode. PMII_P4RXDV and PMII_P4RXD[3:0] should be synchronous to the rising edge of this clock                                     |

| 115      | MMII_P4TXCLK | I           | PD,<br>LVTTL          | Port 4 Transmit Clock in MAC MII Mode 25MHz Free Running clock in 100M Mode and 2.5 MHz free running clock in 10M Mode. MMII_P4TXEN and MMII_P4TXD[3:0] should be synchronous to the rising edge of this clock                                    |

|          | PMII_P4TXCLK | 0           | 8 mA,<br>PD,<br>LVTTL | Port 4 Transmit Clock in PCS MII Mode 25MHz Free Running clock in 100M Mode and 2.5 MHz free running clock in 10M Mode. PMII_P4TXEN and PMII_P4TXD[3:0] should be synchronous to the rising edge of this clock                                    |

| 62       | P4FX         | I           | PD,<br>LVTTL          | Port 4 Fiber Selection for PCS MII/PHY mode  During power on reset, value will be latched by Samurai- 6M/6MX (ADM6996M/MX) at the rising edge of  RESETL(RC) as port 4 Fiber select.  0 <sub>B</sub> Twisted Pair Mode  1 <sub>B</sub> Fiber Mode |

Table 3 IO Signals (cont'd)

| Ball No.   | Name        | Pin  | Buffer                | Function                                                                                                                                                                                                                                                                                                                                                                  |

|------------|-------------|------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |             | Type | Type                  |                                                                                                                                                                                                                                                                                                                                                                           |

| Port 5 MII | Interface   |      |                       |                                                                                                                                                                                                                                                                                                                                                                           |

| 63         | GFCEN       | I    | PU,<br>LVTTL          | Global Flow Control Enable  Value on this pin will be latched by Samurai-6M/6MX  (ADM6996M/MX) at the rising edge of RESETL(RC) as Flow control enable.  Note: Power On Setting  0 <sub>B</sub> Flow Control Capability is depended upon the register setting in corresponding port's Basic Control Register  1 <sub>B</sub> All ports flow control capability is enabled |

|            | MII_P5TXD0  | 0    | 4 mA,<br>PU,<br>LVTTL | Port 5 Transmit Data Bit 0 in MII Mode The LSB bit of MII Transmit data of port 5. Synchronous to the rising edge of MII_P5TXCLK.                                                                                                                                                                                                                                         |

|            | GPSI_P5TXD  | 0    | 4 mA,<br>PU,<br>LVTTL | Port 5 Transmit Data in GPSI Mode When port 5 is operating in GPSI mode, this pin acts as GPSI Transmit Data. Synchronous to the rising edge of GPSI_P5TXCLK.                                                                                                                                                                                                             |

|            | RMII_P5TXD0 | 0    | 4 mA,<br>PU,<br>LVTTL | Port 5 Transmit Data Bit 0 in RMII Mode When port 5 is operating in RMII mode, this pin acts as RMII Transmit Data Bit[0]. Synchronous to the rising edge of REFCLK_IN.                                                                                                                                                                                                   |

| 61         | P5_BUSMD0   | I    | PD,<br>LVTTL          | Port 5 Bus Mode Selection Bit 0  Value on this pin will be latched by Samurai-6M/6MX  (ADM6996M/MX) at the rising edge of RESETL(RC) as port 5 bus mode selection bit 0. Combined with P5_BUSMD1,  Samurai-6M/6MX (ADM6996M/MX) provides 3 bus types for port 5. P5_BUSMD[1:0], Interface  Note: Power On Setting  00 <sub>B</sub> MII                                    |

|            |             |      |                       | 01 <sub>B</sub> GPSI<br>10 <sub>B</sub> RMII<br>11 <sub>B</sub> Reserved and not allowed                                                                                                                                                                                                                                                                                  |

|            | MII_P5TXD1  | 0    | 4 mA,<br>PD,<br>LVTTL | Port 5 Transmit Data Bit 1 in MII Mode The bit[1] of MII Transmit data of port 5. Synchronous to the rising edge of MII_P5TXCLK.                                                                                                                                                                                                                                          |

|            | RMII_P5TXD1 | 0    | 4 mA,<br>PD,<br>LVTTL | Port 5 Transmit Data Bit 1 in RMII Mode The bit[1] of RMII Transmit data of port 5. Synchronous to the rising edge of REFCLK_IN.                                                                                                                                                                                                                                          |

Table 3 IO Signals (cont'd)

| Ball No. | Name        | Pin<br>Type | Buffer<br>Type        | Function                                                                                                                                                                                                                                                                 |

|----------|-------------|-------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 60       | P5_BUSMD1   | 1           | PD,<br>LVTTL          | Port 5 Bus Mode Selection Bit 1  Value on this pin will be latched by Samurai-6M/6MX  (ADM6996M/MX) at the rising edge of RESETL(RC) as port 5 bus mode selection bit 1. See P5_BUSMD0 for more details.  Note: Power On Setting                                         |

|          | MII_P5TXD2  | 0           | 4 mA,<br>PD,<br>LVTTL | Port 5 Transmit Data Bit 2 in MII Mode The bit[2] of MII Transmit data of port 5. Synchronous to the rising edge of MII_P5TXCLK.                                                                                                                                         |

| 59       | SDIO_MD     | I           | PD,<br>LVTTL          | SDC/SDIO Mode Selection  Value on this pin will be latched by Samurai-6M/6MX  (ADM6996M/MX) at the rising edge of RESETL(RC) as  SDC/SDIO control signal which is used to select 16 bit mode.  Note: Power On Setting                                                    |

|          | MII_P5TXD3  | 0           | 4 mA,<br>PD,<br>LVTTL | 0 <sub>B</sub> 16 bits mode, MDC/MDIO timing compatible  Port 5 Transmit Data Bit 3 in MII Mode  The MSB bit of MII Transmit data of port 5. Synchronous to the rising edge of MII_P5TXCLK.                                                                              |

| 66       | PHYAS0      | I           | PD,<br>LVTTL          | PHY Address MSB Bit 0  During power on reset, value will be latched by Samurai-6M/6MX (ADM6996M/MX) at the rising edge of RESETL(RC) as PHY start address select.  PHYAS[1:0] = 00 <sub>B</sub> and PHY address starts from 01000 <sub>B</sub> .  Note: Power On Setting |

|          | MII_P5TXEN  | 0           | 8 mA,<br>PD,<br>LVTTL | Port 5 Transmit Enable TXEN in MII Mode Active high to indicate that the data on MII_P5TXD[3:0] is valid. Synchronous to the rising edge of MII_P5TXCLK.                                                                                                                 |

|          | GPSI_P5TXEN | 0           | 8 mA,<br>PD,<br>LVTTL | Port 5 Transmit Enable TXEN in GPSI Mode  Active high to indicate that the data on GPSI_P5TXD is valid. Synchronous to the rising edge of GPSI_P5TXCLK.                                                                                                                  |

|          | RMII_P5TXEN | 0           | 8 mA,<br>PD,<br>LVTTL | Port 5 Transmit Enable TXEN in RMII Mode Active high to indicate that the data on RMII_P5TXD[1:0] is valid. Synchronous to the rising edge of REFCLK_IN.                                                                                                                 |

| 53       | MII_P5RXD0  | I           | PD,<br>LVTTL          | Port 5 Receive Data Bit 0 in MII Mode In MII mode, the bit is the LSB of MII receive data, synchronous to the rising edge of MII_P5RXCLK.                                                                                                                                |

|          | GPSI_P5RXD  | I           | PD,<br>LVTTL          | Port 5 Receive Data in GPSI Mode In GPSI Mode, this acts as Receive Data Input, synchronous to the rising edge of GPSI_P5RXCLK.                                                                                                                                          |

|          | RMII_P5RXD0 | I           | PD,<br>LVTTL          | Port 5 Receive Data Bit 0 in RMII Mode In RMII mode, the bit is the LSB of RMII receive data, synchronous to the rising edge of REFCLK_IN.                                                                                                                               |

Table 3 IO Signals (cont'd)

| Ball No. | Name             | Pin<br>Type | Buffer<br>Type | Function                                                                                                                                                                                                       |

|----------|------------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 54       | MII_P5RXD1       | Пуре        | PD,<br>LVTTL   | Port 5 Receive Data Bit 1 in MII Mode In MII mode, the bit is the bit[1] of MII receive data, synchronous to the rising edge of MII_P5RXCLK.                                                                   |

|          | RMII_P5RXD1      | I           | PD,<br>LVTTL   | Port 5 Receive Data Bit 1 in RMII Mode In RMII mode, the bit is the MSB of RMII receive data, synchronous to the rising edge of REFCLK_IN.                                                                     |

| 55       | MII_P5RXD2       | I           | PD,<br>LVTTL   | Port 5 Receive Data Bit 2 in MII Mode In MII mode, the bit is the bit[2] of MII receive data. Synchronous to the rising edge of MII_P5RXCLK.                                                                   |

| 56       | MII_P5RXD3       | I           | PD,<br>LVTTL   | Port 5 Receive Data Bit 3 in MII Mode In MII mode, the bit is the bit[3] of MII receive data. Synchronous to the rising edge of MII_P5RXCLK.                                                                   |

| 52       | MII_P5RXDV       | I           | PD,<br>LVTTL   | Port 5 Receive Data Valid in MII Mode Active high to indicate that the data on MII_P5RXD[3:0] is valid. Synchronous to the rising edge of MII_P5RXCLK.                                                         |

|          | RMII_P5<br>CRSDV | I           | PD,<br>LVTTL   | Port 5 Carrier Sense and Receive Data Valid in RMII Mode  Active high to indicate that the data on RMII_P5RXD[1:0] is valid. Synchronous to the rising edge of REFCLK _IN.                                     |

| 68       | MII_P5RXER       | I           | PD,<br>LVTTL   | Port 5 Receive Error in MII Mode Active high to indicate that there is symbol error on the MII_P5RXD[3:0]. Only valid in 100M operation.                                                                       |

|          | RMII_P5RXER      | I           | PD,<br>LVTTL   | Port 5 Receive Error in RMII Mode Active high to indicate that there is symbol error on the RMII_P5 RXD[1:0]. Only valid in 100M operation.                                                                    |

| 57       | MII_P5CRS        | I           | PD,<br>LVTTL   | Port 5 Carrier Sense in MII Mode In full duplex mode, MII_P5CRS reflects the receive carrier sense situation on medium only; In Half Duplex, MII_P5CRS will be high both in receive and transmit condition.    |

|          | GPSI_P5CRS       | I           | PD,<br>LVTTL   | Port 5 Carrier Sense in GPSI Mode In full duplex mode, GPSI_P5CRS reflects the receive carrier sense situation on medium only; In Half Duplex, GPSI_P5CRS will be high both in receive and transmit condition. |

| 58       | MII_P5COL        | I           | PD,<br>LVTTL   | Port 5 Collision Input in MII Mode  Active high to indicate that there is collision on the medium.  Stay low in full duplex operation.                                                                         |

|          | GPSI_P5COL       | I           | PD,<br>LVTTL   | Port 5 Collision Input in GPSI Mode  Active high to indicate that there is collision on the medium.  Stay low in full duplex operation.                                                                        |

Table 3 IO Signals (cont'd)

| Ball No. | Name             | Pin<br>Type | Buffer<br>Type        | Function                                                                                                                                                                                           |  |

|----------|------------------|-------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

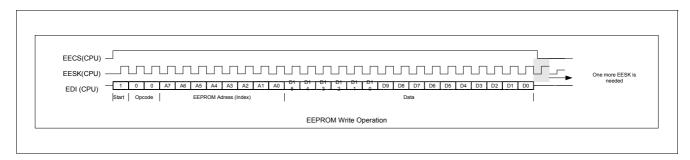

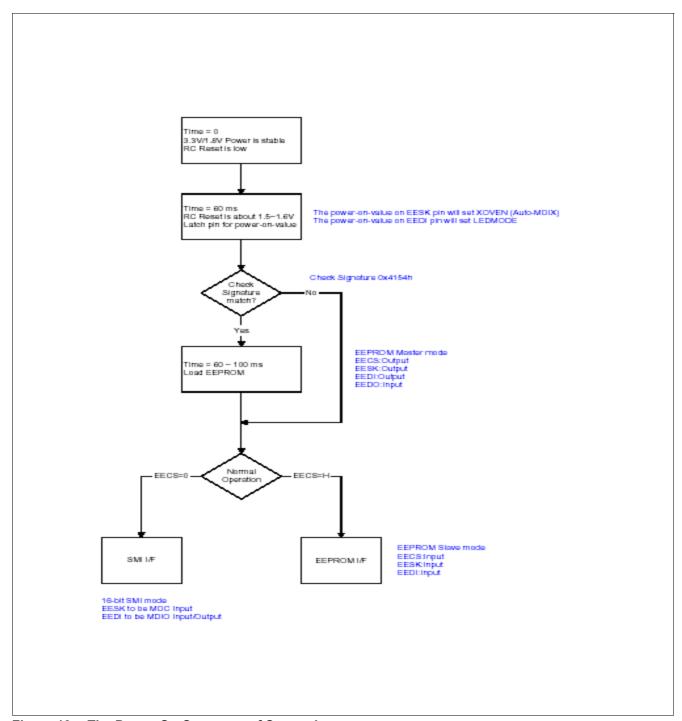

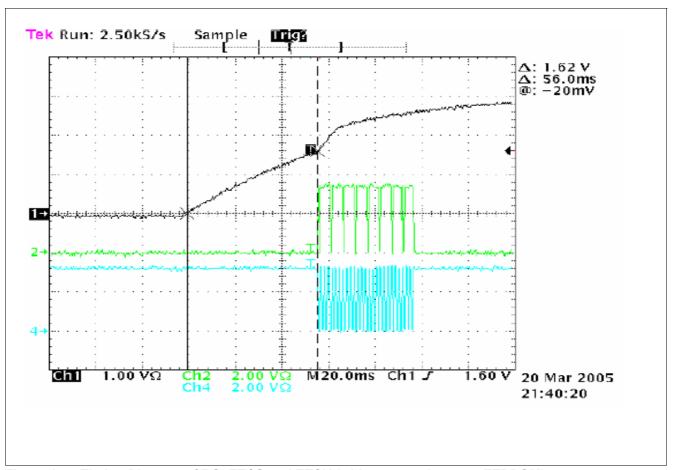

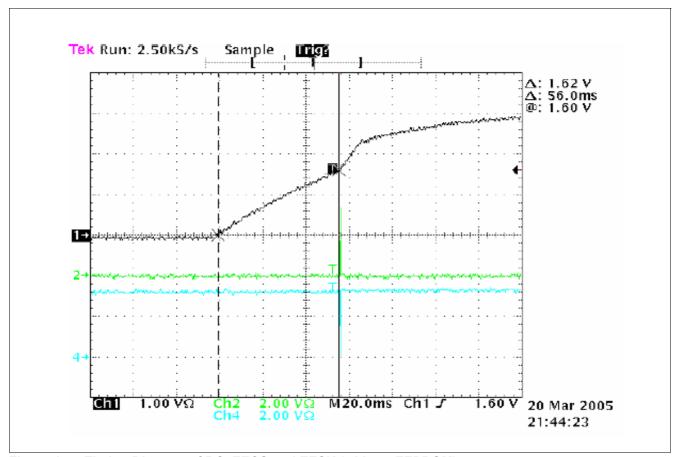

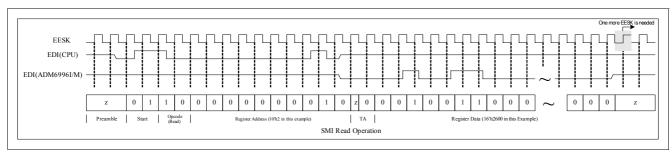

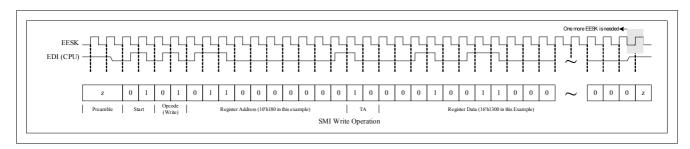

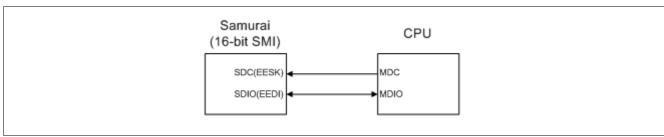

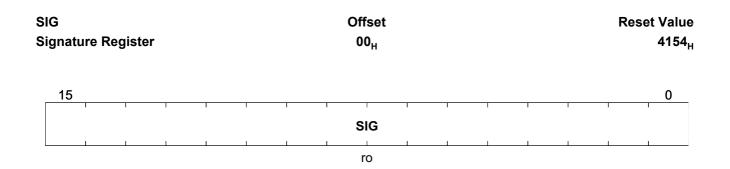

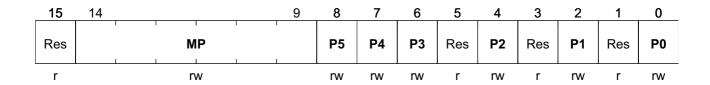

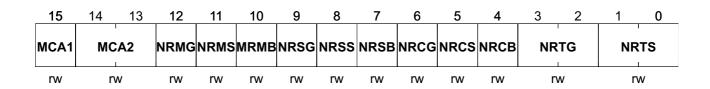

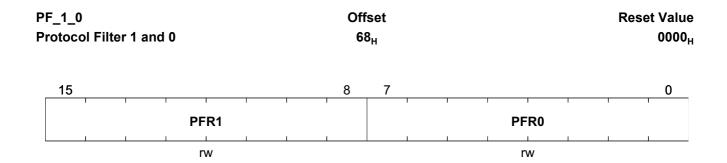

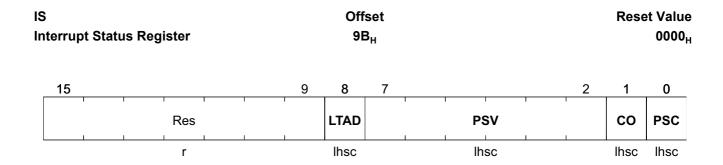

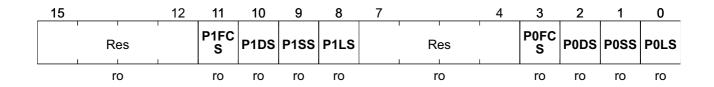

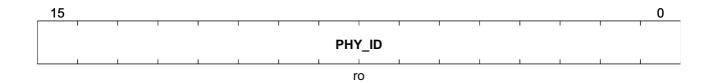

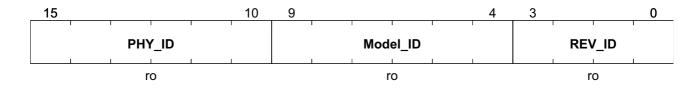

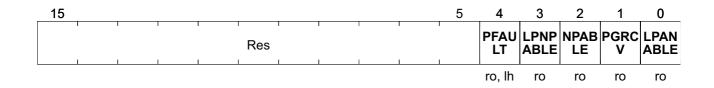

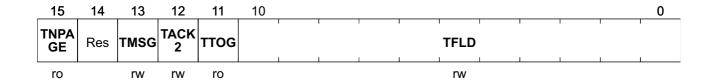

| 72       | MII_P5RXCLK      | 1           | PD,<br>LVTTL          | Port 5 Receive Clock Input in MII Mode MII_P5RXDV and MII_P5RXD[3:0] are synchronous to the rising edge of this clock. It is free running 25 MHz clock in 100M mode and 2.5 MHz clock in 10M mode. |  |