## **Applications**

- Low voltage, high density systems with Intermediate Bus Architectures (IBA)

- Point-of-load regulators for high performance DSP, FPGA, ASIC, and microprocessor applications

- · Industrial computing, servers, and storage

- Broadband, networking, optical, and wireless communications systems

- Active memory bus terminators

### **Benefits**

- Integrates digital power conversion with intelligent power management

- Eliminates the need for external power management components and communication bus

- Completely programmable via pin strapping and one external resistor

- One part that covers all applications

- Reduces board space, system cost and complexity, and time to market

#### **Features**

- RoHS lead free and lead-solder-exempt products are available

- Wide input voltage range: 8V–14V

- High continuous output current: 40A

- Wide programmable output voltage range: 0.5V– 3.65V

- Active digital current share

- Output voltage margining

- Overcurrent and overtemperature protections

- Overvoltage and undervoltage protections, and Power Good signal tracking the output voltage setpoint

- Tracking during turn-on and turn-off with guaranteed slew rates

- Sequenced and cascaded modes of operation

- Single-wire line for frequency synchronization between multiple POLs

- Programmable feedback loop compensation

- Differential output voltage sense

- Enable control

- Flexible fault management and propagation

- Start-up into the load pre-biased up to 100%

- Current sink capability

- Real time current measurements, monitoring, and reporting

- Industry standard size through-hole single-in-line package: 1.8"x0.55"

- Low height of 1.1"

- Wide operating temperature range: 0 to 70°C

- UL 60950-1/CSA 22.2 No. 60950-1-07 Second Edition, IEC 60950-1: 2005, and EN 60950-1:2006

## Description

Power-One's point-of-load converters are recommended for use with regulated bus converters in an Intermediate Bus Architecture (IBA). The ZY2140 is an intelligent, fully programmable step-down point-of-load DC-DC module integrating digital power conversion and power management. The ZY2140 completely eliminates the need for external components for sequencing, tracking, protection, monitoring, and reporting. Performance parameters of the ZY2140 are programmable by pin strapping and an external resistor and can be changed by the user at any time during product development and service without a need for a communication bus.

#### **Reference Documents**

No-Bus<sup>TM</sup> POL Converters. Application Note Z-One<sup>®</sup> POL Converters. Eutectic Solder Process Application Note Z-One<sup>®</sup> POL Converters. Lead-Free Process Application Note

## 1. Ordering Information

| ZY                                    | 21                                    | 40                        | у                                                                                                                           | -    | ZZ                                                                                    |

|---------------------------------------|---------------------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------|

| Product<br>family:<br>Z-One<br>Module | Series:<br>No-Bus<br>POL<br>Converter | Output<br>Current:<br>40A | RoHS compliance: No suffix - RoHS compliant with Pb solder exemption <sup>1</sup> G - RoHS compliant for all six substances | Dash | Packaging Option <sup>2</sup> : R1 – 30 pcs Tray Q1 – 1 pc sample for evaluation only |

<sup>&</sup>lt;sup>1</sup> The solder exemption refers to all the restricted materials except lead in solder. These materials are Cadmium (Cd), Hexavalent chromium (Cr6+), Mercury (Hg), Polybrominated biphenyls (PBB), Polybrominated diphenylethers (PBDE), and Lead (Pb) used anywhere except in solder.

Example: **ZY2140G-R3**: A 30-piece tray of RoHS compliant POL converters. Each POL converter is labeled ZY2140G.

## 2. Absolute Maximum Ratings

Stresses in excess of the absolute maximum ratings may cause performance degradation, adversely affect long-term reliability, and cause permanent damage to the POL converter.

| Parameter             | Conditions/Description      | Min | Max | Units |

|-----------------------|-----------------------------|-----|-----|-------|

| Operating Temperature | Controller Case Temperature | -40 | 105 | °C    |

| Input Voltage         | 250ms Transient             |     | 15  | VDC   |

# 3. Environmental and Mechanical Specifications

| Parameter                          | Conditions/Description                                                                     | Min                | Nom | Max | Units                        |

|------------------------------------|--------------------------------------------------------------------------------------------|--------------------|-----|-----|------------------------------|

| Ambient Temperature Range          |                                                                                            | 0                  |     | 70  | °C                           |

| Storage Temperature (Ts)           |                                                                                            | -55                |     | 125 | °C                           |

| Weight                             |                                                                                            |                    | 33  |     | grams                        |

| Operating Vibration (sinusoidal)   | Frequency Range<br>Magnitude<br>Sweep Rate<br>Repetitions in each axis (Min-Max-Min Sweep) | 5<br>0.5<br>1<br>2 |     | 500 | Hz<br>G<br>oct/min<br>sweeps |

| Non-Operating Shock<br>(half sine) | Acceleration<br>Duration<br>Number of shocks in each axis                                  | 50<br>11<br>10     |     |     | G<br>ms                      |

| MTBF                               | Calculated Per Telcordia Technologies SR-332                                               | TBD                |     |     | MHrs                         |

| Peak Reflow Temperature            | ZY2140                                                                                     |                    |     | 220 | °C                           |

| Peak Reflow Temperature            | ZY2140G                                                                                    |                    | 245 | 260 | °C                           |

| Lead Plating                       | ZY2140 and ZY2140G                                                                         | 100% Matte Tin     |     |     |                              |

| Moisture Sensitivity Level         | JEDEC J-STD-020C                                                                           | 3                  |     |     |                              |

<sup>&</sup>lt;sup>2</sup> Packaging option is used only for ordering and not included in the part number printed on the POL converter label.

## 4. Electrical Specifications

Specifications apply at the input voltage from 8V to 14V, output load from 0 to 40A, ambient temperature from 0°C to 70°C, output capacitance consisting of  $110\mu F$  ceramic and  $220\mu F$  tantalum, and the CCA=1 unless otherwise noted.

## 4.1 Input Specifications

| Parameter                        | Conditions/Description     | Min | Nom        | Max  | Units      |

|----------------------------------|----------------------------|-----|------------|------|------------|

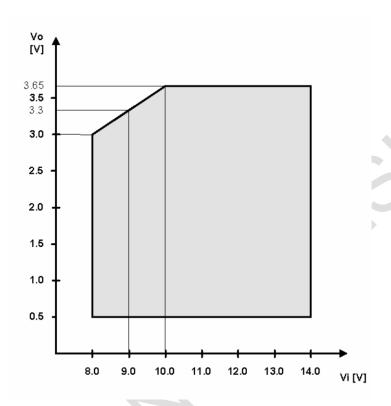

| Input voltage (V <sub>IN</sub> ) | Refer to Figure 1          | 8   |            | 14   | VDC        |

| Undervoltage Lockout Threshold   | Ramping Up<br>Ramping Down |     | 7.5<br>6.6 |      | VDC<br>VDC |

| Input Current                    | V <sub>IN</sub> =12V       |     | 23         |      | mADC       |

| Maximum Input Current            | $V_{IN}=8V$                |     |            | 19.7 | ADC        |

## 4.2 Output Specifications

| Parameter                                                                | Conditions/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Min              | Nom                                                | Max      | Units                 |

|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------------------------------------------|----------|-----------------------|

| Output Current (I <sub>OUT</sub> )                                       | V <sub>IN MIN</sub> to V <sub>IN MAX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -40 <sup>1</sup> |                                                    | 40       | ADC                   |

| Output Voltage Range (V <sub>OUT</sub> )                                 | Programmable <sup>2</sup> with a resistor between TRIM and MARGIN pins Default (no resistor)                                                                                                                                                                                                                                                                                                                                                                                                 | 0.5              | 0.5                                                | 3.65     | VDC<br>VDC            |

| Output Voltage Setpoint<br>Accuracy <sup>3</sup>                         | V <sub>IN</sub> =12V, I <sub>OUT</sub> =0.5*I <sub>OUT MAX</sub> , room temperature                                                                                                                                                                                                                                                                                                                                                                                                          | ±1.5% o          | r 20mV whic<br>greater                             | hever is | %V <sub>OUT</sub>     |

| Line Regulation <sup>3</sup>                                             | V <sub>IN MIN</sub> to V <sub>IN MAX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                  | ±0.5                                               |          | %V <sub>OUT</sub>     |

| Load Regulation <sup>3</sup>                                             | 0 to I <sub>OUT MAX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                  | ±0.5                                               |          | %V <sub>OUT</sub>     |

| Dynamic Regulation<br>Peak Deviation<br>Settling Time                    | 50% - 75% - 50% load step<br>Slew rate 1Α/μs, C <sub>OUT</sub> =380μF<br>to 10% of peak deviation                                                                                                                                                                                                                                                                                                                                                                                            |                  | 280<br>100                                         |          | mV<br>μs              |

| Output Voltage Peak-to-Peak<br>Ripple and Noise<br>BW=20MHz<br>Full Load | V <sub>IN</sub> =12V, V <sub>OUT</sub> =0.75V<br>V <sub>IN</sub> =12V, V <sub>OUT</sub> =2.5V<br>V <sub>IN</sub> =12V, V <sub>OUT</sub> =3.3V                                                                                                                                                                                                                                                                                                                                                |                  | 15<br>25<br>35                                     |          | mV<br>mV<br>mV        |

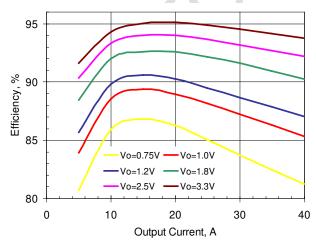

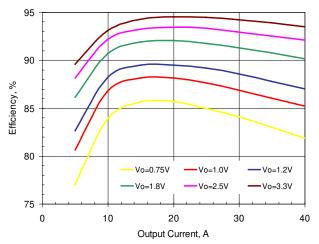

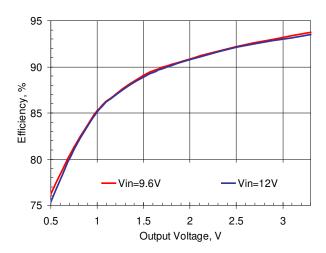

| Efficiency<br>F <sub>Sw</sub> =500kHz<br>Full Load<br>Room temperature   | $\begin{array}{c} V_{\text{IN}} = 12 \text{V}, \ V_{\text{OUT}} = 0.5 \text{V} \\ V_{\text{IN}} = 12 \text{V}, \ V_{\text{OUT}} = 0.75 \text{V} \\ V_{\text{IN}} = 12 \text{V}, \ V_{\text{OUT}} = 1.0 \text{V} \\ V_{\text{IN}} = 12 \text{V}, \ V_{\text{OUT}} = 1.2 \text{V} \\ V_{\text{IN}} = 12 \text{V}, \ V_{\text{OUT}} = 1.8 \text{V} \\ V_{\text{IN}} = 12 \text{V}, \ V_{\text{OUT}} = 2.5 \text{V} \\ V_{\text{IN}} = 12 \text{V}, \ V_{\text{OUT}} = 3.3 \text{V} \end{array}$ |                  | 75.3<br>81.9<br>85.3<br>87<br>90.2<br>92.1<br>93.5 |          | %<br>%<br>%<br>%<br>% |

| Temperature Coefficient                                                  | V <sub>IN</sub> =12V, I <sub>OUT</sub> =0.5*I <sub>OUT MAX</sub>                                                                                                                                                                                                                                                                                                                                                                                                                             |                  | 35                                                 |          | ppm/°C                |

| Switching Frequency                                                      | 2 phases combined                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 450              | 500                                                | 550      | kHz                   |

<sup>&</sup>lt;sup>1</sup> At the negative output current (bus terminator mode) efficiency of the ZY2140 degrades resulting in increased internal power dissipation. Maximum allowable negative current is limited to 40A.

4

<sup>&</sup>lt;sup>2</sup> ZY2140 is a step-down converter, thus the output voltage is always lower than the input voltage as show in **Error! Reference source not found.**.

Digital PWM has an inherent quantization uncertainty of ±6.25mV that is not included in the specified static regulation parameters.

## 4.3 Protection Specifications

| Parameter          | Conditions/Description                                                                                              | ription Min Nom            |                  |            |                       |

|--------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------|------------------|------------|-----------------------|

|                    | Output Overcurrent Protection                                                                                       | n                          |                  |            |                       |

| Type               |                                                                                                                     | Non-Latching, 130ms period |                  |            |                       |

| Threshold          |                                                                                                                     | 140                        |                  |            | %l <sub>OUT</sub>     |

| Threshold Accuracy |                                                                                                                     | -25                        |                  | 25         | %I <sub>OCP.SET</sub> |

|                    | Output Overvoltage Protectio                                                                                        | n                          |                  |            |                       |

| Type               |                                                                                                                     |                            | Late             | ching      |                       |

| Threshold          | Follows the output voltage setpoint                                                                                 |                            | 130 <sup>1</sup> |            | %V <sub>O.SET</sub>   |

| Threshold Accuracy | Measured at V <sub>O.SET</sub> =2.5V                                                                                | -2                         |                  | 2          | %V <sub>OVP.SET</sub> |

| Delay              | From instant when threshold is exceeded until the turn-off command is generated                                     |                            | 6                |            | μs                    |

|                    | Output Undervoltage Protection                                                                                      | on                         |                  |            |                       |

| Type               |                                                                                                                     | N                          | lon-Latching     | , 130ms pe | eriod                 |

| Threshold          | Follows the output voltage setpoint                                                                                 |                            | 75               |            | %V <sub>O.SET</sub>   |

| Threshold Accuracy | Measured at V <sub>O.SET</sub> =2.5V                                                                                | -2                         |                  | 2          | %V <sub>UVP.SET</sub> |

| Delay              | From instant when threshold is exceeded until the turn-off command is generated                                     |                            | 6                |            | μs                    |

|                    | Overtemperature Protection                                                                                          |                            |                  |            |                       |

| Туре               |                                                                                                                     | N                          | lon-Latching     | , 130ms pe | eriod                 |

| Turn Off Threshold | Temperature is increasing                                                                                           |                            | 120              |            | °C                    |

| Turn On Threshold  | Temperature is decreasing after module was shut down by OTP                                                         |                            | 110              |            | °C                    |

| Threshold Accuracy |                                                                                                                     | -5                         |                  | 5          | °C                    |

| Delay              | From instant when threshold is exceeded until the turn-off command is generated                                     |                            | 6                |            | μs                    |

|                    | Power Good Signal (PGOOD p                                                                                          | in)                        |                  |            |                       |

| Logic              | V <sub>OUT</sub> is inside the PG window and stable V <sub>OUT</sub> is outside of the PG window or ramping up/down | High                       |                  |            | N/A                   |

| Lower Threshold    | Follows the output voltage setpoint                                                                                 |                            | Low<br>90        |            | %V <sub>O.SET</sub>   |

| Upper Threshold    | Follows the output voltage setpoint                                                                                 |                            | 110              |            | %V <sub>O.SET</sub>   |

| Delay              | From instant when threshold is exceeded until status of PG pin changes                                              | 6                          |                  | μs         |                       |

| Threshold Accuracy | Measured at V <sub>O.SET</sub> =2.5V                                                                                | -2                         |                  | 2          | %V <sub>O.SET</sub>   |

<sup>&</sup>lt;sup>1</sup> Minimum OVP threshold is 1.0V

14

## 4.4 Feature Specifications

| Parameter                             | Parameter Conditions/Description                                           |                     |                   |                         | Units             |  |  |  |  |

|---------------------------------------|----------------------------------------------------------------------------|---------------------|-------------------|-------------------------|-------------------|--|--|--|--|

|                                       | Current Share (CS pin)                                                     |                     |                   |                         |                   |  |  |  |  |

| Туре                                  |                                                                            | Active, Single Line |                   |                         |                   |  |  |  |  |

| Current Share Accuracy                | I <sub>OUT MIN</sub> ≥20%*I <sub>OUT NOM</sub>                             |                     | %l <sub>out</sub> |                         |                   |  |  |  |  |

|                                       | Tracking                                                                   |                     |                   |                         |                   |  |  |  |  |

| Rising Slew Rate                      | Proportional to SYNC frequency                                             |                     | 0.1               |                         | V/ms              |  |  |  |  |

| Falling Slew Rate                     | Proportional to SYNC frequency                                             |                     | -0.5              |                         | V/ms              |  |  |  |  |

|                                       | Enable (EN pin)                                                            |                     |                   |                         |                   |  |  |  |  |

| EN Pin Polarity                       |                                                                            | Positive (          |                   | output whe oulled high) | n EN pin is       |  |  |  |  |

| EN High Threshold                     |                                                                            | 2.3                 |                   |                         | VDC               |  |  |  |  |

| EN Low Threshold                      |                                                                            |                     |                   | 1.0                     | VDC               |  |  |  |  |

| Open Circuit Voltage                  |                                                                            | 3.3                 |                   |                         | VDC               |  |  |  |  |

| Turn-On Delay                         | From EN pin changing state to V <sub>OUT</sub> starting to ramp up         | 0                   |                   |                         | ms                |  |  |  |  |

| Turn-Off Delay                        | From EN pin changing state to V <sub>OUT</sub> reaching 0V                 |                     | 11                |                         | ms                |  |  |  |  |

|                                       | Feedback Loop Compensation (CC                                             | A pin)              |                   |                         |                   |  |  |  |  |

| CCA pin is open                       | Recommended C <sub>OUT</sub> /ESR range, combination of ceramic + tantalum | 50/5 +<br>220/40    | 100/5 +<br>470/40 | 400/5 +<br>2000/20      | μF/mΩ<br>μF/mΩ    |  |  |  |  |

| CCA pin is connected to GND           | Recommended C <sub>OUT</sub> /ESR range, ceramic                           | 100/5               | 220/5             | 400/5                   | μF/mΩ             |  |  |  |  |

|                                       | Output Current Monitoring (CS                                              | pin)                |                   |                         |                   |  |  |  |  |

| Output Current Monitoring<br>Accuracy | 30%*Iouт nom < Iouт < Iouт nom<br>V <sub>IN</sub> =12V                     | -20                 |                   | +20                     | %l <sub>OUT</sub> |  |  |  |  |

| Conversion Ratio                      | Duty Cycle of the negative pulse corresponding to 100% of nominal current  | 74                  |                   |                         | %                 |  |  |  |  |

|                                       | Remote Voltage Sense (-VS and +V                                           | S pins)             | •                 |                         |                   |  |  |  |  |

| Туре                                  |                                                                            | Differential        |                   |                         |                   |  |  |  |  |

| Voltage Drop Compensation             | Between +VS and VOUT                                                       |                     |                   | 300                     | mV                |  |  |  |  |

| Voltage Drop Compensation             | Between -VS and PGND                                                       |                     |                   | 100                     | mV                |  |  |  |  |

# 4.5 Signal Specifications

| Parameter | Conditions/Description                       | Min           | Nom | Max           | Units            |

|-----------|----------------------------------------------|---------------|-----|---------------|------------------|

| VDD       | Internal supply voltage                      | 3.15          | 3.3 | 3.45          | V                |

|           | SYNC Line                                    |               |     |               |                  |

| ViL_s     | LOW level input voltage                      | -0.5          |     | 0.3 x VDD     | V                |

| ViH_s     | HIGH level input voltage                     | 0.75 x<br>VDD |     | VDD + 0.5     | V                |

| Vhyst_s   | Hysteresis of input Schmitt trigger          | 0.25 x<br>VDD |     | 0.45 x<br>VDD | V                |

| loL_s     | LOW level sink current V(SYNC)=0.5V          | 14            |     | 60            | mA               |

| lpu_s     | Pull-up current source V(SYNC)=0V            | 300           |     | 1000          | μΑ               |

| Tr_s      | Maximum allowed rise time 10/90%VDD          |               |     | 300           | ns               |

| Cnode_s   | Added node capacitance                       |               | 5   | 10            | pF               |

| Freq_s    | Clock frequency of external SYNC line        | 475           |     | 525           | kHz              |

| Tsynq     | Sync pulse duration                          | 22            |     | 28            | % of clock cycle |

| ТО        | Data=0 pulse duration                        | 72            |     | 78            | % of clock cycle |

|           | Inputs: CCA, EN, IM                          | 1             |     |               |                  |

| lup_x     | Pull-up current source V(X)=0                | 25            |     | 110           | μΑ               |

| ViL_x     | LOW level input voltage                      | -0.5          |     | 0.3 x VDD     | V                |

| ViH_x     | HIGH level input voltage                     | 0.7 x VDD     |     | VDD+0.5       | V                |

| Vhyst_x   | Hysteresis of input Schmitt trigger          | 0.1 x VDD     |     | 0.3 x VDD     | V                |

| RdnL_x    | External pull down resistance pin forced low |               |     | 10            | kΩ               |

|           | Power Good and OK Inputs                     | /Outputs      |     |               |                  |

| lup_PG    | Pull-up current source V(PG)=0               | 25            |     | 110           | μΑ               |

| lup_OK    | Pull-up current source V(OK)=0               | 175           |     | 725           | μΑ               |

| ViL_x     | LOW level input voltage                      | -0.5          |     | 0.3 x VDD     | V                |

| ViH_x     | HIGH level input voltage                     | 0.7 x VDD     |     | VDD+0.5       | V                |

| Vhyst_x   | Hysteresis of input Schmitt trigger          | 0.1 x VDD     |     | 0.3 x VDD     | V                |

| loL_x     | LOW level sink current at 0.5V               | 4             |     | 20            | mA               |

|           | Current Share/Sense E                        | Bus           |     |               |                  |

| lup_CS    | Pull-up current source at V(CS)=0V           | 0.84          |     | 3.10          | mA               |

| ViL_CS    | LOW level input voltage                      | -0.5          |     | 0.3 x VDD     | V                |

| ViH_CS    | HIGH level input voltage                     | 0.75 x<br>VDD |     |               | V                |

| Vhyst_CS  | Hysteresis of input Schmitt trigger          | 0.25 x<br>VDD |     | 0.45 x<br>VDD | V                |

| loL_CS    | LOW level sink current V(CS)=0.5V            | 14            |     | 60            | mA               |

| Tr_CS     | Maximum allowed rise time 10/90% VDD         |               |     | 100           | ns               |

## 5. Typical Performance Characteristics

Figure 1. Output Voltage as a Function of Input Voltage

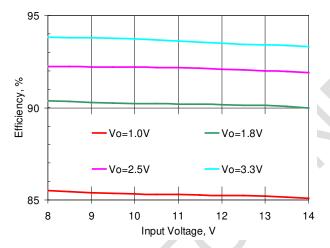

## 5.1 Efficiency Curves

Figure 2. Efficiency vs. Load. Vin=9.6V

Figure 3. Efficiency vs. Load. Vin=12V

Figure 4. Efficiency vs. Output Voltage, lout=40A

Figure 5. Efficiency vs. Input Voltage. Iout=40A

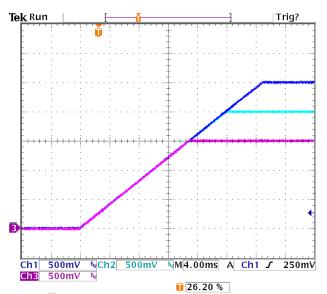

### 5.2 Turn-On Characteristics

Figure 6. Tracking Turn-On. Vin=12V, Ch1 – V1, Ch2 – V2, Ch3 – V3

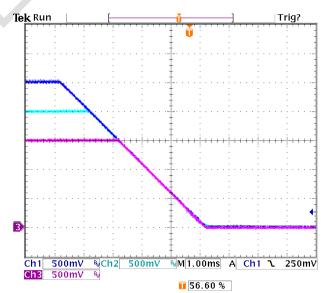

## 5.3 Turn-Off Characteristics

Figure 7. Tracking Turn-Off

Vin=12V, Ch1 - V1, Ch2 - V2, Ch3 - V3

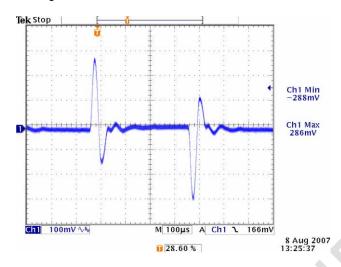

## 5.4 Transient Response

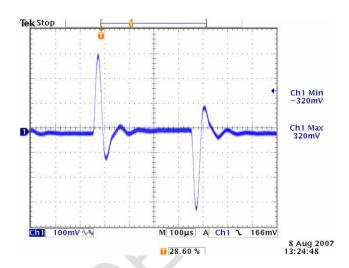

The pictures below show the deviation of the output voltage in response to the 50%-75%-50% step load at 1.0A/ $\mu$ s. In all tests the POL converter had a total of 380 $\mu$ F ceramic and tantalum capacitors connected across the output pins. The speed of the transient response was varied by selecting different CCA settings.

Figure 8. Vin=12V, Vout=3.3V. CCA=1

Figure 9. Vin=12V, Vout=3.3V. CCA=0

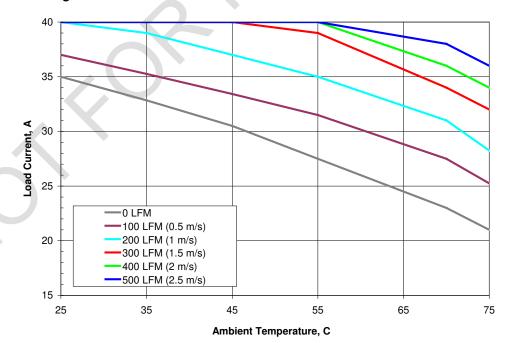

## 5.5 Thermal Derating Curve

Figure 10. Thermal Derating Curves. Vin=12V, Vout=3.3V

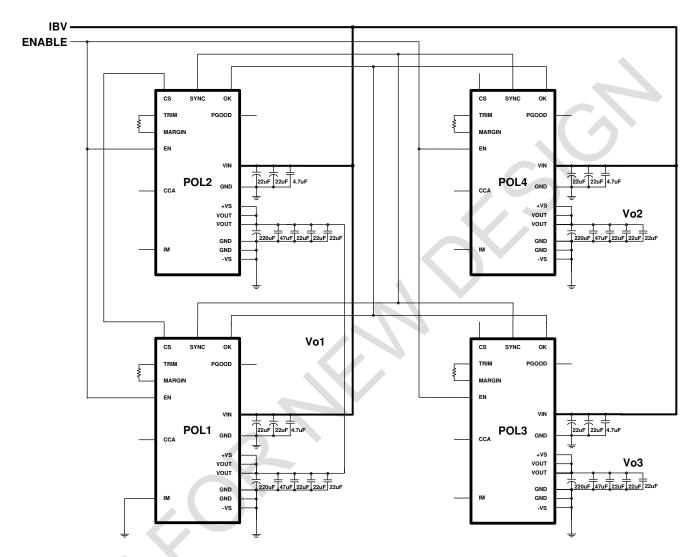

## 6. Typical Application

Figure 11. Complete Schematic of Application with Three Independent Outputs. Intermediate Bus Voltage is from 8V to 14V.

In this application four POL converters are configured to deliver three independent output voltages. POL1 and POL2 are connected in parallel for increased output current. Output voltages are programmed with the resistors connected between TRIM and MARGIN pins of individual converters.

POL1 is configured as a master (IM pin is grounded) and all other POL converters are synchronized to the switching frequency of POL1.

All converters are controlled by the common ENABLE signal. Turn-on and turn-off processes of the system are illustrated by pictures in Figure 6 and Figure 7.

## 7. Pin Assignments and Description

| Pin<br>Name | Pin<br>Number | Pin<br>Type | Buffer<br>Type | Pin Description                   | Notes                                                                                          |

|-------------|---------------|-------------|----------------|-----------------------------------|------------------------------------------------------------------------------------------------|

| OK          | 6             | I/O         | PU             | Fault Status                      | Connect to OK pin of other Z- POLs. Leave open, if not used                                    |

| SYNC        | 4             | I/O         | PU             | Frequency Synchronization<br>Line | Connect to SYNC pin of other Z-POLs or to an external clock generator                          |

| PGOOD       | 11            | I/O         | PU             | Power Good                        |                                                                                                |

| CS          | 3             | I/O         | PU             | Current Share/Sense               | Connect to CS pin of other Z-POLs connected in parallel                                        |

| IM          | 9             | 1           | PU             | Master Mode                       | Tie to GND to make the POL the clock master or leave open to synchronize to external clock     |

| CCA         | 10            | I           | PU             | Compensation Coefficient Address  | Tie to GND for 0 or leave open for 1                                                           |

| MARGIN      | 8             | Α           |                | Output Voltage Margining          | To program the output voltage, connect a resistor between MARGIN and TRIM                      |

| EN          | 5             | I           | PU             | Enable                            | POL is ON when the pin is high or floating. POL is OFF when the pin is low or connected to GND |

| TRIM        | 7             | Α           |                | Output Voltage Trim               | To program the output voltage, connect a resistor between MARGIN and TRIM                      |

| -VS         | 18            | 1           | Α              | Negative Voltage Sense            | Connect to the negative point close to the load                                                |

| +VS         | 15            | I           | Α              | Positive Voltage Sense            | Connect to the positive point close to the load                                                |

| VOUT        | 12, 13        | Р           |                | Output Voltage                    |                                                                                                |

| GND         | 2, 16, 17     | Р           |                | Power Ground                      |                                                                                                |

| VIN         | 1             | Р           |                | Input Voltage                     |                                                                                                |

Legend: I=input, O=output, I/O=input/output, P=power, A=analog, PU=internal pull-up

## 8. Pin and Feature Description

#### 8.1 OK, Fault Status

The open drain input/output with the internal pull-up resistor. The POL converter pulls its OK pin low, if a fault occurs. Pulling low the OK input by an external circuitry turns off the POL converter.

## 8.2 SYNC, Frequency Synchronization Line

The bidirectional input/output with the internal pull-up resistor. If the POL converter is configured as a master, the SYNC line propagates clock to other POL converters. If the POL converter is configured as a slave, the internal clock recovery circuit synchronizes the POL converter to the clock of the SYNC line.

#### 8.3 IM, Interleave Mode

The input with the internal pull-up resistor. When the pin is left floating, the switching frequency is determined by an external clock applied to the SYNC pin. Pulling the IM pin low configures a POL converter as a master. The master determines the clock on the SYNC line.

## 8.4 PG, Power Good

The open drain input/output with the internal pull-up resistor. The pin is pulled low by the POL converter, if the output voltage is outside of the window defined by the Power Good High and Low thresholds.

### 8.5 CCA, Compensation Coefficient Address

Inputs with internal pull-ups to select one of 2 sets of digital filter coefficients optimized for different characteristics of output capacitance.

#### 8.6 CS. Current Share/Sense Bus

The open drain digital input/output with the internal pull-up resistor. The duty cycle of the digital signal is proportional to the output current of the POL converter. External capacitive loading of the pin shall be avoided.

### 8.7 MARGIN, Output Voltage Margining

The output of the 2V internal voltage reference that is used to program the output voltage of the POL converter.

### 8.8 TRIM, Output Voltage Trim

The input of the TRIM comparator for the output voltage programming.

The output voltage is programmed by a single resistor connected between MARGIN and TRIM pins.

### 8.9 EN, Enable

The input with the internal pull-up resistor. The POL converter is turned off, when the pin is pulled low

#### 8.10 -VS and +VS

The differential voltage input of the POL converter feedback loop.

## 9. Application Information

### 9.1 Output Voltage Programming

Resistance of the trim resistor is determined from the equation below:

$$R_{TRIM} = \frac{20 \times (5.5 - V_{OUT})}{V_{OUT}}, \text{ k}\Omega$$

where  $V_{\text{OUT}}$  is the desired output voltage in Volts.

If the  $R_{TRIM}$  is open or the TRIM pin is shorted to PGND, the  $V_{OUT}$ =0.5V.

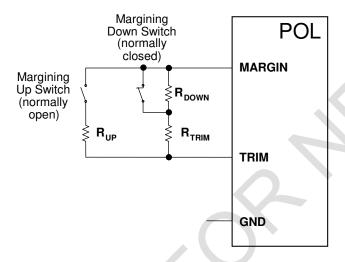

## 9.2 Output Voltage Margining

Margining can be implemented by changing the resistance between the REF and TRIM pins.

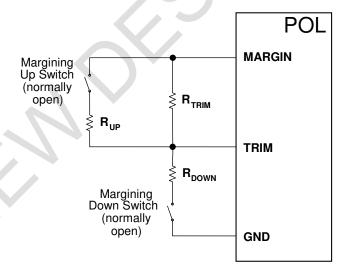

Figure 12. Margining Configuration

In the schematic shown in Figure 12, the nominal output voltage is set with the trim resistor  $R_{\text{TRIM}}$  calculated from the equation in the paragraph 9.1. Resistors  $R_{\text{UP}}$  and  $R_{\text{DOWN}}$  are added to margin the output voltage up and down respectively and determined from the equations below.

$$R_{UP} = \frac{20 \times R_{TRIM}}{20 + R_{TRIM}} \times \left( \frac{5 \times R_{TRIM} - \Delta V\%}{\Delta V\%} \right), \text{ k}\Omega$$

$$R_{DOWN} = (20 + R_{TRIM}) \times \left(\frac{\Delta V\%}{100 - \Delta V\%}\right), \text{ k}\Omega$$

where  $R_{TRIM}$  is the value of the trim resistor in  $k\Omega$  and  $\Delta V\%$  is the absolute value of desired margining expressed in percents of the nominal output voltage.

During normal operation the resistors are removed from the circuit by the switches. The "Margining Down" switch is normally closed shorting the resistor  $R_{\text{DOWN}}$  while the "Margining Up" switch is normally open disconnecting the resistor  $R_{\text{UP}}$ .

An alternative configuration of the margining circuit is shown in Figure 13. In the configuration both switches are normally open that may be advantageous in some implementations.

Figure 13. Alternative Margining Configuration

$R_{\text{UP}}$  and  $R_{\text{DOWN}}$  for this configuration are determined from the following equations:

$$R_{UP} = \frac{20 \times R_{TRIM}}{20 + R_{TRIM}} \times \left( \frac{5 \times R_{TRIM} - \Delta V\%}{\Delta V\%} \right), k\Omega$$

$$R_{DOWN} = \frac{20 \times R_{TRIM}}{20 + R_{TRIM}} \times \left(\frac{100 - \Delta V\%}{\Delta V\%}\right), k\Omega$$

Caution: Noise injected into the TRIM node may affect accuracy of the output voltage and stability of the POL converter. Always minimize the PCB trace length from the TRIM pin to external components to avoid noise pickup.

Refer to *No-Bus<sup>TM</sup> POL Converters. Application Note* on <a href="https://www.power-one.com">www.power-one.com</a> for more application information on this and other product features.

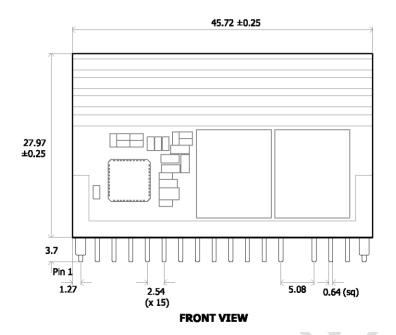

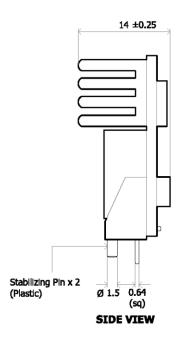

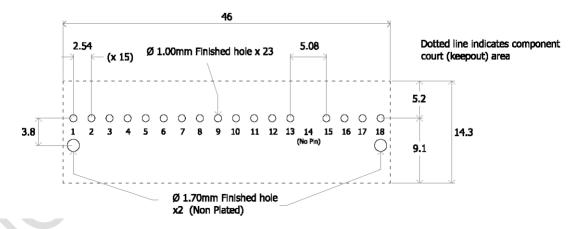

## 10. Mechanical Drawings

#### All Dimensions are in mm

Tolerances: XX.X: ±0.1 XX.XX: ±0.05

Figure 14. Mechanical Drawing

Figure 15. Recommended Footprint - Top View

### Notes:

- 1. NUCLEAR AND MEDICAL APPLICATIONS Power-One products are not designed, intended for use in, or authorized for use as critical components in life support systems, equipment used in hazardous environments, or nuclear control systems without the express written consent of the respective divisional president of Power-One, Inc.

- 2. TECHNICAL REVISIONS The appearance of products, including safety agency certifications pictured on labels, may change depending on the date manufactured. Specifications are subject to change without notice.