# Isolated High-Speed CAN Transceiver

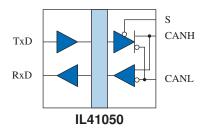

#### **Functional Diagram**

| V <sub>DD2</sub> (V)     | $\mathbf{Tx}\mathbf{D}^{(1)}$ | S                  | CANH                                                                                      | CANL                                                     | Bus State | RxD  |

|--------------------------|-------------------------------|--------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------|------|

| 4.75 to 5.25             | $\downarrow$                  | Low <sup>(2)</sup> | High                                                                                      | Low                                                      | Dominant  | Low  |

| 4.75 to 5.25             | Х                             | High               | $V_{DD2}/2$                                                                               | V <sub>DD2</sub> /2                                      | Recessive | High |

| 4.75 to 5.25             | ↑                             | Х                  | $V_{DD2}/2$                                                                               | V <sub>DD2</sub> /2                                      | Recessive | High |

| <2V (no pwr)             | Х                             | Х                  | 0 <v<2.5< td=""><td>0<v<2.5< td=""><td>Recessive</td><td>High</td></v<2.5<></td></v<2.5<> | 0 <v<2.5< td=""><td>Recessive</td><td>High</td></v<2.5<> | Recessive | High |

| 2>V <sub>DD2</sub> <4.75 | >2V                           | Х                  | 0 <v<2.5< td=""><td>0<v<2.5< td=""><td>Recessive</td><td>High</td></v<2.5<></td></v<2.5<> | 0 <v<2.5< td=""><td>Recessive</td><td>High</td></v<2.5<> | Recessive | High |

Table 1. Function table.

#### Notes:

- 1. TxD input is edge triggered:  $\uparrow$  = Logic Lo to Hi,  $\downarrow$  = Hi to Lo

- 2. Valid for logic state as described or open circuit

X = don't care

#### Features

- Single-chip isolated CAN/DeviceNet transceiver

- Fully compliant with the ISO 11898 CAN standard

- Best-in-class loop delay (180 ns typ.)

- 3.0 V to 5.5 V input power supplies

- >110-node fan-out

- High speed (up to 1 Mbps)

- 2,500 V<sub>RMS</sub> isolation (1 minute)

- Very low Electromagnetic Emission (EME)

- Differential signaling for excellent Electromagnetic Immunity (EMI)

- 30 kV/µs transient immunity

- Silent mode to disable transmitter

- Unpowered nodes do not disturb the bus

- Transmit data (TxD) dominant time-out function

- · Edge triggered, non-volatile input improves noise performance

- · Bus pin transient protection for automotive environment

- Thermal shutdown protection

- · Short-circuit protection for ground and bus power

- -55°C to +125°C operating temperature

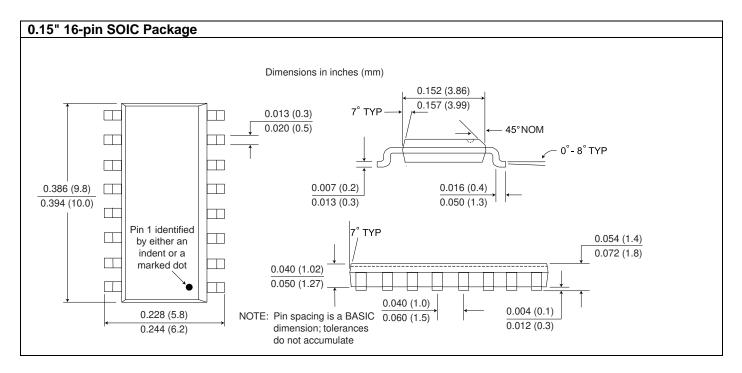

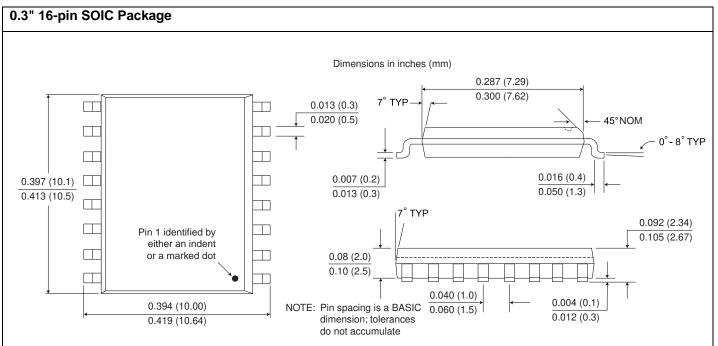

- 0.15" and 0.3" and 16-pin JEDEC-standard SOIC packages

- UL1577 and IEC 61010-2001 approved

#### **Applications**

- Noise-critical CAN

- · Partially-powered CAN

- DeviceNet

- · Factory automation

#### **Description**

The IL41050 is a galvanically isolated, high-speed CAN (Controller Area Network) transceiver, designed as the interface between the CAN protocol controller and the physical bus. The IL41050 provides isolated differential transmit capability to the bus and isolated differential receive capability to the CAN controller via NVE's patented\* IsoLoop spintronic Giant Magnetoresistance (GMR) technology.

Advanced features facilitate reliable bus operation. Unpowered nodes do not disturb the bus, and a unique non-volatile programmable power-up feature prevents unstable nodes. The devices also have a hardware-selectable silent mode that disables the transmitter.

Designed for harsh CAN and DeviceNet environments, IL41050T transceivers have transmit data dominant time-out, bus pin transient protection, thermal shutdown protection, and short-circuit protection, Unique edge-triggered inputs improve noise performance. Unlike optocouplers or other isolation technologies, IsoLoop isolators have indefinite life at high voltage.

IsoLoop<sup>®</sup> is a registered trademark of NVE Corporation. \*U.S. Patent number 5,831,426; 6,300,617 and others.

# Absolute Maximum Ratings<sup>(1) (2)</sup>

| Parameters                          | Symbol                            | Min.   | Тур. | Max.           | Units | Test Conditions                                  |

|-------------------------------------|-----------------------------------|--------|------|----------------|-------|--------------------------------------------------|

| Storage temperature                 | Ts                                | -55    |      | 150            | °C    |                                                  |

| Ambient operating temperature       | T <sub>A</sub>                    | -55    |      | 135            | °C    |                                                  |

| DC voltage at CANH and CANL pins    | $V_{\text{CANH}} V_{\text{CANL}}$ | -27    |      | 40             | V     | $0 V < V_{DD2} < 5.25 V;$<br>indefinite duration |

| Supply voltage                      | $V_{DD1}, V_{DD2}$                | -0.5   |      | 6              | V     |                                                  |

| Digital input voltage               | $V_{TxD}, V_S$                    | -0.3   |      | $V_{DD} + 0.3$ | V     |                                                  |

| Digital output voltage              | V <sub>RxD</sub>                  | -0.3   |      | $V_{DD} + 0.3$ | V     |                                                  |

| DC voltage at V <sub>REF</sub>      | V <sub>REF</sub>                  | -0.3   |      | $V_{DD} + 0.3$ | V     |                                                  |

| Transient Voltage at CANH or CANL   | V <sub>trt(CAN)</sub>             | -200   |      | 200            | V     |                                                  |

| Electrostatic discharge at all pins | V <sub>esd</sub>                  | -4,000 |      | 4,000          | V     | Human body model                                 |

| Electrostatic discharge at all pins | V <sub>esd</sub>                  | -200   |      | 200            | V     | Machine model                                    |

# **Recommended Operating Conditions**

| Parameters                                                    | Symbol                                 | Min.              | Тур. | Max.                                                              | Units | Test Conditions                                             |

|---------------------------------------------------------------|----------------------------------------|-------------------|------|-------------------------------------------------------------------|-------|-------------------------------------------------------------|

| Supply voltage                                                | $V_{ m DD1} \ V_{ m DD2}$              | 3.0<br>4.75       |      | 5.5<br>5.25                                                       | v     |                                                             |

| Input voltage at any bus terminal (separately or common mode) | V <sub>CANH</sub><br>V <sub>CANL</sub> | -12               |      | 12                                                                | V     |                                                             |

| High-level digital input voltage <sup>(3) (4)</sup>           | $V_{IH}$                               | 2.0<br>2.4<br>2.0 |      | $egin{array}{c} V_{ m DD1} \ V_{ m DD1} \ V_{ m DD2} \end{array}$ | V     | $V_{DD1} = 3.3 V$<br>$V_{DD1} = 5.0 V$<br>$V_{DD2} = 5.0 V$ |

| Low-level digital input voltage <sup>(3) (4)</sup>            | V <sub>IL</sub>                        | 0                 |      | 0.8                                                               | V     |                                                             |

| Digital output current (RxD)                                  | I <sub>OH</sub>                        | -8                |      | 8                                                                 | mA    | $V_{DD1} = 3.3V$ to 5V                                      |

| Ambient operating temperature                                 | T <sub>A</sub>                         | -55               |      | 125                                                               | °C    |                                                             |

| Digital input signal rise and fall times                      | t <sub>IR</sub> , t <sub>IF</sub>      |                   |      | 1                                                                 | μs    |                                                             |

# **Insulation Specifications**

| Parameters                   | Symbol | Min. | Тур.                    | Max. | Units         | Test Conditions              |

|------------------------------|--------|------|-------------------------|------|---------------|------------------------------|

| Creepage distance (external) |        | 8.08 |                         |      | mm            |                              |

| Barrier impedance            |        |      | $> 10^{14} \parallel 7$ |      | Ω    pF       |                              |

| Leakage current              |        |      | 0.2                     |      | $\mu A_{RMS}$ | 240 V <sub>RMS</sub> , 60 Hz |

# Safety and Approvals

# IEC61010-2001

TUV Certificate Numbers:

N1502812 (pending)

#### **Classification: Reinforced Insulation**

| Model   | Package               | Pollution Degree | Material Group | Max. Working Voltage |

|---------|-----------------------|------------------|----------------|----------------------|

| IL41050 | SOIC (0.15" and 0.3") | II               | III            | $300 V_{RMS}$        |

#### UL 1577

Component Recognition Program File Number: E207481 Rated  $2,500V_{RMS}$  for 1 minute

# Soldering Profile

Per JEDEC J-STD-020C Moisture Sensitivity Level: MSL=2

#### Notes:

1. Absolute Maximum specifications mean the device will not be damaged if operated under these conditions. It does not guarantee performance.

- 2. All voltages are with respect to network ground except differential I/O bus voltages.

- 3. The TxD input is edge sensitive. Voltage magnitude of the input signal is specified, but edge rate specifications must also be met.

- 4. The maximum time allowed for a logic transition at the TxD input is 1  $\mu$ s.

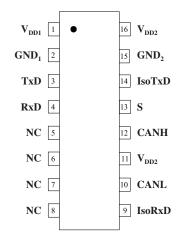

# IL41050-3 Pin Connections (0.15" SOIC Package)

| 1  | V <sub>DD1</sub> | V <sub>DD1</sub> power supply input                                                      |

|----|------------------|------------------------------------------------------------------------------------------|

| 2  | $GND_1$          | V <sub>DD1</sub> power supply ground return                                              |

| 3  | ΤD               | Transmit Data input                                                                      |

| 4  | RxD              | Receive Data output                                                                      |

| 5  | NC               | No internal connection                                                                   |

| 6  | NC               | No internal connection                                                                   |

| 7  | NC               | No internal connection                                                                   |

| 8  | NC               | No internal connection                                                                   |

| 9  | IsoRxD           | Isolated RxD output.<br>No connection should be made to this pin.                        |

| 10 | CANL             | Low level CANbus line                                                                    |

| 11 | V <sub>DD2</sub> | V <sub>DD2</sub> CAN I/O bus circuitry power supply input*                               |

| 12 | CANH             | High level CANbus line                                                                   |

| 13 | S                | Mode select input. Leave open or set low for normal operation; set high for silent mode. |

| 14 | IsoTxD           | Isolated TxD output.<br>No connection should be made to this pin.                        |

| 15 | GND <sub>2</sub> | V <sub>DD2</sub> power supply ground return                                              |

| 16 | V <sub>DD2</sub> | V <sub>DD2</sub> isolation power supply input*                                           |

|    |                  |                                                                                          |

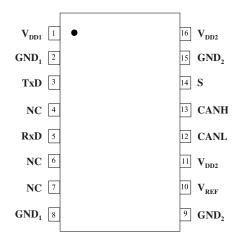

# IL41050 Pin Connections (0.3" SOIC Package)

| 1  | V <sub>DD1</sub> | V <sub>DD1</sub> power supply input                                                      |

|----|------------------|------------------------------------------------------------------------------------------|

| 2  | GND <sub>1</sub> | V <sub>DD1</sub> power supply ground return<br>(pin 2 is internally connected to pin 8)  |

| 3  | TxD              | Transmit Data input                                                                      |

| 4  | NC               | No internal connection                                                                   |

| 5  | RxD              | Receive Data output                                                                      |

| 6  | NC               | No internal connection                                                                   |

| 7  | NC               | No internal connection                                                                   |

| 8  | $GND_1$          | V <sub>DD1</sub> power supply ground return<br>(pin 8 is internally connected to pin 2)  |

| 9  | GND <sub>2</sub> | V <sub>DD2</sub> power supply ground return<br>(pin 9 is internally connected to pin 15) |

| 10 | V <sub>REF</sub> | Reference voltage output<br>(nominally 50% of V <sub>DD2</sub> )                         |

| 11 | V <sub>DD2</sub> | V <sub>DD2</sub> CAN I/O bus circuitry power supply input*                               |

| 12 | CANL             | Low level CANbus line                                                                    |

| 13 | CANH             | High level CANbus line                                                                   |

| 14 | S                | Mode select input. Leave open or set low for normal operation; set high for silent mode. |

| 15 | GND <sub>2</sub> | V <sub>DD2</sub> power supply ground return<br>(pin 15 is internally connected to pin 9) |

| 16 | V <sub>DD2</sub> | V <sub>DD2</sub> isolation power supply input*                                           |

\*NOTE: Pin 11 is not internally connected to pin 16; both should be connected to the V<sub>DD2</sub> power supply for normal operation.

**Specifications** Electrical Specifications are T<sub>min</sub> to T<sub>n</sub> and V.  $V_{DD2} = 4.75 \text{ V}$  to 5.25 V unless otherwise stated

| Electrical Specifications are $T_{min}$ to $T_{max}$ and <b>Parameters</b> | Symbol                     | Min.           | Тур.          | Max.            | Units | Test Conditions                                                                             |

|----------------------------------------------------------------------------|----------------------------|----------------|---------------|-----------------|-------|---------------------------------------------------------------------------------------------|

| Power Supply Current                                                       | *                          |                | <i></i>       |                 |       | 1                                                                                           |

|                                                                            | 10                         | 1              | 1.75          | 3.0             |       | $dr = 0$ bps; $V_{DD1} = 5$ V                                                               |

| Quiescent supply current (recessive)                                       | IQ <sub>VDD1</sub>         | 0.7            | 1.4           | 2.0             | mA    | $dr = 0$ bps; $V_{DD1} = 3.3$ V                                                             |

|                                                                            |                            | 1.2            | 2.0           | 2.2             |       | $dr = 1$ Mbps, $R_L = 60\Omega$ ;                                                           |

| Dynamia supply surrant (dominant)                                          | т                          | 1.2            | 2.0           | 3.2             | m A   | $V_{DD1} = 5 V$                                                                             |

| Dynamic supply current (dominant)                                          | I <sub>VDD1</sub>          | 0.9            | 1.6           | 2.2             | mA    | $dr = 1$ Mbps, $R_L = 60\Omega$ ;                                                           |

|                                                                            |                            | 0.9            | 1.0           | 2.2             |       | $V_{DD1} = 3.3 V$                                                                           |

| Quiescent supply current (recessive)                                       | IQ <sub>VDD2</sub>         | 3.5            | 6.75          | 13              | mA    | 0 bps                                                                                       |

| Dynamic supply current (dominant)                                          | I <sub>VDD2</sub>          | 26             | 52            | 78              | IIIA  | 1 Mbps, $R_L = 60\Omega$                                                                    |

| Transmitter Data input (TxD) <sup>(1)</sup>                                |                            |                |               |                 |       |                                                                                             |

| High level input voltage ↑                                                 | V <sub>IH</sub>            | 2.4            |               | 5.25            | V     | $V_{DD1} = 5 V$ ; recessive                                                                 |

| High level input voltage ↑                                                 | V <sub>IH</sub>            | 2.0            |               | 3.6             | V     | $V_{DD1} = 3.3 \text{ V}$ ; recessive                                                       |

| Low level input voltage ↓                                                  | V <sub>IL</sub>            | -0.3           |               | 0.8             | V     | Output dominant                                                                             |

| TxD input rise and fall time <sup>(2)</sup>                                | tr                         |                |               | 1               | μs    | 10% to 90%tr                                                                                |

| High level input current                                                   | I <sub>IH</sub>            | -10            |               | 10              | μΑ    | $V_{TxD} = V_{DD1}$                                                                         |

| Low level input current                                                    | IL                         | 10             |               | 10              | μΑ    | $V_{TxD} = 0 V$                                                                             |

| Mode select input (S)                                                      | 1                          |                |               | -               |       | 1                                                                                           |

| High level input voltage                                                   | V <sub>IH</sub>            | 2.0            |               | $V_{DD2} + 0.3$ | V     | Silent mode                                                                                 |

| Low level input voltage                                                    | V <sub>IL</sub>            | -0.3           |               | 0.8             | V     | High-speed mode                                                                             |

| High level input current                                                   | I <sub>IH</sub>            | 20             | 30            | 45              | μΑ    | $V_{\rm S} = 2 \rm V$                                                                       |

| Low level input current                                                    | I <sub>IL</sub>            | 15             | 30            | 10              | μΑ    | $V_{\rm S} = 0  \rm V$                                                                      |

| Receiver Data output (RxD)                                                 |                            | -              |               |                 |       |                                                                                             |

| High level output current                                                  | I <sub>OH</sub>            | -2             | -8.5          | -20             | mA    | $V_{RxD} = 0.8 V_{DD1}$                                                                     |

| Low level output current                                                   | I <sub>OL</sub>            | 2              | 8.5           | 20              | mA    | $V_{RxD} = 0.45 V$                                                                          |

| Failsafe supply voltage <sup>(4)</sup>                                     | V <sub>DD2</sub>           | 3.6            |               | 3.9             | V     |                                                                                             |

| Reference Voltage output (V <sub>REF</sub> )                               |                            | 0.45.55        |               | 0.77.11         |       |                                                                                             |

| Reference Voltage output                                                   | V <sub>REF</sub>           | $0.45 V_{DD2}$ | $0.5 V_{DD2}$ | $0.55 V_{DD2}$  | V     | -50 μA <i<sub>VREF&lt; +50 μA</i<sub>                                                       |

| Bus lines (CANH and CANL)                                                  |                            | • •            |               |                 |       |                                                                                             |

| Recessive voltage at CANH pin                                              | V <sub>O(reces)</sub> CANH | 2.0            | 2.5           | 3.0             | V     | $V_{TxD} = V_{DD1}$ , no load                                                               |

| Recessive voltage at CANL pin                                              | V <sub>O(reces)</sub> CANL | 2.0            | 2.5           | 3.0             | V     | $V_{TxD} = V_{DD1}$ , no load                                                               |

| Recessive current at CANH pin                                              | IO(reces) CANH             | -2.0           |               | +2.5            | mA    | $-27 V < V_{CANH} < +32V;$                                                                  |

| -                                                                          |                            |                |               |                 |       | $\begin{array}{c} 0V < V_{DD2} < 5.25V \\ -27 V < V_{CANL} < +32V; \end{array}$             |

| Recessive current at CANL pin                                              | I <sub>O(reces)</sub> CANL | -2.0           |               | +2.5            | mA    |                                                                                             |

| Dominant voltage at CANH pin                                               | V CANH                     | 3.0            | 3.6           | 4.25            | V     | $0 V < V_{DD2} < 5.25 V$<br>$V_{TxD} = 0 V$                                                 |

| Dominant voltage at CANH pin                                               | V <sub>O(dom)</sub> CANH   | 0.5            | 1.4           | 4.23            | V     |                                                                                             |

| Dominant voltage at CANL pin                                               | V <sub>O(dom)</sub> CANL   | 0.5            | 1.4           | 1.75            |       | $V_{TxD} = 0 V$ $V_{TxD} = 0 V; \text{ dominant}$                                           |

| Differential bus input voltage                                             |                            | 1.5            | 2.25          | 3.0             | V     | $v_{\text{TxD}} = 0 \text{ v}$ , dominant<br>42.5 $\Omega \leq R_{\text{L}} \leq 60 \Omega$ |

| $(V_{CANH} - V_{CANL})$                                                    | V <sub>i(dif)(bus)</sub>   |                |               |                 |       | $V_{TxD} = V_{DD1};$                                                                        |

| (VCANH VCANL)                                                              |                            | -50            | 0             | +50             | mV    | $v_{TxD} - v_{DD1}$ ,<br>recessive; no load                                                 |

| Short-circuit output current at CANH                                       | I <sub>O(sc)</sub> CANH    | -45            | -70           | -95             | mA    | $V_{\text{CANH}} = 0 \text{ V},  V_{\text{TxD}} = 0$                                        |

| Short-circuit output current at CANL                                       | I <sub>O(sc)</sub> CANL    | 45             | 70            | 100             | mA    | $V_{CANL} = 36 V, V_{TxD} = 0$                                                              |

| *                                                                          |                            |                |               |                 |       | $-12 V < V_{CANL} < +12V;$                                                                  |

| Differential receiver threshold voltage                                    | V <sub>i(dif)(th)</sub>    | 0.5            | 0.7           | 0.9             | V     | $-12 V < V_{CANH} < +12 V$                                                                  |

| Differential receiver input voltage                                        |                            |                |               |                 |       | $-12 V < V_{CANL} < +12 V;$                                                                 |

| hysteresis                                                                 | V <sub>i(dif)(hys)</sub>   | 50             | 70            | 100             | mV    | $-12 \text{ V} < \text{V}_{\text{CANH}} < +12 \text{ V}$                                    |

| Common Mode input resistance at                                            | _                          |                |               |                 |       | CANIT                                                                                       |

| CANH                                                                       | R <sub>i(CM)(CANH)</sub>   | 15             | 25            | 35              | kΩ    |                                                                                             |

| Common Mode input resistance at                                            | D                          | 1.5            | 25            | 25              | 1.0   |                                                                                             |

| CANL                                                                       | R <sub>i(CM)(CANL)</sub>   | 15             | 25            | 35              | kΩ    |                                                                                             |

| Matching between Common Mode                                               | P                          | 2              | <u>^</u>      |                 | A     | ¥7 ¥7                                                                                       |

| input resistance at CANH, CANL                                             | R <sub>i(CM)(m)</sub>      | -3             | 0             | +3              | %     | $V_{CANL} = V_{CANH}$                                                                       |

| Differential input resistance                                              | R <sub>i(diff)</sub>       | 25             | 50            | 75              | kΩ    |                                                                                             |

|                                                                            |                            |                | 7.5           | 20              | pF    | $V_{TxD} = V_{DD1}$                                                                         |

| Input capacitance, CANH                                                    | C <sub>i(CANH)</sub>       |                | 1.5           | 20              | рг    | $\mathbf{v}_{\mathrm{TxD}} - \mathbf{v}_{\mathrm{DD1}}$                                     |

# Specifications (...cont.)

| Electrical specifications are $T_{min}$ to $T_{max}$ and $V_{DD1}$ , $V_{DD2}$ = 4.5 V to 5.5 V unless otherwise stated. |                            |     |      |     |     |                                                         |  |  |

|--------------------------------------------------------------------------------------------------------------------------|----------------------------|-----|------|-----|-----|---------------------------------------------------------|--|--|

| Differential input capacitance                                                                                           | C <sub>i(dif)</sub>        |     | 3.75 | 10  | pF  | $V_{TxD} = V_{DD1}$                                     |  |  |

| Input leakage current at CANH                                                                                            | I <sub>LI(CANH)</sub>      | 100 | 170  | 250 | μΑ  | $V_{CANH} = 5 V, V_{DD2} = 0 V$                         |  |  |

| Input leakage current at CANL                                                                                            | I <sub>LI(CANL)</sub>      | 100 | 170  | 250 | μΑ  | $V_{CANL} = 5 V, V_{DD2} = 0 V$                         |  |  |

| Thermal Shutdown                                                                                                         |                            |     |      |     |     |                                                         |  |  |

| Shutdown junction temperature                                                                                            | T <sub>i(SD)</sub>         | 155 | 165  | 180 | °C  |                                                         |  |  |

| Timing Characteristics                                                                                                   |                            |     |      |     |     |                                                         |  |  |

| TxD to bus active delay                                                                                                  | t                          | 29  | 63   | 125 | 20  | $V_{\rm S} = 0 \text{ V}; V_{\rm DD1} = 5 \text{ V}$    |  |  |

| TXD to bus active delay                                                                                                  | t <sub>d(TxD-BUSon)</sub>  | 32  | 66   | 128 | ns  | $V_{\rm S} = 0 \text{ V}; V_{\rm DD1} = 3.3 \text{ V}$  |  |  |

| TxD to bus inactive delay                                                                                                | t <sub>d(TxD-BUSoff)</sub> | 29  | 68   | 110 | ns  | $V_{S} = 0 V; V_{DD1} = 5 V$                            |  |  |

| TXD to bus mactive delay                                                                                                 |                            | 32  | 71   | 113 |     | $V_{\rm S} = 0 \text{ V}; V_{\rm DD1} = 3.3 \text{ V}$  |  |  |

| Bus active to RxD delay                                                                                                  | t                          | 24  | 58   | 125 | ns  | $V_{\rm S} = 0 \text{ V}; V_{\rm DD1} = 5 \text{ V}$    |  |  |

| Bus active to KXD delay                                                                                                  | t <sub>d(BUSon-RxD)</sub>  | 27  | 61   | 128 | 115 | $V_{\rm S} = 0 \text{ V}; V_{\rm DD1} = 3.3 \text{ V}$  |  |  |

| Bus inactive to RxD delay                                                                                                | t                          | 49  | 103  | 170 | ns  | $V_{\rm S} = 0 \text{ V}; V_{\rm DD1} = 5 \text{ V}$    |  |  |

| Bus macrive to KXD delay                                                                                                 | t <sub>d(BUSoff-RxD)</sub> | 52  | 106  | 173 | ns  | $V_{\rm S} = 0 \text{ V}; V_{\rm DD1} = 3.3 \text{ V}$  |  |  |

| Loop delay low-to-high or high-to-low                                                                                    | T <sub>LOOP</sub>          | 53  | 180  | 210 | ns  | $V_{\rm S} = 0 \ \rm V$                                 |  |  |

| TxD dominant time for timeout                                                                                            | т                          | 250 | 457  | 765 |     | $V_{TxD} = 0 V$                                         |  |  |

| TXD dominant time for timeout                                                                                            | T <sub>dom(TxD)</sub>      | 250 | 437  | 705 | μs  | $3.0 \text{ V} > \text{V}_{\text{DD1}} < 5.5 \text{ V}$ |  |  |

Electrical Specifications are  $T_{min}$  to  $T_{max}$  and  $V_{DD1}$ ,  $V_{DD2}$ = 4.5 V to 5.5 V unless otherwise stated.

# Magnetic Field Immunity<sup>(3)</sup>

| $\mathbf{V}_{\mathrm{DD1}} = 5 \mathrm{V},  \mathbf{V}_{\mathrm{DD2}} = 5 \mathrm{V}$ |                                                  |       |       |  |     |                   |  |  |

|---------------------------------------------------------------------------------------|--------------------------------------------------|-------|-------|--|-----|-------------------|--|--|

| Power frequency magnetic immunity                                                     | H <sub>PF</sub>                                  | 2,500 | 3,000 |  | A/m | 50 Hz/60 Hz       |  |  |

| Pulse magnetic field immunity                                                         | H <sub>PM</sub>                                  | 3,000 | 3,500 |  | A/m | $t_p = 8 \ \mu s$ |  |  |

| Cross-axis immunity multiplier                                                        | K <sub>X</sub>                                   |       | 1.8   |  |     | Figure 1          |  |  |

|                                                                                       | $V_{DD1} = 3.3 \text{ V}, V_{DD2} = 5 \text{ V}$ |       |       |  |     |                   |  |  |

| Power frequency magnetic immunity                                                     | H <sub>PF</sub>                                  | 1,000 | 1,500 |  | A/m | 50 Hz/60 Hz       |  |  |

| Pulse magnetic field immunity                                                         | H <sub>PM</sub>                                  | 1,800 | 2,000 |  | A/m | $t_p = 8 \ \mu s$ |  |  |

| Cross-axis immunity multiplier                                                        | K <sub>X</sub>                                   |       | 1.5   |  |     | Figure 1          |  |  |

#### Notes:

1. The TxD input is edge sensitive. Voltage magnitude of the input signal is specified, but edge rate specifications must also be met.

2. The maximum time allowed for a logic transition at the TxD input is 1 µs.

3. Uniform magnetic field applied across the pins of the device. Cross-axis multiplier effective when field is applied perpendicular to the pins.

4. If  $V_{DD2}$  falls below the specified failsafe supply voltage, RxD will go High.

# Electrostatic Discharge Sensitivity

This product has been tested for electrostatic sensitivity to the limits stated in the specifications. However, NVE recommends that all integrated circuits be handled with appropriate care to avoid damage. Damage caused by inappropriate handling or storage could range from performance degradation to complete failure.

# Electromagnetic Compatibility

The IL41050 is fully compliant with generic EMC standards EN50081, EN50082-1 and the umbrella line-voltage standard for Information Technology Equipment (ITE) EN61000. The IsoLoop Isolator's Wheatstone bridge configuration and differential magnetic field signaling ensure excellent EMC performance against all relevant standards. NVE conducted compliance tests in the categories below:

#### EN50081-1

Residential, Commercial & Light Industrial Methods EN55022, EN55014 EN50082-2: Industrial Environment Methods EN61000-4-2 (ESD), EN61000-4-3 (Electromagnetic Field Immunity), EN61000-4-4 (Electrical Transient Immunity), EN61000-4-6 (RFI Immunity), EN61000-4-8 (Power Frequency Magnetic Field Immunity), EN61000-4-9 (Pulsed Magnetic Field), EN61000-4-10 (Damped Oscillatory Magnetic Field)

ENV50204

Radiated Field from Digital Telephones (Immunity Test)

Immunity to external magnetic fields is higher if the field direction is "end-to-end" (rather than to "pin-to-pin") as shown in the diagram at right.

Both  $V_{DD2}$  power supply inputs (pins 11 and 16) must be connected to the bus-side power supply. Pin 11 powers the bus side of the CAN I/O circuitry, while pin 16 powers the bus-side isolation circuitry. For testing purposes, they are not internally connected, but the part will not operate without both pins powered, and operation without both pins powered can cause damage.

IL41050

# **Power Supply Decoupling**

Both  $V_{DD1}$  and  $V_{DD2}$  must be bypassed with 100 nF ceramic capacitors. These supply the dynamic current required for the isolator switching and should be placed as close as possible to  $V_{DD}$  and their respective ground return pins.

#### Input Configurations

The TxD input should not be left open as the state will be indeterminate. If connected to an open-drain or open collector output, a pull-up resistor (typically 16 k $\Omega$ ) should be connected from the input to V<sub>DD1</sub>.

The Mode Select ("S") input has a nominal 150 k $\Omega$  internal pull-down resistor. It can be left open or set low for normal operation.

# **Dominant Mode Time-out and Failsafe Receiver Functions**

CAN bus latch up is prevented by an integrated Dominant mode timeout function. If the TxD pin is forced permanently low by hardware or software application failure, the time-out returns the RxD output to the high state no more than 765  $\mu$ s after TxD is asserted dominant. The timer is triggered by a negative edge on TxD. If the duration of the low is longer than the internal timer value, the transmitter is disabled, driving the bus to the recessive state. The timer is reset by a positive edge on pin TxD.

If power is lost on Vdd2, the IL41050 asserts the RxD output high when the supply voltage falls below 3.8 V. RxD will return to normal operation as soon as Vdd2 rises above approximately 4.2 V.

# **Programmable Power-Up**

A unique non-volatile programmable power-up feature prevents unstable nodes. A state that needs to be present at node power up can be programmed at the last power down. For example if a CAN node is required to "pulse" dominant at power up, TxD can be sent low by the controller immediately prior to power down. When power is resumed, the node will immediately go dominant allowing self-check code in the microcontroller to verify node operation. If desired, the node can also power up silently by presetting the TxD line high at power down. At the next power on, the IL41050 will remain silent, awaiting a dominant state from the bus.

The microcontroller can check that the CAN node powered down correctly before applying power at the next "power on" request. If the node powered down as intended, RxD will be set high and stored in IL41050's non-volatile memory. The level stored in the RxD bit can be read before isolated node power is enabled, avoiding possible CAN bus disruption due to an unstable node.

# **Replacing Non-Isolated Transceivers**

The IL41050 is designed to replace common non-isolated CAN transceivers such as the Philips/NXP TJA1050 with minimal circuit changes. Some notable differences:

- Some non-isolated CAN transceivers have internal TxD pull-up resistors, but the IL41050 TxD input should not be left open. If connected to an open-drain or open collector output, a pull-up resistor (typically 16 k $\Omega$ ) should be connected from the input to V<sub>DD1</sub>.

- Initialization behavior varies between CAN transceivers. To ensure the desired power-up state, the IL41050 should be initialized with a TxD pulse (low-to-high for recessive initialization), or shut down the transceiver in the desired power-up state (the "programmable power-up feature").

- Many non-isolated CAN transceivers have a V<sub>REF</sub> output. Such a reference is available on the IL41050 wide-body version.

#### The VREF Output

$V_{REF}$  is a reference voltage output used to drive bus threshold comparators in some legacy systems and is provided on the IL41050 wide-body version. The output is half of the bus supply ±10% (*i.e.*, 0.45  $V_{DD2} \le V_{REF} \le 0.55 V_{DD2}$ ), and can drive up to 50  $\mu$ A.

#### IsoRxD / IsoTxD Outputs

The IsoRxD and IsoTxD outputs are isolated versions of the RxD and TxD signals. These outputs are provided on the narrow-body version for troubleshooting, but normally no connections should be made to the pins.

#### The Isolation Advantage

Battery fire caused by over or under charging of individual lithium ion cells is a major concern in multi-cell high voltage electric and hybrid vehicle batteries. To combat this, each cell is monitored for current flow, cell voltage, and in some advanced batteries, magnetic susceptibility. The IL41050 allows seamless connection of the monitoring electronics of every cell to a common CAN bus by electrically isolating inputs from outputs, effectively isolating each cell from all other cells. Cell status is then monitored via the CAN controller in the Battery Management System (BMS).

Another major advantage of isolation is the tremendous increase in noise immunity it affords the CAN node, even if the power source is a battery. Inductive drives and inverters can produce transient swings in excess of 20 kV/µs. The traditional, non-isolated CAN node provides some protection due to differential signaling and symmetrical driver/receiver pairs, but the IL41050 typically provides more than twice the dV/dt protection of a traditional CAN node.

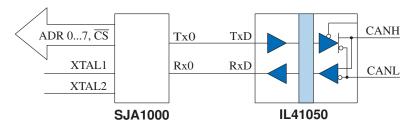

Fig. 2. Isolated CAN node using the IL41050 and an SJA1000 MCU.

IL41050

# Package Drawings, Dimensions and Specifications

IL41050

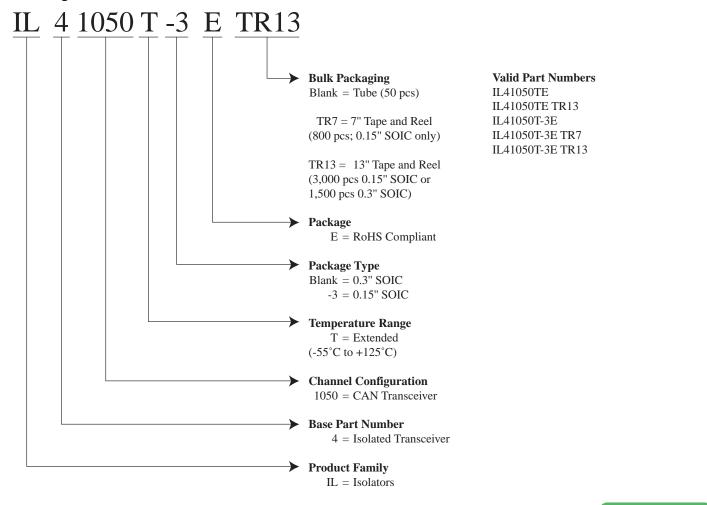

#### Ordering Information and Valid Part Numbers

RoHS COMPLIANT

#### Revision History

# ISB-DS-001-IL41050-J February 2012

ISB-DS-001-IL41050-I June 2011

ISB-DS-001-IL41050-H June 2011

ISB-DS-001-IL41050-G February 2011

ISB-DS-001-IL41050-F April 2010

ISB-DS-001-IL41050-E March 2010

ISB-DS-001-IL41050-D March 2010

ISB-DS-001-IL41050-C February 2010

ISB-DS-001-IL41050-B January 2010

ISB-DS-001-IL41050-A January 2010

# Changes

• Update terms and conditions.

#### Changes

• Added loop delay specifications (p. 5).

#### Changes

- UL approval no longer "pending" (p. 2).

- Clarified V<sub>DD2</sub> power supply connections with note on pinouts page (p. 3) and new explanatory "Application Information" paragraph (p. 6).

#### Changes

• Added "Input Configurations," "Replacing Non-Isolated Transceivers," "the VREF Output," and "IsoRxD/IsoTxD Outputs" Application Information (p. 6).

#### Changes

• Added 7-inch tape-and-reel bulk packaging option (TR7) for narrow-body parts (p. 8).

#### Changes

• Changed narrow-body pinouts for pins 9, 10, 12, 13, and 14 (p. 3).

#### Changes

- Added 0.15" narrow-body SOIC package.

- Added failsafe supply voltage specification and related Note 4.

#### Changes

- Extended min. operating temperature to  $-55^{\circ}$ C.

- Misc. changes and clarifications for final release.

#### Change

- Clarified TxD edge trigger mode. Added information to Applications section.

- Tightened timing specifications based on qualification data.

#### Change

• Initial release.

# IL41050

#### **Datasheet Limitations**

The information and data provided in datasheets shall define the specification of the product as agreed between NVE and its customer, unless NVE and customer have explicitly agreed otherwise in writing. All specifications are based on NVE test protocols. In no event however, shall an agreement be valid in which the NVE product is deemed to offer functions and qualities beyond those described in the datasheet.

#### Limited Warranty and Liability

Information in this document is believed to be accurate and reliable. However, NVE does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NVE be liable for any indirect, incidental, punitive, special or consequential damages (including, without limitation, lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

#### **Right to Make Changes**

NVE reserves the right to make changes to information published in this document including, without limitation, specifications and product descriptions at any time and without notice. This document supersedes and replaces all information supplied prior to its publication.

#### Use in Life-Critical or Safety-Critical Applications

Unless NVE and a customer explicitly agree otherwise in writing, NVE products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical devices or equipment. NVE accepts no liability for inclusion or use of NVE products in such applications and such inclusion or use is at the customer's own risk. Should the customer use NVE products for such application whether authorized by NVE or not, the customer shall indemnify and hold NVE harmless against all claims and damages.

#### Applications

Applications described in this datasheet are illustrative only. NVE makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NVE products, and NVE accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NVE product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customers. Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NVE does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customers. The customer is responsible for all necessary testing for the customer's applications and products using NVE products in order to avoid a default of the applications and the products or of the application or use by customer's third party customers. NVE accepts no liability in this respect.

#### Limiting Values

Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the recommended operating conditions of the datasheet is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

#### **Terms and Conditions of Sale**

In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NVE hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NVE products by customer.

#### No Offer to Sell or License

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### **Export Control**

This document as well as the items described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

#### **Automotive Qualified Products**

Unless the datasheet expressly states that a specific NVE product is automotive qualified, the product is not suitable for automotive use. It is neither qualified nor tested in accordance with automotive testing or application requirements. NVE accepts no liability for inclusion or use of non-automotive qualified products in automotive equipment or applications.

In the event that customer uses the product for design-in and use in automotive applications to automotive specifications and standards, customer (a) shall use the product without NVE's warranty of the product for such automotive applications, use and specifications, and (b) whenever customer uses the product for automotive applications beyond NVE's specifications such use shall be solely at customer's own risk, and (c) customer fully indemnifies NVE for any liability, damages or failed product claims resulting from customer design and use of the product for automotive applications beyond NVE's standard warranty and NVE's product specifications.

An ISO 9001 Certified Company

NVE Corporation 11409 Valley View Road Eden Prairie, MN 55344-3617 USA Telephone: (952) 829-9217 Fax: (952) 829-9189 www.nve.com e-mail: iso-info@nve.com

#### ©NVE Corporation

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

ISB-DS-001-IL41050-J

February 2012