# DS100DF410EVK, DS110DF410EVK, and DS125DF410EVM Evaluation Board Software Installation, Setup, and Operating Guide

# **User's Guide**

Literature Number: SNLU126C February 2013–Revised June 2016

Page

## DS100DF410EVK, DS110DF410EVK, and DS125DF410EVM Evaluation Board Software Installation, Setup, and Operating Guide

The DS100DF410EVK, DS110DF410EVK, and DS125DF410EVM evaluation boards allow the user to examine the advanced signal conditioning capabilities of the quad retimer products. The board connects to a PC using a USB port and the SigCon Architect GUI interface is used to control the device.

All references to the DS110DF410EVK in the document should be taken to apply to the device installed on the evaluation board. The document applies to all of the following devices that can be installed on the board: DS100DF410, DS110DF410, DS125DF410.

#### Topic

2

| 1 | Factures                                | 0  |

|---|-----------------------------------------|----|

| I | Features                                | 3  |

| 2 | Software Installation and Configuration | 5  |

| 3 | Configuring the Device Registers        | 6  |

| 4 | EEPROM and Register Map Informations    | 17 |

| 5 | Bill of Materials                       | 36 |

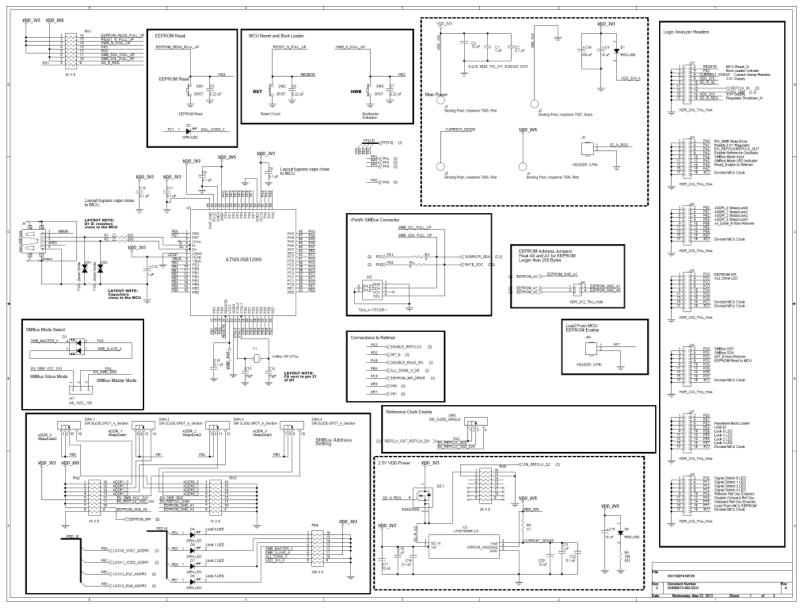

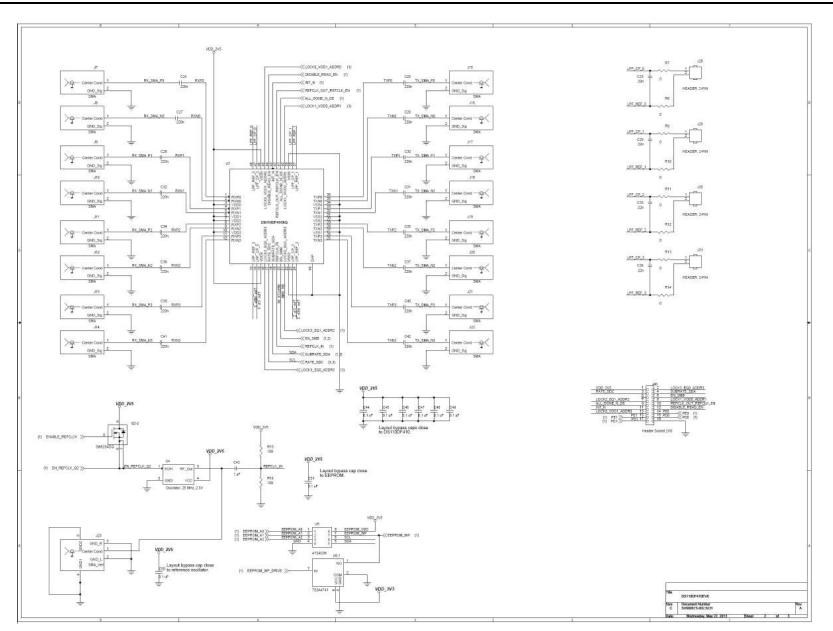

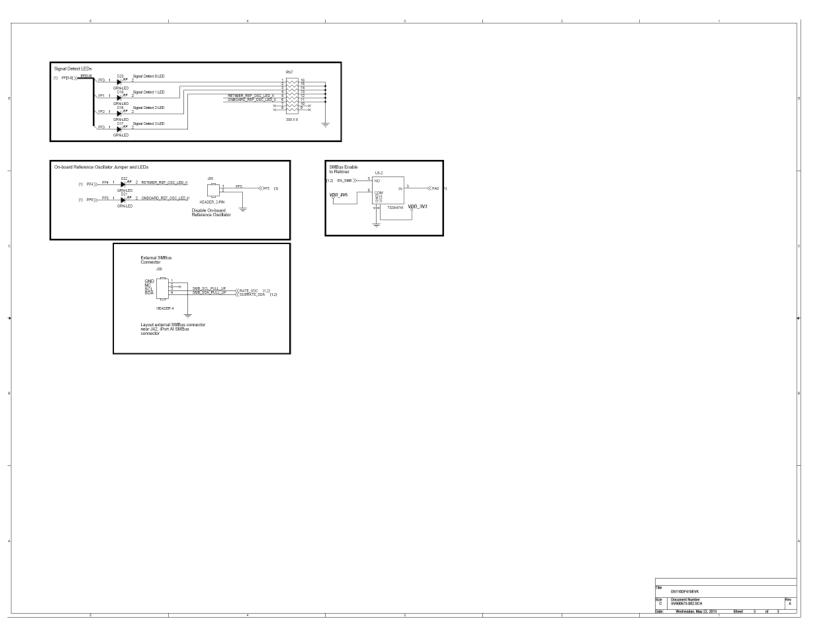

| 6 | Schematic                               | 38 |

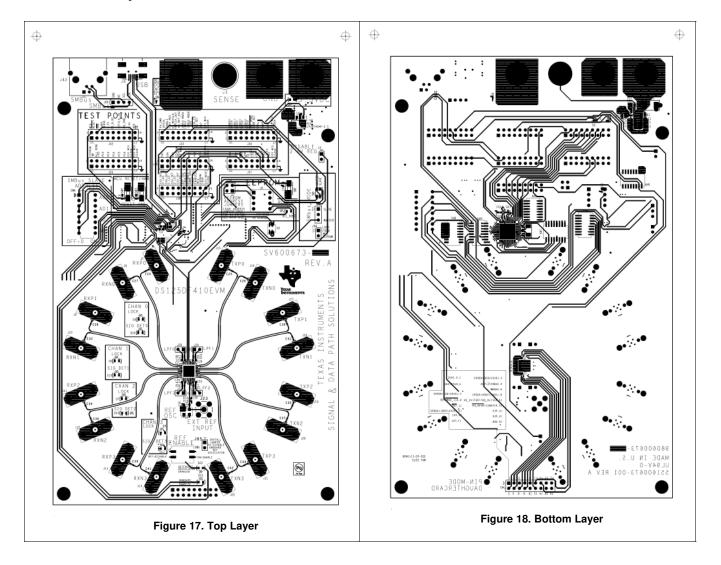

| 7 | Board Layout                            | 41 |

|   | •                                       |    |

#### 1 Features

- Each channel independently locks to 10.3125 Gbps (DS100DF410), 8.5 to 11.3 Gbps (DS110DF410), 9.8 12.5 Gbps (DS125DF410) and sub-multiples of the data rates

- Lock time operation (typically under 15 ms)

- Low latency (~300 ps)

- Adaptive equalization up to 34 dB boost at 5 Gbps GHz

- · Adjustable transmit VOD : 600 to 1300 mVp-p

- Adjustable transmit de-emphasis to -12 dB

- Typical Power Dissipation (EQ+DFE+CDR+DE): 180 mW / channel

- Programmable output polarity inversion

- · Input signal detection, CDR lock detection/indicator

- On-chip Eye Monitor (EOM), PRBS generator

- Single 2.5 V ± 5% or 3.3 V ± 5% power supply

- SMBus/EEPROM configuration modes

- Operating temperature range of -40 to 85°C

- RHS 48-pin, 7 mm x 7 mm package

## 1.1 Applications

- Front port SFF 8431 (SFP+) optical and direct attach copper

- · Backplane reach extension, data retimer

- Backplane reach extension, data retimer

- Ethernet: 10GbE, 1GbE

- Fibre-Channel, Infiniband and other protocols supports

- CPRI: Line bit rate options 3-7

- Interlaken: All lane bit rates

#### 1.2 Ordering Information

| EVM ID             | DEVICE ID         | DEVICE PACKAGE | PACKAGE TYPE |

|--------------------|-------------------|----------------|--------------|

| DS100DF410EVK/NOPB | DS100DF410SQ/NOPB | RHS-48         | QFN          |

| DS110DF410EVK/NOPB | DS110DF410SQ/NOPB | RHS-48         | QFN          |

| DS125DF410EVM      | DS125DF410SQ/NOPB | RHS-48         | QFN          |

4

www.ti.com

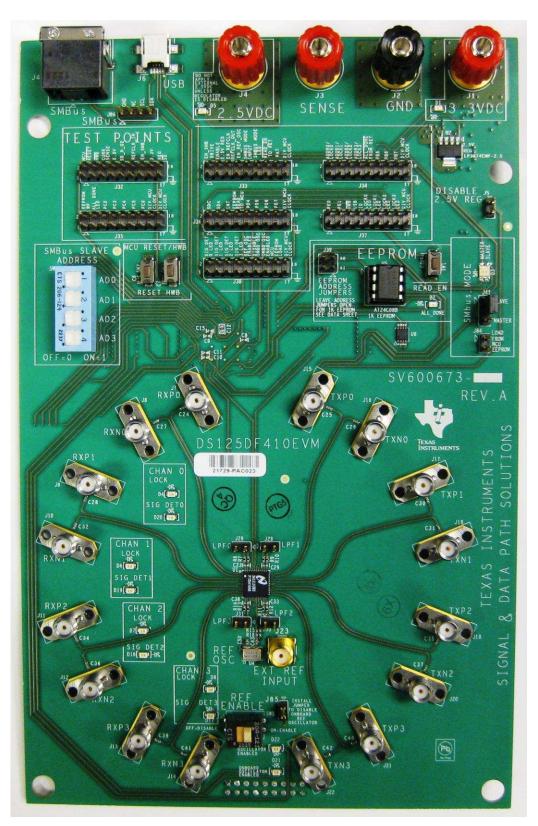

Figure 1. DS100DF410EVK, DS110DF410EVK, DS125DF410EVM Top View

## 2 Software Installation and Configuration

The SigCon Architect software has a device profile for the DS110DF410EVK. The SigCon Architect retimer profiles enable complete register access through SMBus communication with the EVK.

There are several steps for preparing SigCon Architect software for first use.

## 2.1 Installing SigCon Architect Software

1. **(One-time step)** Choose one of the TI SigCon Architect installers to download from the SigCon Architect Tools Folder on TI.com. Follow the prompts to install the software.

- **SNLC055:** With LabView RTE embedded. Download this folder to install SigCon Architect on a computer that does not already have LabView RTE installed.

- **SNLC054:** Without Labview RTE embedded. Download this folder to install SigCon Architect on a computer that already has LabView RTE installed.

2. (**One-time step**) Download the relevant zip folder for the desired profile. For this evaluation module, select the zip folder for all available retimer profiles.

• SNLC057: Retimer profile updaters.

| Name                     | Date modified      | Тур |

|--------------------------|--------------------|-----|

| 🛂 DS125DF111 Updater.exe | 12/8/2015 5:16 PM  | Арр |

| 🕼 DS100DF410 Updater.exe | 12/8/2015 2:28 AM  | Арр |

| 🛂 DS110DF410 Updater.exe | 11/4/2015 11:30 PM | Арр |

| 🛂 DS125DF410 Updater.exe | 10/14/2015 8:36 PM | Арр |

| 🛂 DS110DF111 Updater.exe | 10/6/2015 9:37 PM  | Арр |

#### Figure 2. Retimer Profile Updater Installers

3. Choose the Updater.exe profile for the relevant device. In this case, install "DS110DF410 Updater.exe." Follow the prompts to install.

4. Once SigCon Architect and the correct updater profiles are installed, close any existing instance of SigCon Architect again.

## 2.2 Connecting the DS110DF410EVK Board

- The DS110DF410EVK board requires an external 3.3 V or 2.5 V power supply. The supply terminals are banana jack binding posts. In normal operation, only the 3.3 V DC supply is connected, between J1 (3.3 V DC) and J2 (GND). In order to use the 3.3 V power supply, an on-board 2.5 V DC regulator must be enabled by leaving Pins 1-2 open on J5. If the 2.5 V DC LED is flashing or is not illuminated, the power supply voltage or supply clamping current may be set too low. Try increasing the power supply voltage to 3.4 V DC. In default operation with all channels active, the DS110DF410EVK board will draw approximately 500 mA from a 3.3 V DC supply. A supply current limit setting of at 750 mA is recommended. In order to supply 2.5 V directly, tie Pin 1-2 on J5 to disable the onboard 2.5 V DC regulator and connect a 2.5 V DC supply between J4 (2.5 V DC) and J2 (GND).

- 2. Connect the DS110DF410EVK board's SDA (J86.4), SCL (J86.2), and GND (J86.1) header pins with jumper wires to the SDA, SCL, and GND header pins on the DPS-DONGLE-EVM or equivalent USB2ANY device. A jumper is required on the SMBus Mode header (J41) in the Slave position for proper operation. If the header is installed, the SMBus mode indicator LED should light up green. If the header is not installed or is installed in master mode, the SMBus mode indicator will light up red. Master mode is not currently implemented on this board.

- 3. The DS110DF410EVK board features four pairs of input and output SMA connectors. Use a torque wrench and do not torque the connectors to more than 7-10 inch-pounds (the recommended torque for SMA connectors). The connectors are arranged in pairs and are labeled. RXP0 and RXN0 will be the positive and negative input connectors for Channel 0, and the retimed output for this data stream will be output on connectors TXP0 and TXN0. For Channel 1, the inputs are RXP1 and RXN1, and the outputs are TXP1 and TXN1. For Channel 2, the inputs are RXP2 and RXN2, and the outputs are

#### Configuring the Device Registers

www.ti.com

TXP2 and TXN2. For Channel 3, the inputs are RXP3 and RXN3, and the outputs are TXP3 and TXN3.

## 3 Configuring the Device Registers

Every setting of the SMBus address switches corresponds to a valid SMBus address for the DS110DF410 retimer. Theses switches are within a box labeled "SMBus SLAVE ADDRESS," and the switches are labeled AD0, AD1, AD2, or AD3. The default address, with all the switches off, is 0x30. This is the SMBus Write address for the DS110DF410 retimer. If a different SMBus address is desired, change the SMBus address straps and perform a power-on reset. The SMBus address switches set the SMBus Write address for the DS110DF410 according to Table 1.

| AD3 | AD2 | AD1 | AD0 | DS110DF410 Write Address (Hex) | DS110DF410 Read Address (Hex) |

|-----|-----|-----|-----|--------------------------------|-------------------------------|

| 0   | 0   | 0   | 0   | 0x30                           | 0x31                          |

| 0   | 0   | 0   | 1   | 0x32                           | 0x33                          |

| 0   | 0   | 1   | 0   | 0x34                           | 0x35                          |

| 0   | 0   | 1   | 1   | 0x36                           | 0x37                          |

| 0   | 1   | 0   | 0   | 0x38                           | 0x39                          |

| 0   | 1   | 0   | 1   | 0x3A                           | 0x3B                          |

| 0   | 1   | 1   | 0   | 0x3C                           | 0x3D                          |

| 0   | 1   | 1   | 1   | 0x3E                           | 0x3F                          |

| 1   | 0   | 0   | 0   | 0x40                           | 0x41                          |

| 1   | 0   | 0   | 1   | 0x42                           | 0x43                          |

| 1   | 0   | 1   | 0   | 0x44                           | 0x45                          |

| 1   | 0   | 1   | 1   | 0x46                           | 0x47                          |

| 1   | 1   | 0   | 0   | 0x48                           | 0x49                          |

| 1   | 1   | 0   | 1   | 0x4A                           | 0x4B                          |

| 1   | 1   | 1   | 0   | 0x4C                           | 0x4D                          |

| 1   | 1   | 1   | 1   | 0x4E                           | 0x4F                          |

Table 1. SMBus Address Switch Settings and DS110DF410 SMBus Addresses

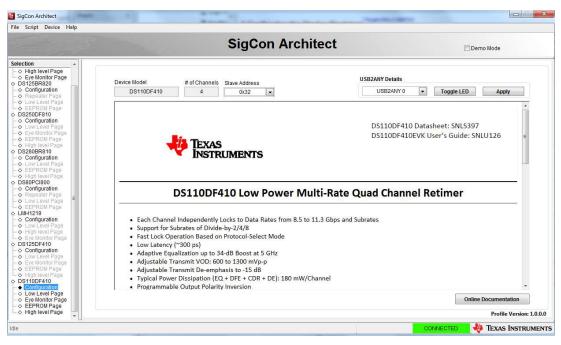

## 3.1 Using SigCon Architect

Open SigCon Architect, and navigate to the Configuration Page of DS110DF410 via the "Selection" column. Choose the appropriate Slave Address. Verify the "USB2ANY Details," specify "USB2ANY 0," and click "Apply." Successful connection is indicated by the green "CONNECTED" indicator on the bottom right of the application. Once connection is successfully established, all settings and controls can be read and written to the device in real-time, as described in the following steps. In the following example, AD[0:3]=0001'b and the "Slave Address" is "0x32." Reference Figure 3.

6

7

Figure 3. SigCon Architect Configuration Page

#### 3.1.1 Low Level Page

In order to read and write to all registers on the DS110DF410, navigate to the Low Level Page as shown below in Figure 4. Only in SMBus Slave Mode can the user read and write to all programmable registers. Click "Read All" in order to load the data in each register from the device to the "Register Map."

| Device Help   |                       |                    |         |          |       |                     |     |                       |            |                  |           |                                          |

|---------------|-----------------------|--------------------|---------|----------|-------|---------------------|-----|-----------------------|------------|------------------|-----------|------------------------------------------|

|               |                       |                    |         | Si       | gC    | on                  | Ar  | chitect               |            |                  |           | 🖾 Demo Mode                              |

|               |                       |                    |         |          |       |                     |     |                       |            |                  |           |                                          |

| /el Page      | Block Select          |                    |         |          |       |                     |     |                       |            |                  |           |                                          |

| nitor Page    | Channel 0 💌           |                    |         |          |       |                     |     |                       |            |                  |           |                                          |

| s20<br>ration | Register Map          |                    | E       | Expand A | H ) [ | Collapse            | All | ]                     |            |                  |           |                                          |

| age<br>'age   | Block / Register Name | Address            | Default | Mode     | Size  | Data                |     |                       | Mask       | Register Data    |           | Mask Value                               |

|               | Global Registers      |                    |         |          |       |                     |     | Current Address       | 7          | Reserved 0x08    | 01        | × FF                                     |

|               | 0xFF                  | 0xFF               | 0x00    | R/W      | 8     | 0x00                | =   | × 8                   |            |                  |           | A                                        |

|               | Channel 0             | Contraction of the | 2002.00 |          | 120   | Construction of the | 100 |                       | 6 🗸        | Reserved_0x08[   |           |                                          |

| e             | 0x00                  | 0x00               | 0x00    | R/W      | 8     | 0x00                |     | Data                  | 5 🔽        | Reserved_0x08[   |           |                                          |

| ie            | 0x01                  | 0x01               | 0x00    | R/W      | 8     | 0x00                |     | × 0                   | 4 🕡        | CDR_CAP_DAC      |           |                                          |

|               | 0x02                  | 0x02               | 0x00    | R        | 8     | 0x00                |     |                       | 3 🗸        | CDR_CAP_DAC      |           |                                          |

|               | 0x03                  | 0x02               | 0x00    | R/W      | 8     | 0x00                |     | Write Register        | 2 🗸        | CDR_CAP_DAC      |           |                                          |

|               | 0x04                  | 0x04               | 0x00    | R/W      | 8     | 0x00                |     | The Register          | 1 🔽        | CDR_CAP_DAC      | _START[1] |                                          |

|               | 0x04                  | 0x04               | 0x00    | R/W      | 8     | 0x00                |     | Broadcast             | 0 🔽        | CDR CAP DAC      | START[0]  |                                          |

| le<br>e       | 0x06                  | 0x05               | 0x00    | R/W      | 8     | 0x00                |     |                       |            |                  |           |                                          |

|               | 0x07                  | 0x07               | 0x00    | R/W      | 8     | 0x00                |     | Read Register         | Field Desc | ription          |           |                                          |

|               | 0x07                  | 0x07               | 0x00    | RW       | 8     | 0x00                |     |                       | -          | Field Name       | Access    | Description                              |

|               | 0x09                  | 0x09               | 0x00    | R/W      | 8     | 0x00                |     | Read All              | Decemen    | 1 0x08[7:5]      | R/W       | UNUSED                                   |

|               | 0x0A                  | 0x09               | 0x10    | R/W      | 8     | 0x10                |     |                       |            |                  |           |                                          |

|               | 0x0A                  | 0x08               | 0x0E    | R/W      | 8     | OXOF                |     |                       | CDR_CA     | P_DAC_START[4:0] | R/W       | Override Starting VCO Cap DAC S<br><4.0> |

|               | 0x0B<br>0x0C          | 0x0B               | 0x0F    | R/W      | 8     | 0x0F                |     | Reset Device          |            |                  |           | <4:0>                                    |

|               | 0x0D                  | 0x0C               | 0x00    | R/W      | 8     | 0x00                |     |                       |            |                  |           |                                          |

|               |                       |                    |         | R/W      | 8     |                     |     | Load Config           |            |                  |           |                                          |

|               | 0x0E                  | 0x0E               | 0x93    | R/W      | 8     | 0x93                |     |                       |            |                  |           |                                          |

|               | 0x0F                  | 0x0F               | 0x69    |          |       | 0x69                |     | Save Config           |            |                  |           |                                          |

|               | 0x10                  | 0x10               | 0x3A    | R/W      | 8     | 0x3A                |     | distanti in terrer su |            |                  |           |                                          |

|               | 0x11                  | 0x11               | 0x20    | R/W      | 8     | 0x20                |     | Note: Load Config     |            |                  |           |                                          |

|               | 0x12                  | 0x12               | 0xE0    | R/W      | 8     | 0xE0                |     | will Overwrite all    |            |                  |           |                                          |

| 8             | 0x13                  | 0x13               | 0x30    | R/W      | 8     | 0x30                |     | Registers.            | _          |                  |           |                                          |

|               | 0x14                  | 0x14               | 0x00    | R/W      | 8     | 0x00                |     |                       |            |                  |           |                                          |

|               | 0x15                  | 0x15               | 0x10    | R/W      | 8     | 0x90                |     |                       |            |                  |           |                                          |

|               | 0x16                  | 0x16               | 0x7A    | R/W      | 8     | 0x7A                |     |                       |            |                  |           |                                          |

|               | 0x17                  | 0x17               | 0x36    | R/W      | 8     | 0x36                |     |                       |            |                  |           |                                          |

|               | 0x18                  | 0x18               | 0x40    | R/W      | 8     | 0x40                |     |                       |            |                  |           |                                          |

|               | 0x19                  | 0x19               | 0x23    | R/W      | 8     | 0x23                |     |                       |            |                  |           |                                          |

| e             | 0x1A                  | 0x1A               | 0x00    | R/W      | 8     | 0x00                | -   |                       |            |                  |           |                                          |

Figure 4. SigCon Architect Low Level Page

#### Read Register:

- Type the readable address in the "Current Address" text box. Click "Read Register." The data in

#### Configuring the Device Registers

this register will appear in the "Data" text box.

Alternatively, you can highlight the desired register by clicking on the corresponding row in the Register Map. In the "Register Data" section the data can be read by checking or unchecking the boxes corresponding to individual bits.

#### • Write Register:

- Type the writable address in the "Current Address" text box, and type the data to write to this address in the "Data" text box. Click "Write Register."

- Alternatively, you can highlight the desired register by clicking on the corresponding row in the Register Map. In the "Register Data" section the registers can be written by checking or unchecking the boxes corresponding to individual bits.

## 3.1.2 High Level Page

The High Level Page has five tabs:

- Block Diagram

- Device Status

- Rx EQ/DFE

- CDR

- Tx DEM/PRBS Generator

Each tab will be described in detail in the subsequent sections.

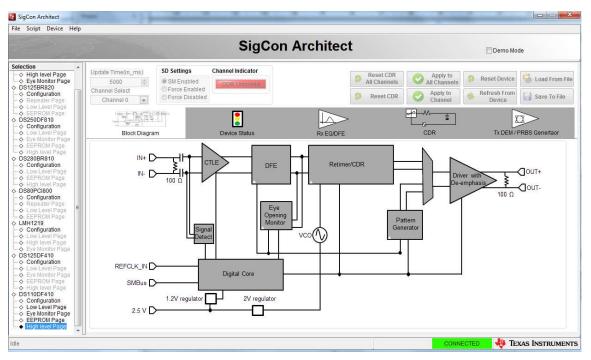

#### 3.1.2.1 Block Diagram

The Block Diagram Page provides a high level graphic of the functional components of the DS110DF410. Reference Figure 5.

Figure 5. SigCon Architect High Level Page: Block Diagram

8

#### 3.1.2.2 Device Status Tab

In order to view a high level summary of the device status and control settings, navigate to the Device Status Tab. Reference Figure 6. This tab is read only. After updating the device settings and controls from the Low Level Page or the corresponding High Level Page tabs, the Device Status Tab will update to display the current settings. Leave the check box marked "Continuous Status Update?" in its default checked state to ensure the status and settings are constantly updated. Set the "Update Time(in\_ms)" in order to alter the time increment in which all the settings will be refreshed.

|                                                                      |                                                        |          | Sig                            | Con         | Ar          | chitect                                            |        |                           |                                                 | [          | Demo Mode                         |

|----------------------------------------------------------------------|--------------------------------------------------------|----------|--------------------------------|-------------|-------------|----------------------------------------------------|--------|---------------------------|-------------------------------------------------|------------|-----------------------------------|

| Page<br>r Page<br>ion<br>rage<br>Page<br>Channel Select<br>Channel 0 | ms) SD Settings<br>SM Enable<br>Force Ena<br>Force Dis | ed C     | nel Indicator                  |             |             | 3                                                  | All Ch | t CDR<br>annels<br>et CDR | Apply to<br>All Channels<br>Apply to<br>Channel | Ref        | set Device State Load From Device |

| on the first sector                                                  | k Diagram                                              | De       | vice Status                    |             |             | Rx EQ/DFE                                          |        |                           |                                                 |            | Tx DEM / PRBS Genertaor           |

|                                                                      | is Status Update?                                      |          |                                |             |             |                                                    |        |                           | U                                               | pdating Ch | annel 3                           |

| Channel                                                              | 0 😑 CDR Locked                                         | 0.765625 | EQ Boost<br>HEO(UI)<br>VEO(mV) | -<br>+<br>+ | 0<br>0<br>0 | DFE Taps 1(mV)<br>DFE Taps 2(mV)<br>DFE Taps 3(mV) | +      | 0                         | DFE Taps 4(mV)<br>DFE Taps 5(mV)                | 0.0<br>600 | DRV_DEM(dB)<br>DRV_SEL_VOD(mV)    |

| E Channel                                                            | 1 OCR Locked                                           |          | EQ Boost<br>HEO(UI)<br>VEO(mV) | -<br>+<br>+ | 0<br>0      | DFE Taps 1(mV)<br>DFE Taps 2(mV)<br>DFE Taps 3(mV) | *      | 0                         | DFE Taps 4(mV)<br>DFE Taps 5(mV)                | 0.0        | DRV_DEM(dB)<br>DRV_SEL_VOD(mV)    |

|                                                                      |                                                        | 1122     | EQ Boost                       | -           | 0           | DFE Taps 1(mV)                                     | +      | 0                         | DFE Taps 4(mV)                                  | 0.0        | DRV DEM(dB)                       |

| Channel                                                              | 2 ODR Locked                                           | 0        | HEO(UI)<br>VEO(mV)             | +           | 0           | DFE Taps 2(mV)<br>DFE Taps 3(mV)                   | +      | 0                         | DFE Taps 5(mV)                                  | 600        | DRV_SEL_VOD(mV)                   |

|                                                                      |                                                        | 1122     | EQ Boost                       | -           | 0           | DFE Taps 1(mV)                                     | +      | 0                         | DFE Taps 4(mV)                                  | 0.0        | DRV DEM(dB)                       |

| Channel                                                              | 3 🔴 CDR Locked                                         | 0        | HEO(UI)                        | +           | 0           | DFE Taps 2(mV)                                     | +      | 0                         | DFE Taps 5(mV)                                  | 600        | DRV_SEL_VOD(mV)                   |

| Page<br>r Page<br>Page                                               |                                                        | 0        | VEO(mV)                        | +           | 0           | DFE Taps 3(mV)                                     |        |                           |                                                 |            |                                   |

Figure 6. SigCon Architect High Level Page: Device Status Tab

- CDR Lock Status: For each channel, there is an indicator signifying if the CDR is locked or unlocked. The CDR Lock indicator will turn green when the CDR state machine detects phase lock to the input signal. The DS110DF410 retimer will usually lock automatically to any input signal in its lock range. When the DS110DF410 retimer is locked, the lock indicator LED on the board will also turn green. The lock indicators' LEDs are located near the input connectors for each channel. The signal detect can be monitored by the Signal Detect LEDs labeled "Sig Det0:3." When this LED turns green, a signal is detected at the corresponding channel.

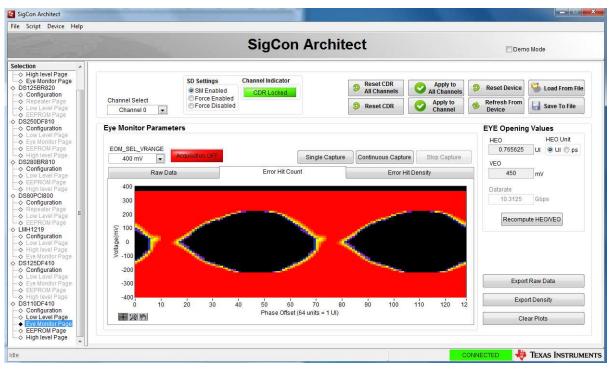

- Eye Diagram Measurements (HEO, VEO): The Eye Diagram Measurements are read only. These measurements will be described in greater detail in Section 3.1.4.

- **EQ Settings:** The EQ Settings are read only, and they will be affected by settings in the RX EQ/DFE Tab. These settings will be described in greater detail in Section 3.1.2.3.

- **DFE Settings:** The DFE Settings are read only, and they will be affected by settings in the RX EQ/DFE Tab. These settings will be described in Section 3.1.2.3.

- Driver Settings: The Driver Settings are read only, and they will be affected by settings in the TX DEM/PRBS Generator Tab. These settings will be described in Section 3.1.2.5.

## 3.1.2.3 Rx EQ/DFE Tab

The Rx EQ/DFE Tab contains the Receiver Controls, both for the Equalizer and the DFE. Reference Figure 7.

9

|                                                                                                                                                                                                                                                                                    | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | SigCon Architect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Selection                                                                                                                                                                                                                                                                          | Updata Time(m_ms) SD Settings Channel Indi<br>5000 0 Porce Enabled OF Core Enabled<br>Channel 6 Channel 0 Charnel 0 Char | cator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| EEPROM Page<br>250DF810<br>Configuration<br>Low Level Page<br>Eve Monitor Page                                                                                                                                                                                                     | Block Diagram Device Str                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | atus RA EQDEE CDR Tx DEM//PRBS Generatur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| High level Page<br>280BR810<br>Configuration<br>Low Level Page<br>EEPROM Page<br>High level Page                                                                                                                                                                                   | Adaptive Mode Solicction C Adaptive Mode 0, No AdaptManual Mode Adaptive Mode 1.CTLE Only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Adaptive Mode 2,CTLE wDFE Fine Tune     Adaptive Mode 3,DFEwCTLE Fine Tune                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ISOPCISO<br>Configuration<br>Repeated Page<br>EEDROAF Page<br>H1218<br>Configuration<br>Law Level Page<br>H121 Page<br>Ene Monitor Page<br>High Level Page | DFE Controls           Enable UPE7           Brcadceat7           Configure Taps1           UPE Tap1           DFE Tap2           DFE Tap3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CTLE Sectings CTLE Boost Stage 3 CTLE Boost Stage 1 CTLE Boost Stage 3 CTLE Boost 3 CTLE Boo |

| Configuration<br>Low Level Page                                                                                                                                                                                                                                                    | DFE Tep 5 + x 0 Clear DFE Taps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 12<br>13 - Reset GTLE Load CTLE Save As CTLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 7. SigCon Architect High Level Page: RX EQ/DFE Tab

- Adaptive Mode Selection: The Adaptive Mode Selection provides four options in which the CTLE and DFE are paired in different combinations to equalize the receiver's input. The DFE Controls and CTLE Settings are grayed out or editable depending on the Adaptive Mode Selection.

- In Adapt Mode 0, the DS110DF410 will not change its current CTLE and DFE settings as it tries to acquire phase lock to the incoming signal. The default settings for the CTLE boost registers and the DFE tap registers are all zero, so if the DS110DF410 retimer has been reset to its default state the equalizers will all be set to their minimum values. This mode is primarily useful for troubleshooting.

- In Adapt Mode 1, the DS110DF410 will adapt the CTLE to an optimum value as it acquires lock. The optimum value is the value of the CTLE coefficients that (1) maximizes the figure of merit for adaptation and (2) is in the CTLE coefficients table. The DFE is not used. The DFE coefficients will be left at the default value of 0.

- In Adapt Mode 2, the CTLE is first adapted until an optimum eye opening is obtained with the DFE coefficients forced to 0. The DFE is then adapted and the DFE coefficients will change if a DFE setting that improves the eye opening is found. Finally the CTLE is adapted again with the new DFE settings, and the CTLE settings will change if a better eye opening can be found. This three step process tends to produce CTLE boost settings that are larger and DFE tap values that are smaller than does Adapt Mode 3.

- In Adapt Mode 3, the CTLE is adapted until the DS110DF410 retimer declares phase lock. This may occur at a much lower CTLE boost setting than optimum. Once phase lock is attained, the DFE is adapted to further optimize the eye opening, after which the CTLE is once again adapted with the new DFE values. In this adapt mode, the DFE tap values are generally greater in magnitude than for Adapt Mode 2 and the CTLE boost values are generally smaller. Adapt Mode 3 may provide superior performance in the presence of a large crosstalk interference.

- DFE Controls: The DFE Controls are configurable in Adapt Mode 2 or 3. The "Enable DFE?" check box must be checked in order to edit the remaining settings. The "Broadcast?" check box applies the controls to every channel. The "Configure Taps?" check box allows the user to manually edit the DFE Taps. Each DFE Tap can be set via the text boxes. The DS110DF410 retimer features a five-tap Decision Feedback Equalizer (DFE). The summing point for the DFE is after the CTLE and just before the comparator that decides whether the current bit is a one or a zero. Tap 1 (the first tap, the tap that adds back to the current bit the previously-received bit delayed from the current bit by one bit time), has a magnitude range from 0x00 to 0x1F. The other taps each have a magnitude range from 0x00 to 0x0F. All taps can be subtracted at the summing point (sign is "-") or added at the summing point (sign is "+") by clicking the "Invert Button." The tap values are applied when the button labeled "Set DFE Taps" is clicked. After adaptation, the text controls show the current values of the various DFE taps.

The button labeled "Clear DFE Taps" sets all the DFE tap values to 0x00. The button labeled "Adapt DFE Taps" will cause the DS110DF410 retimer to attempt to re-adapt the DFE tap values, starting from the current tap values, to find a better setting that optimizes the eye opening figure of merit. If a better set of DFE tap values is not found, the DFE tap values will not change. If, during adaptation, the DS110DF410 retimer loses lock, the CTLE values may be changed by the state machine in order to reacquire lock. The DFE is enabled by default.

- CTLE Settings: The CTLE Settings affect the Equalizer Boost. The CTLE Boost Settings 0 31 have corresponding Boost Stage 0 - 3 settings. Consequently, the Boost Stages can also be manually edited by checking the "Enable Manual EQ Boosting?" check box. There are four stages of cascaded CTLE boost in the DS110DF410 retimer. The high-pass filter function of each stage is variable by the CTLE boost setting for that stage. If a change to the CTLE boost causes the DS110DF410 retimer to drop out of lock, the CDR lock state machine will take over and will reset the CTLE boost settings to relock to the incoming signal (unless the DS110DF410 retimer is in Adapt Mode 0). CTLE Boost Stage 0 is the first stage encountered by the signal, followed by Stages 1, 2, and 3. In general, setting the CTLE so that more of the gain is in the first stage (Stage 0) will reduce the noise propagated through the CTLE and will result in lower random jitter. In general, however, you can determine comparatively how much CTLE boost is being applied by summing the boost settings of all four stages. For example, a CTLE boost setting, given as (Stage 0 boost, Stage 1 boost, Stage 2 boost, Stage 3 boost), of (2, 2, 0. 0) will produce a CTLE boost frequency response almost the same as a setting of (1, 1, 1, 1). The final boost stage. Stage 3, can be set to be a limiting amplifier with relatively flat gain over frequency by checking this checkbox. For some channels, this can provide improved performance, but generally it is better to leave this checkbox in its default, unchecked state. The user can also reset the CTLE, or save the current CTLE settings.

- Load CTLE Table: This button is used to load a non-default CTLE table. When the DS110DF410 starts to adapt the CTLE, either to acquire lock or to optimize the eye-opening figure of merit, it steps through a defined set of CTLE settings. These settings have been designed to provide monotonically-increasing CTLE boost for many channels. They are optimized for backplane channels, either stripline or microstrip, on a printed circuit board substrate. For systems where the channel consists of a cable, however, the default CTLE table may not provide optimum equalization. This is because the loss characteristics of a cable as a function of frequency are different from those of a backplane channel. Instead, the user can load a new, non-default, set of CTLE settings through which the DS110DF410 retimer will step during equalization. In order to load such a table, click the "Load CTLE Table" button. This will cause a file selection window to appear. The CTLE table files are simple text files which can be created or modified using any text editor. The default extension for the CTLE table files is ".ini."

- High Level Controls:

- Reset CDR to All Channels or Reset CDR: These two buttons allow the user to reset the CDR for either the current channel selected or for all channels.

- Apply to All Channels or Apply to Channel: These two buttons allow the user to apply the current settings toeither the channel selected or to all channels.

- Reset Device: This button allows the user to reset the device to a default set-up state.

- Refresh from Device: This button refreshes the device settings and updates any read-only indicators.

- Load From File or Save to File: These two buttons allow the user either to load previously saved register settings from a configuration file (.cfg) to the device or to save current device settings to a configuration file (.cfg).

#### 3.1.2.4 CDR Tab

The CDR Tab allows the user to select the CDR data rate and group divider settings. Reference Figure 8.

11

#### Configuring the Device Registers

www.ti.com

| ript Device Help                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                       |

|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                    | SigCon Architect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 🗖 Demo Mode                                                                                                                                           |

| h level Page<br>Monitor Page<br>59R820<br>offguration<br>peater Page               | 5000 🚖 🔍 SM Enabled CDR Locked                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | et CDR Apply to<br>hannels All Channels Reset Device Store<br>set CDR Apply to<br>Channel Set CDR I Set Comparison Channel                            |

| / Level Page<br>PROM Page<br>IDF810<br>Ifiguration<br>/ Level Page<br>Monitor Page | Block Diagram Device Status Rx EQ/DFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | CDR Tx DEM / PRBS Genetic                                                                                                                             |

| ROM Page<br>I level Page<br>BR810<br>figuration<br>Level Page                      | Mode Selection* © Standard Mode © Manual Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Group divider Settings*<br>Rate/Subrate Group 0 Group 1<br>Div Settings Div Settings                                                                  |

| COM Page<br>evel Page<br>1800<br>guration<br>ater Page<br>evel Page                | Standard Data Rate Selection* <ul></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0x00         2.4         2.4           0x01         1         1           0x02         1.2.4         1.2.4           0x03         1.2.4         1.2.4 |

| ROM Page<br>19<br>Iouration                                                        | Custom Data Rate Selection Group 0 Manual Mode Settings Group 1 Manual Mode Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0x04     1     1     0x05     1     1     0x06     1     1                                                                                            |

| evel Page<br>level Page<br>Ionitor Page<br>0F410<br>guration                       | VCO frequency         0         GHz         VCO frequency         0         GHz           PPM Tolerance         0         PPM Tolerance         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0         0 | © 0007 1.2,4 1.2,4<br>© 0008 1.2,4 1.2,4<br>© 009 2.4 2.4<br>© 000A 1.2,4 1.2,4                                                                       |

| Level Page<br>Monitor Page<br>ROM Page<br>Level Page<br>DF410                      | Write Rate Regs         Write Rate Regs           VCO Count to<br>0x61/0x60         ×         0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x0B 8 1<br>0x0C 8 1<br>0x0C 8. 1<br>0x0D 1,2,4 1,2,4<br>0x0E 1 1                                                                                     |

| figuration<br>Level Page<br>Monitor Page<br>ROM Page                               | PPM Countio<br>0x67(7)/0x64[7:4] 0x0,0x0 0x67(6)/0x64[3:0] 0x0,0x0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | © 0x0F 1.2 1.2                                                                                                                                        |

Figure 8. SigCon Architect High Level Page: CDR Tab

- **Mode Selection:** When in Standard Mode, the only editable control is the "Standard Data Rate Selection." In Manual Mode, the user is able to edit the Custom Data Rate Selection and the Group divider Settings.

- Standard Data Rate Selection: The user can choose one of the selectable protocols, and the data rate will follow the corresponding standard.

- **Custom Data Rate Selection:** The user can manually set the Group 0 and Group 1 Settings by entering the desired VCO frequency and PPM Tolerance in the corresponding text boxes. Clicking "Write Rate Regs" will then program the appropriate register bits to re-configure the Group 0 or 1 lock rates.

- **Group divider Settings:** The user can choose the Subrate and corresponding Group 0 and Group 1 Divider Settings.

- **High Level Controls:** There are eight buttons in the top right of the page which apply to all the settings discussed above. These are identical buttons to the ones described in Section 3.1.2.3.

#### 3.1.2.5 Tx DEM/PRBS Generator Tab

The Tx DEM/PRBS Generator Tab allows the user to control the driver settings and the PRBS Generator Configurations. Reference Figure 9.