## Switch-Mode Single Cell Li-ion Battery Charger with USB OTG

### **General Description**

The RT9451 integrates a high efficiency USB friendly switch mode charger with On-The-Go (OTG) support for single cell Li-ion and Li-polymer batteries, D+D– detection, and a 50mA LDO regulator into a single chip.

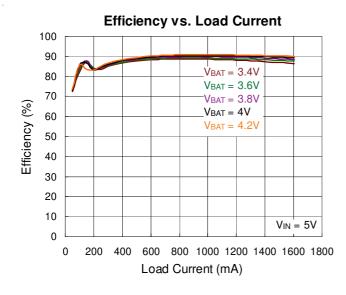

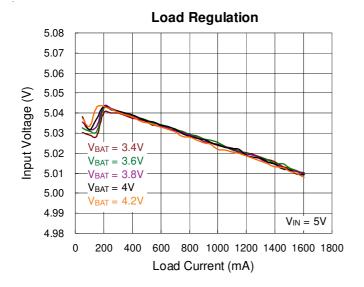

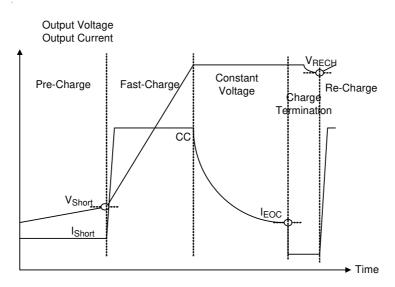

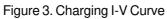

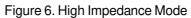

The charger features a synchronous 375kHz PWM controller with integrated power MOSFETs, input current sensing and regulation, Minimum Input Voltage Regulation (MIVR), high accuracy charge current and voltage regulation, and charge termination. It charges the battery in three phases : low current pre-charge, constant current fast charge, and constant voltage trickle charge. The input current is automatically limited to the value set by the host. The charger can be configured to terminate charge based on user-selectable minimum current level and automatically restart the charge cycle if the battery voltage falls below the recharge threshold. A safety timer with reset control provides a safety backup for I<sup>2</sup>C interface. The charger automatically enters sleep mode or high impedance mode when the input supply is removed. The charge status is reported to the host using the I<sup>2</sup>C interface and the STAT pin. The D+D- detection circuit allows automatic detection of a USB wall charger. If a wall charger is detected, the input current limit will automatically increase from 500mA to 975mA.

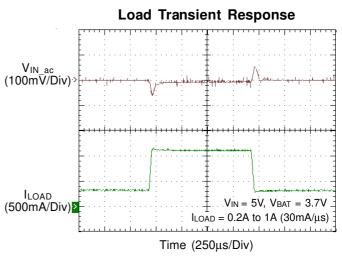

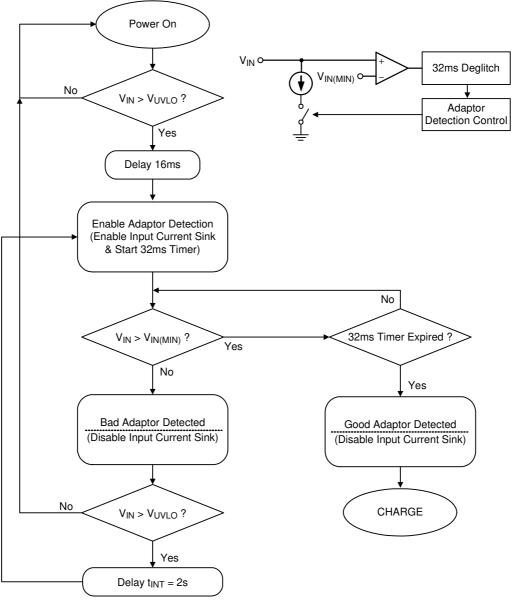

In OTG mode, the PWM controller boosts the battery voltage to 5V and provides up to 1.6A of current to the USB output. At very light load, the Boost operates in burst mode to optimize efficiency. OTG mode can be enabled either through  $l^2C$  interface or GPIO control.

### **Applications**

- Mobile Phones and Smart Phones

- MP3 Players

- Handheld Devices

# Ordering Information

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

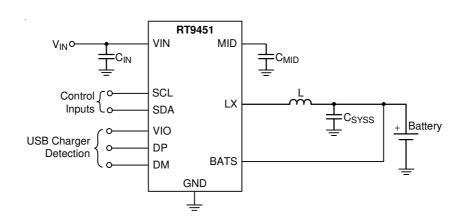

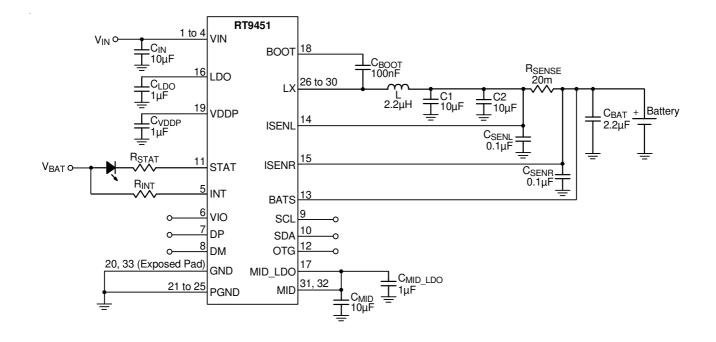

### **Simplified Application Circuit**

## **RT9451**

### **Features**

- Integrated Switching Charger and 50mA LDO in a Single Package

- Charges Faster Than Linear Chargers

- High Accuracy Voltage and Current Regulation

- Charge Voltage Regulation Accuracy : ±1%

Charge Current Regulation Accuracy : ±5%

- Minimum Input Voltage Regulation : 4.2V to 4.76V with Step of 80mV

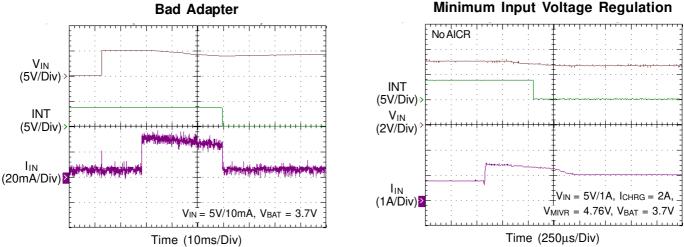

- Bad Adaptor Detection and Rejection

- Safety Limit Register for Maximum Charge Voltage and Current Limiting

- High Efficiency Mini-USB/AC Battery Charger for Single Cell Li-Ion and Li-Polymer Battery Packs

- 28V Absolute Maximum Input Voltage Rating

- 12V Maximum Operating Input Voltage

- Built-In Input Current Sensing and Limiting

- Integrated Power FETs for Up to 4A Charge Rate

- Programmable Charge Parameters through I<sup>2</sup>C Interface (up to 400 Kbps) :

- Input Current

- Fast Charge/Termination Current

- ▶ Charge Voltage (3.5V to 4.44V)

- Safety Timer

- Termination Enable

- Synchronous Fixed Frequency PWM Controller Operating at 375kHz With 0% to 99% Duty Cycle

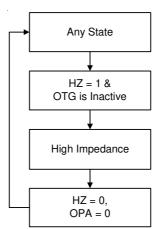

- Automatic High Impedance Mode for Low Power Consumption

- Safety Timer with Reset Control

- Thermal Regulation and Protection

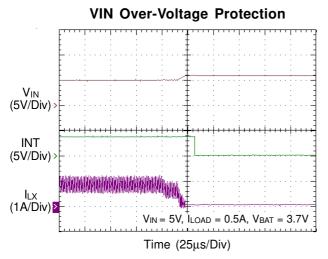

- Input/Output Over-Voltage Protections

- Status Output for Charging and Faults

- USB Friendly Boot-Up Sequence

- Automatic Charging

- Boost Mode Operation for USB OTG

- Input Voltage Range (BATS) : 2.5V to 4.5V

Output Voltage for VIN : 4.425V to 5.506V

- RoHS Compliant and Halogen Free

### **Marking Information**

0Q= : Product Code

YMDNN: Date Code

|   | 0Q=YM<br>DNN |

|---|--------------|

| • |              |

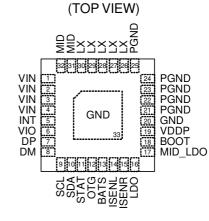

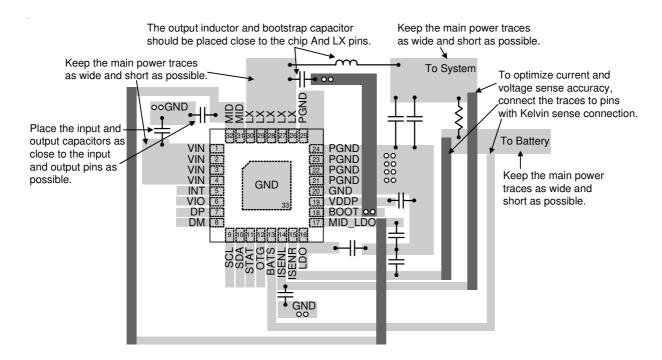

### Pin Configuration

WQFN-32L 4x4

### **Functional Pin Description**

| Pin No.                 | Pin Name | Pin Function                                                                                                                                                                                                                                |

|-------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 4                  | VIN      | Power input. Bypass to PGND with a $10\mu F$ ceramic capacitor. It also provides power to the load in boost mode.                                                                                                                           |

| 5                       | INT      | Interrupt pin (open-drain). This pin is pulled low when a fault occurs.                                                                                                                                                                     |

| 6                       | VIO      | I/O reference voltage. A VIO level above 0.6V disables automatic D+/D-detection.                                                                                                                                                            |

| 7                       | DP       | USB port D+ input connection.                                                                                                                                                                                                               |

| 8                       | DM       | USB port D- input connection.                                                                                                                                                                                                               |

| 9                       | SCL      | I <sup>2</sup> C interface clock input. Open-drain output, connect a 10k $\Omega$ pull-up resistor.                                                                                                                                         |

| 10                      | SDA      | I <sup>2</sup> C interface data input. Open-drain output, connect a 10k $\Omega$ pull-up resistor.                                                                                                                                          |

| 11                      | STAT     | Charge status indicator. Pull low when charge is in progress. Open-drain for other conditions. This pin can also be controlled through I <sup>2</sup> C register. The STAT can be used to drive a LED or communicate with a host processor. |

| 12                      | OTG      | Boost mode enable control. Boost mode is turned on whenever this pin is active. Polarity is user defined through $I^2C$ register. The pin is disabled by default and can be enabled through $I^2C$ register bit.                            |

| 13                      | BATS     | Auxiliary power supply. Connect to the battery pack to provide power in high impedance mode. Bypass to GND with a $1\mu$ F ceramic capacitor.                                                                                               |

| 14                      | ISENL    | Charge current sense input. Battery current is sensed via the voltage drop across an external sense resistor. A $0.1\mu$ F ceramic capacitor to PGND is required.                                                                           |

| 15                      | ISENR    | Battery voltage and current sense input. Bypass to PGND with a ceramic capacitor (minimum $0.1\mu$ F) if there are long inductive leads to battery.                                                                                         |

| 16                      | LDO      | LDO output. LDO is regulated to 4.9V and drives 60mA of current. Bypass LDO to GND with a minimum 1 $\mu$ F ceramic capacitor. LDO is enabled when VIN is above the VIN UVLO threshold.                                                     |

| 17                      | MID_LDO  | LDO input voltage. Please connect to MID.                                                                                                                                                                                                   |

| 18                      | воот     | Bootstrap supply for high-side gate driver. Connect a 100nF ceramic capacitor (voltage rating above 10V) from BOOT pin to LX pin.                                                                                                           |

| 19                      | VDDP     | Internal bias regulator voltage for driver. Connect a $1\mu$ F ceramic capacitor from this output to PGND. External loads on VDDP is not allowed.                                                                                           |

| 20, 33<br>(Exposed Pad) | GND      | Pure ground. The exposed pad must be soldered to a large PCB and connected to GND for maximum thermal dissipation.                                                                                                                          |

| 21 to 25                | PGND     | Power ground.                                                                                                                                                                                                                               |

| 26 to 30                | LX       | Switch node.                                                                                                                                                                                                                                |

| 31, 32                  | MID      | Connection point between reverse blocking MOSFET and high-side MOSFET. Bypass to PGND with a minimum of $10\mu$ F capacitor. No other circuits are recommended to connect at MID pin.                                                       |

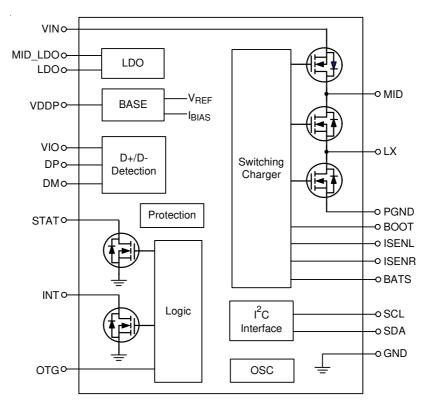

### **Functional Block Diagram**

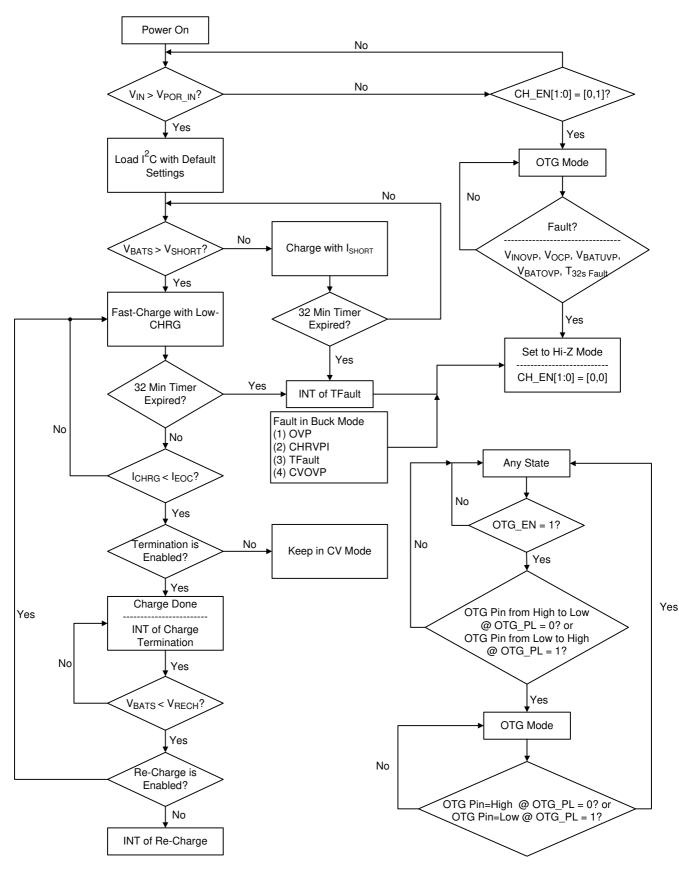

### Operation

The RT9451 is designed for single cell Li-lon battery charger in portable applications.

#### **Base Circuits**

Base circuits provide the internal power, VDD and reference voltage and bias current.

#### **Protection Circuits**

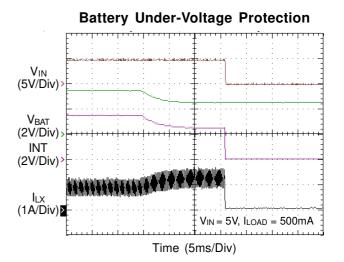

The protection circuits include the OVP, UVLO and OTP circuits. The protection circuits turn off the charging when the input power or die temperature is in abnormal level.

#### Switching Charger

The switching charger controls the operation during the charging process. The controller will make sure the battery is well charged in a suitable current, voltage, and die temperature.

#### Logic Circuits

The STAT and INT indicate the charger and interrupt condition. During the charging process, the STAT pin is

pulled low and pulled high when the charger is under abnormal condition or charge done. The INT pin indicates the fault condition. When any fault occurs, the INT is pulled low.

#### LDO

The RT9451 provides a 50mA LDO to support the peripheral circuits. The output voltage is regulated to 4.9V and the maximum output current is 120mA.

#### OSC

The oscillator runs at fixed 375kHz frequency for the PWM control of switching charger.

#### I<sup>2</sup>C Interface

The I<sup>2</sup>C interface is used to program battery voltage, charge current, termination current, MIVR level, and OTG voltage.

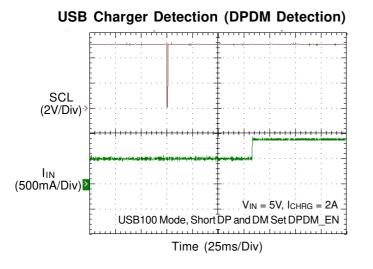

#### D+/D- Detection

The D+/D- detection can detect the devices which are inserted to the USB connector.

### Absolute Maximum Ratings (Note 1)

| <ul> <li>Supply Voltage VIN</li></ul>          | <ul> <li>-0.3V to 28V</li> <li>-0.3V to 6V</li> </ul> |

|------------------------------------------------|-------------------------------------------------------|

| Output Current (average) LX                    | - 4A                                                  |

| Output Current (continuous) LDO                | · 100mA                                               |

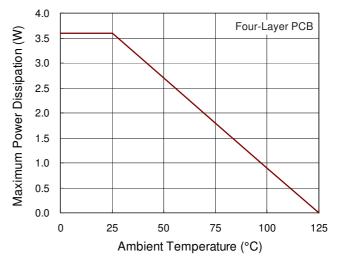

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                                       |

| WQFN-32L 4x4                                   | · 3.59W                                               |

| Package Thermal Resistance (Note 2)            |                                                       |

| WQFN-32L 4x4, $\theta_{JA}$                    | · 27.8°C/W                                            |

| WQFN-32L 4x4, $\theta_{JC}$                    | · 7°C/W                                               |

| Junction Temperature                           | - 150°C                                               |

| Lead Temperature (Soldering, 10 sec.)          | · 260°C                                               |

| Storage Temperature Range                      | <ul> <li>−65°C to 150°C</li> </ul>                    |

| ESD Susceptibility (Note 3)                    |                                                       |

| HBM (Human Body Model)                         | · 2kV                                                 |

| MM (Machine Model)                             | · 200V                                                |

### Recommended Operating Conditions (Note 4)

| Supply Input Voltage Range, VIN | 4.3V to 12V    |

|---------------------------------|----------------|

| Junction Temperature Range      | –40°C to 125°C |

| Ambient Temperature Range       | –40°C to 85°C  |

### **Electrical Characteristics**

(V\_BATS = 3.6V  $\pm$  5%, T\_A = 25°C, unless otherwise specified)

| Parameter                                                                               | Symbol     | ol Test Conditions                            |                                       |     | Тур   | Мах  | Unit |

|-----------------------------------------------------------------------------------------|------------|-----------------------------------------------|---------------------------------------|-----|-------|------|------|

| Input Currents                                                                          |            |                                               |                                       |     |       |      |      |

| Battery Discharge Current in<br>High Impedance Mode<br>(ISENL, ISENR, LX, BATS<br>Pins) | Idischarge | VBATS = 4.2 V                                 | High impedance mode,<br>SDA = SCL = 0 |     | 2     | 30   | μΑ   |

| VIN Supply Ouwent                                                                       | lq         |                                               | Charger PWM ON                        |     | 10000 | ^    |      |

| VIN Supply Current                                                                      |            | $V_{IN} > V_{IN(MIN)}$                        | Charger PWM OFF                       |     |       | 5000 | μΑ   |

| Voltage Regulation                                                                      |            |                                               |                                       |     |       |      |      |

| Output Charge Voltage                                                                   | Voreg      | Operating in voltage regulation, programmable |                                       | 3.5 |       | 4.44 | V    |

| Voltage Regulation<br>Accuracy                                                          |            | 0 to 85°C                                     | -1                                    |     | 1     | %    |      |

## **RT9451**

| Parameter                                        | Parameter Symbol Test Condition |                                                                                                                                                              | Min  | Тур | Мах  | Unit |

|--------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| Current Regulation Fast Charg                    | ge                              |                                                                                                                                                              |      |     | •    | •    |

| Output Charge Current                            | ICHRG                           | $\label{eq:VSHORT} \begin{array}{l} V_{SHORT} \leq V_{BATS} < V_{OREG} \\ V_{IN} > 5V, \ R_{SENSE} = 20m\Omega, \\ LOW\_CHG = 0, \ programmable \end{array}$ | 1000 |     | 4000 | mA   |

|                                                  |                                 | $\label{eq:VBATS} \begin{array}{l} V_{BATS} < V_{OREG}, \ V_{IN} > 5V, \\ R_{SENSE} = 20m\Omega, \ LOW\_CHG = 1 \end{array}$                                 |      | 150 |      |      |

| <b>Charge Termination Detection</b>              | l                               |                                                                                                                                                              |      |     |      |      |

| Termination Charge Current                       | I <sub>EOC</sub>                | $V_{BATS} > V_{OREG} - V_{RECH}, V_{IN} > 5V,$<br>RSENSE = 20m $\Omega$ , programmable                                                                       | 50   | -   | 400  | mA   |

| Deglitch Time for Charge<br>Termination          |                                 | Both Rising and Falling, 2mV<br>Overdrive, t <sub>RISE</sub> , t <sub>FALL</sub> = 100ns                                                                     |      | 43  |      | μs   |

| Charge Current Accuracy                          |                                 |                                                                                                                                                              |      |     |      |      |

| Offset Voltage, Sense Voltage<br>Amplifier       |                                 | $\label{eq:VSHORT} \begin{array}{l} V_{SHORT} \leq V_{BATS} < V_{OREG} \\ V_{IN} > 5V, \ R_{SENSE} = 20m\Omega, \\ LOW\_CHG = 0, \ programmable \end{array}$ | -1   |     | 1    | mV   |

| BAD Adaptor Detection                            |                                 |                                                                                                                                                              |      |     |      |      |

| Input Voltage Lower Limit                        | VIN(MIN)                        | Bad adaptor detection, VIN falling                                                                                                                           | 3.5  | 3.7 | 3.9  | V    |

| Deglitch Time for VIN Rising above $V_{IN(MIN)}$ |                                 | Rising voltage, 2mV over drive,<br>t <sub>RISE</sub> = 100ns                                                                                                 |      | 30  |      | ms   |

| Hysteresis for $V_{IN(MIN)}$                     | $\Delta V_{IN(MIN)}$            | V <sub>IN</sub> rising                                                                                                                                       | 100  |     | 200  | mV   |

| Current Source to GND                            |                                 | During bad adaptor detection                                                                                                                                 | 20   | 30  | 40   | mA   |

| Detection Interval                               | TINT                            | Input power source detection                                                                                                                                 |      | 2   |      | s    |

| Minimum Input Voltage Regula                     | ation                           |                                                                                                                                                              |      |     |      |      |

| Minimum Input Voltage<br>Regulation Threshold    | V <sub>MIVR</sub>               | Charge mode, programmable                                                                                                                                    | 4.2  | -   | 4.76 | V    |

| V <sub>MIVR</sub> Accuracy                       |                                 |                                                                                                                                                              | -2   |     | 2    | %    |

| Active Input Current Regulation                  | on                              |                                                                                                                                                              |      |     |      |      |

| AICR                                             |                                 | AICR = 100mA                                                                                                                                                 | 80   | 90  | 100  | mA   |

| AICh                                             |                                 | AICR = 500mA                                                                                                                                                 | 400  | 450 | 500  | ШA   |

| VDDP Regulator                                   |                                 |                                                                                                                                                              |      |     |      |      |

| Internal Bias Regulator Voltage                  | V <sub>DDP</sub>                | $\label{eq:VIN} \begin{split} V_{IN} &> V_{IN(min)} \text{ or } V_{BATS} > V_{BATMIN}, \\ I_{VDDP} &= 1mA, \ C_{VDDP} = 1 \mu F \end{split}$                 | 2    | -   | 6    | V    |

| VDDP Output Short Current<br>Limit               |                                 |                                                                                                                                                              |      | 60  |      | mA   |

| Voltage from BOOT to LX Pin                      |                                 | During charge or boost operation                                                                                                                             |      |     | 6    | V    |

| Battery Recharge Threshold                       | 1                               | 1                                                                                                                                                            |      |     | I    |      |

| Recharge Threshold Voltage                       | VRECH                           | Below VOREG                                                                                                                                                  | 100  | 130 | 160  | mV   |

| Deglitch Time                                    |                                 | V <sub>BATS</sub> decreasing below threshold,<br>t <sub>FALL</sub> = 100ns, 10mV overdrive                                                                   |      | 130 |      | ms   |

## **RT9451**

| Parameter                                                          |              | Symbol                | Test Conditions                                                                  | Min  | Тур  | Max  | Unit |

|--------------------------------------------------------------------|--------------|-----------------------|----------------------------------------------------------------------------------|------|------|------|------|

| Stat Output                                                        |              |                       |                                                                                  |      |      |      |      |

| Low Level Output Sa<br>Voltage                                     | aturation    |                       | I <sub>O</sub> = 10mA, Sink Current                                              |      |      | 0.4  | V    |

| High Level Leakage                                                 | Current      |                       | Voltage on STAT pin is 5V                                                        |      |      | 1    | μA   |

| <b>Reverse Protection</b>                                          | Comparat     | or                    |                                                                                  |      |      |      |      |

| Reverse Protection $\overline{V_{IN} - V_{BATS}}$                  | Threshold,   | V <sub>SLP</sub>      | $2.3V \le V_{BATS} \le V_{OREG}$ , VIN Falling                                   | 0    | 40   | 100  | mV   |

| Reverse Protection I<br>Hysteresis                                 | Exit         | VSLP-EXIT             | $2.3V \le V_{BATS} \le V_{OREG}$                                                 | 40   | 100  | 200  | mV   |

| Deglitch Time for VII<br>above V <sub>SLP</sub> + V <sub>SLP</sub> |              |                       | Rising Voltage                                                                   |      | 30   |      | ms   |

| VIN UVLO                                                           |              |                       |                                                                                  |      |      |      |      |

| Under-Voltage Locko<br>Threshold                                   | out          | Vuvlo                 | VIN Rising                                                                       | 3.05 | 3.3  | 3.55 | v    |

| Under-Voltage Lock<br>Threshold Hysteresis                         |              | ΔV <sub>UVLO</sub>    | VIN falling from above $V_{\text{UVLO}}$                                         |      | 150  |      | mV   |

| PWM                                                                |              |                       |                                                                                  |      |      |      |      |

| Internal N-MOSFET                                                  | High-Side    | RDSON_UG              | AICR = None, from VIN to LX                                                      |      | 80   | 160  |      |

| On-Resistance                                                      | Low-Side     | RDSON_LG              | from LX to PGND                                                                  |      | 60   | 120  | mΩ   |

| Maximum Duty Cycl                                                  | e            | D <sub>MAX</sub>      |                                                                                  |      | 99.5 |      | %    |

| Minimum Duty Cycle                                                 | 9            | D <sub>MIN</sub>      |                                                                                  | 0    |      |      | %    |

| Boost Mode Opera                                                   | tion for VIN |                       |                                                                                  |      |      |      |      |

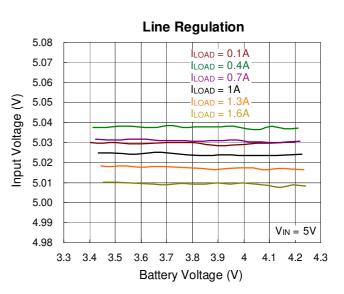

| Boost Output Voltag                                                | e Accuracy   |                       | $2.5V < V_{IN} < 4.5V$ ; Including line and load regulation over full temp range | -5   |      | 5    | %    |

| Maximum Output Cu<br>Boost                                         | urrent for   |                       | $V_{IN_B} = 5V, 2.5V < V_{BATS} < 4.5V$                                          | 1600 |      |      | mA   |

| Cycle-by-Cycle Curr<br>for Boost                                   | ent Limit    |                       | $V_{IN_B} = 5V, 2.5V < V_{BATS} < 4.5V$                                          | 4    | 6    | 8    | A    |

| Over-Voltage Protec<br>Threshold for Boost                         |              | VIN_BOVP              | Threshold over VIN to turn off<br>converter during boost                         | 5.6  | 6    | 6.3  | v    |

| Over-Voltage Protection<br>Hysteresis                              |              | $\Delta V_{IN\_BOVP}$ | $V_{IN}$ falling from above $V_{IN_BOVP}$                                        |      | 200  |      | mV   |

| Maximum Battery Voltage for , Boost                                |              | VBATMAX               | VBATS rising edge during boost                                                   | 4.5  | 4.75 | 5    | V    |

| Maximum Battery Vo<br>Hysteresis                                   | oltage       | $\Delta V_{BATMAX}$   | V <sub>BATS</sub> falling from above V <sub>BATMAX</sub>                         |      | 200  |      | mV   |

| Minimum Battery Vo                                                 | Itage for    | Voaten                | During boosting                                                                  |      | 2.5  |      | v    |

| Boost (BATS pin)                                                   | -            | VBATMIN               | Before boost Starts                                                              |      | 2.9  | 3.05 | v    |

## **RT9451**

| Parameter                                | Symbol                          | Test Conditions                                                                                                | Min | Тур | Max | Unit |

|------------------------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Charger Protection                       |                                 |                                                                                                                |     |     |     | •    |

| Input VIN Threshold Voltage              | VIN_OVP                         | Threshold over V <sub>IN</sub> to turn off converter during charge                                             | 11  | 12  | 13  | V    |

| V <sub>IN</sub> Hysteresis               |                                 | $V_{\text{IN}}$ falling from above $V_{\text{IN}\_\text{OVP}}$                                                 |     | 140 |     | mV   |

| Battery OVP Threshold Voltage            | VOVP_BATS                       | V <sub>BATS</sub> threshold over V <sub>OREG</sub> to turn<br>off charger during charge (% V <sub>OREG</sub> ) | 110 | 117 | 121 | %    |

| OVP Hysteresis                           | $\Delta \text{OVP}_\text{BATS}$ | Lower limit for V <sub>BATS</sub> falling from > VOVP (% VOREG)                                                |     | 11  |     | %    |

| Cycle-by-Cycle Current Limit for Charge  | I <sub>LIMIT</sub>              | Charge mode operation                                                                                          | 5   | 7   | 9   | А    |

| Trickle to Fast Charge<br>Threshold      | V <sub>SHORT</sub>              | $V_{\text{BATS}}$ rising, $V_{\text{SHORT}}$ connected to $V_{\text{DDP}}$                                     | 1.9 | 2.1 | 2.2 | v    |

| VSHORT Hysteresis                        | $\Delta V_{SHORT}$              | VBATS falling from above VSHORT                                                                                |     | 100 |     | mV   |

| Trickle Charge Charging<br>Current       | ISHORT                          | VBATS ≤ VSHORT                                                                                                 | 70  | 80  | 90  | mA   |

| Thermal Regulation Threshold             |                                 | Charge current begins to taper down                                                                            |     | 120 |     | °C   |

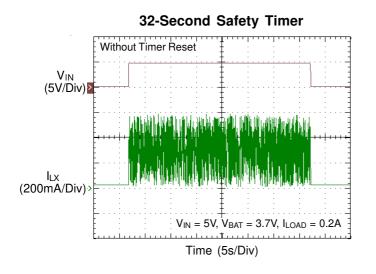

| Time Constant for the<br>32-Second Timer | T <sub>32S</sub>                | 32 Second Mode                                                                                                 |     | 32  |     | s    |

| LDO                                      |                                 |                                                                                                                |     |     |     | •    |

| LDO Output Voltage                       | V <sub>LDO</sub>                | $V_{IN} = 5.5V$                                                                                                | 4.8 | 4.9 | 5   | V    |

| PSRR                                     |                                 | $f = 100Hz, C_{LDO} = 1\mu F$                                                                                  |     | 60  |     | dB   |

| Maximum LDO Output Current               | Ildo                            |                                                                                                                | 60  |     |     | mA   |

| Dropout Voltage                          | Vdo                             | $V_{IN} = 4.5V$ , $I_{LDO} = 50mA$                                                                             |     | 100 | 250 | mV   |

| D+ / D Detection                         |                                 |                                                                                                                |     |     |     |      |

| D+ Voltage Source                        | $V_{DP\_SCR}$                   |                                                                                                                | 0.5 | 0.6 | 0.7 | V    |

| D+ Voltage Source Output<br>Current      |                                 |                                                                                                                | 250 |     |     | μA   |

| D– Current Sink                          | Idm_sink                        |                                                                                                                | 50  | 100 | 150 | μA   |

| Input Capacitance                        | Cı                              | DM pin, switch open                                                                                            |     | 4.5 | 5   | рF   |

| input Capacitance                        | 5                               | DP pin, switch open                                                                                            |     | 4.5 | 5   | pr   |

| Input Leakage                            | lı                              | DM pin, switch open                                                                                            | -1  |     | 1   | μA   |

| Input Leakage                            | ц.                              | DP pin, switch open                                                                                            | -1  |     | 1   | μΛ   |

| DP Low Comparator Threshold              | Vdp_low                         |                                                                                                                | 0.8 |     |     | V    |

| DM High Comparator<br>Threshold          | V <sub>DM_HIGH</sub>            |                                                                                                                | 0.8 |     |     | v    |

| DM Low Comparator Threshold              | V <sub>DM_LOW</sub>             |                                                                                                                |     |     | 475 | mV   |

| Logic Levels and Timing Char             | acteristics (                   | SCL, SDA, INT)                                                                                                 |     |     |     |      |

| Output Low Threshold Level               | Vol                             | $I_0 = 3mA$ , Sink Current (SDA, INT)                                                                          |     |     | 0.4 | V    |

| Input Low Threshold Level                |                                 |                                                                                                                |     |     | 0.4 | V    |

| Parameter                          | Symbol              | Test Conditions        | Min | Тур | Max | Unit |

|------------------------------------|---------------------|------------------------|-----|-----|-----|------|

| Input High Threshold Level         |                     |                        | 1.2 |     |     | V    |

| Input Bias Current (SCL, SDA, INT) | I <sub>(bias)</sub> | V <sub>IO</sub> = 1.8V |     |     | 1   | μA   |

| SCL Clock Frequency                | fscl                |                        |     |     | 400 | kHz  |

| Oscillator                         |                     | •                      |     |     |     |      |

| Oscillator Frequency               | fosc                |                        |     | 375 |     | kHz  |

| Frequency Accuracy                 |                     |                        | -10 |     | 10  | %    |

| Thermal Shutdown                   |                     | •                      |     |     |     |      |

| Thermal Shutdown Threshold         | T <sub>SD</sub>     |                        |     | 165 |     | °C   |

| Thermal Shutdown Hysteresis        | $\Delta T_{SD}$     |                        |     | 10  |     | °C   |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

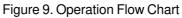

### **Typical Application Circuit**

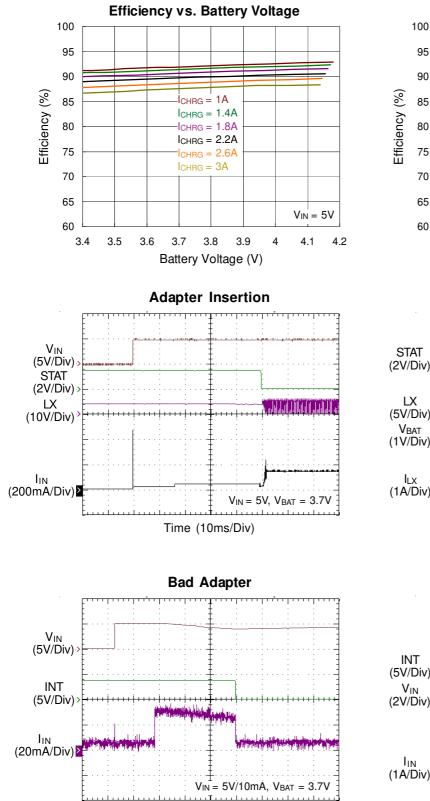

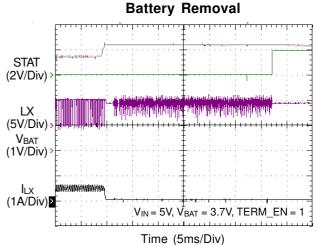

#### **Typical Operating Characteristics Charge Mode**

Copyright @2017 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

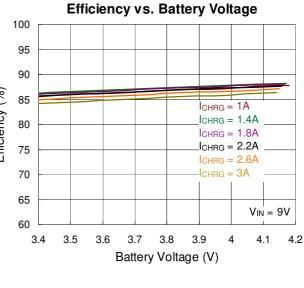

#### **Boost Mode**

### **Application Information**

The RT9451 is an integrated solution of single-cell Li-ion and Li-polymer battery charger for portable applications. The part integrates a synchronous PWM controller with power MOSFETs to provide MIVR (Minimum Input Voltage Regulation), input current sensing, high accuracy current and voltage regulation, and charge termination in a small package for space limited devices. The part also features USB OTG (On-The-Go) function and USB charger detection (DPDM detection) function.

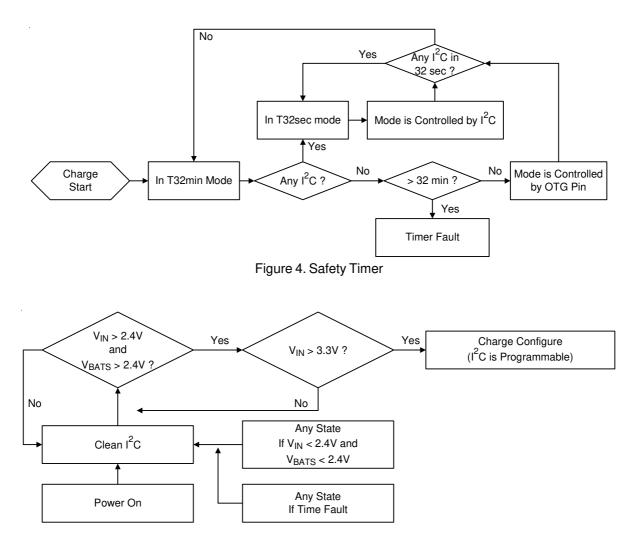

The RT9451 provides three operation modes : charge mode, boost mode (USB OTG), and high impedance mode. In charge mode, the RT9451 supports a precision charging system for single cell. In boost mode, the RT9451 works as a Boost converter and boosts the voltage from battery to VIN pin for sourcing the OTG devices. In high impedance mode, the RT9451 stops charging or boosting and operates in a mode with low quiescent current from V<sub>IN</sub> or battery to reduce the power consumption when the portable device is in standby mode.

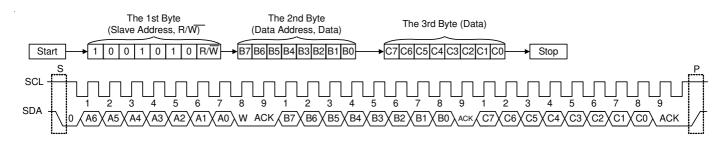

In charge mode, the RT9451 integrates USB charger detection for input current limit of 500mA and 1A. The detection is automatically triggered after each POR. The detection result can be ignored by the host via I<sup>2</sup>C interface. The slave address for the RT9451 is "1001010".

#### I<sup>2</sup>C Interface Timing Diagram

The RT9451 acts as an  $I^2C$  -bus slave. The  $I^2C$ -bus master configures the settings for charge mode and boost mode by sending command bytes to the RT9451 via the 2-wire  $I^2C$ -bus. After the START condition, the  $I^2C$  master sends a chip address. This address is seven bits long followed by an eighth bit which is a data direction bit (R/W). The second byte selects the register to which the data will be written. The third byte contains data to the selected register.

S = Start Condition W = Write (SDA = "0") R = Read (SDA = "1") ACK = Acknowledge P = Stop Condition

#### I<sup>2</sup>C Information

#### Slave Address : 1001010

|          | Table 1. Register Address Map |          |               |                                |  |  |  |

|----------|-------------------------------|----------|---------------|--------------------------------|--|--|--|

| Register | Address (Hex)                 | Name     | Default Value | Description                    |  |  |  |

| 0        | 0                             | CONTROL  | 0000 1010     | Enable control register        |  |  |  |

| 1        | 1                             | CONFIG_A | 0000 0001     | Charger current register       |  |  |  |

| 2        | 2                             | CONFIG_B | 0001 1001     | Charger voltage register       |  |  |  |

| 3        | 3                             | CONFIG_C | 0000 0010     | Special charger settings       |  |  |  |

| 4        | 4                             | CONFIG_D | 0100 0000     | Charger safety limits settings |  |  |  |

| 6        | 6                             | STATUS_A | 0000 0000     | Status register A              |  |  |  |

| 7        | 7                             | STATUS_B | 0000 0001     | Status register B              |  |  |  |

| 8        | 8                             | INT1     | 0000 0000     | Interrupt bits                 |  |  |  |

| 9        | 9                             | INT2     | 0000 0000     | Interrupt bits (charger)       |  |  |  |

| 10       | 0A                            | INT3     | 0000 0000     | Interrupt bits (boost)         |  |  |  |

| 11       | 0B                            | MASK1    | 0000 0000     | Interrupt masking bits         |  |  |  |

| 12       | 0C                            | MASK2    | 0000 0000     | Interrupt masking bits         |  |  |  |

| 13       | 0D                            | MASK3    | 0000 0000     | Interrupt masking bits         |  |  |  |

| 14       | 0E                            | CHIPID   | 0000 0001     | Chip ID register               |  |  |  |

#### **Control Register (Control)**

Address - 0x00h

| Data Bit    | D7     | D6       | D5       | D4       | D3     | D2      | D1   | D0      |

|-------------|--------|----------|----------|----------|--------|---------|------|---------|

| Field Name  | STAT_I | EN [1:0] | Not Used | Not Used | LDO_EN | DPDM_EN | CH_E | N [1:0] |

| Read/Write  | R/W    | R/W      | R/W      | R/W      | R/W    | R/W     | R/W  | R/W     |

| Reset Value | 0      | 0        | 0        | 0        | 1      | 0       | 1    | 0       |

| Field Name    | Bit Definition                                                  |  |  |  |  |

|---------------|-----------------------------------------------------------------|--|--|--|--|

|               | STAT enable bits                                                |  |  |  |  |

|               | 00 – AUTO (controlled by charger status)                        |  |  |  |  |

| STAT_EN [1:0] | 01 – ON (low impedance)                                         |  |  |  |  |

|               | 10 – OFF (high impedance)                                       |  |  |  |  |

|               | 11 – not defined                                                |  |  |  |  |

|               | LDO enable bit                                                  |  |  |  |  |

| LDO_EN        | 0 – Disabled                                                    |  |  |  |  |

|               | 1 – Enabled                                                     |  |  |  |  |

|               | D+/D- detection enable                                          |  |  |  |  |

| DPDM EN       | 0 – Disabled                                                    |  |  |  |  |

|               | 1 – Enabled                                                     |  |  |  |  |

|               | Note : Bit is automatically reset after detection is completed. |  |  |  |  |

|               | Charger enable bits                                             |  |  |  |  |

| CH_EN [1:0]   | 00 – Disabled / HiZ mode                                        |  |  |  |  |

|               | 01 – Boost mode                                                 |  |  |  |  |

|               | 10 – Charge                                                     |  |  |  |  |

|               | 11 – Charge with automatic recharge                             |  |  |  |  |

#### Charger CONFIG Register A (CONFIG\_A)

Address - 0x01h

| Data Bit    | D7     | D6           | D5  | D4  | D3  | D2           | D1  | D0  |

|-------------|--------|--------------|-----|-----|-----|--------------|-----|-----|

| Field Name  | LMTSEL | VICHRG [3:0] |     |     |     | VITERM [2:0] |     |     |

| Read/Write  | R/W    | R/W          | R/W | R/W | R/W | R/W          | R/W | R/W |

| Reset Value | 0      | 0            | 0   | 0   | 0   | 0            | 0   | 1   |

| Field Name   | Bit Definition <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LMTSEL       | Input current limit selection<br>0 – Input current limit is set to the higher of AICR [1:0] (CONFIG_B) and D+D– det.<br>result<br>1 – AICR [1:0] (CONFIG_B) applied, D+D– detection result is ignored                                                                                                                                                                                                                                                            |

| VICHRG [3:0] | Charge current sense voltage (current equivalent for 20mΩ shunt)<br>0000 – 20mV (1000mA)<br>0001 – 24mV (1200mA)<br>0010 – 28mV (1400mA)<br>0011 – 32mV (1600mA)<br>0100 – 36mV (1800mA)<br>0101 – 40mV (2000mA)<br>0110 – 44mV (2200mA)<br>0111 – 48mV (2400mA)<br>1000 – 52mV (2600mA)<br>1001 – 56mV (2800mA)<br>1001 – 66mV (3000mA)<br>1011 – 64mV (3200mA)<br>1100 – 68mV (3400mA)<br>1101 – 72mV (3600mA)<br>1110 – 76mV (3800mA)<br>1111 – 80mV (4000mA) |

| VITERM [2:0] | Termination current sense voltage (current equivalent for $20m\Omega$ shunt) $000 - 1mV (50mA)$ $001 - 2mV (100mA)$ $010 - 3mV (150mA)$ $011 - 4mV (200mA)$ $100 - 5mV (250mA)$ $101 - 6mV (300mA)$ $110 - 7mV (350mA)$ $111 - 8mV (400mA)$                                                                                                                                                                                                                      |

(1) During charging the lower value of VMCHRG [3:0] (CONFIG\_D register) and VICHRG [2:0] applies.

| Copyright@2017 Richtek Technology Corporation. All rights reserved. | <b>RICHTEK</b> is a registered trademark of Richtek Technology Corporation. |

|---------------------------------------------------------------------|-----------------------------------------------------------------------------|

| www.richtek.com                                                     | DS9451-01 March 2017                                                        |

| 10                                                                  |                                                                             |

#### Charger CONFIG Register B (CONFIG\_B)

Address - 0x02h

| Data Bit    | D7         | D6  | D5          | D4  | D3  | D2  | D1  | D0  |  |

|-------------|------------|-----|-------------|-----|-----|-----|-----|-----|--|

| Field Name  | AICR [1:0] |     | VOREG [5:0] |     |     |     |     |     |  |

| Read/Write  | R/W        | R/W | R/W         | R/W | R/W | R/W | R/W | R/W |  |

| Reset Value | 0          | 0   | 0           | 1   | 1   | 0   | 0   | 1   |  |

| Field Name  | Bit Definition <sup>(1)</sup>                                                                                                                                                                                                                                 |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AICR [1:0]  | Input current limit setting<br>00 – 100mA<br>01 – 500mA<br>11 – No input current limit                                                                                                                                                                        |

| VOREG [5:0] | Battery regulation voltage / boost output voltage<br>00 0000 - 3.50V / 4.425V<br>00 0001 - 3.52V / 4.448V<br>00 0011 - 3.56V / 4.471V<br><br>01 1000 - 3.98V / 4.977V<br>01 1001 - 4.00V / 5V<br>01 1010 - 4.02V / 5.023V<br><br>10 1111 - 4.44V / 5.506V<br> |

|             | 11 1111 – 4.44V / 5.506V                                                                                                                                                                                                                                      |

(1) During charging the lower value of VMCHRG [3:0] (CONFIG\_D register) and VICHRG [5:0] applies.

#### Charger CONFIG Register C (CONFIG\_C)

Address - 0x03h

| Data Bit    | D7       | D6     | D5     | D4      | D3      | D2         | D1  | D0  |

|-------------|----------|--------|--------|---------|---------|------------|-----|-----|

| Field Name  | Not Used | OTG_PL | OTG_EN | TERM_EN | LOW_CHG | MIVR [2:0] |     |     |

| Read/Write  | R/W      | R/W    | R/W    | R/W     | R/W     | R/W        | R/W | R/W |

| Reset Value | 0        | 0      | 0      | 0       | 0       | 0          | 1   | 0   |

| Field Name | Bit Definition                                                                                                                                                |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OTG_PL     | OTG pin polarity<br>0 – Active low<br>1 – Active high                                                                                                         |

| OTG_EN     | OTG pin enable<br>0 – Pin is disabled<br>1 – Pin is enabled                                                                                                   |

| TERM_EN    | Charge termination enable<br>0 – Disabled<br>1 – Enabled                                                                                                      |

| LOW_CHG    | Low charge current enable bit (current equivalent for $20m\Omega$ shunt)<br>0 – Normal charge current sense voltage per register CONFIG_A<br>1 – 3mV (150mA)  |

| MIVR [2:0] | Input voltage MIVR regulation voltage<br>000 - 4.20V<br>001 - 4.28V<br>010 - 4.36V<br>011 - 4.44V<br>100 - 4.52V<br>101 - 4.60V<br>110 - 4.68V<br>111 - 4.76V |

#### Charger CONFIG Register D (CONFIG\_D)

Address - 0x04h

| Data Bit    | D7           | D6  | D5  | D4  | D3          | D2  | D1  | D0  |  |

|-------------|--------------|-----|-----|-----|-------------|-----|-----|-----|--|

| Field Name  | VMCHRG [3:0] |     |     |     | VMREG [3:0] |     |     |     |  |

| Read/Write  | R/W          | R/W | R/W | R/W | R/W         | R/W | R/W | R/W |  |

| Reset Value | 0            | 1   | 0   | 0   | 0           | 0   | 0   | 0   |  |

| Field Name   | Bit Definition <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VMCHRG [3:0] | Maximum charge current sense voltage (current equivalent for 20mΩ shunt)           0000 – 20mV (1000mA)           0001 – 24mV (1200mA)           0010 – 28mV (1400mA)           0011 – 32mV (1600mA)           0100 – 36mV (1800mA)           0101 – 40mV (2000mA)           0110 – 44mV (2200mA)           0111 – 48mV (2400mA)           1000 – 52mV (2600mA)           1001 – 56mV (2800mA)           1010 – 60mV (3000mA)           1011 – 64mV (3200mA)           1110 – 68mV (3400mA)           1101 – 72mV (3600mA)           1110 – 76mV (3800mA)           1111 – 80mV (4000mA) |

| VMREG [3:0]  | Maximum Battery Regulation Voltage / Maximum OTG Regulation Voltage<br>0000 - 4.20V / 5.230V<br>0001 - 4.22V / 5.253V<br>0010 - 4.24V / 5.276V<br><br>1100 - 4.44V / 5.506V<br><br>1111 - 4.44V / 5.506V                                                                                                                                                                                                                                                                                                                                                                                 |

#### STATUS Register A (STATUS\_A)

Address - 0x06h

| Data Bit    | D7       | D6      | D5       | D4           | D3 | D2 | D1  | D0       |

|-------------|----------|---------|----------|--------------|----|----|-----|----------|

| Field Name  | Not Used | STANDBY | Not Used | CHSTAT [2:0] |    |    | LDO | Not Used |

| Read/Write  | R        | R       | R        | R            | R  | R  | R   | R        |

| Reset Value | 0        | 0       | 0        | 0            | 0  | 0  | 0   | 0        |

| Field Name   | Bit Definition <sup>(1)</sup>                                                                                                                                                                                                                                 |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Not used     | N/A                                                                                                                                                                                                                                                           |

| STANDBY      | Standby status indicator<br>0 – Device is in ACTIVE mode<br>1 – Device is in STANDBY mode                                                                                                                                                                     |

| Not used     | N/A                                                                                                                                                                                                                                                           |

| CHSTAT [2:0] | Charger status bit<br>000 – High impedance mode or ready to charge<br>001 – Charge in progress (fast charge)<br>010 – Charge done<br>011 – Boost mode<br>100 – Charge in progress (pre charge)<br>101 – Not defined<br>110 – Not defined<br>111 – Not defined |

| LDO          | LDO status bit<br>0 – LDO is disabled (OFF)<br>1 – LDO is enabled (ON), no fault                                                                                                                                                                              |

| Not used     | N/A                                                                                                                                                                                                                                                           |

(1) Default values reflect state after Power On Reset, no charger plugged in, no faults present.

#### STATUS Register B (STATUS\_B)

Address - 0x07h

| Data Bit    | D7    | D6       | D5       | D4       | D3       | D2     | D1     | D0  |

|-------------|-------|----------|----------|----------|----------|--------|--------|-----|

| Field Name  | RESET | Not used | Not used | Not used | Not used | DPDM_D | DPDM_R | OTG |

| Read/Write  | W     | R        | R        | R        | R        | R      | R      | R   |

| Reset Value | 0     | 0        | 0        | 0        | 0        | 0      | 0      | 1   |

| Field Name | Bit Definition <sup>(1)</sup>                                                                                                            |

|------------|------------------------------------------------------------------------------------------------------------------------------------------|

|            | Reset                                                                                                                                    |

| RESET      | 0 – No effect                                                                                                                            |

| HEGET      | 1 – Reset all parameters to default values                                                                                               |

|            | Note : Read always returns "0"                                                                                                           |

| Not used   | N/A                                                                                                                                      |

| DPDM_D     | D+/D- detection done bit<br>0 – DPDM detection in progress or not started after initial power up reset<br>1 – DPDM detection is complete |

| DPDM_R     | D+D– detection result<br>0 – Standard USB port (500mA current limit)<br>1 – USB charger (975mA current limit)                            |

| отд        | OTG pin status<br>0 – OTG pin at low level<br>1 – OTG pin at high level                                                                  |

(1) Default values reflect state after Power On Reset, no charger plugged in, no faults present, OTG pin high.

#### Interrupt Register 1 (INT1)

Address - 0x08h

| Data Bit    | D7   | D6      | D5       | D4       | D3       | D2       | D1       | D0       |

|-------------|------|---------|----------|----------|----------|----------|----------|----------|

| Field Name  | TSDI | VINOVPI | Not used |

| Read/Write  | R    | R       | R        | R/W      | R/W      | R/W      | R/W      | R        |

| Reset Value | 0    | 0       | 0        | 0        | 0        | 0        | 0        | 0        |

| Field Name | Bit Definition                                                                                                                                      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| TSDI       | Thermal shutdown fault. Set if die temperature exceeds thermal shutdown threshold.<br>Reset when die temperature drops below TSD release threshold. |

| VINOVPI    | VIN over-voltage protection. Set when VIN > VIN_OVP is detected.                                                                                    |

| Not used   | N/A                                                                                                                                                 |

#### Interrupt Register 2 (INT2)

Address - 0x09h

| Data Bit    | D7     | D6     | D5       | D4      | D3      | D2     | D1      | D0      |

|-------------|--------|--------|----------|---------|---------|--------|---------|---------|

| Field Name  | CHRVPI | CHBADI | CHBATOVI | CHTERMI | CHRCHGI | CH32MI | CHTREGI | CHMIVRI |

| Read/Write  | R      | R      | R        | R       | R       | R      | R       | R       |

| Reset Value | 0      | 0      | 0        | 0       | 0       | 0      | 0       | 0       |

| Field Name | Bit Definition <sup>(1)</sup>                                                                   |

|------------|-------------------------------------------------------------------------------------------------|

| CHRVPI     | Charger fault. Reverse protection (VIN > $V_{IN(MIN)}$ and VIN < $V_{BATS}$ + $V_{SLP}$ (fault) |

| CHBADI     | Charger fault. Bad adaptor (VIN < $V_{IN(MIN)}$ during power on detection)                      |

| CHBATOVI   | Charger fault. Battery OVP                                                                      |

| CHTERMI    | Charge terminated                                                                               |

| CHRCHGI    | Recharge request (VBATS < VOREG - VRECH)                                                        |

| CH32MI     | Charger fault. 32 minutes time-out                                                              |

| CHTREGI    | Charger warning. Thermal regulation loop active.                                                |

| CHMIVRI    | Charger warning. Input voltage MIVR loop active.                                                |

(1) All charger faults result in disabling the charger (CH\_EN [1:0] = 00). Recharge request disables the charger only if CH\_EN [1:0] = 10.

#### Interrupt Register 3 (INT3)

Address - 0x0Ah

| Data Bit    | D7        | D6     | D5       | D4        | D3      | D2          | D1          | D0          |

|-------------|-----------|--------|----------|-----------|---------|-------------|-------------|-------------|

| Field Name  | BSTVINOVI | BSTOLI | BSTLOWVI | BSTBATOVI | BST32SI | Not<br>used | Not<br>used | Not<br>used |

| Read/Write  | R         | R      | R        | R         | R       | R           | R           | R           |

| Reset Value | 0         | 0      | 0        | 0         | 0       | 0           | 0           | 0           |

| Field Name | Bit Definition <sup>(1)</sup>            |

|------------|------------------------------------------|

| BSTVINOVI  | Boost fault. VIN OVP (VIN > VIN_BOVP)    |

| BSTOLI     | Boost fault. Over load.                  |

| BSTLOWVI   | Boost fault. Battery voltage is too low. |

| BSTBATOVI  | Boost fault. Battery over voltage.       |

| BST32SI    | Boost fault. 32s time-out fault.         |

| Not used   | N/A                                      |

| Not used   | N/A                                      |

| Not used   | N/A                                      |

(1) All charger faults result in disabling the charger (CH\_EN [1:0] = 00).

#### Interrupt MASK Register 1 (MASK1)

Address - 0x0Bh

| Data Bit    | D7   | D6      | D5       | D4       | D3       | D2       | D1       | D0       |

|-------------|------|---------|----------|----------|----------|----------|----------|----------|

| Field Name  | TSDM | VINOVPM | Not used |

| Read/Write  | R/W  | R/W     | R/W      | R/W      | R/W      | R/W      | R/W      | R/W      |

| Reset Value | 0    | 0       | 0        | 0        | 0        | 0        | 0        | 0        |

| Field Name | Bit Definition <sup>(1)</sup> |

|------------|-------------------------------|

|            | TSD fault interrupt mask      |

| TSDM       | 0 – Interrupt not masked      |

|            | 1 – Interrupt masked          |

|            | VIN OVP fault interrupt mask  |

| VINOVPM    | 0 – Interrupt not masked      |

|            | 1 – Interrupt masked          |

| Not used   | N/A                           |

(1) Setting any of the interrupt mask bits does not disable protection circuits. When set, the respective fault will not be signaled on the INT pin.

#### Interrupt MASK Register 2 (MASK2)

Address - 0x0Ch

| Data           |        |        |          |         |         |        |         |         |

|----------------|--------|--------|----------|---------|---------|--------|---------|---------|

| Data<br>Bit    | D7     | D6     | D5       | D4      | D3      | D2     | D1      | D0      |

| Field<br>Name  | CHRVPM | CHBADM | CHBATOVM | CHTERMM | CHRCHGM | CH32MM | CHTREGM | CHMIVRM |

| Read/<br>Write | R/W    | R/W    | R/W      | R/W     | R/W     | R/W    | R/W     | R/W     |

| Reset<br>Value | 0      | 0      | 0        | 0       | 0       | 0      | 0       | 0       |

| Field Name | Bit Definition <sup>(1)</sup>                                                                             |

|------------|-----------------------------------------------------------------------------------------------------------|

| CHRVPM     | Charger reverse protection interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked             |

| CHBADM     | Charger Bad adaptor interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked                    |

| CHBATOVM   | Charger battery over voltage interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked           |

| CHTERMM    | Charge terminated interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked                      |

| CHRCHGM    | Charger recharge request interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked               |

| СН32ММ     | Charger 32m timeout interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked                    |

| CHTREGM    | Charger thermal regulation loop active interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked |

| CHMIVRM    | Charger input current MIVR active interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked      |

(1) Setting any of the interrupt mask bits does not disable protection circuits. When set, the respective fault will not be signaled on the INT pin.

#### Interrupt MASK Register 3 (MASK3)

Address - 0x0Dh

| Data Bit       | D7        | D6     | D5       | D4        | D3      | D2          | D1          | D0          |

|----------------|-----------|--------|----------|-----------|---------|-------------|-------------|-------------|

| Field Name     | BSTVINOVM | BSTOLM | BSTLOWVM | BSTBATOVM | BST32SM | Not<br>used | Not<br>used | Not<br>used |

| Read/Write     | R/W       | R/W    | R/W      | R/W       | R/W     | R/W         | R/W         | R/W         |

| Reset<br>Value | 0         | 0      | 0        | 0         | 0       | 0           | 0           | 0           |

| Field Name | Bit Definition <sup>(1)</sup>                                                                 |

|------------|-----------------------------------------------------------------------------------------------|

| BSTVINOVM  | Boost VIN over voltage interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked     |

| BSTOLM     | Boost over load interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked            |

| BSTLOWVM   | Boost low battery voltage interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked  |

| BSTBATOVM  | Boost battery over voltage interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked |

| BST32SM    | Boost 32s time out interrupt mask<br>0 – Interrupt not masked<br>1 – Interrupt masked         |

| Not used   | N/A                                                                                           |

| Not used   | N/A                                                                                           |

| Not used   | N/A                                                                                           |

(1) Setting any of the interrupt mask bits does not disable protection circuits. When set, the respective fault will not be signaled on the INT pin.

#### CHIP ID Register (CHIPID)

Address - 0x0Eh

| Data Bit    | D7 | D6     | D5         | D4 | D3             | D2 | D1 | D0 |

|-------------|----|--------|------------|----|----------------|----|----|----|

| Field Name  |    | VENDOR | R_ID [3:0] |    | CHIP_REV [3:0] |    |    |    |

| Read/Write  | R  | R      | R          | R  | R              | R  | R  | R  |

| Reset Value | 0  | 0      | 0          | 0  | 0              | 0  | 0  | 1  |

#### **Charge Mode Operation**

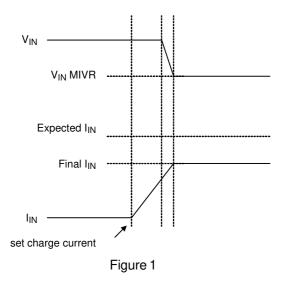

#### Minimum Input Voltage Regulation (MIVR)

The RT9451 features input voltage MIVR function to prevent input voltage drop due to insufficient current provided by the adaptor or USB input. If MIVR function is enabled, the input voltage decreases when the over current of the input power source occurs and is regulated at a predetermined voltage level which can be set from 4.20V to 4.76V with the step of 80mV by I<sup>2</sup>C interface to MIVR [2:0] in the register of address 0X03. The INT pin is pulled low to notify the host and the CHMIVR bit is set to high. At this time, the current drawn by the RT9451 equals to the maximum current value that the input power can provide at the predetermined voltage level, instead of the set value. And CHMIVR bit is set to "1" and INT pin is pulled low to notify the host. The MIVR function is initially set to 4.36V.

#### USB Power Source Detection (DPDM Detection)

An USB charger detection mechanism is integrated in RT9451 to detect between dedicated charger or not. The detection is triggered by VIN power on or DPDN\_EN bit in the register address of 0x00h. The DPDN\_EN bit is automatically reset to "0" after it is triggered. The DPDM detection status and result are reported in DPDM\_D DPDM\_R bits in the register address of 0x07h. The result is set to 975mA for dedicated charger (DP and DM pins short together) or 500mA for others. The detection mechanism can be disable by pulling VIO pin high.

#### Active Input Current Regulation (AICR)

The AICR setting is determined by both AICR [1:0] in register 0x02h, DPDM\_R bit in register 0x07h and LMTSEL bit in register 0x01h. If LMTSEL bit is set to "0", the valid current limit is the maximum value of AICR [1:0] and DPDM\_R result. If LMTSEL bit is set to "1", the AICR [1:0] dominates and DPDM\_R result is ignored. For the latter, the input current limit of "00", "01" and "10" in AICR [1:0] corresponds to 100mA, 500mA and 975mA respectively. If the application does not need input current limit, write "11" into the AICR [1:0].

#### **Charge Profile**

The RT9451 provides a precision Li-ion or Li-polymer charging solution for single-cell applications. Input current limit, charge current, termination current, charge voltage and input voltage MIVR are all programmable via the I<sup>2</sup>C interface. In charge mode, the RT9451 has five control loops to regulate input current, charge current, charge voltage, input voltage MIVR and device junction temperature. During the charging process, all five loops are enabled and the dominant one will take over the control.

For normal charging process, the Li-ion or Li-polymer battery is charged in three charging modes depending on the battery voltage. At the beginning of the charging process, the RT9451 is in pre-charge mode. When the battery voltage rises above pre-charge threshold voltage ( $V_{PREC}$ ), the RT9451 enters fast-charge mode. Once the battery voltage is close to the regulation voltage ( $V_{OREG}$ ), the RT9451 enters constant voltage mode.

#### **Pre-Charge Mode**

For life-cycle consideration, the battery can not be charged with large current under low battery condition. When the BATS pin voltage is below pre-charge threshold voltage ( $V_{PREC}$ ), the charger is in pre-charge mode with a weak charge current which equals to the pre-charge current ( $I_{PREC}$ ). In pre-charge mode, the charger basically works as an LDO. The pre-charge current also acts as the current limit when the BATS pin is shorted.

#### Fast-Charge Mode and Settings

As the BATS pin rises above  $V_{PREC}$ , the charger enters fast-charge mode and the power MOSFETs starts switching. Unlike the linear charger, the switching charger is a current amplifier. The current drawn by the RT9451 is different from the current into the battery. The user can set the input current limit ( $I_{IN\_LIMIT}$ ) and output charge current ( $I_{CHRG}$ ) respectively. The real charging current is determined by both IIN\\_LIMIT [1:0] and VICHRG [3:0].

#### Cycle-by-Cycle Current Limit

The charger of the RT9451 has an embedded cycle-bycycle current limit for inductor. Once the inductor current touches the threshold (5.5A min.), the charger stops charging immediately to prevent over current from damaging the device. Notice that, the mechanism can not be disabled by any way.

#### Low Current Charging (LOW\_CHG)

The RT9451 has two charge current settings for the charge current in fast-charge mode. One is LOW\_CHG bit, the other is VICHRG[3:0] bits. If LOW\_CHG is set to "1", the charge current is limited to 150mA ( $R_{SENSE} = 20m\Omega$ ). If LOW\_CHG is set to "0", the charge current is determined by VICHRG[3:0] bits.

#### Charge Current (I<sub>CHRG</sub>)

The charge current into the battery is determined by the sense resistor ( $R_{SENSE}$ ) and VICHRG [3:0] bits in the register of address 0x01. The voltage between the ISENL and ISENR pins is regulated to the voltage controlled by VICHRG [3:0]. The charge current equals to the voltage between the ISENL and ISENR pins ( $V_{ICHRG}$ ) divided by R<sub>SENSE</sub> :

$\mathsf{I}_{\mathsf{CHRG}} = \frac{\mathsf{V}_{\mathsf{I}\mathsf{CHRG}}}{\mathsf{R}_{\mathsf{SENSE}}}$

For example, for a  $20m\Omega$  sense resistor, the charge current can be set from 1000mA (VICHRG [3:0] = "0000") to 4000mA (VICHRG [3:0] = "1111").

When input current limit and charge current are both set, the charge current in fast charge phase is calculated as below :

| I <sub>CHRG</sub> = MIN | VICHRG,  |  |

|-------------------------|----------|--|

|                         | Rsense ' |  |

where D is the duty cycle and  $\eta$  is the efficiency.

#### **Constant Voltage Mode and Settings**

The RT9451 enters constant voltage mode when the BATS voltage is close to the output-charge voltage (V<sub>OREG</sub>). Once entering this mode, the charge current begins decreasing. For default settings (charge current termination is disabled, TERM\_EN = 0), the RT9451 does not turn off and always regulates the battery voltage at V<sub>OREG</sub>. However, once the charge current termination is enabled, the charger terminates if the charge current is below termination current (VITERM [2:0] / R<sub>SENSE</sub>) in constant-voltage mode. The charge current termination function is controlled by TERM\_EN bit in the register of address 0x01 via the  $l^2C$  interface. After termination, a new charge cycle restarts when one of the following conditions is detected :

- ➤ The BATS pin voltage falls below the V<sub>OREG</sub>-V<sub>RECH</sub> threshold and CH\_EN [1:0] = 11.

- VIN Power On Reset (POR).

- CH\_EN [1:0] is set from "0X" to "1X".

#### Output Charge Voltage (VOREG)

The output-charge voltage is set by the VOREG [5:0] in the register 0x02h. Its range is from 3.5V to 4.45V. The default is 4V (011001).

#### Termination Current (IEOC)

If the charger current termination is enabled (TERM\_EN = "1"), the end-of-charge current is determined by both the termination current sense voltage (VITERM [2:0]) and sense resistor ( $R_{SENSE}$ ). VITERM range is from 1mV to 8mV with the step of 1mV. The end-of-charge current is calculated as below :

$I_{EOC} = \frac{V_{ITERM}}{R_{SENSE}}$

#### **Recharge Behavior**

There are two recharge behavior depending on CH\_EN [1:0] setting. If CH\_EN [1:0] = "11", the RT9451 will recharge automatically once BATS falls below  $V_{OREG}$ - $V_{RECH}$  threshold. If CH\_EN [1:0] = "10", the RT9451 will not recharge automatically but set CHRECH flag and pull low INT pin to notify the host the battery need to be recharged.