v03.0610

GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

#### **Typical Applications**

The HMC668LP3(E) is ideal for:

- Cellular/3G and LTE/WiMAX/4G

- BTS & Infrastructure

- Repeaters and Femtocells

- Tower Mounted Amplifiers

- Test & Measurement Equipment

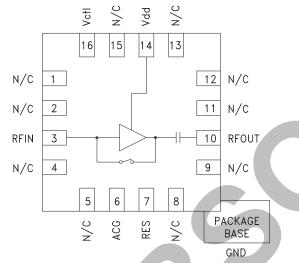

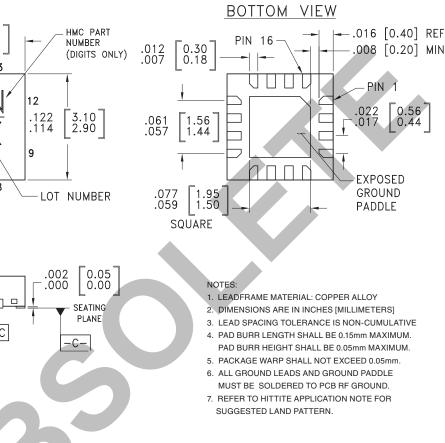

#### **Functional Diagram**

#### Features

Noise Figure: 0.9 dB Output IP3: +33 dBm Gain: 16 dB Failsafe Operation: Bypass is enabled when LNA is unpowered Single Supply: +3V or +5V

16 Lead 3x3mm QFN Package: 9 mm<sup>2</sup>

#### **General Description**

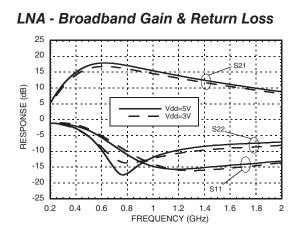

The HMC668LP3(E) is a versatile, high dynamic range GaAs MMIC Low Noise Amplifier that integrates a low loss LNA bypass mode on the IC. The amplifier is ideal for receivers and LNA modules operating between 0.7 and 1.2 GHz and provides 0.9 dB noise figure, 16 dB of gain and +33 dBm IP3 from a single supply of +5V @ 57mA. Input and output return losses are excellent and no external matching components are required. A single control line is used to switch between LNA mode and a low loss bypass mode. The failsafe topology enables the LNA bypass path, when no DC power is available. The HMC668LP3(E) offers improved noise figure versus the previously released HMC373LP3(E).

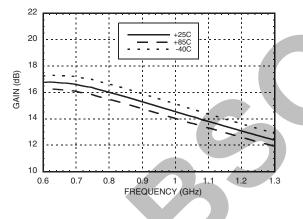

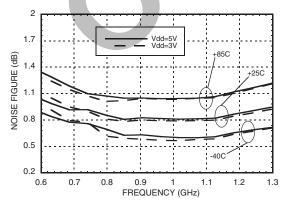

#### Electrical Specifications, $T_{A} = +25^{\circ}$ C, Rbias = 0 Ohm LNA Mode **Bypass Mode** Failsafe Mode Parameter Vdd = +3VVdd = +5VUnits Min. Тур. Max Min. Тур. Max. Min. Тур. Max. Min. Тур. Max. Frequency Range 0.7 - 1.2 0.7 - 1.2 0.7 - 1.2 0.7 - 1.2 GHz Gain 12 15 13 16 -2.5 -1.5 -2.5 -1.5 dB Gain Variation Over Temperature 0.03 0.016 0.0008 0.0008 dB / °C Noise Figure 0.85 1.1 0.9 1.1 dB 12 12 Input Return Loss 12 13 dB Output Return Loss 13 14 13 13 dB **Reverse Isolation** 22 23 -dB Power for 1dB Compression 13 13 22 24 dBm (P1dB)<sup>[1]</sup> Third Order Intercept (IP3)<sup>[2]</sup> 27 33 26 26 dBm Supply Current (Idd) 32 40 57 70 0.05 mΑ -Switching Speed (90% -10%) 200 LNA Mode to Bypass Mode ns Bypass Mode to LNA Mode 85 85 ns

[1] P1dB for LNA Mode is referenced to RFOUT while P1dB for Bypass and Failsafe Modes are referenced to RFIN. [2] IP3 for LNA Mode is referenced to RFOUT while IP3 for Bypass and Failsafe Modes are referenced to RFIN.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0610

#### GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

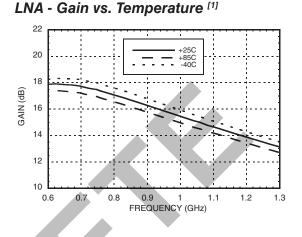

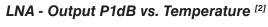

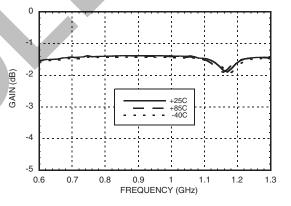

LNA - Gain vs. Temperature [2]

LNA - Noise Figure vs. Temperature [3]

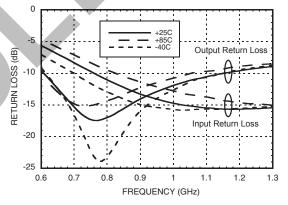

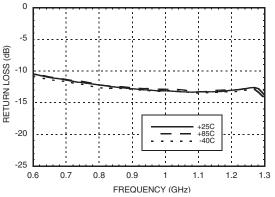

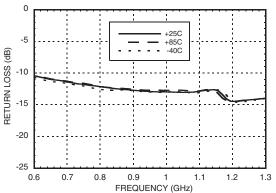

LNA - Return Loss vs. Temperature [1]

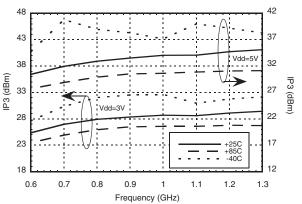

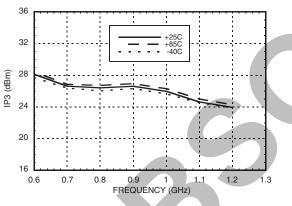

LNA - Output IP3 vs. Temperature, Output Power @ 0 dBm

[1] Vdd = 5V [2] Vdd = 3V [3] Measurement reference plane shown on evaluation PCB drawing.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0610

1.2

1.3

GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

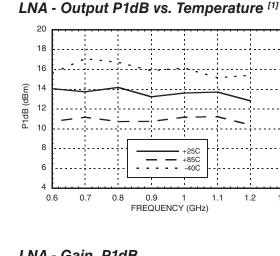

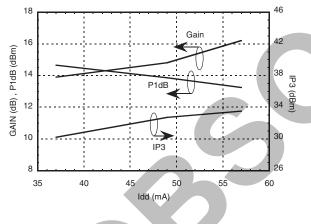

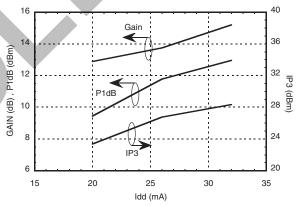

LNA - Gain, P1dB, Output IP3 vs. Current <sup>[1]</sup> @ 900 MHz

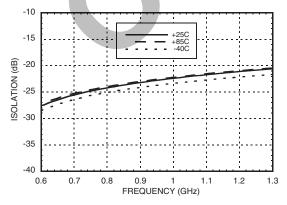

LNA - Reverse Isolation vs. Temperature [1]

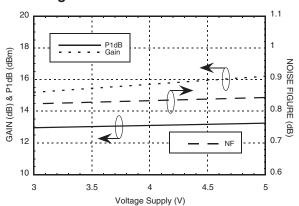

LNA - Output P1dB, Gain & Noise Figure <sup>[3]</sup> vs. Vdd @ 900 MHz

[3] Measurement reference plane shown on evaluation PCB drawing. [1] Vdd = 5V [2] Vdd = 3V

Information furnished by Analog Devices is believed to be accurate and reliable. However, responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

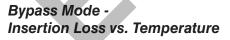

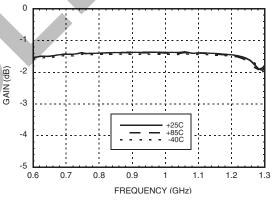

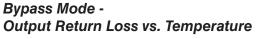

Bypass Mode -

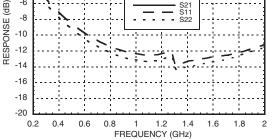

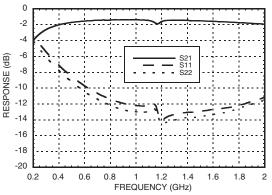

Bypass Mode -Broadband Gain & Return Loss

v03.0610

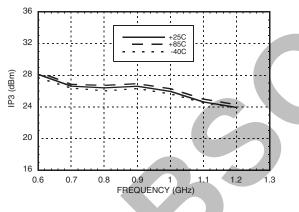

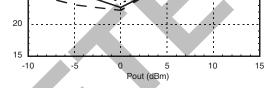

Bypass Mode - Input IP3 vs. Temperature, Output Power @ 5 dBm

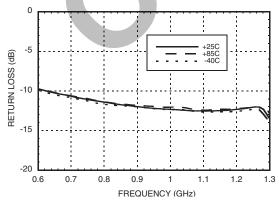

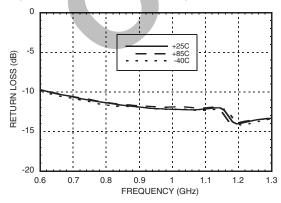

Bypass Mode -Input Return Loss vs. Temperature

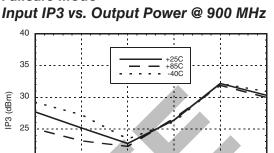

Input IP3 vs. Output Power @ 900 MHz

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0610

GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

Failsafe Mode -

Failsafe Mode -Broadband Gain & Return Loss

Failsafe Mode - Input IP3 vs. Temperature, Output Power @ 5 dBm

Failsafe Mode -Input Return Loss vs. Temperature

Failsafe Mode -Insertion Loss vs. Temperature

Failsafe Mode -Output Return Loss vs. Temperature

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

#### Absolute Maximum Ratings

| -                                                                |                   |

|------------------------------------------------------------------|-------------------|

| Drain Bias Voltage (Vdd)                                         | +6 Vdc            |

| Control Voltage (Vctl)                                           | +6 Vdc            |

| RF Input PowerLNA Mode(RFIN)Bypass / Failsafe Mode               | +5 dBm<br>+20 dBm |

| Channel Temperature                                              | 150 °C            |

| Continuous Pdiss (T = 85 °C)<br>(derate 10.71 mW/°C above 85 °C) | 0.70 W            |

| Thermal Resistance<br>(channel to ground paddle)                 | 93.33 °C/W        |

| Storage Temperature                                              | -65 to +150° C    |

| Operating Temperature -40 to +85° C                              |                   |

| ESD Sensitivity (HBM)                                            | Class 1A          |

v03.0610

#### Typical Supply Current vs. Vdd

| Rbias Ω | ldd (mA) |         |  |

|---------|----------|---------|--|

|         | Vdd= 3V  | Vdd= 5V |  |

| 0       | 32       | 57      |  |

| 15      | 26       | 49      |  |

| 47      | 20       | 37      |  |

| 180 [1] | 10       | 20      |  |

[1] Recommended maximum Rbias

ELECTROSTATIC SENSITIVE DEVICE OBSERVE HANDLING PRECAUTIONS

#### Truth Table

| LNA Mode      | VctI = Vdd = 3 to 5V    |

|---------------|-------------------------|

| Bypass Mode   | Vctl= 0V, Vdd = 3 to 5V |

| Failsafe Mode | VctI = Vdd = N/C        |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0610

GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

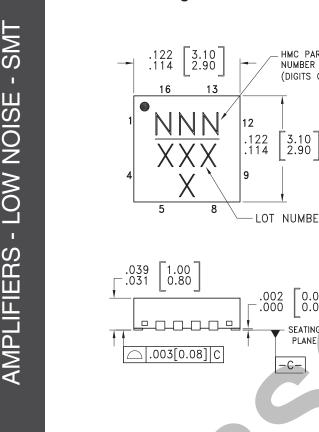

#### **Outline Drawing**

#### **Package Information**

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating          | Package Marking [3] |

|-------------|----------------------------------------------------|---------------|---------------------|---------------------|

| HMC668LP3   | Low Stress Injection Molded Plastic                | Sn/Pb Solder  | MSL1 <sup>[1]</sup> | 668<br>XXXX         |

| HMC668LP3E  | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1 <sup>[2]</sup> | <u>668</u><br>XXXX  |

[1] Max peak reflow temperature of 235 °C

[2] Max peak reflow temperature of 260 °C

[3] 4-Digit lot number XXXX

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0610

### GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

#### **Pin Descriptions**

| Pin Number                          | Function | Description                                                                                                                          | Interface Schematic       |

|-------------------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1, 2, 4, 5, 8, 9,<br>11, 12, 13, 15 | N/C      | No connection required. These pins may be<br>connected to RF GND. Performance will not<br>be affected.                               |                           |

| 3                                   | RFIN     | This pin is DC coupled.<br>Off-chip DC blocking capacitor required.                                                                  |                           |

| 6                                   | ACG      | AC Ground. Attach bypass capacitor per application circuit.                                                                          |                           |

| 7                                   | RES      | External resistor pin for current control. See table for external resistor value vs. bias current data.                              | ESD<br>ACG RES            |

| 10                                  | RFOUT    | This pin is matched to 50 Ohms                                                                                                       |                           |

| 14                                  | Vdd      | Power Supply voltage pin. External bypass<br>capacitors required.                                                                    | Vdd<br>Q                  |

| 16                                  | Vctl     | Control voltage pin for LNA / Bypass<br>Modes. Setting voltage equal to VDD enables LNA<br>Mode. External Bypass capacitor required. | VctI<br>ESD<br>ESD<br>ESD |

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0610

GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

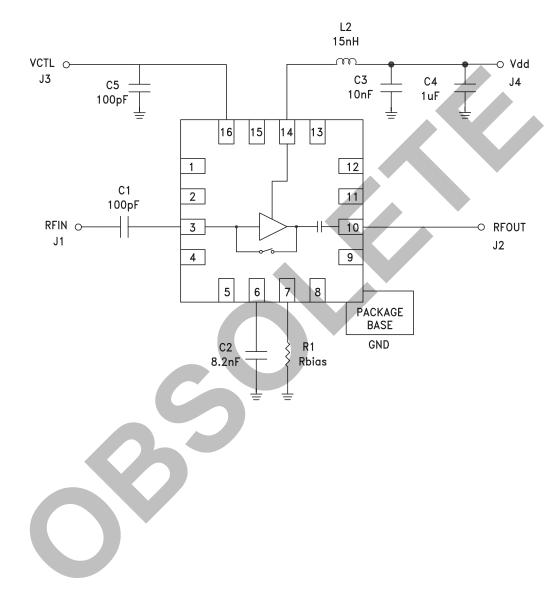

#### Application Circuit

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

v03.0610

#### GaAs PHEMT MMIC LNA w/ FAILSAFE BYPASS MODE, 700 - 1200 MHz

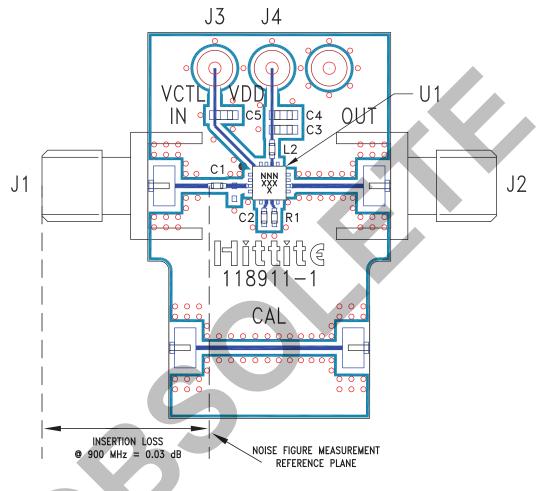

#### **Evaluation PCB**

#### List of Materials for Evaluation PCB 121922 [1]

| Item    | Description                  |  |

|---------|------------------------------|--|

| J1 - J2 | PCB Mount SMA Connector      |  |

| J3 - J4 | DC Pin                       |  |

| C1      | 100 pF Capacitor, 0402 Pkg.  |  |

| C2      | 8200 pF Capacitor, 0402 Pkg. |  |

| C3      | 10 nF Capacitor, 0603 Pkg.   |  |

| C4      | 1 μF Capacitor, 0603 Pkg.    |  |

| C5      | 100 pF Capacitor, 0603 Pkg.  |  |

| L2      | 15 nH Inductor, 0402 Pkg.    |  |

| R1      | 0 Ohm Resistor, 0402 Pkg.    |  |

| U1      | HMC668LP3(E) Amplifier       |  |

| PCB [2] | 118911 Evaluation Board      |  |

[1] Reference this number when ordering complete evaluation PCB

[2] Circuit Board Material: Rogers 4350

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohm impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.