# Ballast Design for 54W UV-C Disinfection Lamp (Voltage Mode Preheating) with Controller IC ICB2FL03G & 600V CoolMOS<sup>™</sup> PFD7

ICB2FL03G

# About this document

## **Product Highlights**

- Lowest count of external components

- 650 V half-bridge driver with Coreless Transformer Technology

- Supports customer in-circuit test mode for reduced tester time

- Supports multi-lamp designs (in series connection)

- Integrated digital timers up to 40 seconds

- Numerous monitoring and protection features for highest reliability

- Very high accuracy of frequencies and timers over the whole temperature range

- Very low standby losses

#### **Features PFC**

- Discontinuous mode PFC for load ranges 0 to 100 %

- Integrated digital compensation of PFC control loop

- Improved compensation for low THD of AC input current, also in DCM operation

- Adjustable PFC current limitation

#### Features Lamp Ballast Inverter

- Adjustable detection of overload and rectifier effect (EOL)

- Detection of capacitive load operation

- Improved ignition control allows for operation close to magnetic saturation of inductors

- Restart with skipped preheating at short interruptions of line voltage (for emergency lighting)

- Parameters adjustable by resistors only

- Pb-free lead plating; RoHS-compliant

In our UV-C ballast design we have deployed 600V CoolMOSTM from the new PFD7 family. The PFD7 family of products combine highest efficiency with a very high level of robustness. In order to reduce system cost we decided to use a version in a low cost SOT223 package. The ballast was designed for 54W T5 lamp, but can be used with L55 W 2G11UV-C lamp.

## Table of contents

## **Table of contents**

|                                                                     | About this document                                                                                                                                                                                                                                                                                      |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     | Table of contents    2                                                                                                                                                                                                                                                                                   |

| 1                                                                   | Introduction                                                                                                                                                                                                                                                                                             |

| 1.1                                                                 | Functional Description                                                                                                                                                                                                                                                                                   |

| 1.2                                                                 | Pinning and Picture of the Demo Board7                                                                                                                                                                                                                                                                   |

| 1.3                                                                 | Parameters of the Demo Board7                                                                                                                                                                                                                                                                            |

| 1.4                                                                 | Description of Normal Start-up Steps8                                                                                                                                                                                                                                                                    |

| 2                                                                   | <b>VCC Chip Supply</b>                                                                                                                                                                                                                                                                                   |

| 2.1                                                                 | Operation with Half-Bridge not Working 11                                                                                                                                                                                                                                                                |

| 2.2                                                                 | Operation with Half-Bridge Working12                                                                                                                                                                                                                                                                     |

| 3                                                                   | PFC                                                                                                                                                                                                                                                                                                      |

| 3.1                                                                 | THD Correction                                                                                                                                                                                                                                                                                           |

| 4                                                                   | Ignition Regulator - Control during Ignition 15                                                                                                                                                                                                                                                          |

| 4.1                                                                 | Operation Close to Different Saturation Levels                                                                                                                                                                                                                                                           |

| 4.2                                                                 | Bus Voltage Breakdown during Ignition16                                                                                                                                                                                                                                                                  |

| 5                                                                   | Filament Detection                                                                                                                                                                                                                                                                                       |

| 5.1                                                                 | LVS Pin                                                                                                                                                                                                                                                                                                  |

| 5.2                                                                 | RES Pin                                                                                                                                                                                                                                                                                                  |

| 6                                                                   | Detection of Failures                                                                                                                                                                                                                                                                                    |

| 6.1                                                                 | Surge Detection                                                                                                                                                                                                                                                                                          |

| 6.2                                                                 | Inverter Overcurrent Protection                                                                                                                                                                                                                                                                          |

| 6.3                                                                 | PFC Overcurrent Protection                                                                                                                                                                                                                                                                               |

| 6.4                                                                 | Bus Overvoltage Protection 109% – 105% Threshold23                                                                                                                                                                                                                                                       |

| 6.5                                                                 | Bus Undervoltage Protection in Run Mode with 75% Threshold                                                                                                                                                                                                                                               |

| 6.6                                                                 | EOL Detection                                                                                                                                                                                                                                                                                            |

|                                                                     |                                                                                                                                                                                                                                                                                                          |

| 6.6.1                                                               | EOL1 (Overload)                                                                                                                                                                                                                                                                                          |

| 6.6.2                                                               | EOL1 (Overload)                                                                                                                                                                                                                                                                                          |

| 6.6.2<br>6.6.3                                                      | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26                                                                                                                                                                                                                                    |

| 6.6.2                                                               | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27                                                                                                                                                                                                             |

| 6.6.2<br>6.6.3                                                      | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27Capacitive load (Cap Load)28                                                                                                                                                                                 |

| 6.6.2<br>6.6.3<br>6.6.4<br>6.7<br>6.7.1                             | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27                                                                                                                                                                                                             |

| 6.6.2<br>6.6.3<br>6.6.4<br>6.7<br>6.7.1<br>6.7.2                    | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27Capacitive load (Cap Load)28Cap Load 1 (Idling Detection / Current Mode Preheating)28Cap Load 2 (Overcurrent / Operation Below Resonance)29                                                                  |

| 6.6.2<br>6.6.3<br>6.6.4<br>6.7<br>6.7.1                             | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27Capacitive load (Cap Load)28Cap Load 1 (Idling Detection / Current Mode Preheating)28                                                                                                                        |

| 6.6.2<br>6.6.3<br>6.6.4<br>6.7<br>6.7.1<br>6.7.2                    | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27Capacitive load (Cap Load)28Cap Load 1 (Idling Detection / Current Mode Preheating)28Cap Load 2 (Overcurrent / Operation Below Resonance)29                                                                  |

| 6.6.2<br>6.6.3<br>6.6.4<br>6.7<br>6.7.1<br>6.7.2<br>6.8             | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27Capacitive load (Cap Load)28Cap Load 1 (Idling Detection / Current Mode Preheating)28Cap Load 2 (Overcurrent / Operation Below Resonance)29Emergency Detection30                                             |

| 6.6.2<br>6.6.3<br>6.6.4<br>6.7<br>6.7.1<br>6.7.2<br>6.8<br><b>7</b> | EOL1 (Overload)24EOL2 (Rectifier Effect)24Switched Rectifier Effect26Hard Rectifier Effect27Capacitive load (Cap Load)28Cap Load 1 (Idling Detection / Current Mode Preheating)28Cap Load 2 (Overcurrent / Operation Below Resonance)29Emergency Detection30Advice for Design, Layout and Measurements32 |

## Table of contents

| 7.3    | RFPH pin (Preheating Frequency)                                                           |

|--------|-------------------------------------------------------------------------------------------|

| 7.4    | RTPH Pin (Preheating Time)                                                                |

| 7.5    | PFCVS Pin                                                                                 |

| 7.6    | RES Pin                                                                                   |

| 7.7    | VCC Pin                                                                                   |

| 7.8    | LVS Pin                                                                                   |

| 7.9    | LSCS Pin                                                                                  |

| 7.10   | Advice for Board Layout                                                                   |

| 8      | Annex                                                                                     |

| 8.1    | Built-In Customer Test Mode                                                               |

| 8.2    | Calculations                                                                              |

| 8.2.1  | Sample Calculation: EOL for 54W T5 Design (Excel)                                         |

| 8.2.2  | Sample Calculation – Start-up Network for 54W T5 Design (Excel)                           |

| 8.2.3  | Inductor L1 of the Boost Converter                                                        |

| 8.2.4  | Shunt Resistors for Ignition Voltage R <sub>24</sub> , R <sub>25</sub> 43                 |

| 8.2.5  | Ballast Parameters                                                                        |

| 8.3    | Troubleshooting                                                                           |

| 8.3.1  | VCC does not reach 10.5 V (V <sub>VCCOff</sub> ) or 14 V (V <sub>VCCOn</sub> ) $\dots$ 46 |

| 8.3.2  | VCC Hiccup between 14 V (V <sub>VCCOff</sub> ) and 10.5 V (V <sub>VCCOn</sub> )           |

| 8.3.3  | No LSGD Pulse                                                                             |

| 8.3.4  | No HSGD Pulse                                                                             |

| 8.3.5  | No PFCGD Pulse                                                                            |

| 8.3.6  | The IC Starts without a High-Side Filament                                                |

| 8.3.7  | The IC Starts without a Low-Side FilamentThe IC Starts without a Low-Side Filament47      |

| 8.3.8  | The IC Stops within t <sub>PRERUN</sub> after Ignition47                                  |

| 8.3.9  | The IC Stops about t <sub>PRERUN</sub> after Ignition                                     |

| 8.3.10 | The IC Stops about 3 s after Ignition    48                                               |

| 8.4    | BOM Schematic Layout                                                                      |

| 8.5    | Interference Suppression according to EN 5501551                                          |

| 9      | <b>Terminology</b>                                                                        |

|        | <b>Revision history</b>                                                                   |

|        | <b>Disclaimer</b>                                                                         |

# 1 Introduction

The fluorescent lamp ballast Controller ICB2FL03G is designed to control a boost converter as an active power factor correction (PFC) filter in critical/discontinuous conduction mode (CritCM/DCM) and in half-bridge topologies as a lamp inverter. The intelligent control concept enables designers to develop cost-effective ballasts for fluorescent lamps (FL) that fulfill the requirements of a high-performance T5 lamp ballast as well as multi-lamp topologies (series connection), T8 and T4 designs. A state machine controlling the operating modes, a completely integrated digital control loop for the PFC output voltage and low tolerances for reference voltages and operating frequency over the whole temperature range are a result of the advanced mixed signal technology with only few components required externally. Combined with a high-voltage level shift driver with Coreless Transformer Technology for the half-bridge inverter, the IC offers a significant number of exceptional features for FL ballasts.

The FL ballast controller ICB2FL03G has improved and extended functionality to enable high-quality single or multi-lamp ballasts (series connection) with a low number of external components. It helps to save system costs and to easily achieve class A2 of the energy efficiency index (EEI) for fluorescent lamp ballasts.

Further information and the data sheet can be found at: *http://www.infineon.com/smartlighting* Unless otherwise specified, all values given in this Application Note are typical values.

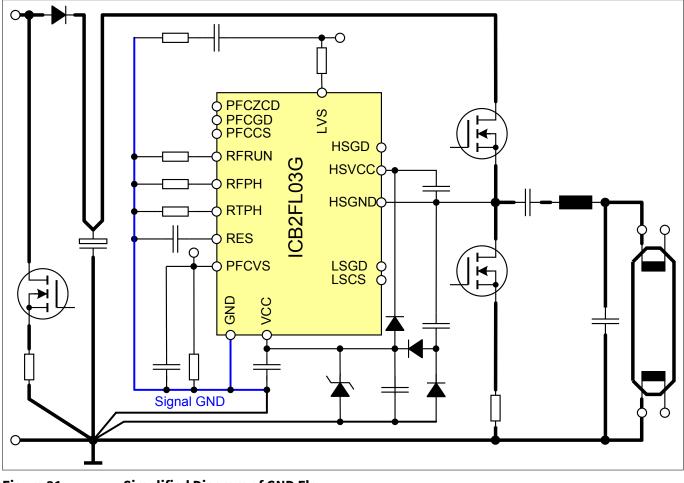

# 1.1 Functional Description

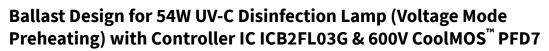

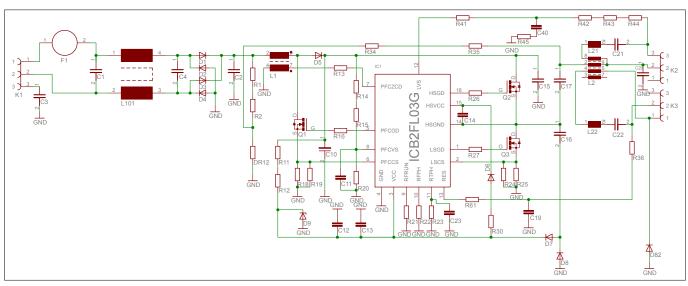

The functional description is given based on the circuit diagram of a lamp ballast for the T5 fluorescent lamps (*Figure 1*).

## Figure 1 Schematic for 54W T5 demo board

The schematic shows the circuit of the demo board with the reference name of each component for a single lamp design with voltage mode preheating. This schematic supports all protection functions of the IC.

After switching on the mains, the filter capacitor  $C_2$  and the bulk capacitor  $C_{10}$  are charged to the peak voltage of the mains supply. The capacitors  $C_{12}$  and  $C_{13}$ , which support the IC supply voltage VCC, are charged via the startup resistors  $R_{11}$  and  $R_{12}$ . The current consumption of the IC at this stage is typically below 90  $\mu$ A until the supply voltage has reached typ. 10.6 V. Above this level the current consumption is typ. 120  $\mu$ A, and a current source of typically 21.3  $\mu$ A at the RES pin is activated, which detects a connected low-side filament. As long as the voltage level at the RES pin is below 1.6 V, the filament is assumed to be undamaged. A resistor  $R_{36}$  is placed on the path of the measured current to adjust the voltage drop and – in conjunction with the capacitor  $C_{19}$  – filters the alternating voltage on the filament during run mode. A current is fed through the resistors  $R_{34}$  and  $R_{35}$  to the high-side filament and through the resistors  $R_{41}$ ,  $R_{42}$ ,  $R_{43}$  and  $R_{44}$  to the LVS pin. A filament is detected if

the current is above typ. 12  $\mu$ A. If the measured current at the LVS pin is too small, this fault generates a higher current level of typically 42.6  $\mu$ A at the RES pin. The following points are checked in the sequence below before the IC activates the driver outputs.

- Connected filaments

- VCC > VVCCOn (14.0 V)

- Bus voltage between 12.5 % and 105 %

#### **Inverter section**

With the first pulse the low side MOSFET  $Q_3$  of the half-bridge is turned on. Then the floating capacitor  $C_{14}$ , which supplies the high-side control logic like a battery, is charged from capacitor  $C_{13}$  via  $R_{30}$  and the diode  $D_6$ . The resistor  $R_{30}$  prevents activation of the overcurrent protection at the LSCS pin. This means that the high-side MOSFET  $Q_2$  can already be turned on with the next half cycle. The capacitor  $C_{16}$  together with the diodes  $D_7$  and  $D_8$  acts as a charge pump at the output of the half-bridge inverter. The continuous recharging of  $C_{16}$  with the inverter frequency shifts energy for the supply voltage VCC of the IC to  $C_{13}$ . A surplus of energy is dissipated by the zener diode  $D_9$ . In addition,  $C_{16}$  is used to limit the voltage slew rate and to produce zero voltage switching conditions.

During operation  $C_{16}$  is recharged without losses in the deadtime periods of MOSFET  $Q_2$  and  $Q_3$  by the inductively driven current of the load circuit. Consequently, the succeeding turn-on of the MOSFET occurs at zero voltage. At turn-off,  $C_{16}$  limits the voltage slew rate in such a way that the MOSFET channel is already turned off before the drain-to-source voltage has reached considerable levels. The inverter therefore creates negligible switching losses in normal operation. The load circuit of the inverter consists of a series resonant circuit with the resonance inductor  $L_2$  and the resonance capacitor  $C_{20}$ . The lamp is connected in parallel to the resonance capacitor. This example shows voltage-controlled preheating. This means that the resonance-inductor  $L_2$  has two additional windings. Each of those windings drives a current in the filament via the band-pass consisting of  $L_{21}/C_{21}$  and  $L_{22}/C_{22}$ . The band-pass filter ensures that the current in the filaments is only flowing during the preheat phase. By reducing the frequency during run mode, the heating current is almost completely blocked by the band-pass. The load circuit also contains a capacitor  $C_{17}$ . This capacitor is charged to half the value of the bus voltage – operating the lamp symmetrically to the ground potential of the rectified mains supply is possible as a result.

#### PFC

The MOSFET  $Q_1$  of the PFC boost converter starts the operation simultaneously with the inverter. This circuit consists of the inductor  $L_1$ , diode  $D_5$ , MOSFET  $Q_1$  together with the bulk capacitor  $C_{10}$ . Such a boost converter can transform the input voltage to any arbitrary higher output voltage. Using a suitable control method this converter is used as an active harmonic filter and for correction of the power factor. The input current follows the same sinusoidal waveform as the AC mains supply voltage. At the output of the PFC preconverter a feedback-controlled DC voltage is available at capacitor  $C_{10}$  for the application. The PFC stage is operated with a controlled turn-on time without input voltage sense. A turn-on time set by the control unit is followed by a turn-off time, which is determined by the duration until the current in the inductor and hence in the diode too has reached the level zero. This point of time is detected by the voltage level at the zero current detector winding on the inductor  $L_1$  and is fed to the IC via the resistor  $R_{13}$  and the PFCZCD pin. The result is a gapless triangularly shaped current through inductor  $L_1$  (so-called critical conduction mode), which is sustained for a turn-on time in the range of 24.0  $\mu$ s down to 270 ns. A further reduction of the energy flow extends the turn-off time of the PFC MOSFET, causing triangularly shaped currents with gaps (discontinuous conduction mode). Such a control method allows stable operation of the boost converter over a large range of input voltage as well as output power. The current into the PFCZCD pin is used to perform THD correction for optimized THD.

The IC includes a couple of protection features for the PFC preconverter. The overcurrent is sensed at the PFCCS pin. The bus voltage, overvoltage and undervoltage are monitored at the PFCVS pin as well as the open loop detection. The ICB2FL03G includes the error amplifier with entire compensation built up by a digital PI regulator and a self-calibrating notch filter to suppress the voltage ripple of the bulk capacitor.

## Startup

The inverter starts at a frequency of 135 kHz. The frequency is reduced within 10 ms in 15 steps to the preheating frequency, which is adjustable by the resistor R<sub>22</sub>. The duration of preheating can be selected

between zero and 2500 ms by the resistor  $R_{23}$ . Subsequently, the frequency is further reduced in 127 steps and a time period of 40 ms to the run frequency  $f_{RUN}$ , which is adjustable by the resistor  $R_{21}$ . The ballast should be designed in such a way that during the preheating phase the voltage across the lamp is low and at the same time the current in the filaments is large.

In the ignition phase following the preheating period the frequency of the inverter should be at – or at least close to – the resonance frequency of the resonant circuit in order to reach a voltage sufficient for ignition of the lamp. After successful ignition and frequency reduction to the run frequency the current in the lamp should reach its nominal value and the current in the filaments should become minimal. During the ignition period a high voltage at the lamp and a large current in the resonant circuit are generated due to the unloaded resonant circuit. The current in the resonant circuit is monitored by the resistors R<sub>24</sub> and R<sub>25</sub>. As soon as the voltage at pin LSCS exceeds a level of 0.8 V, the operating frequency is controlled by the integrated ignition regulator, which works stable close to magnetic saturation of the resonant choke. If the level of 0.8 V at pin LSCS is not crossed any more, the operating frequency of the inverter decreases with the typical step width of the ignition phase towards the run frequency. As a result of this measure the ignition phase is extended from 40 ms up to 235 ms with a lamp not willing to ignite, while the voltage at the lamp remains on the level of the ignition voltage. If the run frequency is not achieved within 235 ms after finishing the preheating period, the IC switches to the failure mode. In such a situation the gate drives will be shut down, the current consumption of the IC will be reduced to max. 170 µA and the detection of the filaments and the input voltage will be activated. A restart is initiated dependent on the failure counter directly or either by lamp removal or after a new cycle of turn-off and turn-on of the mains voltage. After successful ignition a fixed pre-run time of typ. 625 ms is implemented to block several protection functions until stable lamp operation can be guaranteed.

## **Protection functions**

Numerous protection functions complement the basic functions of the ICB2FL03G. As soon as the level at pin LSCS exceeds the voltage threshold of 0.8 V for longer than 500 ns, it is recognized as a risky operating condition as it can occur during lamp removal in a running device or during transients in the mains voltage, and the IC switches to the failure mode. During run mode of the inverter a deviation from the typical zero voltage switching is recognized as an operation with capacitive load. Under such operating conditions, peak currents occur during turnon of the MOSFETs due to switched charging of the charge pump capacitor C<sub>16</sub>. The IC distinguishes between two different types of capacitive load as follows:

- Cap load 1 (idling detection / current mode preheating) Cap Load 1 (Idling Detection / Current Mode Preheating)

- Cap load 2 (overcurrent / operation below resonance) Cap Load 2 (Overcurrent / Operation Below Resonance)

Finally, dangerous operating conditions can arise when the fluorescent lamp reaches the end of lifetime or under operating conditions leading to thermal instability of the lamp. As a consequence, the lamp voltage becomes unsymmetrical or increases. To detect such operating conditions, the resistors  $R_{41}$ ,  $R_{42}$ ,  $R_{43}$ ,  $R_{44}$ ,  $R_{45}$  and the capacitor  $C_{40}$  measure the lamp voltage by evaluating the current through these resistors at the pin LVS. The turnoff threshold for EOL1 (End of Life 1) is at 210  $\mu$ A<sub>PP</sub> with a duration of 620  $\mu$ s. The rectifier effect with unsymmetrical lamp voltage is called EOL2 (End of Life 2) and the turn-off threshold is at +/- 42  $\mu$ A with a duration of typ. 2500 ms. Due to intelligent failure differentiation, the ICB2FL03G is able to detect a surge at the input voltage without latching this failure.

The IC controls the operating frequency of the inverter during the different operating sequences, such as soft start, preheat, ignition, pre-run and run mode. During the different operating sequences only some of the protection features are active at first. All the protection features are active during run mode only. The integrated circuit ICB2FL03G has a unique combination of features that make design of high-quality lamp ballast with a low number of external components possible.

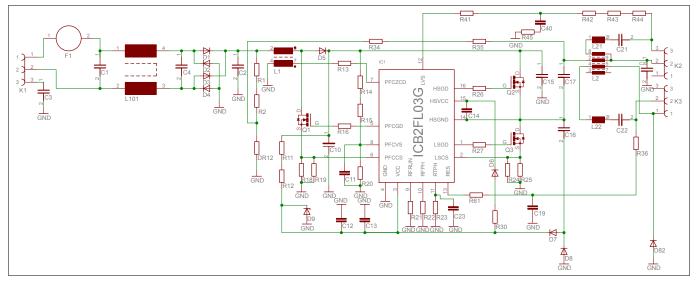

## **1.2** Pinning and Picture of the Demo Board

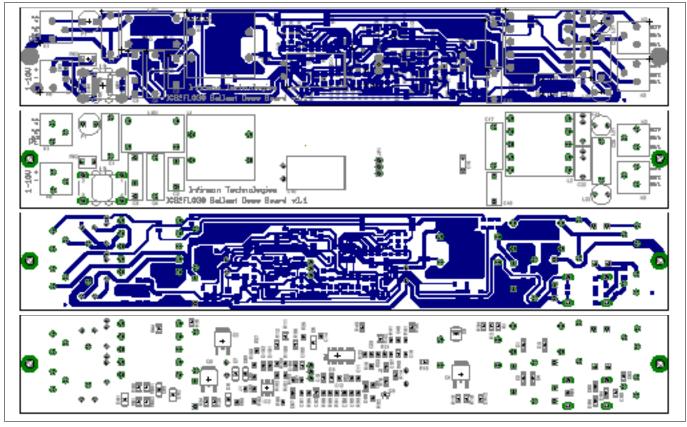

The following section shows the pinning of the IC and a picture of the demo board described in this document.

#### Figure 2 Pinning of IC

The pinning and a short pin description is given in *Figure 2*. A detailed pin description can be found in the data sheet.

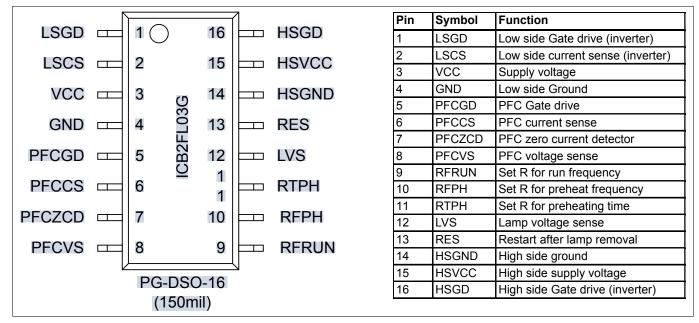

## Figure 3 Top and Bottom Views of the Demo Board

*Figure 3* shows a picture of the demo board for the 54W T5 design with voltage mode preheating. Please visit the Infineon Smart Lighting website (*http://www.infineon.com/smartlighting*) for further information.

## 1.3 Parameters of the Demo Board

*Table 1* gives an overview of the operational characteristics of the demo board.

#### Table 1Operational characteristics of the 54W T5 demo board

|                 | Value | Unite              | Comment         |

|-----------------|-------|--------------------|-----------------|

| V <sub>IN</sub> | 230   | V <sub>ACRMS</sub> | (180 V - 270 V) |

| Table 1           | Operational characteristics of the 54W T5 demo board (continued) |                   |                                                                              |  |

|-------------------|------------------------------------------------------------------|-------------------|------------------------------------------------------------------------------|--|

|                   | Value                                                            | Unite             | Comment                                                                      |  |

| I <sub>IN</sub>   | 257                                                              | mA <sub>RMS</sub> | @ 230 V input voltage                                                        |  |

| P <sub>IN</sub>   | 59.1                                                             | W <sub>RMS</sub>  | @ 230 V input voltage<br>(EEI = A2 CELMA efficiency<br>class)                |  |

| V <sub>BUS</sub>  | 410                                                              | V <sub>RMS</sub>  |                                                                              |  |

| f <sub>PH</sub>   | 106.4                                                            | kHz               |                                                                              |  |

| f <sub>RUN</sub>  | 45.5                                                             | kHz               |                                                                              |  |

| t <sub>PH</sub>   | 1000                                                             | ms                |                                                                              |  |

| V <sub>Lamp</sub> | 118                                                              | V <sub>RMS</sub>  |                                                                              |  |

| I <sub>Lamp</sub> | 460                                                              | mA <sub>RMS</sub> |                                                                              |  |

| V <sub>IGN</sub>  | > 620                                                            | V <sub>RMS</sub>  |                                                                              |  |

| n                 | > 91                                                             | %                 | With lamp after 30 min.<br>operation in run mode @<br>230 V <sub>ACRMS</sub> |  |

| PF                | > 0.99                                                           |                   | @ 230 V <sub>ACRMS</sub> input<br>voltage                                    |  |

| A <sub>THD</sub>  | < 4                                                              | %                 | @ 230 V <sub>ACRMS</sub> input<br>voltage                                    |  |

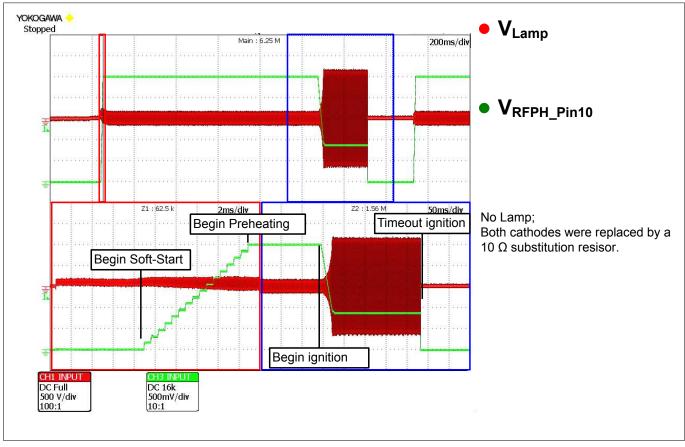

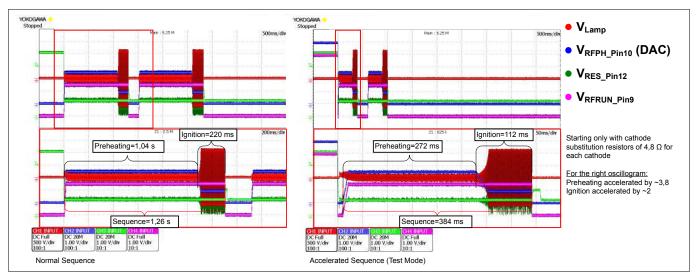

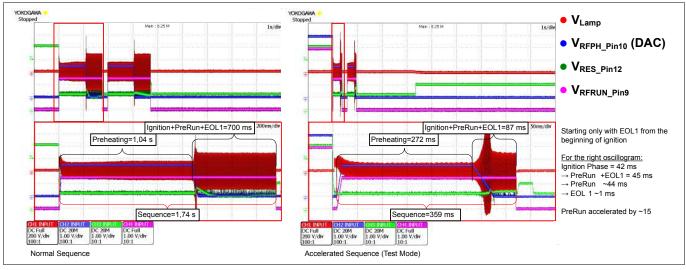

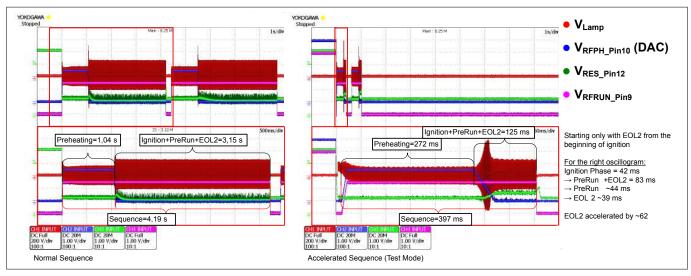

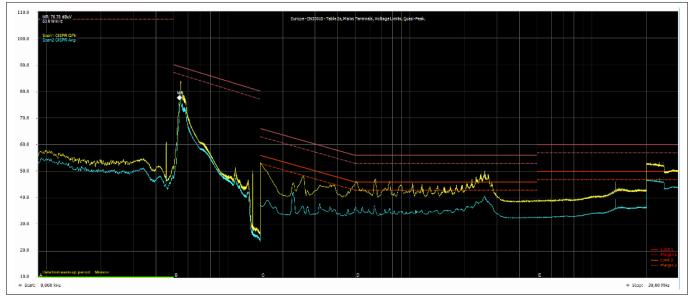

## 1.4 Description of Normal Start-up Steps

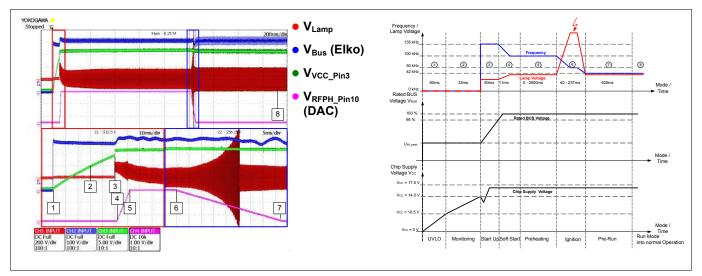

This section describes the normal start-up procedure from phase 1 (UVLO) to phase 8 (run mode). *Figure 4* shows a measurement and diagram from the start-up procedure. Dependent on the voltage at the RES pin, the current consumption of the IC can be higher due to  $I_{RES1}$  to  $I_{RES4}$ .

## Figure 4 Start-up Procedure

The current consumption of the IC in Phase 1 (UVLO) is I<sub>VCCqu1</sub>. The current fed via the high ohmic VCC start-up resistors (R<sub>11</sub> and R<sub>12</sub>) charges the VCC capacitor and delivers this quiescent current. After reaching

a first threshold of V<sub>VCCOff</sub> the IC goes into monitoring mode and checks for connected cathodes. The current consumption in this Phase 2 is  $I_{VCCqu2}$  and has to be also delivered via the start-up resistors. The voltage at the VCC pin rises up to V<sub>VCCO</sub>n and the IC becomes active and starts inverter switching (provided that both cathodes are present). Phase 3, also called start-up, activates the whole IC and leads to a current consumption of  $I_{VCCSupply}$ .

The internal reference starts up within the first 130  $\mu$ s and the IC checks the level of the bus voltage. If the bus voltage is in the specified range of 12.5 % and 105 %, the LSGSD switches on several times to charge the HSVCC capacitor via R<sub>30</sub> and D<sub>6</sub>. After reaching the HSVCC turn-on threshold of V<sub>HSVCCOn</sub> the HSGD also starts working (HSGD and LSGD alternating) and supplies the IC via a charge pump, and the VCC voltage rises to the voltage clamped by D<sub>9</sub>. The inverter works with a start-up frequency of f<sub>StartUp</sub>. To prevent the IC reaching the UVLO threshold of V<sub>VCCOff</sub> when all gate drives become active at the same time, the PFC section starts working with a delay of about 200  $\mu$ s (see also *Figure 5*). After reaching a bus voltage of 95 % the IC enters soft start, phase 4.

In this phase the IC shifts the frequency down to the adjusted preheating frequency. This frequency shift can be seen at the signal at the RFPH pin when the voltage rises from GND to 2.5 V (*Figure 4*).

After reaching the preheating frequency the IC stays in this preheating phase (Phase 5) for the adjusted preheating time. At the end of the preheating time the IC enters ignition mode (Phase 6) and begins reducing the frequency down to the adjusted run frequency. This can also be seen on the signal at the RFPH pin. The voltage at this pin falls until the voltage at the LSCS pin reaches the threshold of 0.8 V. Then the ignition regulator begins regulating the ignition voltage to this maximum level, also during magnetic saturation of the resonant choke. While regulating the ignition voltage, the voltage at the RFPH pin remains at the achieved level between 2.5 V and GND.

After successful ignition during  $t_{NOIgnition}$  (limited duration of the ignition phase) the IC enters the pre-run mode, Phase 7, and the voltage at the RFPH pin falls to GND. The pre-run mode is a safety mode (with limited protection functions active for  $t_{PRERUN}$ ) in order to prevent a malfunction of the IC due to an instable system – e.g., the lamp parameters are not in a steady state condition. In this phase the ignition regulator is also active in order to re-ignite the lamp if the lamp shows very poor ignition behavior. After a duration of  $t_{PRERUN}$  the IC disables the ignition regulator and switches to the run mode (Phase 8) and all protection functions become active.

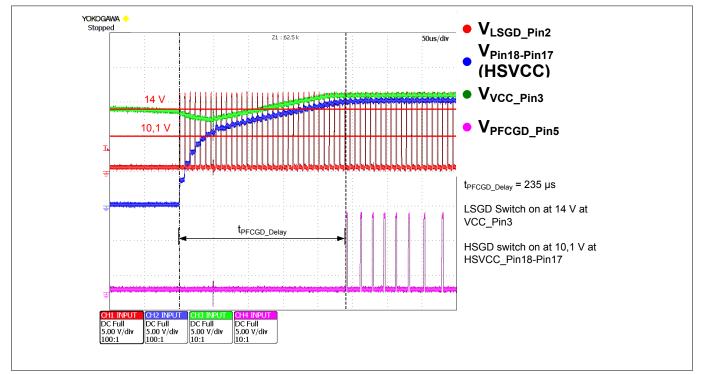

Figure 5

PFCGD Start-up Delay

A detailed evaluation of the start-up is shown in *Figure 5*. After reaching the V<sub>VCCO</sub>n threshold the IC enters power-up mode and starts LSGD switching with a short internal delay. The LSGD turns on several times to charge the HSVCC. In this time the voltage at the VCC pin breaks down a little bit because the IC current consumption is now higher than the current fed from the high ohmic start-up resistors R<sub>11</sub> and R<sub>12</sub>. The VCC capacitors C<sub>12</sub> and/or C<sub>13</sub> must be large enough to store the energy needed for charging the HSVCC capacitor C<sub>14</sub> to the V<sub>HSVCCOn</sub> threshold without reaching the UVLO threshold at VCC. After reaching the V<sub>HSVCCOn</sub> threshold (typ. 10.4 V) the HSGD starts working too, and the VCC supply is now generated from the working half-bridge via the charge pump and the energy provided is high enough to increase the VCC voltage up to the clamped limit of the external Z-diode D<sub>9</sub>. The PFCGD starts working with a delay of about 235 µs. This delay is implemented in the IC to ensure a stable VCC supply before the current consumption of the IC becomes higher due to the additional working PFCGD. This feature prevents UVLO during the start-up process. *Troubleshooting* provides advice on how to react to malfunctions in the functional sequence described here.

2 VCC Chip Supply

# 2 VCC Chip Supply

The high ohmic resistors ( $R_{11}$  and  $R_{12}$ ) for the startup supply have to be connected to the bus electrolytic capacitor to ensure an IC supply during start-up mode, latch mode and short interruption of the input voltage (emergency lighting feature according to VDE 0108). The IC logic implements an ability for self-generated reset. The condition for reset is an active IC with a current consumption of about  $I_{VCCSupply}$  with inactive gate drives. This results in a falling VCC voltage down to the  $V_{VCCOff}$  threshold, also called UVLO (Undervoltage Lockout), which resets the IC via the VCC. At this self-generated UVLO the IC goes into active mode with inactive gate drives. Without a working half-bridge there is no supply via the charge pump and the VCC capacitor discharges down to  $V_{VCCOff}$  (UVLO threshold), leading to a restart of the IC.

Please refer to Sections 3.2 and 3.3 of the Data Sheet for further information to functional restrictions in cases in which the start-up resistors or an external supply can provide too much current, and the IC cannot discharge the VCC capacitor. In latched failure mode the IC has a current consumption of  $I_{VCCLatch}$  and this current has to be delivered by the start-up resistors. The current out of the RES pin has to be considered for calculation of the start-up resistors together with  $I_{VCCLatch}$ .

## 2.1 Operation with Half-Bridge not Working

Without an active inverter section the start-up resistors have to supply the IC with a minimum current of  $I_{VCCLatch}$ . Please note that this current must be possible at the minimum input voltage. (This range is necessary for correct restart after internally generated UVLO and correct function of the hiccup mode). A maximum current of 2 mA is a good design proposal for correct IC function at self-generated UVLO.

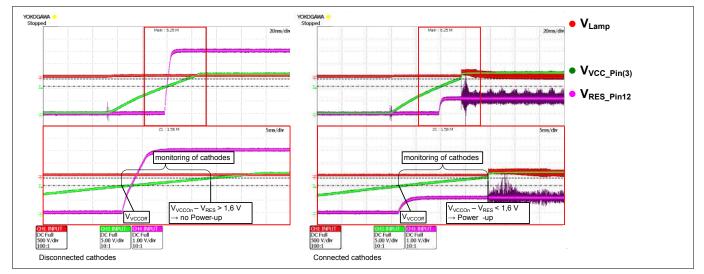

For the start-up of the IC supply it is important to check the voltage level at the RES pin. Due to the capacitor and resistor at the RES pin, the dv/dt at this pin is limited and, for example, might be slower than the VCC dv/dt at external supply or with low-ohmic start-up resistors. The voltage  $V_{RES}$  must reach the filament detection level before the IC supply voltage VCC reaches the  $V_{VCCOn}$  threshold. Otherwise, removed filaments cannot be detected correctly because the filament detection status is checked between  $V_{VCCOn}$ .

## Figure 6

dv/dt at VCC and RES Pins @ Start-up

*Figure 6* shows two oscillograms with the signals at the VCC and RES pins when connecting the input voltage. The left oscillogram shows the signals when the cathodes are open and the voltage at the RES pin rises to > 1.6 V. This voltage level must be reached while the IC monitors the cathodes for correct filament detection. The right oscillogram shows that the IC goes into power-up when the cathodes are connected.

2 VCC Chip Supply

## 2.2 Operation with Half-Bridge Working

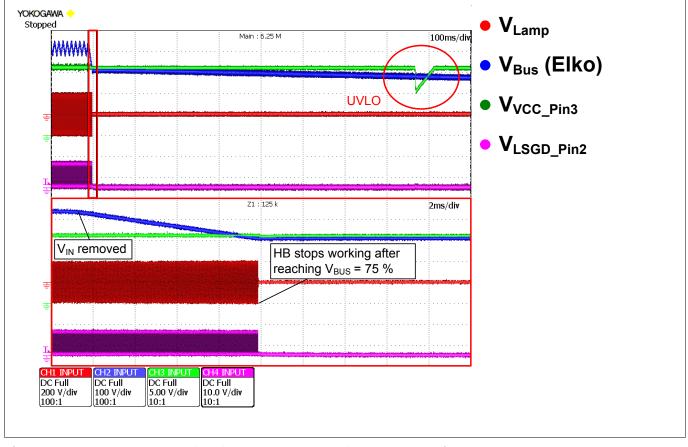

With continuous working of the inverter section (LSGD and HSGD) the IC is supplied mainly via the charge pump  $(C_{16}, D_7 \text{ and } D_8)$  connected to the half-bridge. With this solution of a VCC supply during run mode, the IC can generate an UVLO by itself by stopping the inverter.

An example of a self-generated UVLO is shown in *Figure 7*. To understand the following explanation, the state diagram in the Data Sheet (Section 3.3) must be viewed. Removing the board supply  $V_{IN}$  in run mode leads to discharging of the bus electrolytic capacitor. After  $V_{BUS}$  reaches the 75 % threshold the IC detects bus undervoltage and goes into "Fault U" failure handling with deactivation of the gate drives and entry to the powerdown mode. After about 750 ms the state machine exits the decision block "Counter Skip Preheat > 7" with "Y" and then goes into active mode with inactive gate drives. As a consequence, the VCC capacitor is discharged to the  $V_{VCCOff}$  threshold (red circle). This UVLO resets the IC logic.

Example of Self-Generated UVLO after Counter Skip Preheat > 7 = Y

3 PFC

# 3 PFC

The control of the PFC starts with a fixed operating frequency and increasing on-time, and changes over into critical conduction mode (CritCM) operation (also called borderline/transition conduction mode) as soon as a sufficient signal level at the pin PFCZCD is available. The benefit of this feature is to save external components for the compensation and for the synchronization with the AC input voltage. The dynamic response and the suppression of the superimposed ripple of the bus voltage fulfill even high requirements. Finally, during light load conditions the PFC control changes the operating mode from CritCM to DCM (discontinuous conduction mode) which provides stable operation even down to no load.

A detailed description of the digital control loop for PFC can be found in the Data Sheet (Section 2.4.3)

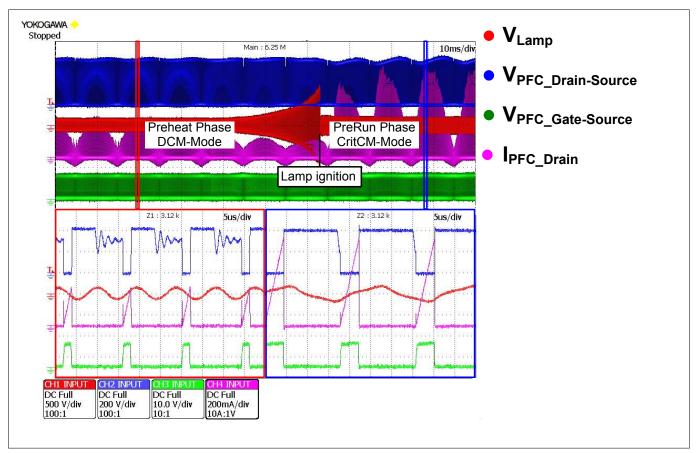

## Figure 8 DCM and CritCM Mode of the PFC Stage

*Figure 8* shows an oscillogram of the two operating modes DCM and CritCM of the PFC. The bottom left of the oscillogram shows the DCM waveforms under light load in the preheating phase. The bottom right illustrates the CritCM waveforms during run mode with a higher load.

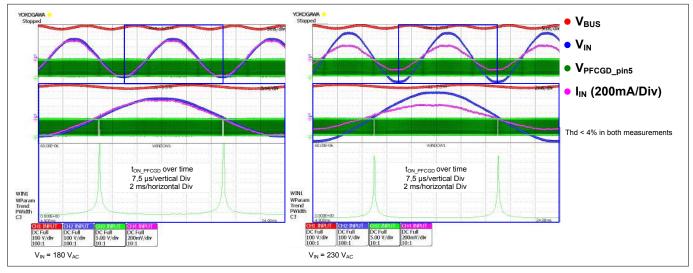

# 3.1 THD Correction

Figure 3-2 shows two oscillograms at different input voltages. The bottom thirds of the oscillograms show the PFCGD on-time over one input voltage half-wave. When the input voltage is decreasing, the on-time of the PFCGD increases and has its maximum at the minimum of the input voltage. The oscillogram on the left side shows the on-time at 180 V<sub>AC</sub> input voltage and the oscillogram on the right side is taken at an input voltage of 230 V<sub>AC</sub>. The oscillograms demonstrate the excellent performance of the PFC stage. In both cases the THD is below 4 % and no gap in current flowing near the input voltage minimum is visible. For proper THD correction in other designs it is necessary to modify the resistance at the PFCZCD pin in respect to the ratio and value of the PFC choke and the MOSFET size. A good way to find an optimum is to calculate  $R_{ZCD}$  with *#unique\_14/unique\_14\_Connect\_42\_equation-block\_uj3\_xzq\_nnb* in a first step.

## 3 PFC

Calculation of R<sub>ZCD</sub>:

$$R_{\rm ZCD} = \frac{\frac{R_{\rm ZCD}}{N_{\rm PFC}} \cdot V_{\rm BUS}}{1.5 \,\mathrm{mA}}$$

In a second step a potentiometer can be used to evaluate the optimal value for best THD optimization.

Figure 9 THD Correction: PFC On-time Extension over Input Half-Wave

*Figure 9* shows the waveform of the input current with a THD-optimized resistor at the PFCZCD pin. The overall THD for the input current harmonics is < 4 % with a gapless input current (magenta waveform). The bottom third of the oscillogram shows the on-time of the PFC MOSFET. Near to the zero-crossing of the input voltage, the on-time is increased by the IC via the signal at the PFCZCD pin for THD optimization.

4 Ignition Regulator - Control during Ignition

4

Ignition Regulator – Control during Ignition

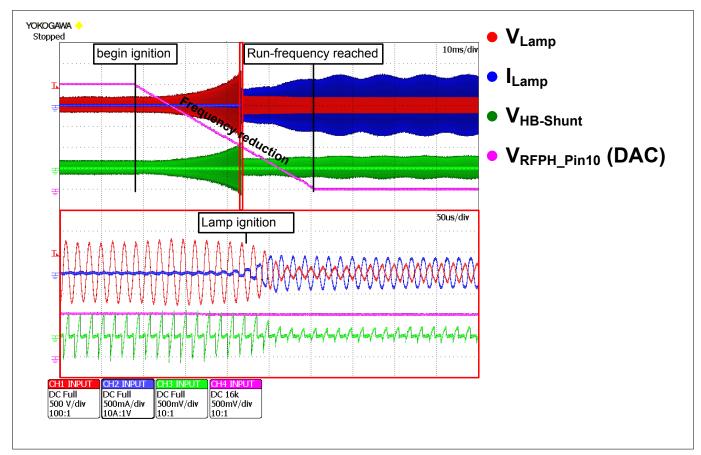

After entering the ignition mode, the frequency decreases from the preheating frequency to the run frequency. This frequency shift (generated by the internal digital logic) can be measured at the RFPH pin. The voltage is 2.5 V during preheating mode and decreases down to GND potential. When the adjusted ignition voltage is reached for the first time, the digital frequency control stays at its working point and an analog regulator takes over the ignition voltage regulation in respect to the adjusted frequency of the digital logic. The digital logic readjusts the frequency only when the working point leaves the regulation area of the analog regulator. After lamp ignition, the resonant circuit is damped by the lamp and the IC reduces the frequency down to the adjusted run frequency (Figure 4-1). The ignition regulator is also active in the pre-run phase to improve the ignition of lamps with bad ignition behavior.

## Figure 10 Normal Ignition Phase

If the voltage at the RFPH pin (DAC) reaches 0 V during the ignition phase without successful lamp ignition, the sequence control enters the pre-run phase with the ignition regulator still activated. This can be caused due to very high EMI at the LSCS pin, or due to a calculation of the resonant circuit and/or LSCS shunt resistors, that the ignition frequency is close to or below the run frequency. Several heavy bus voltage breakdowns during ignition can cause this behavior too. The ignition timeout timer cannot be set and the ignition voltage can stay about 625 ms longer than the maximum ignition time at the lamp.

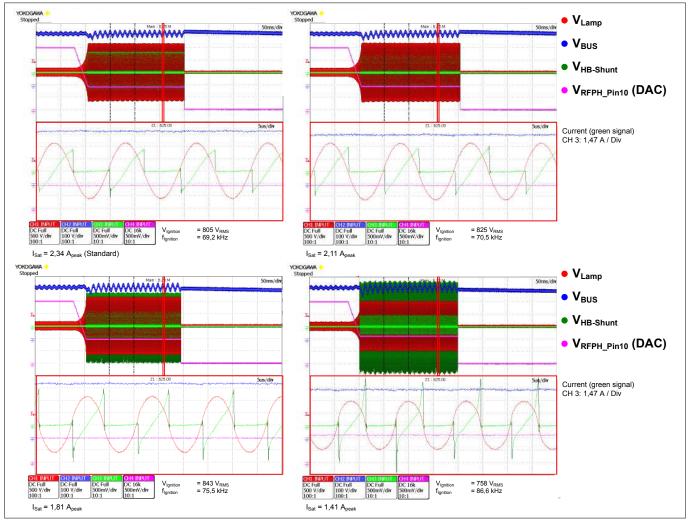

## 4.1 Operation Close to Different Saturation Levels

*Figure 11* shows four oscillograms taken with chokes of different saturation levels. The top-left oscillogram was taken with the standard choke of the demo board, the other ones use modified chokes with a smaller current capability and saturation effects. The ignition voltage is approximately constant over the saturation behavior of the lamp choke and best ignition voltage regulation (also at high temperatures of the lamp choke) is possible.

## 4 Ignition Regulator - Control during Ignition

Figure 11 Ignition voltage @ different levels of saturation of the resonant choke

These oscillograms demonstrate the performance of the ignition regulator at different levels of saturation. Actually, at relatively low saturation levels the ignition voltage is a little bit higher than with the standard choke. Even at very high saturation levels the ignition voltage breakdown is only about 5 %. Consequently, this ignition control concept is very suitable for designs working close to the magnetic saturation of the resonant choke and enables best ignition voltage regulation, also at higher temperatures of the ballast components. Due to the thermal behavior of the ferrite, the ability of the ignition regulator to work with saturated chokes offers a great advantage for restarts with a warmed-up ballast – for example, after a certain running time.

## 4.2 Bus Voltage Breakdown during Ignition

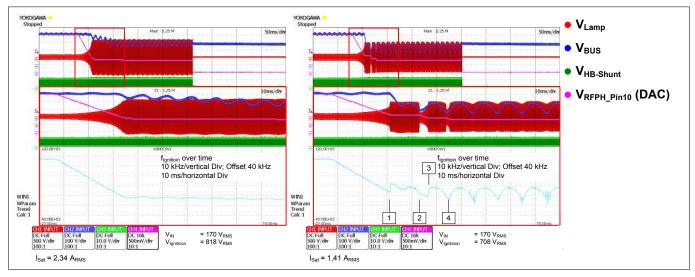

The following measurements of the ignition regulator at bus voltage breakdown were taken with small modifications to the demo board. The resonant capacitor  $C_{20}$  was mounted in a direction to realize current mode preheating. The demo board was prepared with 10  $\Omega$  substitution resistors for each cathode. This results in very high power consumption during ignition mode. The input voltage was also reduced to 170 V<sub>AC</sub> to provoke bus voltage breakdown during ignition mode because of the limited power that can be transferred by the PFC stage. *Figure 12* shows two oscillograms taken under these conditions to demonstrate that the ignition voltage control concept is also very suitable for current mode preheating ballasts in which the load during ignition becomes very high.

#### 4 Ignition Regulator - Control during Ignition

The left oscillogram shows the ignition voltage without saturation effects of the resonance inductor. The ignition frequency over time is illustrated in the bottom third of the oscillograms. After entering the ignition mode, the frequency decreases from about 107 kHz down to 70 kHz. At this point the frequency is regulated by the analog ignition voltage regulator to the maximum ignition voltage level. The oscillogram shows that there is no influence of the heavy bus voltage breakdown on the ignition voltage. The ignition regulator can compensate the bus voltage breakdown of about 25 % from 400 V down to 300 V completely

The oscillogram on the right shows the behavior in the same application under the same conditions but with heavy saturated choke – see *Figure 11*, bottom right. The digital logic reduces the inverter frequency down to about 75 kHz, then the ignition voltage reaches the adjusted ignition voltage and the analog regulator takes over the voltage control (Point 1). Due to the high bus voltage breakdown the analog regulator reaches the end of its working area and the digital logic compensates for this by reducing the inverter frequency again (Point 2 to Point 3). After this, the analog regulator takes over the regulation as seen at Point 1. At Point 4 the working area of the analog regulator is left again and the digital frequency control reduces the frequency. From this point onward, the analog ignition control regulator takes over and almost entirely eliminates the high bus voltage ripple of about 150 V.

**5 Filament Detection**

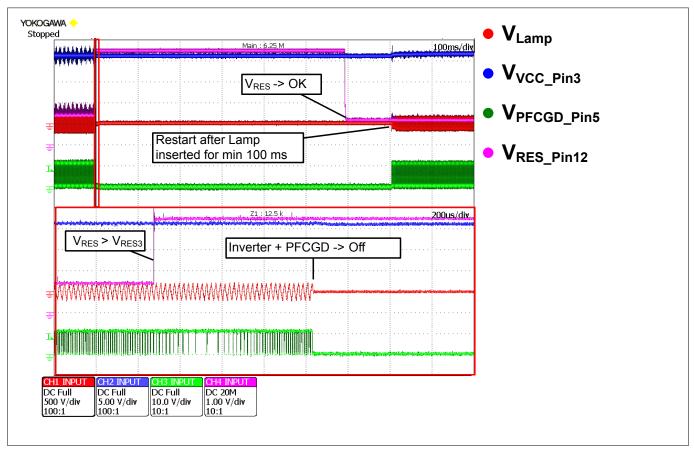

# 5 Filament Detection

The high-side filament is detected via the LVS pin while the low-side filament is monitored via the RES pin. For proper filament detection the LVS and RES circuits have to be dimensioned correctly because they act together and not independently of each other. The RES pin acts as a current source and in order of the voltage at this pin (generated with a resistor R<sub>36</sub>, connected via the low-side filament to GND) the IC detects the filaments. The current flowing out of the RES pin depends on the voltage level V<sub>RES</sub> and the status of the high-side filament.

When there is no current or a current below the filament detection limit flowing into the LVS pin, the current out of the RES pin is doubled and, as a consequence, the voltage at this pin rises and reaches the level for detecting missing filaments. In this way, the result from the high-side filament detection is mirrored at the RES pin. If the lowside filament at the RES pin is not inserted, the voltage at this pin rises and also reaches the level for detecting missing filaments because there is no GND connection.

## 5.1 LVS Pin

This pin has the function of detecting the high-side cathode before the IC starts and lamp removal in failure mode. In the run mode the pin detects the EOL1 (overload) and EOL2 (rectifier effect) conditions. This is realized by analyzing the amplitude and the DC offset of the lamp voltage via an equivalent current into the pin. If the functions are not needed, the LVS pin can be deactivated by connecting the pin directly to GND. In this case EOL1 and EOL2 detection via this pin is not possible. A deactivated LVS pin can be reactivated when the voltage at this pin goes higher than V<sub>LVSEnable1</sub> during run mode. For correct functioning of the LVS pin, the resistors for filament detection have to be connected directly after the line rectifier to ensure that the short input voltage interruption can be detected with the LVS pin. The charge of the preheating capacitor  $C_{21}$  must be covered by the capacitor in the EOL network C<sub>40</sub> in such a way that no fail detection of inserted cathode occurs. If the capacitor in the preheating circuit C<sub>21</sub> has a high capacitance and C<sub>40</sub> is relatively low, a transient current flows via C<sub>21</sub> and L<sub>21</sub> that can be high enough to lead to high-side filament detection. An internal voltage of 5 V can be used for calculation of the LVS current before startup (not specified in the Data Sheet - see also The IC Starts without a High-Side Filament). This means that the current flowing into the LVS pin can be calculated with the voltage over the LVS series resistor (between R<sub>41</sub> and R<sub>42</sub>) related to GND subtracted by 5 V and divided by the value of R<sub>41</sub>. The safest solution is to design the LVS network in such a way that the voltage at C<sub>40</sub> stays below 5 V without a connected HS filament.

Calculation of I<sub>LVSstartup</sub>:

$$I_{\rm LVSstartup} = \frac{V_{C40 \rm toGND} - V_{\rm BUS}}{R_{41}}$$

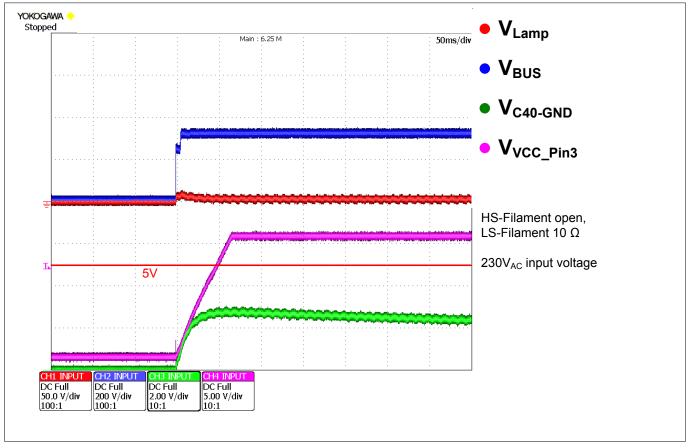

*Figure 13* shows an oscillogram with the waveforms for start-up without a connected high-side filament. The voltage across  $C_{40}$  in reference to GND is below 5 V (green signal). Due to the internal voltage of 5 V there is no current flowing into the LVS pin and no wrong high-side filament detection can occur. If this voltage rises above  $5V+I_{LVSSink}$  multiplied by the value of  $R_{41}$ , wrong high-side filament detection can provoke a single start-up of the IC. In this case the value of  $C_{40}$  or  $R_{41}$  can be increased. If possible, decreasing the capacitance in the preheating circuit can help to reduce the current flowing into the LVS pin. A third option is to reduce the feeding voltage by the divider  $R_1$ ,  $R_2$ ,  $D_{R12}$  from the rectified AC input voltage.

# Ballast Design for 54W UV-C Disinfection Lamp (Voltage Mode Preheating) with Controller IC ICB2FL03G & 600V CoolMOS<sup>™</sup> PFD7

## **5 Filament Detection**

## Figure 13 Startup without High-side Filament

During run mode there is no high-side filament detection via the LVS pin.

A step-by-step tutorial for dimensioning of the EOL1 and EOL2 thresholds is given in *Sample Calculation: EOL for 54W T5 Design (Excel)* of this document.

## 5.2 RES Pin

To deactivate the filament detection for high-side and low-side filaments the RES pin can be connected directly to GND. As explained in *Filament Detection*, this pin is a current source and detects if the filaments are present via the voltage drop at R<sub>36</sub>. The current out of the RES pin is affected by the LVS status during start-up and the actual voltage at this pin. During run mode, this pin detects the low-side filament. When this filament is broken or removed, the voltage will rise to 5 V. The voltage passes the V<sub>RES3</sub> threshold for detecting a missing low-side filament.

For current mode preheating designs an additional series resistor to the RES pin (for example 330  $\Omega$ ) is recommended to avoid destroying the ESD structure if the voltage at the RES pin rises to higher levels. This voltage spike can occur in current mode preheating designs during lamp removal and depends on the resonant circuit and RES pin wiring.

For reliable filament detection during start-up, the voltage  $V_{RES}$  has to reach the filament detection level until the chip supply voltage VCC reaches the turn-on threshold of  $V_{VCCOn}$  (see also *Figure 6*).

# 6 Detection of Failures

This chapter provides advice in the event of failures along with examples for evaluating the failure detection functions. Detailed descriptions of the failure conditions can be found in the Data Sheet. Chapters 3 and 4 of the Data Sheet show tables and flow charts indicating which protection feature is active in which operating mode and how the IC will react to each particular failure.

## 6.1 Surge Detection

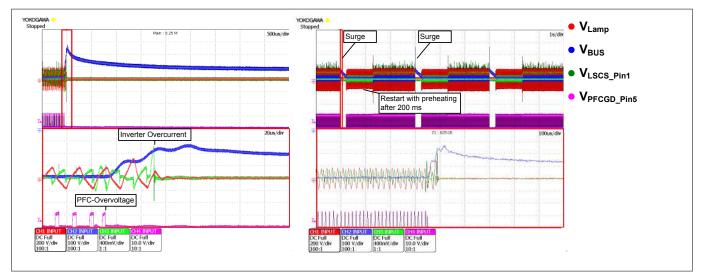

The ICB2FL03G implements a special detection for surge events. Bus overvoltage followed by inverter overcurrent is detected as a surge, which leads to a restart without latching this failure. Figure 6-1 shows two oscillograms with the signals under surge conditions. For these oscillograms the half-bridge MOSFETs were replaced by 500 V types to provoke an earlier avalanche breakdown in the case of bus overvoltage. In the original mounting with 600 V MOSFETs the surge voltage must be so high that other components can become destroyed before the half-bridge breakdown initiates surge detection.

Figure 14 Surge Detection; Surge Pulse of 1100 V

The left oscillogram shows one single surge event with a higher resolution and the right one shows three surge events for explanation of the flow diagram. Directly after bus voltage rising due to the surge pulse, the PFC stage detects PFC overvoltage and stops the PFCGD. At a bus voltage of about 620 V the half-bridge MOSFET breaks down due to the avalanche effect. This results in a high current spike at the LSCS pin. The IC detects this overcurrent during overvoltage and stops the inverter gate drives (see Chapter 3.3 in the Data Sheet: "Fault A"). This signal combination does not increment the "Fault Counter" and leads to an IC restart after about 200 ms with preheating. This can be seen in the right oscillogram.

It is important that the time constant of the low-pass filter at this PFCVS pin (generated by the voltage divider and  $C_{11}$ ) is small enough that the voltage can rise fast enough to the 109 % threshold during surge conditions. Otherwise the surge condition cannot be clearly detected.

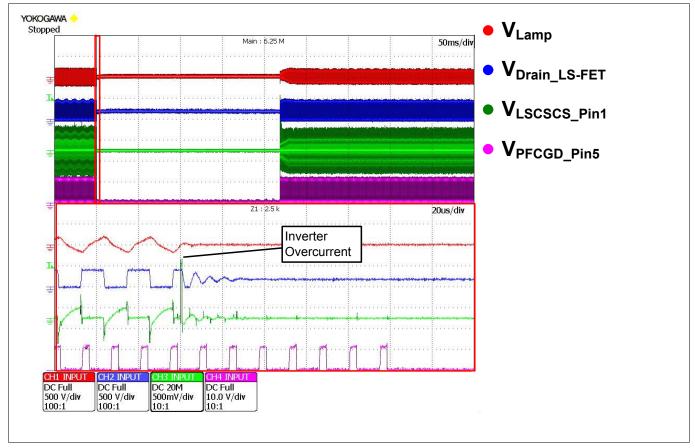

## 6.2 Inverter Overcurrent Protection

The inverter overcurrent protection via the LSCS pin detects two different thresholds dependent on the actual operation mode. The first threshold of  $V_{LSCSOvC2}$  is only active during preheating and run modes. In all other modes the detection threshold of  $V_{LSCSOvC1}$  is active for inverter overcurrent protection. Overshooting these thresholds results in a single restart of the IC. After a second detection within 40 s the IC goes into latched fault mode. This means that an input voltage interruption or a lamp removal is necessary for a new start-up of the IC.

## Figure 15 Inverter Overcurrent

*Figure 15* shows an oscillogram with a generated inverter overcurrent. A series resistor of  $1 \text{ k}\Omega$  was inserted in series with the LSCS pin for this measurement. The overcurrent signal is generated by a waveform generator and is overlaid directly at the LSCS pin via a diode.

The half-bridge (blue signal) stops immediately after detecting inverter overcurrent: Fault F. With a short delay of about 100 µs the PFCGD stops working too. This delay is caused by the digital logic. About 200 ms after turning off and incrementing the failure counter, the IC starts another start-up. If a second inverter overcurrent or another Fault F failure occurs within 40 s, the IC goes into latched fault mode.

## 6.3 PFC Overcurrent Protection

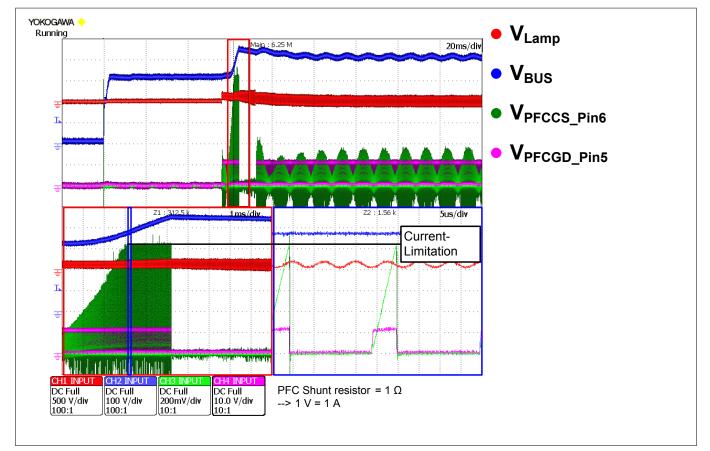

**Figure 16** shows an oscillogram of the demo board start-up. The green waveform shows the voltage at the PFCCS pin (across the PFC shunt resistor of 1  $\Omega$ ). In the beginning, the PFC starts in soft start mode and with a short turn-on time. The turn-on time is increased continuously because the bus voltage is below the nominal value (red area of the oscillogram).

#### Figure 16 PFC Overcurrent

The current through the PFC inductor increases and after reaching the PFC overcurrent threshold of V<sub>PFCCSOff</sub> the PFCGD turns off cycle by cycle. This working point is shown in the blue area of the oscillogram and is not handled as an operation fault. This feature protects the PFC stage against overload.

## 6.4 Bus Overvoltage Protection 109% – 105% Threshold

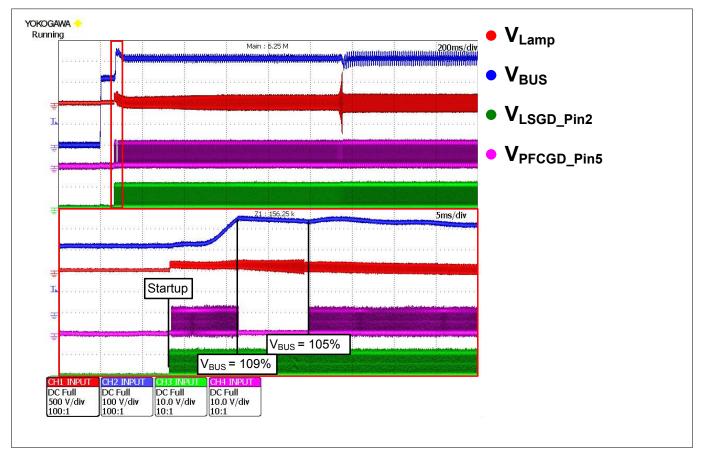

Depending on the input voltage, a short bus overvoltage can occur during start-up, which is fully covered by the bus overvoltage protection. *Figure 17* shows an oscillogram explaining the functionality of the bus overvoltage protection. Start-up activates the inverter gate drives and the PFC gate drive with a short delay. Then the bus voltage rises and reaches the 109 % threshold. The PFC gate drive stops immediately as long as the bus voltage is above the 105 % threshold and the PFC gate drive is activated again, and the bus voltage goes to the nominal value. If the bus voltage is > 109% for longer than 625 ms, the IC goes into power-down and stops working. The IC restarts automatically without preheating when the bus voltage is below the 105 % threshold.

#### Figure 17 Bus Overvoltage Hysteresis (Start-up)

An additional description of the overvoltage detection in run mode can be found in *Surge Detection*. The surge detection described there is a combined detection of bus overvoltage and inverter overcurrent during pre-run or or run mode.

## 6.5 Bus Undervoltage Protection in Run Mode with 75% Threshold

This failure protection is described in *Emergency Detection* because it is used for the emergency lighting feature. Bus undervoltage can also occur in other operation modes. This results in running with lower bus voltage until the IC detects this failure condition after entering run mode.

## 6.6 EOL Detection

This section gives a short introduction on how the EOL (End of Life) tests with high accuracy can be done on our demo board. More information and a description of the normative measurement can be found in EN61347-2-3 (VDE 0712-33). The names EOL1 and EOL2 are defined by Infineon Technologies AG. A lamp

overvoltage/overload is called EOL1 and the rectifier effect according to the standard is called EOL2. The standard contains also circuit descriptions that are necessary for performing the EOL tests on the ballast. An additional description on how this detection works can be found in Section 2.5 of the Data Sheet. The EOL conditions are monitored via the LVS pin. A step-by-step guide with a detailed explanation for basic calculation of the LVS network is given in *Sample Calculation: EOL for 54W T5 Design (Excel)*. Due to some omissions in the calculations, an experimental adjustment in the circuit may be necessary.

For the following measurements the demo board was supplied with 230  $V_{DC}$  because under DC supply there is no influence of the AC ripple on the measurement. When the tests are done with an AC supply it is important that the measurement field covers at least a full input voltage half-wave and an integer multiple of it. Otherwise, due to the AC ripple, the measurement cannot be reproduced. In this case the resolution of the oscilloscope must be high enough to record all high-frequency waveforms with good accuracy.

## 6.6.1 EOL1 (Overload)

C21 O YOKOGAWA Stopped VLamp Man : 6.25 M C17 O-L2 K2 K1 V<sub>EOL\_Resistor</sub> EOL\_Resistor FOI 1 Test circuit REOL1 K6 K5 Rsub Rsub R36 = 538 V<sub>PP</sub> VLamp VLam = 188 Vpm RES-PinO FOI 1 Detection

Figure 15 shows an oscillogram after EOL1 detection and an example of an EOL2 test setup.

## Figure 18 EOL1 (Overload) Detection; EOL1 Test Setup

The test was done with a series resistor to the lamp. The resistance of the series resistor was increased until the IC detected the lamp overvoltage and entered the failure analysis flow. The measured EOL1 shutdown voltage was 538 V<sub>PP</sub>. This value matches very well with the calculated value (*Sample Calculation: EOL for 54W T5 Design (Excel)*). There is an internal counter which counts up when the EOL1 event is present and counts down when the EOL1 event is not detected. If the EOL1 threshold is not reached in every cycle, the time to turn off the IC can be longer than 620  $\mu$ s.

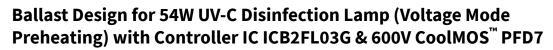

# 6.6.2 EOL2 (Rectifier Effect)

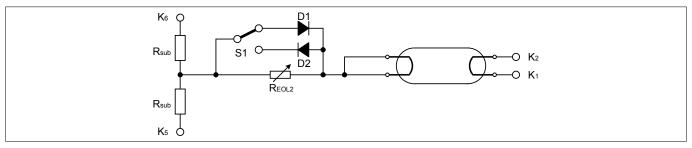

*Figure 19* shows an example test setup for the EOL2 test. A complete description can be found in the standard EN61347-2-3 (VDE 0712-33). When the current flows via D1, a positive rectifier effect is simulated (EOL2+). Current flowing via D2 simulates a negative rectifier effect (EOL2). The level of the positive or negative superimposed lamp voltage can be adjusted with REOL2. The higher the value of this resistor, the higher the EOL2 voltage because the resonant circuit of the demo board works like a constant current source for the lamp current.

#### Figure 19 EOL2 Test Setup

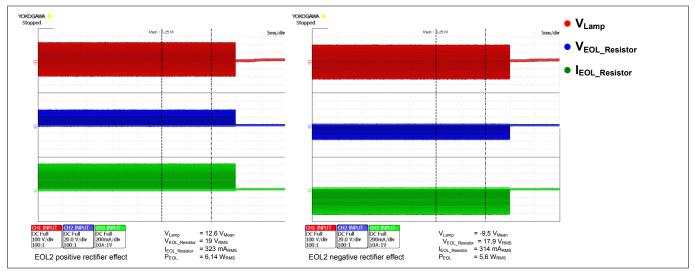

This failure condition is allowed for a duration of 2.5 s until the IC goes into failure analysis flow. So for the exact measurement of the EOL2 thresholds it is important to increase the value of  $R_{EOL2}$  very slowly. The EOL2 power can be calculated by multiplying the RMS values of the current through  $R_{EOL2}$  and the voltage over this resistor. *Figure 20* shows an example of a measurement for EOL2+ (left) and EOL2 (right) detection.

## Figure 20 EOL2 (Rectifier Effect) Detection

The measured values for EOL2 detection are +6.1 W and -5.6 W. The calculated values from *Sample Calculation: EOL for 54W T5 Design (Excel)* are 5.3 W for EOL2+ and 5.3 W for EOL2, a little bit lower than the measured values. This is due to some omissions in the calculations and the influence of the voltage drop of the diode (D1 or D2 of the test circuit), which generates a higher RMS value of the voltage via the EOL2 resistor for the measured values. This means that an experimental adjustment in the circuit may be necessary. Please note that parasitic inductivity of the resistors have to be low.

The difference between the positive and negative thresholds is due to the internal IC design. There is an internal series resistor of about 5 k $\Omega$  to an internal voltage source of about 600 mV at the LVS pin (not specified in the Data Sheet). The internal signal processing of the IC generates an internal potential at the LVS pin of about 800 mV at +42  $\mu$ A and about 400 mV at -42  $\mu$ A. Due to these differences the positive lamp voltage shift for EOL2 must be higher than the negative to reach the EOL2 turn-off current at the LVS pin. The EOL2 power results from the lamp current multiplied by the EOL2 lamp voltage shift. Consequently, the difference between positive and negative EOL2 rises with the lamp current because the EOL2 lamp voltage shift needed for the same EOL2 power is smaller and the influence of the voltage at the LVS pin becomes higher. Figure 6-14 shows a theoretical example of this effect for a designed EOL2 power rating of 6 W.

#### Figure 21 EOL2 Power Difference

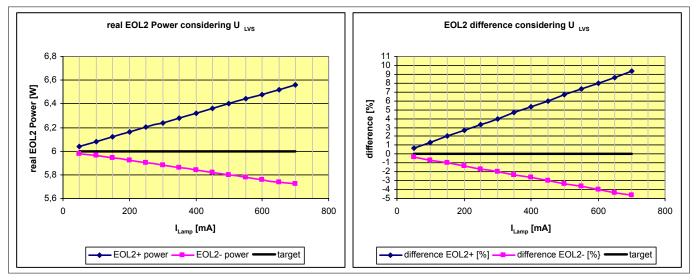

When the symmetry between the positive and negative EOL2 power must be as good as possible, an additional compensation circuit can feed an additional current into the LVS pin to correct the offset/asymmetry between the positive and negative EOL2 thresholds. *Figure 22* shows an example of such a compensation circuit.

#### Figure 22 Compensation Circuit for better EOL2 Symmetry @ High Lamp Currents

The reference names of R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and C<sub>1</sub> are referenced to the small schematic in *Figure 35* and these components are a part of the standard BOM without compensation at the LVS pin. Only three resistors connected to the IC supply voltage are necessary (shown in red) for the compensation circuit. For this design, good matching between the positive and negative EOL2 threshold can be achieved with R4 = 2.2 MΩ, R5 = 680 kΩ and R6 = 470 kΩ. Due to the high-ohmic values of the resistors there are no high losses in this compensation circuit. Please note that this circuit can influence the filament detection via the current into the LVS pin before start-up.

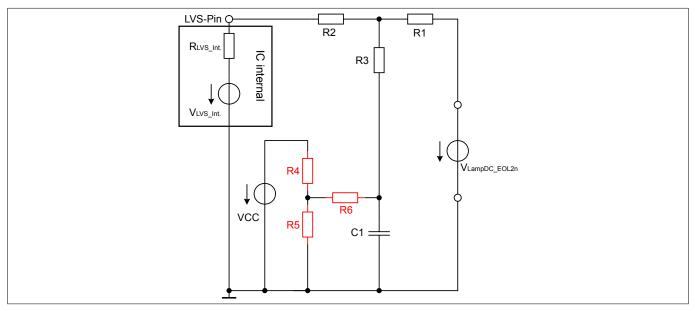

## 6.6.3 Switched Rectifier Effect

*Figure 23* shows two oscillograms of the IC behavior when the switched rectifier effect (according to EN61347-2-3; VDE 0712-33) occurs during run mode. Applying this test to the ballast leads to an EOL1 detection

because the peak lamp voltage rises to the EOL1 detection limit and the duration to turn off is much shorter than for EOL2 detection. There is an internal counter which counts up when the EOL1 event is present and counts down when the EOL1 event is not detected. If the EOL1 threshold is not reached in every cycle, the time to turn off the IC can be longer than 620  $\mu$ s (e.g. the amplitude is close to the detection limits). After detecting EOL1 the IC goes into power-down mode with a typical current consumption of I<sub>VCCLatch</sub>. In this mode, the maximum LVS current for the safe operating area is limited to max. 210  $\mu$ A. Due to this failure condition the voltage at C40 in reference to GND can rise to high values and a voltage limitation at C40 might be necessary to limit the current flowing into the LVS pin.

## Figure 23 Switched Rectifier Effect according to EN 61347-2-3 (VDE 0712-33)

The left oscillogram shows the signals when the switched rectifier effect is applied in the negative direction and the right one shows the behavior for the positively switched rectifier effect.

Result: The requirements of the standard are fulfilled.

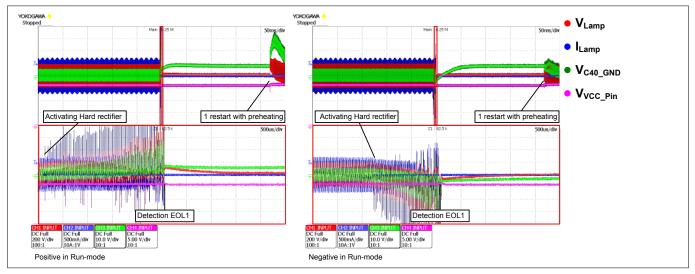

## 6.6.4 Hard Rectifier Effect

*Figure 24* shows two oscillograms with the IC behavior when the hard rectifier effect (according to EN 61347-2-3; VDE 0712-33) occurs during run mode.

Applying this test in run mode leads to EOL1 detection due to the same reasons as explained in *Switched Rectifier Effect*.

Figure 24 Hard Rectifier Effect according to EN 61347-2-3 (VDE 0712-33)

The left oscillogram shows the signals when the hard rectifier effect is applied in the positive direction while the oscillogram on the left side shows the hard rectifier effect when applied in the negative direction. Result: The requirements of the standard are fulfilled.

## 6.7 Capacitive load (Cap Load)

This section is intended to give an understanding of the effects that take place when the ballast works under capacitive load conditions. To help the explanation, two oscillograms show the signals under cap load 1 and cap load 2. Further information on this can be found in the Data Sheet (Section 2.6).

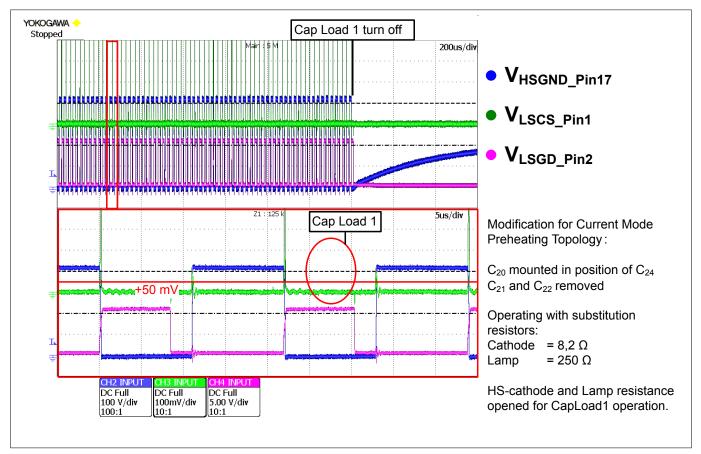

# 6.7.1 Cap Load 1 (Idling Detection / Current Mode Preheating)

This protection feature is only necessary in current mode preheating topologies, where the half-bridge goes into idling operation when the lamp is disconnected during run mode. In current mode preheating designs, the resonant capacitor ( $C_{20}$ ) is connected "behind" the lamp cathodes, so the cathodes are in series with the resonant capacitor. Removing the lamp and the cathodes results in an open load condition with direct charging and discharging of the snubber  $C_{16}$  by the MOSFET, and the half-bridge switches into cap load 1 operation.

## Figure 25 Cap Load 1 Detection in Designs with Current Mode Preheating

*Figure 25* shows an oscillogram in cap load 1 operation with a modified demo board for current mode preheating topologies. The modification to the demo board is described beside the oscillogram. The horizontal red line indicates the V<sub>LSCSCap1</sub> threshold and the red circle indicates the area where the signal of the LSCS pin should reach this threshold during normal operation. Only a high current spike at the moment of turning on the LS-FET is present in this oscillogram. This leads to "Fault F" detection after about 2500 ms.

In current mode preheating designs there is a higher probability of overload detection during ignition mode. In current mode designs the voltage at the RES pin can increase to very high levels when removing the lamp during ignition and run modes. Please check *RES Pin* for information on how the circuit at the RES pin can be modified for this ballast topology.

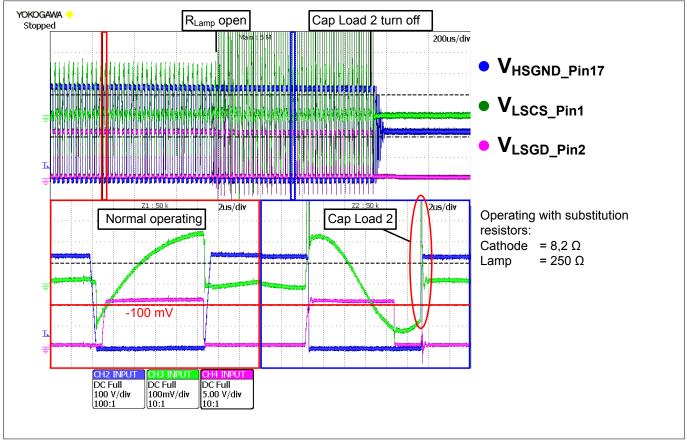

## 6.7.2 Cap Load 2 (Overcurrent / Operation Below Resonance)

Cap load 2 operation can only occur in designs when the run frequency is below the resonance frequency of the unloaded resonance circuit. Cap load 2 operation is detected if the voltage at the LSCS pin is below  $V_{LSCSCap3}$  for longer than  $t_{LSCSCap2}$  directly before the HSGD is turned on, or if it exceeds a threshold of  $V_{LSCSCap2}$  for longer than  $t_{LSCSCap3}$  during on-switching of the HSGD. The duration for detecting this failure is 620  $\mu$ s.

## Figure 26 Cap Load 2 Detection

*Figure 26* shows an oscillogram under Cap load 2 operation. The red circle shows the relevant area for detecting cap load 2.

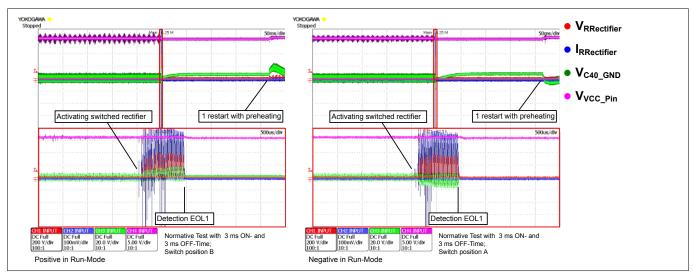

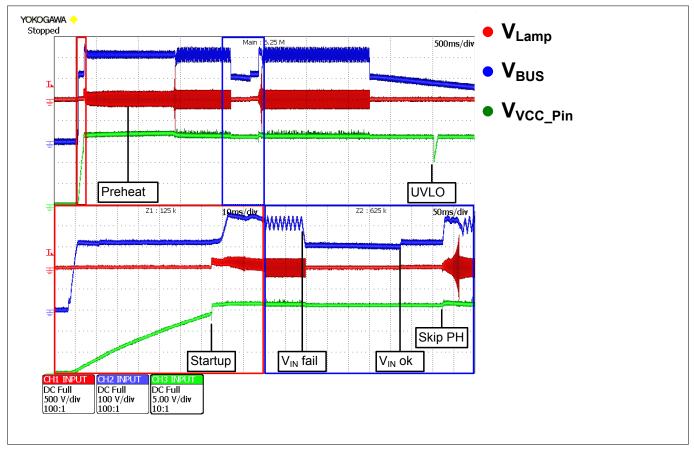

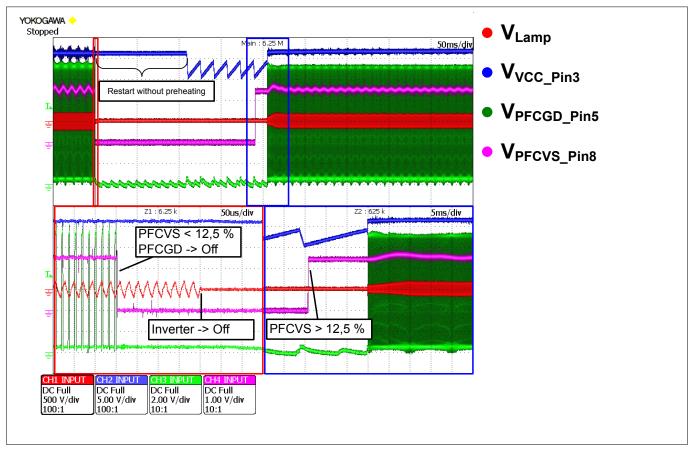

## 6.8 Emergency Detection

The ICB2FL03G supports emergency detection requirements (according to VDE 0108). To fulfill this standard, it is necessary that the illumination returns immediately after short input voltage interruptions. The ICB2FL03G detects short interruptions of the input voltage via the LVS pin together with the value of the bus voltage, and restarts within a specific time frame directly with lamp ignition without a prior preheating phase.

Please check the advice given in *VCC Chip Supply* and *LVS Pin* on designing the ballast in such a way that correct emergency detection functionality is guaranteed. In the event of an input voltage interruption, the IC supply has to be connected to the bus voltage. *Figure 27* shows an oscillogram that demonstrates the functionality of this feature. The oscillogram shows the following sequences: start from connecting the input voltage to run mode followed by input voltage interruption of about 250 ms with direct lamp ignition without preheating and then an input voltage interruption of about 3 s in run mode.

# Ballast Design for 54W UV-C Disinfection Lamp (Voltage Mode Preheating) with Controller IC ICB2FL03G & 600V CoolMOS<sup>™</sup> PFD7

#### **6 Detection of Failures**

#### Figure 27 Emergency Detection

The bottom left of the oscillogram shows the phase from turning on the input voltage to the preheating phase. The bottom right of the oscillogram shows an input voltage interruption in run mode ( $V_{IN}$  fail) for about 250 ms. After reaching 75 % of the rated bus voltage the IC detects bus undervoltage, sets the "skip preheating" flag and stops the inverter. The current consumption falls to a minimum value and the IC checks the presence of the cathodes 7 times in an interval of  $t_{TIMER1}$ . When the input voltage is present again ( $V_{IN}$  ok), checked via the current to the LVS pin, and the counter skip preheating is < 7, the IC restarts without preheating. In the top right of the oscillogram there is a second interruption of the input voltage for longer than 700 ms and the IC goes into a self-generated reset (via UVLO). This resets the "skip preheating" flag and the IC will start with preheating after a new input voltage detection. For an external supply it must be ensured that the IC can perform this UVLO.

7

# Advice for Design, Layout and Measurements

This section gives some advice on ballast design with the ICB2FL03G. It also provides some additional technical information on the IC function and advice for measurements.

## 7.1 Deactivation of Lamp Section

## 7.1.1 Deactivation of Lamp Section