SLAS094E - MARCH 1995 - REVISED OCTOBER 2000

- 8-Bit Resolution

- Easy Microprocessor Interface or Stand-Alone Operation

- Operates Ratiometrically or With 5-V Reference

- 4- or 8-Channel Multiplexer Options With Address Logic

- Input Range 0 to 5 V With Single 5-V Supply

- Remote Operation With Serial Data Link

- Inputs and Outputs Are Compatible With TTL and MOS

- Conversion Time of 32 μs at f<sub>clock</sub> = 250 kHz

- Functionally Equivalent to the ADC0834 and ADC0838 Without the Internal Zener Regulator Network

- Total Unadjusted Error . . . ±1 LSB

### description

These devices are 8-bit successive- approximation analog-to-digital converters, each with an input-configurable multichannel multiplexer and serial input/output. The serial input/ output is configured to interface with standard shift registers or microprocessors. Detailed information on interfacing with most popular microprocessors is readily available from the factory.

The TLC0834 (4-channel) and TLC0838 (8-channel) multiplexer is software-configured for single-ended or differential inputs as well as pseudodifferential input assignments. The differential analog voltage input allows for common-mode rejection or offset of the analog zero input voltage value. In addition, the voltage reference input can be adjusted to allow encoding of any smaller analog voltage span to the full 8 bits of resolution.

The TLC0834C and TLC0838C are characterized for operation from  $0^{\circ}$ C to  $70^{\circ}$ C. The TLC0834I and TLC0838I are characterized for operation from  $-40^{\circ}$ C to  $85^{\circ}$ C. The TLC0834Q is characterized for operation from  $-40^{\circ}$ C to  $125^{\circ}$ C.

# **AVAILABLE OPTIONS**

|                |                         |                          | PACKAGE             |                       |  |  |  |  |  |  |  |

|----------------|-------------------------|--------------------------|---------------------|-----------------------|--|--|--|--|--|--|--|

| TA             | SMALL<br>OUTLINE<br>(D) | SMALL<br>OUTLINE<br>(DW) | PLASTIC DIP<br>(N)  | TSSOP<br>(PW)         |  |  |  |  |  |  |  |

| 0°C to 70°C    | TLC0834CD               | TLC0838CDW               | TLC0834CN TLC0838CN | TLC0834CPW TLC0838CPW |  |  |  |  |  |  |  |

| -40°C to 85°C  | TLC0834ID               | TLC0838IDW               | TLC0834IN TLC0838IN | TLC0834IPW TLC0838IPW |  |  |  |  |  |  |  |

| -40°C to 125°C | _                       | _                        | TLC0834QN —         | _                     |  |  |  |  |  |  |  |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLAS094E – MARCH 1995 – REVISED OCTOBER 2000

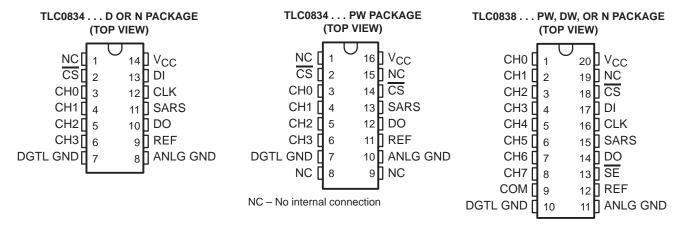

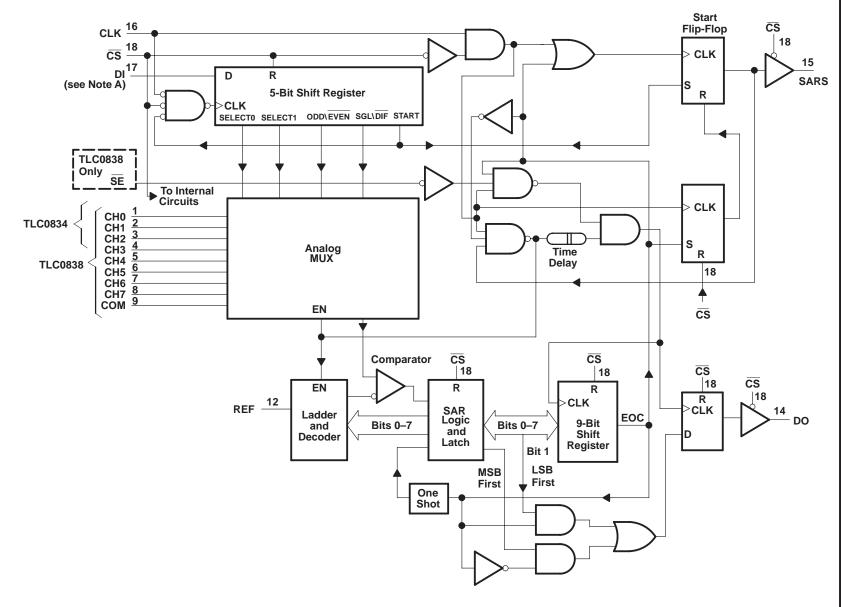

# functional block diagram

NOTES A: For the TLC0834, DI is input directly to the D input of SELECT1; SELECT0 is forced to a high.

B: Terminal numbers shown are for the DW or N package.

SLAS094E - MARCH 1995 - REVISED OCTOBER 2000

# functional description

The TLC0834 and TLC0838 use a sample-data-comparator structure that converts differential analog inputs by a successive-approximation routine. Operation of both devices is similar with the exception of  $\overline{SE}$ , an analog common input, and multiplexer addressing. The input voltage to be converted is applied to a channel terminal and is compared to ground (single ended), to an adjacent input (differential), or to a common terminal (pseudo differential) that can be an arbitrary voltage. The input terminals are assigned a positive (+) or negative (–) polarity. When the signal input applied to the assigned positive terminal is less than the signal on the negative terminal, the converter output is all zeros.

Channel selection and input configuration are under software control using a serial-data link from the controlling processor. A serial-communication format allows more functions to be included in a converter package with no increase in size. In addition, it eliminates the transmission of low-level analog signals by locating the converter at the analog sensor and communicating serially with the controlling processor. This process returns noise-free digital data to the processor.

A particular input configuration is assigned during the multiplexer-addressing sequence. The multiplexer address shifts into the converter through the data input (DI) line. The multiplexer address selects the analog inputs to be enabled and determines whether the input is single ended or differential. When the input is differential, the polarity of the channel input is assigned. Differential inputs are assigned to adjacent channel pairs. For example, channel 0 and channel 1 may be selected as a differential pair. These channels cannot act differentially with any other channel. In addition to selecting the differential mode, the polarity may also be selected. Either channel of the channel pair may be designated as the negative or positive input.

The common input on the TLC0838 can be used for a pseudodifferential input. In this mode, the voltage on the common input is considered to be the negative differential input for all channel inputs. This voltage can be any reference potential common to all channel inputs. Each channel input can then be selected as the positive differential input. This feature is useful when all analog circuits are biased to a potential other than ground.

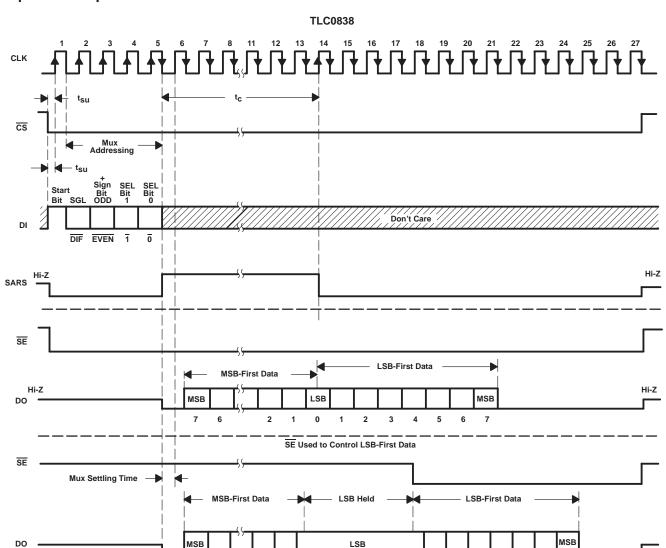

A conversion is initiated by setting  $\overline{CS}$  low, which enables all logic circuits.  $\overline{CS}$  must be held low for the complete conversion process. A clock input is then received from the processor. On each low-to-high transition of the clock input, the data on DI is clocked into the multiplexer-address shift register. The first logic high on the input is the start bit. A 3- to 4-bit assignment word follows the start bit. On each successive low-to-high transition of the clock input, the start bit and assignment word are shifted through the shift register. When the start bit is shifted into the start location of the multiplexer register, the input channel is selected and conversion starts. The SAR status output (SARS) goes high to indicate that a conversion is in progress, and DI to the multiplexer shift register is disabled for the duration of the conversion.

An interval of one clock period is automatically inserted to allow the selected multiplexed channel to settle. DO comes out of the high-impedance state and provides a leading low for one clock period of multiplexer settling time. The SAR comparator compares successive outputs from the resistive ladder with the incoming analog signal. The comparator output indicates whether the analog input is greater than or less than the resistive-ladder output. As the conversion proceeds, conversion data is simultaneously output from DO, with the most significant bit (MSB) first. After eight clock periods, the conversion is complete and SARS goes low.

The TLC0834 outputs the least-significant-bit (LSB) first data after the MSB-first data stream. When  $\overline{SE}$  is held high on the TLC0838, the value of the LSB remains on the data line. When  $\overline{SE}$  is forced low, the data is then clocked out as LSB-first data. (To output LSB first,  $\overline{SE}$  must first go low, then the data stored in the 9-bit shift register outputs LSB first.) When  $\overline{CS}$  goes high, all internal registers are cleared. At this time, the output circuits go to the high-impedance state. If another conversion is desired,  $\overline{CS}$  must make a high-to-low transition followed by address information.

DI and DO can be tied together and controlled by a bidirectional processor I/O bit received on a single wire. This is possible because DI is only examined during the multiplexer-addressing interval and DO is still in the high-impedance state.

SLAS094E - MARCH 1995 - REVISED OCTOBER 2000

# sequence of operation

**TLC0834 MUX-ADDRESS CONTROL LOGIC TABLE**

|         | 0000 :07( 7(2) | J. 1200 00.11.110 |     | •   |     |     |  |  |

|---------|----------------|-------------------|-----|-----|-----|-----|--|--|

|         | MUX ADDRE      | CHANNEL NUMBER    |     |     |     |     |  |  |

| SGL/DIF | ODD/EVEN       | SELECT BIT 1      | CH0 | CH1 | CH2 | CH3 |  |  |

| L       | L              | L                 | +   | _   |     |     |  |  |

| L       | L              | Н                 |     |     | +   | _   |  |  |

| L       | Н              | L                 | _   | +   |     |     |  |  |

| L       | Н              | Н                 |     |     | -   | +   |  |  |

| Н       | L              | L                 | +   |     |     |     |  |  |

| H       | L              | Н                 |     |     | +   |     |  |  |

| H       | Н              | L                 |     | +   |     |     |  |  |

| Н       | l н            | I н               |     |     |     | +   |  |  |

H = high level, L = low level, - or + = terminal polarity for the selected input channel

# sequence of operation

SLAS094E - MARCH 1995 - REVISED OCTOBER 2000

#### TLC0838 MUX-ADDRESS CONTROL LOGIC TABLE

|         | MUX ADDRESS |     |     |     | SE  | LECTE | D CHA | NNEL | NUMB | ER  |     |     |

|---------|-------------|-----|-----|-----|-----|-------|-------|------|------|-----|-----|-----|

| SGL/DIF | ODD/EVEN    | SEL | ECT |     | 0   |       | 1     |      | 2    |     | 3   | сом |

| 3GL/DIF | ODD/EVEN    | 1   | 0   | CH0 | CH1 | CH2   | CH3   | CH4  | CH5  | CH6 | CH7 |     |

| L       | L           | L   | L   | +   | -   |       |       |      |      |     |     |     |

| L       | L           | L   | Н   |     |     | +     | _     |      |      |     |     |     |

| L       | L           | Н   | L   |     |     |       |       | +    | _    |     |     |     |

| L       | L           | Н   | Н   |     |     |       |       |      |      | +   | _   |     |

| L       | Н           | L   | L   | _   | +   |       |       |      |      |     |     |     |

| L       | Н           | L   | Н   |     |     | -     | +     |      |      |     |     |     |

| L       | Н           | Н   | L   |     |     |       |       | -    | +    |     |     |     |

| L       | Н           | Н   | Н   |     |     |       |       |      |      | -   | +   |     |

| Н       | L           | L   | L   | +   |     |       |       |      |      |     |     | -   |

| Н       | L           | L   | Н   |     |     | +     |       |      |      |     |     | -   |

| Н       | L           | Н   | L   |     |     |       |       | +    |      |     |     | -   |

| Н       | L           | Н   | Н   |     |     |       |       |      |      | +   |     | -   |

| Н       | Н           | L   | L   |     | +   |       |       |      |      |     |     | _   |

| Н       | Н           | L   | Н   |     |     |       | +     |      |      |     |     | -   |

| Н       | Н           | Н   | L   |     |     |       |       |      | +    |     |     | -   |

| Н       | Н           | Н   | Н   |     |     |       |       |      |      |     | +   | _   |

H = high level, L = low level, - or + = polarity of external input

# absolute maximum ratings over recommended operating free-air temperature range (unless otherwise noted) $\!\!\!\!\!^{\dagger}$

| Supply voltage, V <sub>CC</sub> (see Note 1)                            | 6.5 V                                     |

|-------------------------------------------------------------------------|-------------------------------------------|

| Input voltage range: Logic                                              |                                           |

| Analog                                                                  | $\dots$ -0.3 V to V <sub>CC</sub> + 0.3 V |

| Input current, I <sub>I</sub>                                           | ±5 mA                                     |

| Total input current                                                     | ±20 mA                                    |

| Operating free-air temperature range, T <sub>A</sub> : C suffix         | 0°C to 70°C                               |

| I suffix                                                                | 40°C to 85°C                              |

| Storage temperature range, T <sub>stq</sub>                             | –65°C to 150°C                            |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds: N package | e 260°C                                   |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values, except differential voltages, are with respect to the network ground terminal.

SLAS094E - MARCH 1995 - REVISED OCTOBER 2000

# recommended operating conditions

|                                                |                                                   | MIN | NOM | MAX | UNIT |

|------------------------------------------------|---------------------------------------------------|-----|-----|-----|------|

| Supply voltage, V <sub>CC</sub>                |                                                   | 4.5 | 5   | 5.5 | V    |

| High-level input voltage, VIH                  |                                                   | 2   |     |     | V    |

| Low-level input voltage, V <sub>IL</sub>       |                                                   |     |     | 0.8 | V    |

| Clock frequency, f(clock)                      |                                                   | 10  |     | 600 | kHz  |

| Clock duty cycle (see Note 2)                  | 40%                                               |     | 60% |     |      |

| Pulse duration, CS high, t <sub>W</sub>        |                                                   | 220 |     |     | ns   |

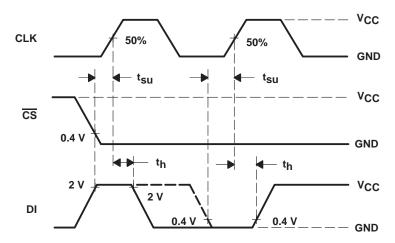

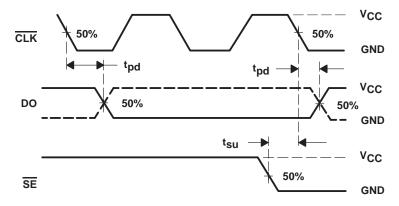

| Setup time, CS low, SE low, or data valid be   | efore CLK↑, t <sub>SU</sub> (see Figures 1 and 2) | 350 |     |     | ns   |

| Hold time, data valid after CLK↑, th (see Fig  | see Figure 1) 90                                  |     |     |     | ns   |

| Operating free air temperature T.              | C suffix                                          | 0   |     | 70  | °C   |

| Operating free-air temperature, T <sub>A</sub> | I suffix                                          | -40 |     | 85  | -0   |

NOTE 2: The clock-duty-cycle range ensures proper operation at all clock frequencies. When a clock frequency is used outside the recommended duty-cycle range, the minimum pulse duration (high or low) is 1 μs.

# electrical characteristics over recommended range of operating free-air temperature, $V_{CC}$ = 5 V, $f_{(clock)}$ = 250 kHz (unless otherwise noted)

# digital section

|                 | 24244555                           |                            |                            | (    | SUFFIX |      | ı    | SUFFIX |      |    |

|-----------------|------------------------------------|----------------------------|----------------------------|------|--------|------|------|--------|------|----|

|                 | PARAMETER                          | TEST COM                   | MIN                        | TYP‡ | MAX    | MIN  | TYP‡ | MAX    | UNIT |    |

| V               | High-level output voltage          | $V_{CC} = 4.75 V$ ,        | I <sub>OH</sub> = -360 μA  | 2.8  |        |      | 2.4  |        |      | V  |

| VOH             | High-level output voltage          | $V_{CC} = 4.75 V$ ,        | $I_{OH} = -10 \mu\text{A}$ | 4.6  |        |      | 4.5  |        |      | V  |

| VOL             | Low-level output voltage           | $V_{CC} = 5.25 \text{ V},$ | I <sub>OL</sub> = 1.6 mA   |      |        | 0.34 |      |        | 0.4  | V  |

| lіН             | High-level input current           | V <sub>IH</sub> = 5 V,     | V <sub>IH</sub> = 5 V      |      | 0.005  | 1    |      | 0.005  | 1    | μΑ |

| IJĽ             | Low-level input current            | V <sub>IL</sub> = 0,       | V <sub>IL</sub> = 0        |      | -0.005 | -1   |      | -0.005 | -1   | μΑ |

| loh             | High-level output (source) current | $V_{OH} = 0$ ,             | T <sub>A</sub> = 25°C      | -6.5 | -24    |      | -6.5 | -24    |      | mA |

| l <sub>OL</sub> | Low-level output (sink) current    | $V_{OL} = V_{CC}$          | T <sub>A</sub> = 25°C      | 8    | 26     |      | 8    | 26     |      | mA |

| lo=             | High-impedance-state output        | V <sub>O</sub> = 5 V,      | T <sub>A</sub> = 25°C      |      | 0.01   | 3    |      | 0.01   | 3    |    |

| loz             | current (DO or SARS)               | $V_{O} = 0,$               | T <sub>A</sub> = 25°C      |      | -0.01  | -3   |      | -0.01  | -3   | μΑ |

| Ci              | Input capacitance                  |                            |                            |      |        |      |      | 5      |      | pF |

| Со              | Output capacitance                 |                            |                            |      |        |      |      | 5      |      | pF |

<sup>†</sup> All parameters are measured under open-loop conditions with zero common-mode input voltage (unless otherwise specified).

<sup>‡</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

SLAS094E - MARCH 1995 - REVISED OCTOBER 2000

# electrical characteristics over recommended range of operating free-air temperature, V<sub>CC</sub> = 5 V, f<sub>(clock)</sub> = 250 kHz (unless otherwise noted) (continued)

# analog and converter section

|                       | PARAMETER                          |             | TEST CONDITIONS†     | MIN                                  | TYP‡ | MAX | UNIT |

|-----------------------|------------------------------------|-------------|----------------------|--------------------------------------|------|-----|------|

| VIC                   | Common-mode input voltage          |             | See Note 3           | -0.05<br>to<br>V <sub>CC</sub> +0.05 |      |     | V    |

|                       |                                    | On channel  | V <sub>I</sub> = 5 V |                                      |      | 1   |      |

|                       | Ctandhu innut augrant (aca Nata 4) | Off channel | V <sub>I</sub> = 0   |                                      |      | -1  |      |

| <sup>I</sup> I(stdby) | Standby input current (see Note 4) | On channel  | V <sub>I</sub> = 0   |                                      |      | -1  | μΑ   |

|                       |                                    | Off channel | V <sub>I</sub> = 5 V |                                      |      | 1   |      |

| ri(REF)               | Input resistance to REF            |             |                      | 1.3                                  | 2.4  | 5.9 | kΩ   |

<sup>†</sup> All parameters are measured under open-loop conditions with zero common-mode input voltage.

NOTES: 3. When channel IN- is more positive than channel IN+, the digital output code is 0000 0000. Connected to each analog input are two on-chip diodes that conduct forward current for analog input voltages one diode drop above VCC. Care must be taken during testing at low V<sub>CC</sub> levels (4.5 V) because high-level analog input voltage (5 V) can, especially at high temperatures, cause the input diode to conduct and cause errors for analog inputs that are near full scale. As long as the analog voltage does not exceed the supply voltage by more than 50 mV, the output code is correct. To achieve an absolute 0- to 5-V input range requires a minimum V<sub>CC</sub> of 4.950 V for all variations of temperature and load.

4. Standby input currents go in or out of the on or off channels when the A/D converter is not performing conversion and the clock is in a high or low steady-state condition.

#### total device

|     | PARAMETER      | MIN | TYP <sup>‡</sup> | MAX  | UNIT |

|-----|----------------|-----|------------------|------|------|

| Icc | Supply current |     | 0.6              | 1.25 | mA   |

<sup>‡</sup> All typical values are at  $V_{CC} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

## operating characteristics, $V_{CC} = 5 \text{ V}$ , $f_{(clock)} = 250 \text{ kHz}$ , $t_r = t_f = 20 \text{ ns}$ , $T_A = 25^{\circ}\text{C}$ (unless otherwise noted)

|                  | PARAMETER                                    |                          | TEST C                      | CONDITIONS§            | MIN   | TYP  | MAX | UNIT             |

|------------------|----------------------------------------------|--------------------------|-----------------------------|------------------------|-------|------|-----|------------------|

|                  | Supply-voltage variation error               | V <sub>CC</sub> = 4.75 \ | / to 5.25 V                 |                        | ±1/16 | ±1/4 | LSB |                  |

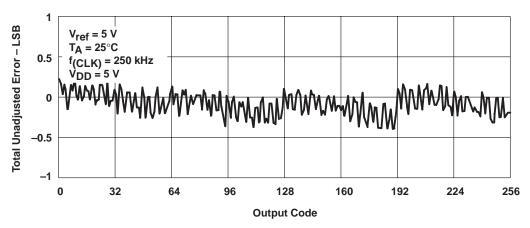

|                  | Total unadjusted error (see Note 5)          | $V_{ref} = 5 V$ ,        | $T_A = MIN \text{ to } MAX$ |                        |       | ±1   | LSB |                  |

|                  | Common-mode error                            | Differential m           | ode                         |                        | ±1/16 | ±1/4 | LSB |                  |

|                  | Propagation delay time, output               | C 100 pE                 |                             |                        | 1500  | no   |     |                  |

| <sup>t</sup> pd  | data after CLK↓ (see Note 6 and Figure 2)    | LSB-first data           | C <sub>L</sub> = 100 pF     |                        |       | 600  | ns  |                  |

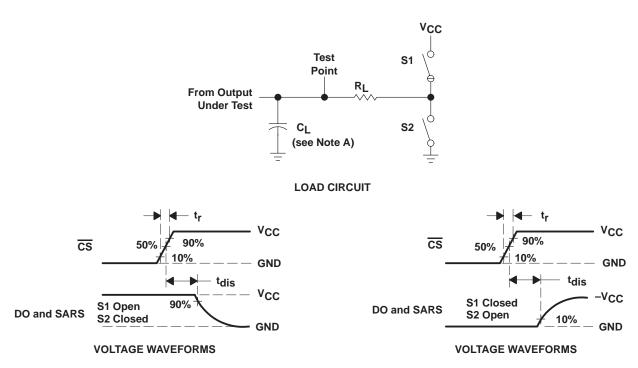

| <b>.</b>         | Output that he that he BO as OABO after OOA  | ( Einen 0)               | $C_L = 10 pF$ ,             | R <sub>L</sub> = 10 kΩ |       |      | 250 | no               |

| <sup>t</sup> dis | Output disable time, DO or SARS after CS↑ (  | (see Figure 3)           | $C_L = 100 pF$ ,            | $R_L = 2 k\Omega$      |       |      | 500 | ns               |

| t <sub>C</sub>   | Conversion time (multiplexer-addressing time | e not included)          |                             |                        |       |      | 8   | clock<br>periods |

<sup>§</sup> All parameters are measured under open-loop conditions with zero common-mode input voltage. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

NOTES: 5. Total unadjusted error includes offset, full-scale, linearity, and multiplexer errors.

6. The MSB-first data is output directly from the comparator and, therefore, requires additional delay to allow for comparator response

<sup>‡</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

# PARAMETER MEASUREMENT INFORMATION

Figure 1. Data-Input Timing

Figure 2. Data-Output Timing

#### PARAMETER MEASUREMENT INFORMATION

NOTE A: C<sub>I</sub> includes probe and jig capacitance.

Figure 3. Output Disable Time Test Circuit and Voltage Waveforms

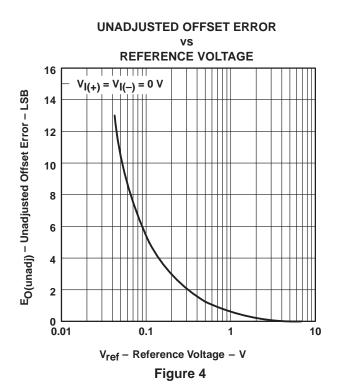

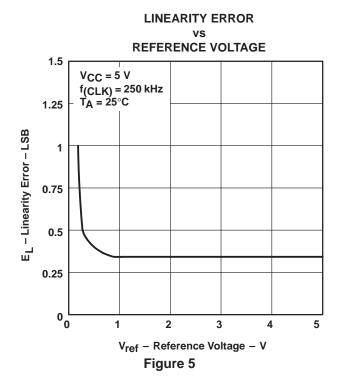

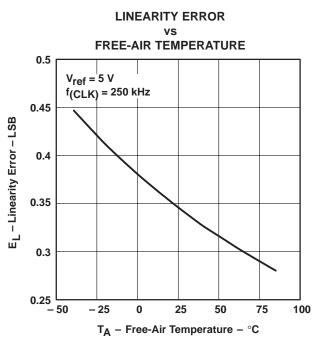

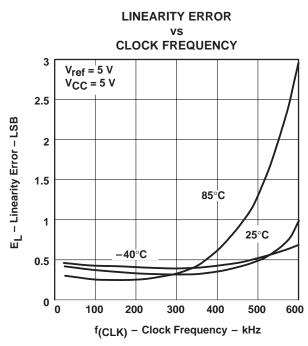

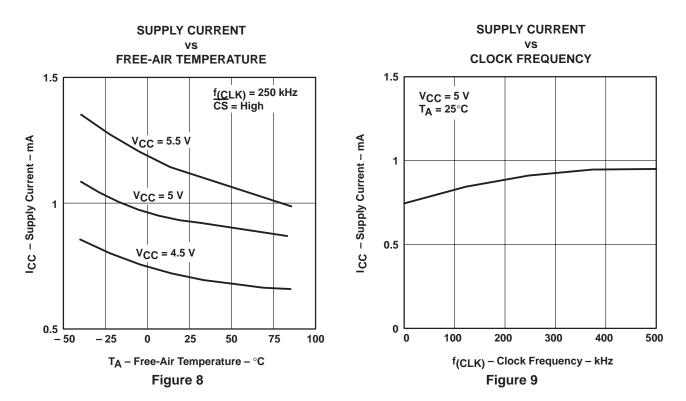

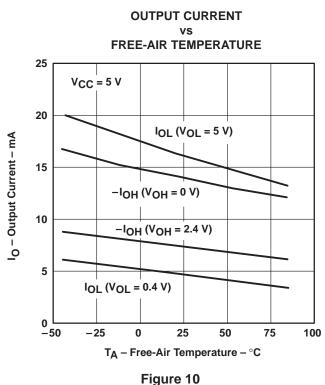

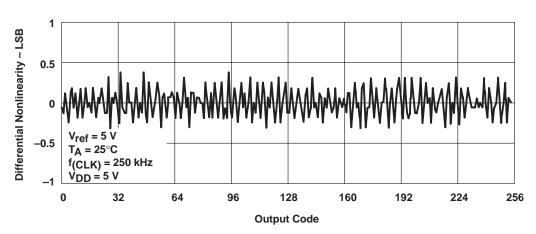

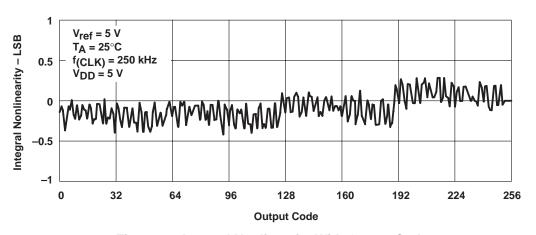

#### TYPICAL CHARACTERISTICS

Figure 6

Figure 7

#### TYPICAL CHARACTERISTICS

#### **TYPICAL CHARACTERISTICS**

Figure 11. Differential Nonlinearity With Output Code

Figure 12. Integral Nonlinearity With Output Code

Figure 13. Total Unadjusted Error With Output Code

www.ti.com

14-Oct-2022

# **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan            | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|---------------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| TLC0834CD        | ACTIVE     | SOIC         | D                  | 14   | 50             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | TLC0834C                | Samples |

| TLC0834CDR       | ACTIVE     | SOIC         | D                  | 14   | 2500           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0834C                | Samples |

| TLC0834CN        | ACTIVE     | PDIP         | N                  | 14   | 25             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type |              | TLC0834CN               | Samples |

| TLC0834ID        | ACTIVE     | SOIC         | D                  | 14   | 50             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0834I                | Samples |

| TLC0834IDR       | ACTIVE     | SOIC         | D                  | 14   | 2500           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0834I                | Samples |

| TLC0834IN        | ACTIVE     | PDIP         | N                  | 14   | 25             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type |              | TLC0834IN               | Samples |

| TLC0838CDW       | ACTIVE     | SOIC         | DW                 | 20   | 25             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0838C                | Samples |

| TLC0838CDWG4     | ACTIVE     | SOIC         | DW                 | 20   | 25             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0838C                | Samples |

| TLC0838CDWR      | ACTIVE     | SOIC         | DW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0838C                | Samples |

| TLC0838CDWRG4    | ACTIVE     | SOIC         | DW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0838C                | Samples |

| TLC0838CN        | ACTIVE     | PDIP         | N                  | 20   | 20             | RoHS & Green        | NIPDAU                        | N / A for Pkg Type |              | TLC0838CN               | Samples |

| TLC0838CPW       | ACTIVE     | TSSOP        | PW                 | 20   | 70             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | TLC0838C                | Samples |

| TLC0838CPWR      | ACTIVE     | TSSOP        | PW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | 0 to 70      | TLC0838C                | Samples |

| TLC0838IDW       | ACTIVE     | SOIC         | DW                 | 20   | 25             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0838I                | Samples |

| TLC0838IDWR      | ACTIVE     | SOIC         | DW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM |              | TLC0838I                | Samples |

| TLC0838IN        | ACTIVE     | PDIP         | N                  | 20   | 20             | RoHS &<br>Non-Green | NIPDAU                        | N / A for Pkg Type | -40 to 85    | TLC0838IN               | Samples |

| TLC0838IPW       | ACTIVE     | TSSOP        | PW                 | 20   | 70             | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | TLC0838I                | Samples |

| TLC0838IPWR      | ACTIVE     | TSSOP        | PW                 | 20   | 2000           | RoHS & Green        | NIPDAU                        | Level-1-260C-UNLIM | -40 to 85    | TLC0838I                | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

# PACKAGE OPTION ADDENDUM

www.ti.com 14-Oct-2022

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

**PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

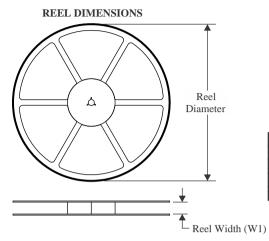

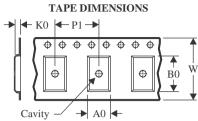

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

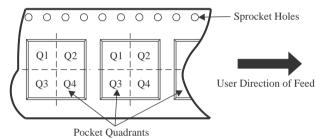

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLC0834CDR  | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| TLC0834IDR  | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

| TLC0838CDWR | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.3       | 2.7        | 12.0       | 24.0      | Q1               |

| TLC0838CPWR | TSSOP           | PW                 | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

| TLC0838IDWR | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8       | 13.3       | 2.7        | 12.0       | 24.0      | Q1               |

| TLC0838IPWR | TSSOP           | PW                 | 20 | 2000 | 330.0                    | 16.4                     | 6.95       | 7.1        | 1.6        | 8.0        | 16.0      | Q1               |

www.ti.com 9-Aug-2022

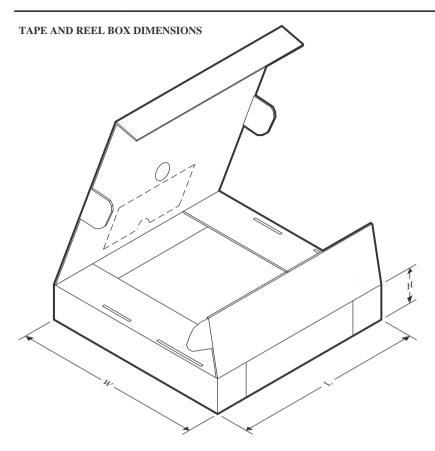

# \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins SPQ Le |      | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|-------------|------|-------------|------------|-------------|

| TLC0834CDR  | SOIC         | D               | 14          | 2500 | 350.0       | 350.0      | 43.0        |

| TLC0834IDR  | SOIC         | D               | 14          | 2500 | 350.0       | 350.0      | 43.0        |

| TLC0838CDWR | SOIC         | DW              | 20          | 2000 | 367.0       | 367.0      | 45.0        |

| TLC0838CPWR | TSSOP        | PW              | 20          | 2000 | 350.0       | 350.0      | 43.0        |

| TLC0838IDWR | SOIC         | DW              | 20          | 2000 | 367.0       | 367.0      | 45.0        |

| TLC0838IPWR | TSSOP        | PW              | 20          | 2000 | 350.0       | 350.0      | 43.0        |

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 9-Aug-2022

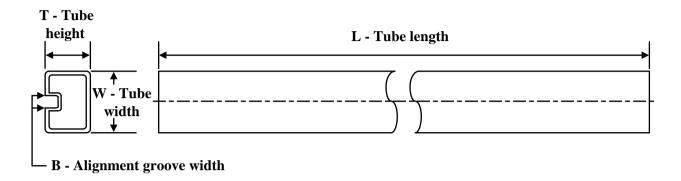

# **TUBE**

\*All dimensions are nominal

| Device       | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|--------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TLC0834CD    | D            | SOIC         | 14   | 50  | 505.46 | 6.76   | 3810   | 4      |

| TLC0834CN    | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230  | 4.32   |

| TLC0834ID    | D            | SOIC         | 14   | 50  | 505.46 | 6.76   | 3810   | 4      |

| TLC0834IN    | N            | PDIP         | 14   | 25  | 506    | 13.97  | 11230  | 4.32   |

| TLC0838CDW   | DW           | SOIC         | 20   | 25  | 507    | 12.83  | 5080   | 6.6    |

| TLC0838CDWG4 | DW           | SOIC         | 20   | 25  | 507    | 12.83  | 5080   | 6.6    |

| TLC0838CN    | N            | PDIP         | 20   | 20  | 506    | 13.97  | 11230  | 4.32   |

| TLC0838CPW   | PW           | TSSOP        | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

| TLC0838IDW   | DW           | SOIC         | 20   | 25  | 506.98 | 12.7   | 4826   | 6.6    |

| TLC0838IDW   | DW           | SOIC         | 20   | 25  | 507    | 12.83  | 5080   | 6.6    |

| TLC0838IN    | N            | PDIP         | 20   | 20  | 506    | 13.97  | 11230  | 4.32   |

| TLC0838IPW   | PW           | TSSOP        | 20   | 70  | 530    | 10.2   | 3600   | 3.5    |

# IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated