## The Infinite Bandwidth Company™

### **MIC2558**

#### PCMCIA Dual Card Socket V<sub>PP</sub> Switching Matrix

#### **Final Information**

#### **General Description**

The MIC2558 Dual  $V_{PP}$  Matrix switches the four voltages required by PCMCIA (Personal Computer Memory Card International Association) card  $V_{PP1}$  and  $V_{PP2}$  Pins. The MIC2558 provides selectable 0V, 3.3V, 5.0V, or 12.0V (±5%) from the system power supply to  $V_{PP1}$  and  $V_{PP2}$ . Output voltage is selected by two digital inputs per  $V_{PP}$  pin. Output current ranges up to 120mA. Four output states,  $V_{PP}$ ,  $V_{CC}$ , high impedance, and active logic low are available, and  $V_{PP1}$  is independent of  $V_{PP2}$ . An auxiliary control input determines whether the high impedance (open) state or low logic state is asserted.

In standby mode or full operation, the device draws very little quiescent current, typically less than  $1\mu$ A.

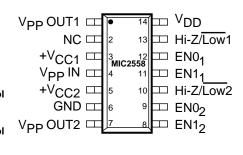

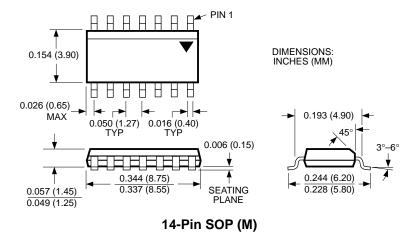

The MIC2558 is available in a 14-pin SOIC package.

### **Applications**

- PCMCIA V<sub>PP</sub> Pin Voltage Switch

- · Power Supply Management

#### **Features**

- Complete PCMCIA V<sub>PP</sub> Switch Matrix in a Single IC

- Dual Matrix allows independent V<sub>PP1</sub> and V<sub>PP2</sub>

- Digital Selection of 0V, V<sub>CC</sub>, V<sub>PP</sub>, or High Impedance Output

- No V<sub>PPOLIT</sub> Overshoot or Switching Transients

- · Break-Before-Make Switching

- Ultra Low Power Consumption

- 120mA V<sub>PP</sub> (12V) Output Current

- Optional Active Source Clamp for Zero Volt Condition

- 3.3V or 5V Supply Operation

- 14-Pin SOIC Package

### **Ordering Information**

| Part Number   | Temperature Range | Package            |

|---------------|-------------------|--------------------|

| MIC2558BM     | –40°C to +85°C    | 14-pin SOIC        |

| MIC2558BM T&R | –40°C to +85°C    | 14-SO Tape & Reel* |

<sup>\* 2,500</sup> Parts per reel.

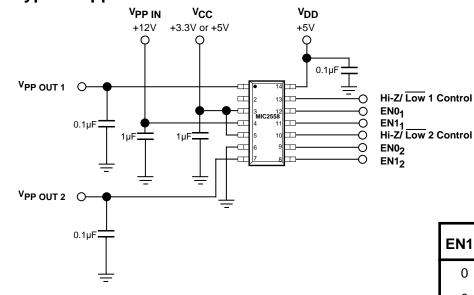

# **Typical Application**

## **Pin Configuration**

| EN1 | EN0 | Hi-Z/Low | V <sub>PP OUT</sub>            |

|-----|-----|----------|--------------------------------|

| 0   | 0   | 0        | 0V, (Sink current)             |

| 0   | 0   | 1        | Hi-Z (No Connect)              |

| 0   | 1   | х        | V <sub>CC</sub> (3.3V or 5.0V) |

| 1   | 0   | х        | V <sub>PP</sub>                |

| 1   | 1   | Х        | Hi-Z (No Connect)              |

# Absolute Maximum Ratings (Notes 1 and 2)

| Power Dissipation, $T_{AMBIENT} \le 25^{\circ}C$ SOIC | 800 mW          |

|-------------------------------------------------------|-----------------|

| Derating Factors (To Ambient)                         |                 |

| SOIC                                                  | 4 mW/°C         |

| Storage Temperature                                   | -65°C to +150°C |

| Operating Temperature (Die)                           | 125°C           |

| Operating Temperature (Ambient)                       | -40°C to +85°C  |

| Lead Temperature (5 sec)                              | 260°C           |

| Supply Voltage, V <sub>PP IN</sub>    | 15V                     |

|---------------------------------------|-------------------------|

| V <sub>CC</sub>                       | 7.5V                    |

| $V_{DD}$                              | 7.5V                    |

| Logic Input Voltages                  | -0.3V toV <sub>DD</sub> |

| Output Current (each Output)          |                         |

| V <sub>PP OUT</sub> = 12V             | 600mA                   |

| V <sub>PP</sub> OUT = V <sub>CC</sub> | 250mA                   |

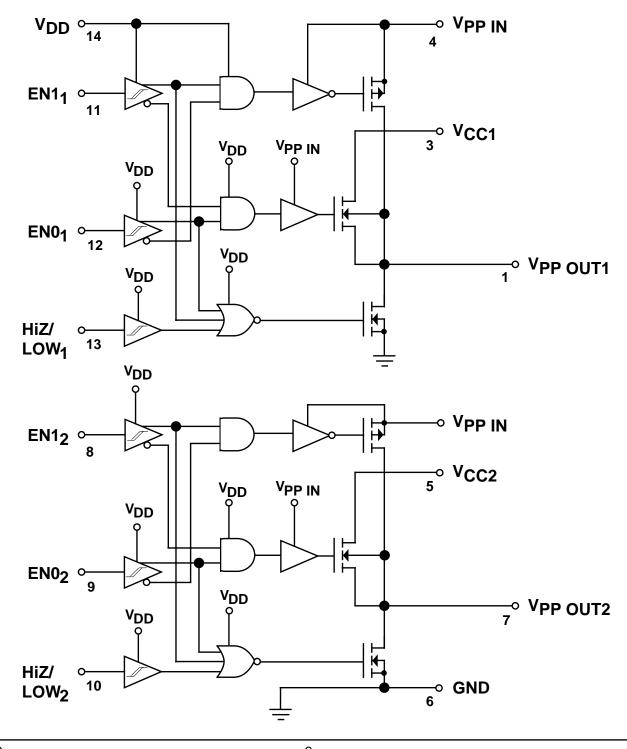

# **Logic Block Diagram**

$\textbf{Electrical Characteristics:} \hspace{0.2cm} \text{(Over operating temperature range with V}_{DD} = V_{CC} = 5V, V_{PP\ IN} = 12\ V \hspace{0.2cm} \text{unless otherwise specified.)}$

| Symbol                  | Parameter                                                   | Conditions                                                               | Min        | Тур | Max             | Units |

|-------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|------------|-----|-----------------|-------|

| INPUT                   |                                                             |                                                                          |            | •   |                 |       |

| V <sub>IH</sub>         | Logic 1 Input Voltage                                       |                                                                          | 2.2        |     |                 | V     |

| V <sub>IL</sub>         | Logic 0 Input Voltage                                       |                                                                          |            |     | 0.8             | V     |

| V <sub>IN</sub> (Max)   | Input Voltage Range                                         |                                                                          | <b>-</b> 5 |     | V <sub>DD</sub> | V     |

| I <sub>IN</sub>         | Input Current                                               | 0 V < V <sub>IN</sub> < V <sub>DD</sub>                                  |            |     | ±1              | μΑ    |

| EACH OUT                | PUT                                                         |                                                                          |            |     |                 |       |

| $V_{OL}$                | Clamp Low Output Voltage                                    | EN0 = EN1 = HiZ = 0, I <sub>SINK</sub> = 1.6mA                           |            |     | 0.4             | V     |

| I <sub>OUT</sub> , Hi-Z | High Impedance Output<br>Leakage Current                    | EN0 = EN1 = 0, HiZ = 1.<br>0 ≤ V <sub>PP OUT</sub> ≤ 12V                 |            | 1   | 10              | μΑ    |

| R <sub>OC</sub>         | Clamp Low Output Resistance                                 | Resistance to Ground. I <sub>SINK</sub> = 2mA<br>EN0 = EN1 = 0, HiZ = 0. |            | 130 | 250             | Ω     |

| R <sub>O</sub>          | Switch Resistance, VPP OUT = VCC                            | I <sub>PP OUT</sub> = −10 mA (Sourcing)                                  |            | 2.5 | 5               | Ω     |

| R <sub>O</sub>          | Switch Resistance, V <sub>PP OUT</sub> = V <sub>PP IN</sub> | I <sub>PP OUT</sub> = −100 mA (Sourcing)                                 |            | 0.5 | 1               | Ω     |

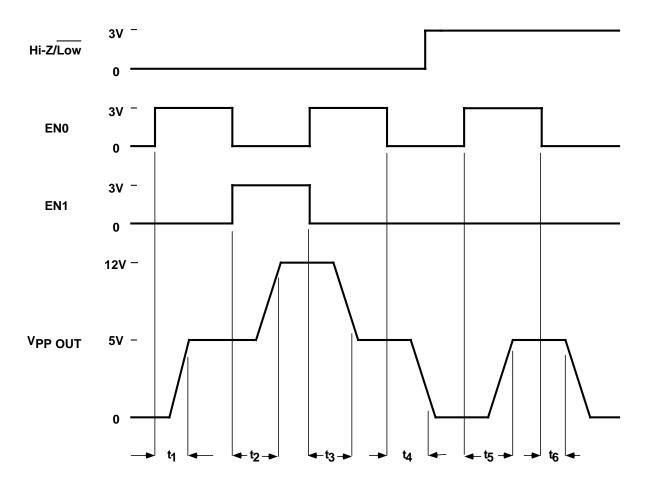

| SWITCHING               | G TIME (See Figure 1)                                       |                                                                          |            |     |                 |       |

| t <sub>1</sub>          | Delay + Rise Time                                           | $V_{PP\ OUT} = 0V \text{ to } 5V \text{ (Notes } 3, 5)$                  |            | 15  | 50              | μs    |

| t <sub>2</sub>          | Delay + Rise Time                                           | V <sub>PP OUT</sub> = 5V to 12V (Notes 3, 5)                             |            | 12  | 50              | μs    |

| t <sub>3</sub>          | Delay + Fall Time                                           | V <sub>PP OUT</sub> = 12V to 5V (Notes 3, 5)                             |            | 25  | 75              | μs    |

| t <sub>4</sub>          | Delay + Fall Time                                           | V <sub>PP OUT</sub> = 5V to 0V (Notes 3, 5)                              |            | 45  | 100             | μs    |

| t <sub>5</sub>          | Output Turn-On Delay                                        | V <sub>PP OUT</sub> = Hi-Z to 5V (Notes 4, 5)                            |            | 10  | 50              | μs    |

| t <sub>6</sub>          | Output Turn-Off Delay                                       | V <sub>PP OUT</sub> = 5V to Hi-Z (Notes 4, 5)                            |            | 75  | 200             | ns    |

| POWER SU                | JPPLY                                                       |                                                                          |            |     |                 |       |

| I <sub>DD</sub>         | V <sub>DD</sub> Supply Current                              |                                                                          |            | _   | 1               | μΑ    |

| I <sub>CC</sub>         | V <sub>CC</sub> Supply Current                              | I <sub>PP OUT</sub> = 0                                                  |            | -   | 1               | μА    |

| I <sub>PP</sub>         | I <sub>PP</sub> Supply Current                              | $V_{PP OUT1} = V_{PPOUT2} = 0 \text{ V or } V_{PP}$ . $I_{PPOUT} = 0$ .  |            | -   | 10              | μΑ    |

|                         |                                                             | V <sub>PP OUT1</sub> = V <sub>PPOUT2</sub> = V <sub>CC</sub>             |            | 20  | 80              | μА    |

### **Electrical Characteristics (continued)**

| Symbol                  | Parameter               | Conditions | Min | Тур | Max  | Units |  |

|-------------------------|-------------------------|------------|-----|-----|------|-------|--|

| POWER SUPPLY, continued |                         |            |     |     |      |       |  |

| V <sub>CC</sub>         | Operating Input Voltage |            |     |     | 6    | V     |  |

| V <sub>DD</sub>         | Operating Input Voltage |            | 2.8 |     | 6    | V     |  |

| V <sub>PP IN</sub>      | Operating Input Voltage |            | 8.0 |     | 14.5 | V     |  |

NOTE 1: Functional operation above the absolute maximum stress ratings is not implied.

NOTE 2: Static-sensitive device. Store only in conductive containers. Handling personnel and equipment should be grounded to prevent damage from static discharge.

NOTE 3:

With R<sub>L</sub> =  $2.9 k\Omega$  and C<sub>OUT</sub> =  $0.1 \mu F$  on V<sub>PP OUT</sub>. R<sub>L</sub> =  $2.9 k\Omega$ . R<sub>L</sub> is connected to V<sub>CC</sub> during t<sub>5</sub>, and is connected to ground during t<sub>6</sub>. Rise and fall times are measured to 90% of the difference of initial and final values. NOTE 4: NOTE 5:

Figure 1. Timing Diagram.

### **Applications Information**

PCMCIA  $V_{PP1}$  and  $V_{PP2}$  control is easily accomplished using the MIC2558 voltage selector/switch IC. Two control bits per  $V_{PP\ OUT}$  pin determine output voltage and standby/operate mode condition. Output voltages of 0V (defined as less than 0.4V),  $V_{CC}$  (3.3V or 5V),  $V_{PP}$ , or a high impedance state, are available. When either the high impedance or low voltage conditions are selected, the device switches into "sleep" mode and draws only nanoamperes of leakage current.

The MIC2558 is a dual low-resistance power MOSFET switching matrix that operates from the computer system main power supply. Device power is obtained from  $V_{DD}$ , which may be either 3.3V or 5V, and FET drive is obtained from  $V_{PP\ IN}$  (usually +12V). Internal break-before-make switches determine the output voltage and device mode.  $V_{PP1}$  and  $V_{PP2}$  are completely indepenent from each other.

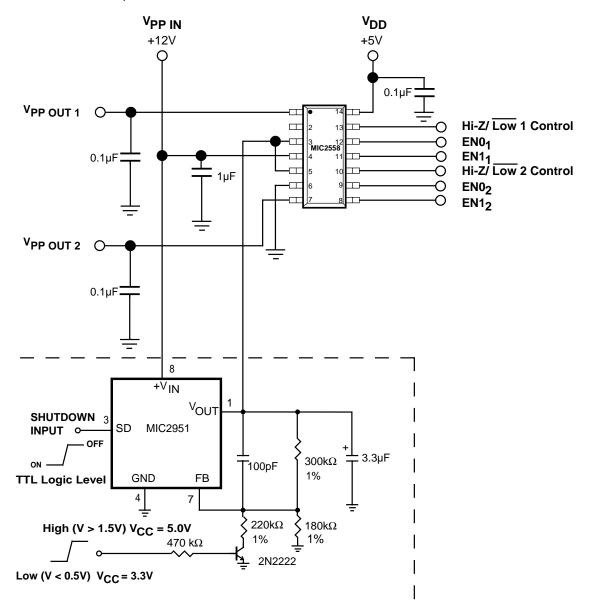

#### **Supply Bypassing**

For best results, bypass  $V_{CC}$  and  $V_{PP\ IN}$  inputs with 1 $\mu$ F capacitors. Both  $V_{PP\ OUT}$  pins should have a 0.01 $\mu$ F to 0.1 $\mu$ F capacitor for noise reduction and electrostatic discharge (ESD) damage prevention. Larger values of output capacitor will create large current spikes during transitions, requiring larger bypass capacitors on the  $V_{CC}$  and  $V_{PP\ IN}$  pins.

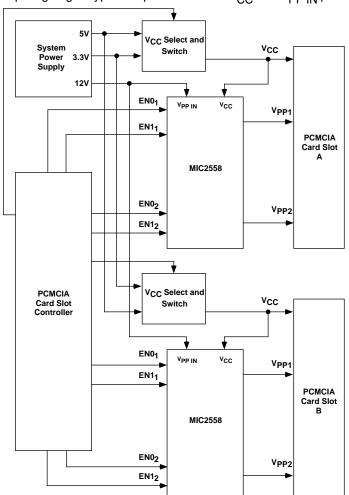

Figure 2. MIC2558 Typical two slot PCMCIA application with dual  $V_{\rm cc}$  (5.0V or 3.3V).

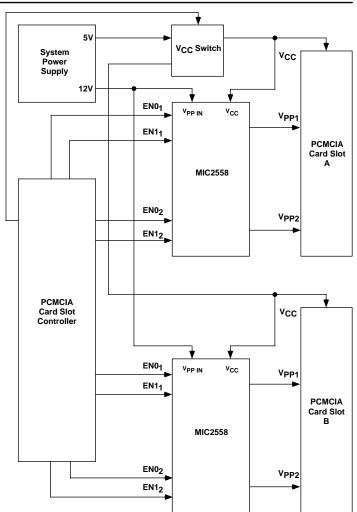

Figure 3. MIC2558 Typical two slot PCMCIA application with single 5.0V  $V_{\rm cc}$ .

#### **PCMCIA Implementation**

The Personal Computer Memory Card International Association (PCMCIA) specification requires two V<sub>PP</sub> supply pins per PCMCIA slot. V<sub>PP</sub> is primarily used for programming Flash (EEPROM) memory cards. The two V<sub>PP</sub> supply pins may be programmed to different voltages. Fully implementing PCMCIA specifications requires a MIC2558 and a controller. Figure 2 shows this full configuration, supporting both 5.0V and 3.3V V<sub>CC</sub> operation. Figure 3 is a simplified design with fixed V<sub>CC</sub> = 5V.

When a memory card is initially inserted, it should receive V $_{CC}$ — usually 5.0V  $\pm 5\%$ . The card sends a handshaking data stream to the controller, which then determines whether or not this card requires V $_{PP}$  and if the card is designed for 5.0V or 3.3V V $_{CC}$ . If the card uses 3.3V V $_{CC}$ , the controller commands this change, which is reflected on the V $_{CC}$  pins of both the PCMCIA slot and the MIC2558.

During Flash memory programming, the PCMCIA controller outputs a (1,0) to one or both halves of the MIC2558, which connects  $V_{PP\ IN}$  to  $V_{PP\ OUT1}$  and/or  $V_{PP\ OUT2}$ . The low ON resistance of the MIC2558 switch requires only a small bypass capacitor on the  $V_{PP\ OUT}$  pins, with the main filtering

action performed by a large filter capacitor on  $V_{PP\ IN}$ . The  $V_{PP\ OUT}$  transition from  $V_{CC}$  to 12.0V typically takes 25 $\mu$ S. After programming is completed, the controller outputs a (0,1) to the MIC2558, which then reduces  $V_{PP\ OUT}$  to the  $V_{CC}$  level. Break-before-make switching action reduces switching transients and lowers maximum current spikes through the switch from the output capacitor.

If no card is inserted, or the system is in sleep mode, the controller outputs either a (0,0) or a (1,1) to the MIC2558. Either input places the switch into shutdown mode, where current consumption drops even further.

The HiZ/Low input controls the optional logic low output clamp. With HiZ/Low in the high state and EN0 = EN1 = 0,  $V_{PP\ OUT}$  enters a high impedance (open) state. With HiZ/Low in the low state and EN0 = EN1 = 0,  $V_{PP\ OUT}$  is clamped to ground, providing a logic low signal. The clamp does not require any DC bias current for operation.

MOSFET drive and bias voltage is derived from  $V_{PP\ IN}$ . Internal device control logic is powered from  $V_{DD}$ , which should be connected to the same supply voltage as the PCMCIA controller (normally either 3.3V or 5V).

#### **Output Current**

MIC2558 output switches are capable of far more current than usually needed in PCMCIA applications. PCMCIA  $V_{PP}$  output current is limited primarily by switch resistance voltage drop (I x R) and the requirement that  $V_{PP\;OUT}$  cannot drop more than 5% below nominal.  $V_{PP\;OUT}$  will survive output short circuits to ground if  $V_{PP\;IN}$  or  $V_{CC}$  are current limited by the regulator that supplies these voltages.

**V<sub>CC</sub>** Switching and Control Block

Figure 3. Full PCMCIA Implementation of  $V_{PP}$  and  $V_{CC}$  switching using MIC2558 and MIC2951 voltage regulator.

# **Package Information**

#### MICREL INC. 1849 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL + 1 (408) 944-0800 FAX + 1 (408) 944-0970 WEB http://www.micrel.com

This information is believed to be accurate and reliable, however no responsibility is assumed by Micrel for its use nor for any infringement of patents or other rights of third parties resulting from its use. No license is granted by implication or otherwise under any patent or patent right of Micrel Inc.

© 1997 Micrel Incorporated