Sample &

Buy

### UCC28704

SLUSCA8A-FEBRUARY 2016-REVISED FEBRUARY 2016

# UCC28704 High-Efficiency Off-Line CV and CC Flyback Controller with Primary-Side Regulation (PSR)

#### **Features** 1

- Efficiency Performance Exceeds DoE Level VI and EU CoC V5 Tier-2 External Power Supply Standards

- Primary-Side Regulation Eliminates Opto-Coupler and Secondary Feedback Components

- Compatible with Synchronous Rectifier

- Enables <30-mW No-Load Input Power

- ±5% Output Voltage (CV) and Current (CC) Regulation

- Enhanced Dynamic Load Response

- Constant Current Output Under-Voltage Protection (CCUV) with Auto-Restart Response

- Cable Compensation (300 mV at 5-V Full Load)

- 85-kHz Maximum Switching Frequency

- DCM Valley-Switching Operation

- Clamped Gate-Drive Output for MOSFET

- NTC Resistor Interface

- Resistor or External HV Depletion-Mode FET Start-Up

- Fault Protections: Input Low Line, Output Over-Voltage, Over-Current, and Short-Circuit

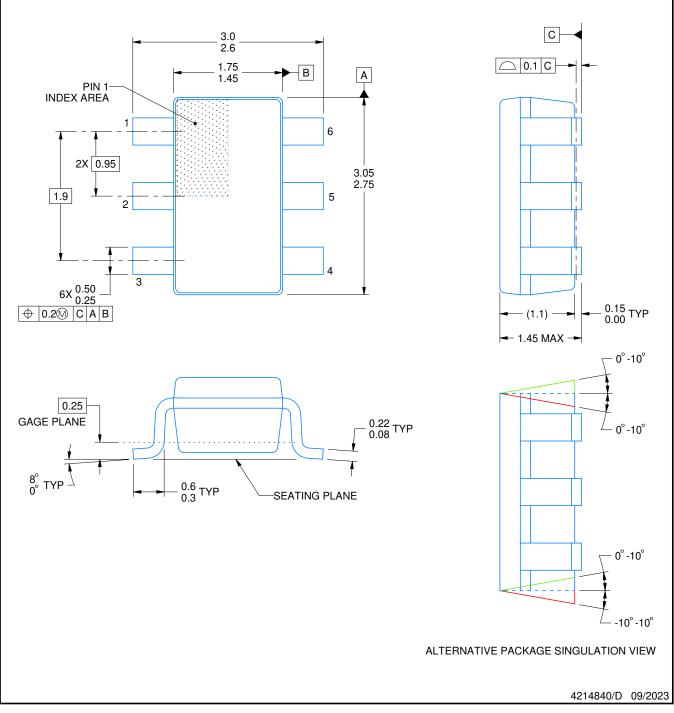

- SOT23-6 Package

#### Applications 2

- Adapters and Chargers for Phones and Tablets

- USB Type-C AC Adapters for Consumer Electronics

- Low Power AC to DC SMPS

- Industrial and Medical SMPS

NTC/SU

GND

# 3 Description

The UCC28704 Off-line flyback controller is a highly integrated, 6-pin primary-side regulated PWM controller for designing high efficiency AC-to-DC power supplies with low standby power consumption to comply with global efficiency standards. The controller has ultra-low current consumption at startup to enable designs with <30-mW no-load input power and save standby mode energy consumption. Intelligent primary-side sensing and control enables 5% output voltage and current control without using an opto coupler or secondary-side feedback circuits.

UCC28704 incorporates an enhanced load transient response technique which helps minimize the output capacitor, reducing the overall system size and cost. The controller also eliminates the need for loop compensation components which simplify the design and debugging process for power supply designers. The converter output voltage and current is regulated to prevent overstress conditions that may damage the load or connectors. Similarly, the CCUV shutdown feature monitors for an output under voltage fault to protect connectors from over heat or burn out from soft shorts, which greatly enhance overall system reliability. Board or component over temperature protection is facilitated with an NTC interface pin.

UCC28704 can be readily used with TI secondaryside synchronous rectifier (SR) controllers at 2-A or higher output current levels for higher conversion efficiency or more compact designs.

### Device Information <sup>(1)</sup>

| PART NUMBER | PACKAGE | BODY SIZE (NOM)   |

|-------------|---------|-------------------|

| UCC28704    | SOT23-6 | 2.90 mm × 1.60 mm |

(1) For all available packages, see the orderable addendum at the end of the datasheet.

### 5-V, 2-A Adapter Efficiency Performance

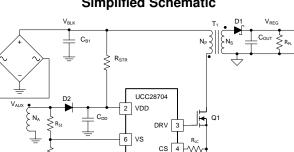

Simplified Schematic

| www.ti.com |

|------------|

|            |

Texas Instruments

## **Table of Contents**

| 1 | Feat          | tures                            | 1    |  |  |  |  |

|---|---------------|----------------------------------|------|--|--|--|--|

| 2 | Арр           | lications                        | 1    |  |  |  |  |

| 3 | Description 1 |                                  |      |  |  |  |  |

| 4 | Rev           | ision History                    | 2    |  |  |  |  |

| 5 | Pin           | Configuration and Functions      | 3    |  |  |  |  |

| 6 | Spe           | cifications                      | 4    |  |  |  |  |

|   | 6.1           | Absolute Maximum Ratings         | 4    |  |  |  |  |

|   | 6.2           | ESD Ratings                      | 4    |  |  |  |  |

|   | 6.3           | Recommended Operating Conditions | 4    |  |  |  |  |

|   | 6.4           | Thermal Information              | 5    |  |  |  |  |

|   | 6.5           | Electrical Characteristics       | 5    |  |  |  |  |

|   | 6.6           | Typical Characteristics          | 7    |  |  |  |  |

| 7 | Deta          | ailed Description                | 9    |  |  |  |  |

|   | 7.1           | Overview                         | 9    |  |  |  |  |

|   | 7.2           | Functional Block Diagram         | 9    |  |  |  |  |

|   | 7.3           | Feature Description              | . 10 |  |  |  |  |

|   | 7.4           | Device Functional Modes          | . 24 |  |  |  |  |

| 8  | App   | ications and Implementation       | 25   |

|----|-------|-----------------------------------|------|

|    | 8.1   | Application Information           | . 25 |

|    | 8.2   | Typical Application               | 25   |

|    | 8.3   | Do's and Don'ts                   | 33   |

| 9  | Pow   | er Supply Recommendations         | 34   |

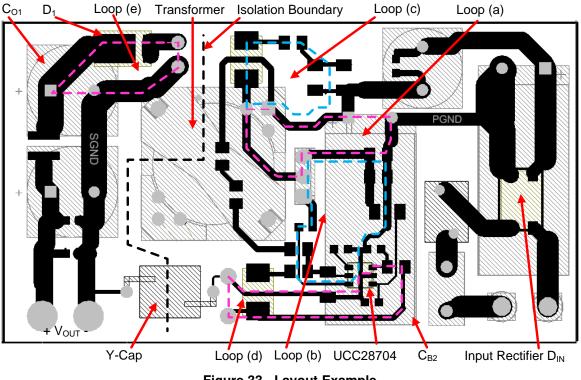

| 10 | Laye  | out                               | 34   |

|    |       | Layout Guidelines                 |      |

|    | 10.2  | Layout Example                    | . 35 |

| 11 | Dev   | ice and Documentation Support     | 36   |

|    | 11.1  | Device Support                    | . 36 |

|    | 11.2  | Documentation Support             | . 39 |

|    | 11.3  | Community Resources               | . 39 |

|    | 11.4  | Trademarks                        | . 39 |

|    | 11.5  | Electrostatic Discharge Caution   | . 39 |

|    | 11.6  | Glossary                          | . 39 |

| 12 |       | hanical, Packaging, and Orderable |      |

|    | Infor | mation                            | 39   |

|    |       |                                   |      |

# 4 Revision History

| DATE          | REVISION | NOTES            |

|---------------|----------|------------------|

| February 2016 | А        | Initial release. |

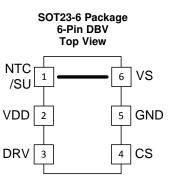

# 5 Pin Configuration and Functions

### **Pin Functions**

|        | PIN | I/O <sup>(1)</sup> | DECODIDITION                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME   | NO. | 1/0(**             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| NTC/SU | 1   | I/O                | NTC/SU is a multi-function pin. First, it provides an interface to an external NTC (negative temperature coefficient) resistor for remote temperature sensing. Pulling this pin low shuts down PWM action. Additionally, when used with an external depletion-mode FET and a low-voltage NPN transistor this pin provides high-voltage start up control. A maximum 100-pF noise filter capacitance may be added to this pin. The pin should be left floating if not used. |

| VDD    | 2   | Р                  | VDD is the bias supply input pin to the device.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DRV    | 3   | 0                  | DRV is an output pin used to drive the gate of an external high voltage MOSFET switching transistor.                                                                                                                                                                                                                                                                                                                                                                      |

| CS     | 4   | I                  | CS input connects to a ground referenced current sense resistor in series with the power switch. The resulting voltage is used to monitor and control the peak-primary current. A series resistor is added to this pin to compensate the peak-primary current levels as the AC mains input varies. A small capacitance, up to 30 pF, can be added to this pin to filter the current sense signal.                                                                         |

| GND    | 5   | G                  | GND pin is both the reference pin for the controller and the low-side return for the drive output. Special care should be taken to return all AC decoupling capacitors as close as possible to this pin and avoid any common-mode signal trace length with analog signal return paths.                                                                                                                                                                                    |

| VS     | 6   | Ι                  | VS is an input used to provide voltage and timing feedback to the controller. This pin is connected to a voltage divider between an auxiliary winding and GND. The value of the upper resistor of this divider is used to program the AC-mains run-and-stop thresholds and line compensation at the CS pin. Avoid placing a filter capacitor on this input which would interfere with accurate sensing of this waveform.                                                  |

(1)

P = Power, G = Ground, I = Input, O = Output, I/O = Input/Output

#### Specifications 6

### 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted) <sup>(1)</sup>

|                   |                                                           | MIN   | MAX           | UNIT |

|-------------------|-----------------------------------------------------------|-------|---------------|------|

| V <sub>VDD</sub>  | Bias supply voltage                                       |       | 38            | V    |

| VS                | Voltage range                                             | -0.75 | 7             | V    |

| CS, NTC           | Voltage range                                             | -0.5  | 5             | V    |

| V <sub>DRV</sub>  | Gate-drive voltage at DRV                                 | -0.5  | Self-limiting | V    |

| I <sub>DRV</sub>  | DRV continuous sink current                               |       | 50            | mA   |

| I <sub>DRV</sub>  | DRV peak sourcing current, V <sub>DRV</sub> = 10 V to 0 V |       | Self-limiting | mA   |

| I <sub>DRV</sub>  | DRV peak sink current, V <sub>DRV</sub> = 0 V to 10 V     |       | Self-limiting | mA   |

| I <sub>VS</sub>   | VS, peak, 1% duty-cycle, when detecting line voltage      |       | 1.2           | mA   |

| TJ                | Operating junction temperature range                      | -55   | 150           | °C   |

| T <sub>STG</sub>  | Storage temperature                                       | -65   | 150           | °C   |

| T <sub>LEAD</sub> | Lead temperature 0.6 mm from case for 10 seconds          |       | 260           | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings (1) only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 ESD Ratings

|                    |                         |                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup> | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM) ESD stress voltage <sup>(2)</sup>      | ±500  | V    |

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (1)

(2)

### 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|                 |                                                     | MIN   | MAX      | UNIT |

|-----------------|-----------------------------------------------------|-------|----------|------|

| VDD             | Bias supply operating voltage                       | 8.5   | 35       | V    |

| C <sub>DD</sub> | VDD bypass capacitor                                | 0.047 | no limit | μF   |

| I <sub>VS</sub> | VS pin sourcing current when detecting line voltage |       | 1.0      | mA   |

| TJ              | Operating junction temperature                      | -40   | 125      | °C   |

### 6.4 Thermal Information

|                    |                                                             | UCC28704 |      |

|--------------------|-------------------------------------------------------------|----------|------|

|                    | THERMAL METRIC                                              | DBV      | UNIT |

|                    |                                                             | 6 PINS   |      |

| $\theta_{JA}$      | Junction-to-ambient thermal resistance (1)                  | 150      | °C/W |

| θ <sub>JCtop</sub> | Junction-to-case (top) thermal resistance (2)               | 55       | °C/W |

| $\theta_{JB}$      | Junction-to-board thermal resistance (3)                    | 60       | °C/W |

| $\Psi_{JT}$        | Junction-to-top characterization parameter <sup>(4)</sup>   | 3        | °C/W |

| Ψ <sub>JB</sub>    | Junction-to-board characterization parameter <sup>(5)</sup> | 55       | °C/W |

(1) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

(2) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(3) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(4) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(5) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

### 6.5 Electrical Characteristics

| Over operating free-air temperature range, $V_{VDD} = 25 \text{ V}$ , $R_{NTC} = \text{open}$ , $-40^{\circ}\text{C} \le T_A \le 125^{\circ}\text{C}$ , $T_J = T_A$ (unless otherwise noted) |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | PARAMETER                                                                          | TEST CONDITIONS                                    | MIN   | ТҮР   | MAX                                      | UNIT |

|-----------------------|------------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|------------------------------------------|------|

| BIAS SUP              | PLY INPUT                                                                          |                                                    |       |       | L. L |      |

| I <sub>RUN</sub>      | Supply current, run                                                                | I <sub>DRV</sub> = 0, run state                    | 1.65  | 2.3   | 2.65                                     | mA   |

| I <sub>WAIT</sub>     | Supply current, wait                                                               | $I_{DRV} = 0$ , $V_{VDD} = 20$ V, wait state       | 40    | 70    | 100                                      | μA   |

| I <sub>START</sub>    | Supply current, start                                                              | $I_{DRV} = 0, V_{VDD} = 17 V$ , start state        |       | 1.5   | 2.5                                      | μA   |

| I <sub>FAULT</sub>    | Supply current, fault                                                              | I <sub>DRV</sub> = 0, fault state                  | 1.7   | 2.2   | 2.8                                      | mA   |

| UNDER-V               | OLTAGE LOCKOUT                                                                     |                                                    |       |       | ·                                        |      |

| V <sub>VDD(on)</sub>  | VDD turn-on threshold                                                              | V <sub>VDD</sub> low to high                       | 17.5  | 21    | 23                                       | V    |

| V <sub>VDD(off)</sub> | VDD turn-off threshold                                                             | V <sub>VDD</sub> high to low                       | 7.3   | 7.7   | 8.15                                     | V    |

| <b>VS INPUT</b>       |                                                                                    |                                                    |       |       | L.                                       |      |

| V <sub>VSR</sub>      | Regulating level (1)                                                               | Measured at no-load condition, $T_J = 25^{\circ}C$ | 4.02  | 4.06  | 4.1                                      | V    |

| V <sub>VSNC</sub>     | Negative clamp level                                                               | I <sub>VS</sub> = -300 μA                          | 190   | 250   | 325                                      | mV   |

| I <sub>VSB</sub>      | Input bias current                                                                 | $V_{VS} = 4 V$                                     | -0.25 | 0     | 0.25                                     | μA   |

| CS INPUT              |                                                                                    |                                                    |       |       |                                          |      |

| V <sub>CST(max)</sub> | Max CS threshold voltage (2)                                                       | V <sub>VS</sub> = 3.70 V                           | 720   | 750   | 784                                      | mV   |

| V <sub>CST(min)</sub> | Min CS threshold voltage (2)                                                       | V <sub>VS</sub> = 4.35 V                           | 170   | 187.5 | 210                                      | mV   |

| K <sub>AM</sub>       | AM control ratio                                                                   | V <sub>CST(max)</sub> / V <sub>CST(min)</sub>      | 3.55  | 4     | 4.4                                      | V/V  |

| V <sub>CCR</sub>      | Constant-current regulating level                                                  |                                                    | 345   | 356   | 369                                      | mV   |

| K <sub>LC</sub>       | Line compensating current<br>ratio, I <sub>VSLS</sub> /<br>(current out of CS pin) | I <sub>VSLS</sub> = -300 μA                        | 23    | 25    | 29                                       | A/A  |

| T <sub>CSLEB</sub>    | Leading-edge blanking time                                                         | DRV output duration, $V_{CS} = 1 V$                | 170   | 255   | 340                                      | ns   |

(1) The regulation level and OV threshold at VS decrease with increasing temperature by 1 mV/°C. This compensation over temperature is included to reduce the variances in power supply output regulation over-voltage detection with respect to the external output rectifier.

(2) These threshold voltages represent average levels. This device automatically varies the current sense threshold to improve EMI performance.

# **Electrical Characteristics (continued)**

| Over operating free-air temperature range, $V_{VI}$ | $_{DD}$ = 25 V, $R_{NTC}$ = open, –40°C ≤ T | $T_A \le 125^{\circ}C$ , $T_J = T_A$ (unless otherwise noted) |

|-----------------------------------------------------|---------------------------------------------|---------------------------------------------------------------|

|                                                     |                                             |                                                               |

|                        | PARAMETER                                                             | TEST CONDITIONS                                                | MIN  | ТҮР  | MAX                                      | UNIT |  |

|------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------|------|------|------------------------------------------|------|--|

| DRV                    |                                                                       |                                                                |      |      | ·                                        |      |  |

| I <sub>DRS</sub>       | DRV source current                                                    | $V_{DRV} = 5 V, V_{VDD} = 9 V$                                 | 25   | 32   | 38                                       | mA   |  |

| R <sub>DRVLS</sub>     | DRV low-side drive resistance                                         | I <sub>DRV</sub> = 10 mA                                       |      | 6.5  | 12                                       | Ω    |  |

| V <sub>DRCL</sub>      | DRV clamp voltage                                                     | $V_{VDD} = 35 V$                                               | 9.5  | 10.6 | 13                                       | V    |  |

| R <sub>DRVSS</sub>     | DRV pull-down in start state                                          |                                                                | 165  | 205  | 250                                      | kΩ   |  |

| TIMING                 |                                                                       |                                                                |      |      | ·                                        |      |  |

| f <sub>SW(max)</sub>   | Maximum switching frequency (3)                                       | V <sub>VS</sub> = 3.7 V                                        | 78   | 85   | 94                                       | kHz  |  |

| f <sub>SW(min)</sub>   | Minimum switching frequency                                           | V <sub>VS</sub> = 4.6 V                                        | 0.88 | 1.03 | 1.18                                     | kHz  |  |

| t <sub>ZTO</sub>       | Zero-crossing timeout delay                                           |                                                                | 1.7  | 2.39 | 3                                        | μs   |  |

| t <sub>CCUV_BLAN</sub> | Blanking delay time before CCUV shutdown                              | $V_{\text{VS}}$ step from 3.5 V to 2.4 V to DRV stop switching | 90   | 120  | 150                                      | ms   |  |

| PROTECTI               | N                                                                     | · · · · · ·                                                    |      |      |                                          |      |  |

| K <sub>OVP</sub>       | Over-voltage threshold ratio to $V_{VSR}$                             | V <sub>OVP</sub> /V <sub>VSR</sub>                             | 1.13 | 1.15 | 1.18                                     | V/V  |  |

| V <sub>CCUV</sub>      | CCUV $V_O = 3.0 V$                                                    | $T_J = 25^{\circ}C$ , auto restart after fault                 | 2.41 | 2.48 | 2.55                                     | V    |  |

| V <sub>OCP</sub>       | Over-current threshold                                                | At CS input                                                    | 1.35 | 1.51 | 1.6                                      | V    |  |

| I <sub>VSL(run)</sub>  | VS line-sense run current                                             | Current out of VS pin - increasing                             | 190  | 220  | 265                                      | μA   |  |

| I <sub>VSL(stop)</sub> | VS line-sense stop current                                            | Current out of VS pin - decreasing                             | 70   | 80   | 100                                      | μA   |  |

| K <sub>VSL</sub>       | VS line-sense ratio I <sub>VSL(run)</sub> /<br>I <sub>VSL(stop)</sub> |                                                                | 2.55 | 2.8  | 2.95                                     | A/A  |  |

| T <sub>J(stop)</sub>   | Thermal shut-down temperature <sup>(4)</sup>                          | Internal junction temperature                                  |      | 150  |                                          | °C   |  |

|                        | MPENSATION                                                            | •                                                              |      |      |                                          |      |  |

| V <sub>CVS(max)</sub>  | Maximum compensation at VS                                            | Change in VS regulating level at full-<br>load                 | 180  | 220  | 260                                      | mV   |  |

| NTC INPUT              |                                                                       | ·                                                              |      |      | L. L |      |  |

| V <sub>NTCTH</sub>     | NTC shut-down threshold                                               | VDD UVLO cycle when below this threshold                       | 0.9  | 0.95 | 1                                        | V    |  |

| I <sub>NTC</sub>       | NTC pull-up current, out of pin                                       | V <sub>NTC</sub> = 1.1 V                                       | 90   | 100  | 120                                      | μA   |  |

These frequency limits represent average levels. This device automatically varies the switching frequency to improve EMI performance. Not tested in production. (3) (4)

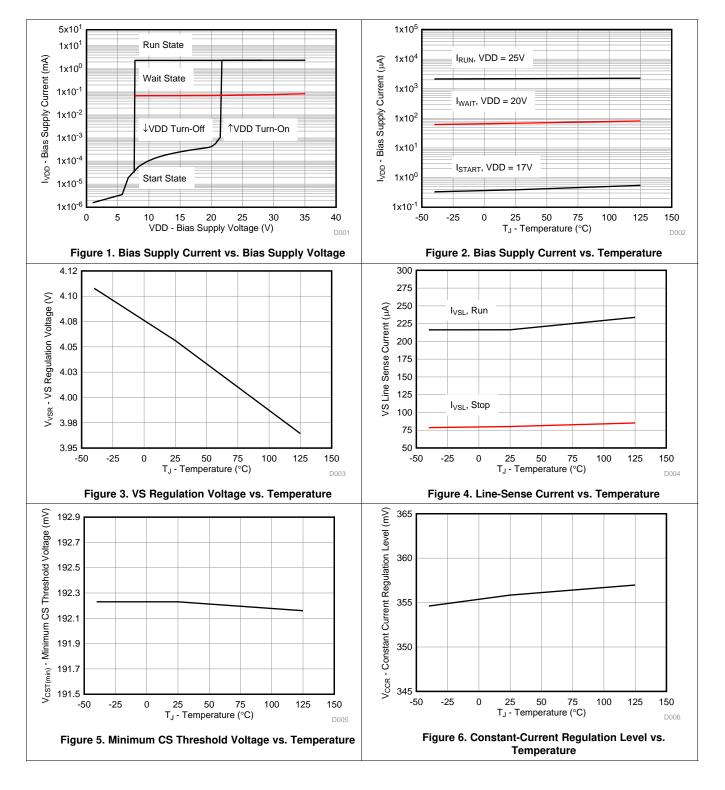

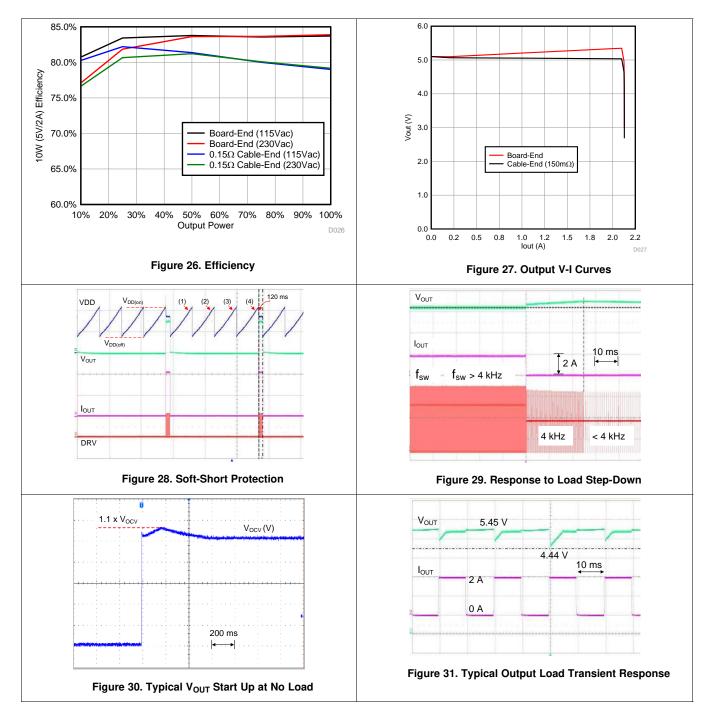

### 6.6 **Typical Characteristics**

VDD = 25 V, unless otherwise noted.

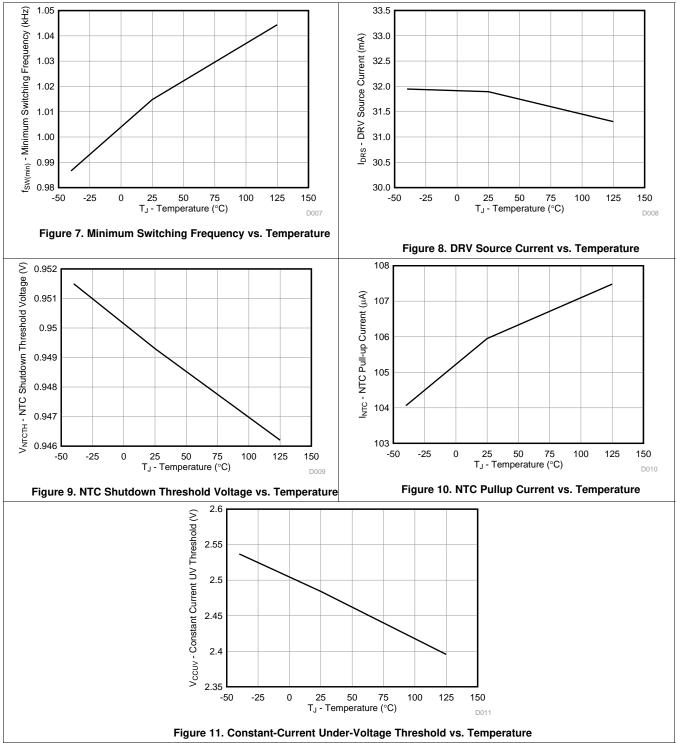

## **Typical Characteristics (continued)**

VDD = 25 V, unless otherwise noted.

## 7 Detailed Description

### 7.1 Overview

The UCC28704 flyback power supply controller provides accurate constant voltage and constant current regulation with primary-side feedback control. It also eliminates the need for opto-coupler feedback circuits. The controller optimizes the modulation scheme and the device's power management to boost power conversion efficiency, lower power dissipation at no-load and light load. Frequency dithering reduces the EMI peak energy at the fundamental switching frequency and harmonics. Features include fixed cable compensation and constant current output under-voltage shutdown, or CCUV, to protect USB terminals from getting over-heated or burn-out condition during soft-short circuit fault.

The controller operates in discontinuous conduction mode with valley switching to minimize switching losses. A combination of frequency modulation and primary peak current modulation to provide high power conversion efficiency across the load range. Accurate voltage and constant current regulation, fast dynamic response, and fault protection are achieved with primary-side control. A complete charger solution can be realized with a straightforward design process, low cost and low component count.

In UCC28704, as compared to UCC28700/1/2/3, features such as constant current under voltage protection and enhanced load transient schemes have been added. Also, in UCC28704, the demagnetizing ratio has been extended to 0.475 along with an increased AM ratio of 4:1. The maximum frequency of the controller is set at 85 kHz and the AM region switching frequency is optimally set at 25 kHz to have better trade-offs between no-load standby power consumption and load transient response. UCC28704 also incorporates schemes to have better noise rejection at the output voltage sense (VS pin) allowing for improved output voltage ripple reduction.

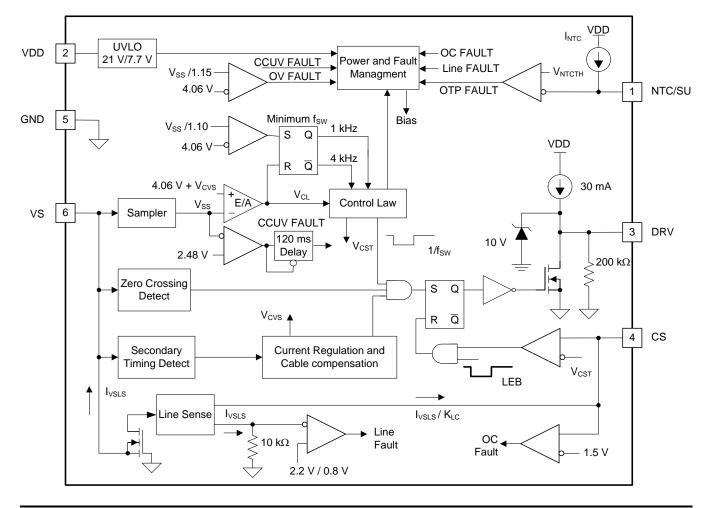

### 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Detailed Pin Description

### 7.3.1.1 VDD (Device Bias Voltage Supply)

The VDD pin is typically powered from a rectified auxiliary transformer winding, the same winding that is used to capture the output voltage level. A bypass capacitor, with minimum value 0.047  $\mu$ F, on the VDD pin is used for initially biasing the device to start-up along with a resistive or active source of start-up charging current. UVLO start / stop levels of 21 V / 7.7 V accommodate lower values of VDD capacitance that in turns keeps the start-up current low, which for resistive start-up has an impact on both stand-by power and power-on delay. A high, 35-V, maximum operating level on VDD alleviates concerns with leakage energy charging of VDD and gives added flexibility to when varying power supply output voltage must be supported.

### 7.3.1.2 GND (Ground)

This is an external return pin, and provides the reference point for both external signal and the gate drive of the device. The VDD bypass capacitor should be placed close to this pin. Critical component GND connections from the VS, CS and NTC pins should have dedicated and short paths to this pin.

### 7.3.1.3 VS (Voltage-Sense)

The VS pin is connected to a resistor divider from the auxiliary winding to ground. The output-voltage feedback information is sampled at the end of the transformer secondary current demagnetization time to provide an accurate representation of the output voltage. Timing information to achieve valley-switching and to control the duty cycle of the secondary transformer current is determined by the waveform on the VS pin. The VS input is a critical signal and will generally be with relatively high impedance. To avoid unpredictable behavior avoid placing a filter capacitor on this pin and keep the total PCB area tied to VS at a minimum.

The VS pin also senses the bulk capacitor input voltage to provide for ac-input run and stop thresholds, and to compensate the current-sense threshold across the AC-input range. This information is sensed by monitoring the current pulled out of the VS pin during the MOSFET on-time. During this time the voltage on the VS pin is clamped to about 250mV below GND. As a result, the current out of the pin is determined by the upper VS divider resistor, the auxiliary to primary turns-ratio and the bulk input voltage level. For the AC-input run/stop function, the run threshold on VS is  $I_{VSL(run)}$  (typical 220  $\mu$ A) and the stop threshold is  $I_{VSL(stop)}$  (typical 80  $\mu$ A). The values for the auxiliary voltage divider upper-resistor  $R_{S1}$  and lower-resistor  $R_{S2}$  can be determined by the equations below.

$$R_{S1} = \frac{\sqrt{2 \times V_{IN(run)}}}{N_{PA} \times I_{VSL(run)}} \approx \frac{V_{BULK(run)}}{N_{PA} \times I_{VSL(run)}}$$

where

- N<sub>PA</sub> is the transformer primary-to-auxiliary turns ratio,

- V<sub>IN(run)</sub> is the AC rms voltage to enable turn-on of the flyback converter (run),

- V<sub>BULK(run)</sub> is the DC bulk voltage to enable turn-on of the flyback converter (run),

- I<sub>VSL(run)</sub> is the run-threshold for the current pulled out of the VS pin during the primary MOSFET on-time. (see the *Electrical Characteristics* table).

$$R_{S2} = \frac{R_{S1} \times V_{VSR}}{N_{AS} \times (V_{OCV} + V_F) - V_{VSR}}$$

where

- V<sub>OCV</sub> is the converter regulated output voltage,

- V<sub>F</sub> is the output rectifier forward voltage drop at near-zero current,

- N<sub>AS</sub> is the transformer auxiliary to secondary turns ratio,

- R<sub>S1</sub> is the VS divider high-side resistance,

- V<sub>VSR</sub> is the CV regulating level at the VS input (see the *Electrical Characteristics* table).

(2)

This pin is also used to sense the output constant current under voltage (CCUV) level, used to shut down the converter in the case of a soft-short circuit at its output. Refer to Constant Current Under-Voltage Protection for further information.

### Feature Description (continued)

### 7.3.1.4 DRV (Gate Drive)

The DRV pin is connected to the MOSFET gate pin, usually through a series resistor. The DRV provides a gate drive signal which is clamped to 10.5-V internally. During turn-on the driver applies a typical 30-mA current source out of the DRV pin. When the DRV voltage rises to above 9 V the output current is reduced to about 100  $\mu$ A. This current brings the DRV voltage to the 10.5-V clamp level, or to VDD, whichever is less. The 30-mA current provides adequate turn-on speed while automatically limiting noise generated at turn-on by the MOSFET drain dv/dt and by the leading edge turn-on current spike. The gate drive turn-off current is internally limited to about 400 mA when DRV is above about 4 V. At lower DRV voltages the current will reduce, eventually being limited by the low-side on resistance, R<sub>DS(on)</sub>. The drain turn-on and turn-off dv/dt can be further impacted by adding external resistor in series with DRV pin. The drain current resonances can be damped with a small series gate resistor, generally less than a 1  $\Omega$ .

### 7.3.1.5 CS (Current Sense)

The current sense pin is connected through a series resistor ( $R_{LC}$ ) to the current-sense resistor ( $R_{CS}$ ). The controller varies the internal current sense threshold between 0.188 V and 0.75 V, setting a corresponding control range for the peak-primary winding current to a 4-to-1 range. The series resistor  $R_{LC}$  provides an input voltage feed-forward function. The voltage drop across this resistor reduces primary-side peak current as the line voltage increases, compensating for the increased di/dt and delays in the MOSFET turn-off. There is an internal leading-edge blanking time of 255 ns to eliminate sensitivity to the MOSFET turn-on leading edge current spike. If additional blanking time is needed, a small bypass capacitor, up to 30 pF, can be placed on between CS pin and GND pin. The value of  $R_{CS}$  is determined by the target output current in constant current (CC) regulation. The values of  $R_{CS}$  and  $R_{LC}$  can be determined by the equations below. The term  $\eta_{XFMR}$  is intended to account for the energy stored in the transformer but not delivered to the secondary. This includes transformer core and copper losses, bias power, and primary leakage inductance losses.

**Example:** With a transformer core and copper losses of 3%, leakage inductance caused power losses 2%, and bias power to output power ratio of 0.5%. The transformer power transfer efficiency is estimated as  $\eta_{XFMR} = 100\% - 3\% - 2\% - 0.5\% = 94.5\%$

$$R_{CS} = \frac{V_{CCR} \times N_{PS}}{2 \times I_{OCC}} \times \sqrt{\eta_{XFMR}}$$

where

- V<sub>CCR</sub> is a current regulation constant (see the *Electrical Characteristics* table),

- N<sub>PS</sub> is the transformer primary-to-secondary turns ratio (a typical turns-ratio of 12 to 15 is recommended for 5-V output),

- I<sub>OCC</sub> is the target output current in constant-current regulation,

- $\eta_{XFMR}$  is the transformer efficiency.

$$R_{LC} = \frac{K_{LC} \times R_{S1} \times R_{CS} \times (t_D + t_{GATE\_OFF}) \times N_{PA}}{L_P}$$

where

- $R_{S1}$  is the VS pin high-side resistor value,

- R<sub>CS</sub> is the current-sense resistor value,

- t<sub>D</sub> is the current-sense delay (typical 50 ns) plus MOSFET turn-off delay,

- t<sub>GATE OFF</sub> is the primary-side main MOSFET turn-off time,

- N<sub>PA</sub> is the transformer primary-to-auxiliary turns-ratio,

- L<sub>P</sub> is the transformer primary inductance,

- K<sub>LC</sub> is a current-scaling constant (see the *Electrical Characteristics* table).

(4)

(3)

ÍNSTRUMENTS

Texas

www.ti.com

### Feature Description (continued)

### 7.3.1.6 NTC/SU (NTC Thermistor Shutdown and External Start Up Control)

The UCC28704 uses an external NTC resistor tied to the NTC/SU pin to program a thermal shutdown temperature for the power supply. The NTC/SU shutdown threshold is 0.95 V with an internal 105- $\mu$ A current source which results in a 9.05-k $\Omega$  thermistor shutdown threshold. A small capacitor with value not greater than 100 pF can be used on this pin for any noise reduction purposes. The capacitor with its value greater than 100 pF can cause a false over-temperature protection response. The NTC/SU pin should be left floating if not used.

The NTC/SU pin can be used to control an external depletion-mode FET to enable active high-voltage start up, Refer to Initial Power-On with A Depletion-Mode FET for more detail.

### 7.3.2 Primary-Side Regulation (PSR)

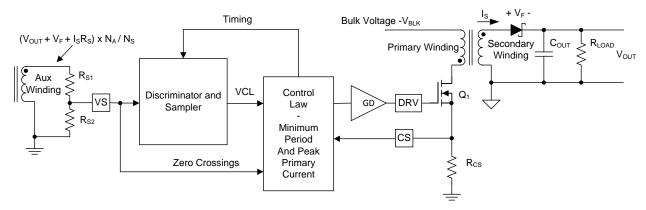

Figure 12 illustrates a simplified flyback convertor with the main voltage regulation blocks of the device shown. The power train operation is the same as any DCM flyback circuit but accurate output voltage and current sensing is the key to primary-side control.

Figure 12. Simplified Flyback Convertor (with the Main Voltage Regulation Blocks)

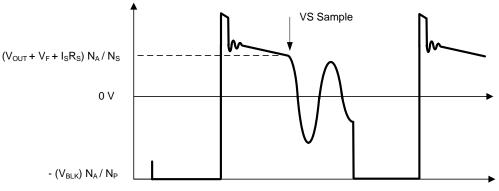

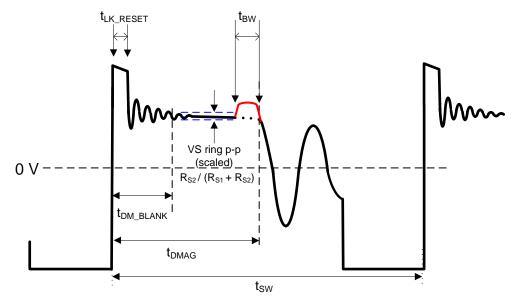

In primary-side control, the output voltage is sensed on the auxiliary winding during the transfer of transformer energy to the secondary. As shown in Figure 13 during this time, the auxiliary winding voltage has a down slope representing a decreasing total rectifier forward voltage drop  $V_F$  and resistance voltage drop ( $I_SR_S$ ) as the secondary current decreases to zero. To achieve an accurate representation of the secondary output voltage on the auxiliary winding, the discriminator reliably blocks the leakage inductance reset and ringing, continuously samples the auxiliary voltage during the down slope after the ringing is diminished, and captures the error signal at the time the secondary winding reaches zero current. The internal reference on VS is 4.06 V; the resistor divider is selected as outlined in the VS pin description.

Figure 13. Auxiliary Winding Voltage

### Feature Description (continued)

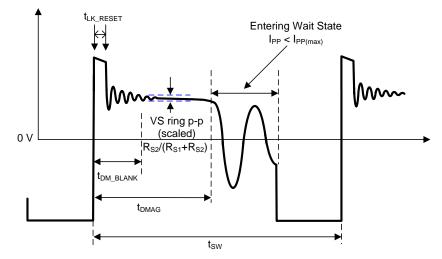

The UCC28704 VS signal sampler includes signal discrimination methods to ensure an accurate sample of the output voltage from the auxiliary winding. There are however critical details of the auxiliary winding signal to ensure reliable operation, specifically the reset time of the leakage inductance and the duration of any subsequent leakage inductance ring. Refer to Figure 14 for a detailed illustration of waveform criteria to ensure a reliable sample on the VS pin. The first detail to examine is the duration of the leakage inductance reset pedestal,  $T_{LK\_RESET}$  in Figure 14. Since this can mimic the waveform of the secondary current decay, followed by a sharp downslope, it is important to keep the leakage reset time less than 750 ns for  $I_{PRI}$  minimum, and less than 3.0  $\mu$ s for  $I_{PRI}$  maximum. The second detail is the amplitude of ringing on the  $V_{AUX}$  waveform following  $t_{LK\_RESET}$ . The peak-to-peak voltage at the VS pin should be less than approximately 250 mV\_p-p at least 250 ns before the end of the demagnetization time,  $t_{DMAG}$ . If there is a concern with excessive ringing, it usually occurs during light or no load conditions, when  $t_{DMAG}$  is at the minimum,  $t_{DMAG(min)}$ . The tolerable ripple on VS is scaled up to the auxiliary winding voltage by  $R_{S1}$  and  $R_{S2}$ , and is equal to 250 mV  $\times$  ( $R_{S1}+R_{S2}$ ) /  $R_{S2}$ . The snubber designs can be designed to allow the ripple voltage to meeting these requirements.

As mentioned in Device Functional Modes, when  $I_{PP} < I_{PP(max)}$ , the device operation enters a "Wait" state during each switching cycle of its non-switching portion as shown in Figure 14. In the *Wait* state, the device bias current changes to  $I_{WAIT}$  (typical 70  $\mu$ A) from  $I_{RUN}$  (typical 2.3 mA), reducing its bias power to help boost efficiency at light load and to reduce standby load power.

Figure 14. Auxiliary Waveform Details

#### 7.3.3 Primary-Side Constant Voltage (CV) Regulation

Feature Description (continued)

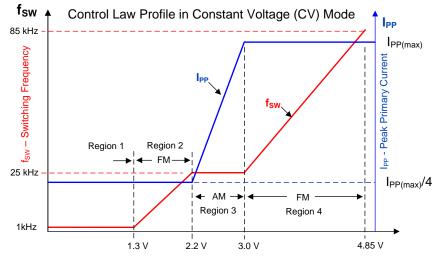

During voltage regulation (CV mode), the controller operates in frequency modulation mode and peak current amplitude modulation mode as illustrated in Figure 15 below. The UCC28704 incorporates internal voltage-loop compensation circuits so that external compensation is not necessary, provided that the value of  $C_{OUT}$  is high enough. The following equation determines a minimum value of  $C_{OUT}$  necessary to maintain a phase margin of about 40 degrees over the full-load range,

$$C_{OUT} \ge 100 \times \frac{I_{OCC}}{V_{OCV} \times f_{MAX}}$$

(5)

The internal operating frequency limits of the device are  $f_{SW(max)}$  and  $f_{SW(min)}$ , typically 85 kHz and 1 kHz, respectively. The choice of transformer primary inductance and primary-peak current sets the maximum operating frequency of the converter, which must be equal to or lower than  $f_{SW(max)}$ . Conversely, the choice of maximum target operating frequency and primary-peak current determines the transformer primary-inductance value. The actual minimum switching frequency for any particular converter depends on several factors, including minimum loading level, leakage inductance losses, switch-node capacitance losses, other switching and conduction losses, and bias-supply requirements. In any case, the minimum steady-state frequency of the converter must always exceed  $f_{SW(min)}$  or the output voltage may rise to the over-voltage protection level (OVP) and the controller responds as described in Fault Protection.

To achieve a regulated output voltage in the CV mode operation, energy balance has to be maintained. As the UCC28704 has a minimum switching frequency typical 1 kHz, together with the energy per switching cycle determined by converter parameters, such as the transformer primary inductance Lp and the selected  $R_{CS}$  resistor, the converter has a minimum input power. A proper pre-load needs to be selected to ensure that this minimum energy is balanced during the no-load condition. The selection of the line compensation resistor value ( $R_{LC}$ ) connected to the CS pin can impact the energy per switching cycle based on low-line and high-line conditions. Typical Application section provides a design example to show how to implement these considerations.

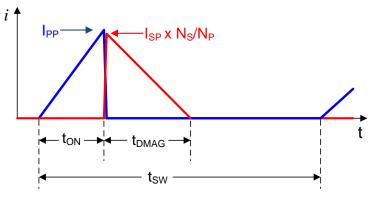

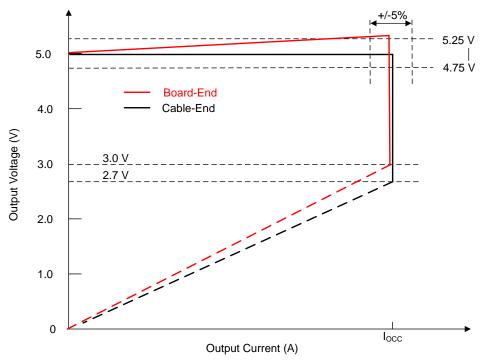

In the CV mode operation, the cable compensation is in effect. The cable compensation is to adjust the output voltage at board-end to be higher than the no-load setup point, noted as  $V_{OCV}$ , then to compensate the voltage drop due to the cable resistance through which the load current  $I_O$  is flowing. The UCC28704 cable compensation is fixed at 6% of  $V_{OCV}$  at full load, and the board-end output voltage is described by Equation 6:

$$V_{OUT} = V_{OCV} \times (1 + 0.06 \times \frac{I_0}{I_{OCC}})$$

(6)

www.ti.com

### Feature Description (continued)

Due to the cable compensation, the output voltage at board-end is seen higher than  $V_{OCV}$  with a positive slope when load current  $I_O> 0$ . The output voltage at the cable's end can be flat, upturned, or downturned, depending on the cable total resistance in use. Primary-Side Constant Current (CC) Regulation has more descriptions on the cable compensation.

Control Voltage, E/A Output - V<sub>CL</sub>

In CV mode operation, the control consists of four regions, namely, region 1 through 4. The device internal error op-amp output  $V_{CL}$  sets a particular region operation. Refer to Figure 12 for  $V_{CL}$ . The steady-state control-law voltage,  $V_{CL}$ , ranges between 1.3 V to 4.85 V. Heavy load operation is usually in region 4 where frequency modulation to output regulation is used and primary-peak current is controlled at its maximum. Region 3 is usually for medium-load range typically from 10% load and above. In this region switching frequency is fixed at nominal 25 kHz along with primary-peak current varying from 25% to 100% of its maximum. A low operating frequency range (region 2) is for lighter loads to achieve stable regulation at low frequencies. In region 2, peak-primary current is always maintained at  $I_{PP(max)}/4$  in the lower frequency level. Transitions between levels are automatically accomplished by the controller depending on the internal control-law voltage,  $V_{CL}$ . During a load transient condition when  $V_{CL} > 4.85$  V, the device operates in constant current mode. When load is in step-down transient demanding frequency lower than 4 kHz, first, the device stays at 4 kHz for up to 500 ms, or the output voltage reaches about 10% over the  $V_{OCV}$  within 500 ms, then the device adjusts the switching frequency to be lower than 4 kHz as needed. More details can be found in Load Transient Response.

**NSTRUMENTS**

FXAS

### Feature Description (continued)

### 7.3.4 Primary-Side Constant Current (CC) Regulation

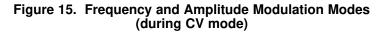

Timing information at the VS pin and current information at the CS pin allow accurate regulation of the secondary average current. The control law dictates that as power is increased in CV regulation and approaching CC regulation the primary-peak current is at  $I_{PP(max)}$ . Referring to Figure 16 below, the primary peak current ( $I_{PP}$ ), turns-ratio ( $N_S/N_P$ ), secondary demagnetization time ( $t_{DMAG}$ ), and switching period ( $t_{SW}$ ) determine the secondary average output current. Ignoring leakage inductance effects, the average output current is constant for given By regulating the secondary rectifier conduction duty cycle, the output average current is constant for given  $I_{PP}$  and transformer turns-ratio. When the load increases, the secondary-side rectifier conduction duty cycle keep increasing. Once it reaches preset value of 0.475, the converter switching frequency is then reduced to maintain 0.475 secondary-side duty cycle. Therefore, the output current is kept constant. Because the current is kept constant, the increasing load results in lower output voltage. Converter can shut down in this condition if the output voltage drops below CCUV protection level, or UCC28704 VDD drops below its UVLO turn-off threshold.

Figure 16. Transformer Currents

$$I_{OUT} = \frac{I_{PP}}{2} \times \frac{N_P}{N_S} \times \frac{t_{DMAG}}{t_{SW}}$$

(7)

As shown in Figure 17 below, CV mode operation is from  $I_0 = 0$  to  $I_{OCC}$ ; at  $I_0 = I_{OCC}$ , the operation enters CC mode and  $V_0$  starts to drop as the load resistance becomes further lower while  $I_0$  is maintained at  $I_{OCC}$  until Vo reaches the CCUV threshold. Details of the CCUV operation are given in Constant Current Under-Voltage Protection. Figure 17 shows the output at board-end and at cable-end. The cable compensation nominally compensates 300 mV for a 5V-output at the  $I_{OCC}$  level.

Figure 17. Typical Target Output V-I Characteristic

### Feature Description (continued)

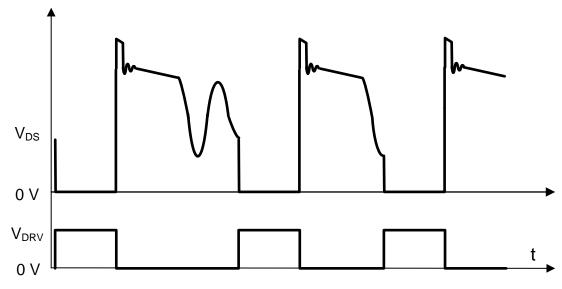

### 7.3.5 Valley-Switching and Valley-Skipping

The UCC28704 utilizes valley switching to reduce switching losses in the MOSFET, reduce induced-EMI, and minimize the turn-on current spike at the sense resistor. The controller operates in valley-switching in all load conditions unless the  $V_{DS}$  ringing diminished.

Referring to Figure 18 below, the UCC28704 operates in a valley-skipping mode in most load conditions to maintain an accurate voltage or current regulation point and still switch on the lowest available  $V_{DS}$  voltage.

Figure 18. Valley-Skipping Mode

The UCC28704 forces a controlled minimum switching period corresponding to the power supply operating frequency. In each switching cycle, after the minimum period is expired, the UCC28704 looks for the next resonant valley on the auxiliary winding. The controller initiates a new power cycle at this valley point which corresponds to a reduced voltage level on the power MOSFET. If at the point in time when the minimum period expires ringing on the transformer winding has decayed such that no further resonant valleys can be detected a new power cycle is initiated following a fixed time,  $t_{ZTO}$ .

### Feature Description (continued)

### 7.3.6 Start-Up Operation

Upon application of input voltage to the converter, the start up resistance connected to VDD from the bulk capacitor voltage ( $V_{BULK}$ ) charges the VDD capacitor. During charging of the VDD capacitor, the device supply current is less than 1.5  $\mu$ A. When VDD reaches the 21-V UVLO turn-on threshold, the controller is enabled and the converter starts switching. The peak-primary currents with initial three cycles are limited to  $I_{PP(min)}$ . This allows sensing any initial input or output faults with minimal power delivery. When confirmed that the input voltage is above the programmed converter turn-on voltage and with no faults detected, the start-up process proceeds and normal power conversion follows. The converter remains in discontinuous conduction mode operation during charging of the output capacitor(s), maintaining a constant output current until the output voltage is in regulation.

Initial power-on to the UCC28704 device is achieved by one of the two approaches that are described in Initial Power-On with a Start-Up Resistor and Initial Power-On with A Depletion-Mode FET.

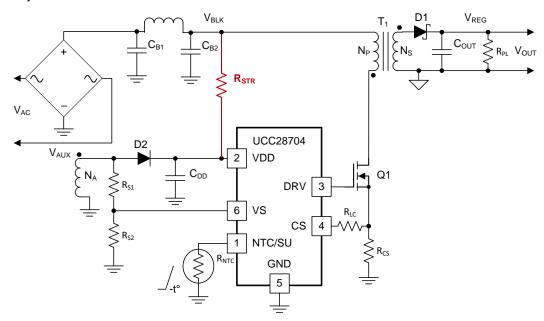

### 7.3.6.1 Initial Power-On with a Start-Up Resistor

A common used initial power-on approach for UCC28704 is to use a start-up resistor,  $R_{STR}$ , to tie VDD to  $V_{BLK}$ , as show in Figure 19. With this approach, the VDD pin is connected to a bypass capacitor to ground and a start-up resistance to the input bulk capacitor (+) terminal. The VDD turn-on UVLO threshold is 21 V ( $V_{VDD(on)}$ )and turn-off UVLO threshold is 7.7 V ( $V_{VDD(off)}$ ), with an available operating range up to 35 V. The USB charging practice requires the output current to operate in constant-current mode from 5 V to typical about 3 V; this is easily achieved with a nominal VDD of approximately 15 V. The additional VDD headroom up to 35 V allows for VDD to rise due to the leakage energy delivered to the VDD capacitor in high-load conditions. Also, the wide VDD range provides the advantage of selecting a relatively small VDD capacitor and high-value start-up resistance to minimize no-load stand-by power loss in the start-up resistor.

The  $R_{STR}$  value has effect to power-on delay time and no-load standby power losses. Both are usually part of the design specifications. Increase  $R_{STR}$  reduces standby power losses while increases power-on delay time. A typical range of  $R_{STR}$  is from 10 M $\Omega$  to 15 M $\Omega$  as initial design start point for off-line AC-to-DC adapters where power-on delay time usually requires less than two seconds. Due to the limited voltage rating,  $R_{STR}$  is normally implemented by two or three resistors in series.

Figure 19. Power-On with Start-Up Resistor

### Feature Description (continued)

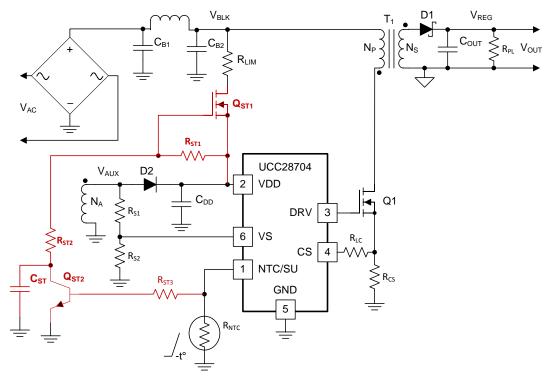

### 7.3.6.2 Initial Power-On with A Depletion-Mode FET

The UCC28704 NTC/SU pin can control an external depletion-mode FET to provide more efficient start-up. This provides a fast start-up time with eliminating the loss associated with the start-up circuit. Therefore, the standby power at no load can be minimized. This gives an alternative method to power on the device initially. As shown in Figure 20, the depletion mode FET HV start-up circuit consists of Q<sub>ST1</sub>, Q<sub>ST2</sub>, C<sub>ST</sub>, R<sub>ILIM</sub>, and R<sub>ST1</sub> to R<sub>ST3</sub>.

Before VDD reaches  $V_{VDD(on)}$ , NTC/SU stays low,  $Q_{ST1}$  turns on, which enables the quick charge of  $C_{DD}$  thereby achieving a shorter power-on delay time. After VDD  $\geq V_{VDD(on)}$ , NTC/SU starts sourcing 105  $\mu$ A to turn on  $Q_{ST2}$  then turns off  $Q_{ST1}$ . This stops  $Q_{ST1}$  providing current to UCC28704 and minimizes the loss in the start-up circuit. In normal operation when  $I_{PP} < I_{PP(max)}$ , the device enters *wait* state in each switching cycle, see Figure 14 for *wait* state time. During *wait* state, NTC/SU stops sourcing 105  $\mu$ A; which turns off  $Q_{ST2}$  and can potentially cause  $Q_{ST1}$  to turn on. Hence  $C_{ST}$  is added to ensure that  $Q_{ST1}$  is off even during *wait* state. For reference,  $R_{ST1} = R_{ST2} = 2 M\Omega$ ,  $R_{ST3} = 100 \ k\Omega$ ,  $C_{ST} = 1 \ nF$ ,  $R_{ILIM} = 365 \ k\Omega$ , as an example. To select a depletion-mode FET for  $Q_{ST1}$ , BSS126 or similar can be an option.

Figure 20. Power-On with a Depletion-Mode FET

### Feature Description (continued)

### 7.3.7 Fault Protection

There is comprehensive fault protection incorporated into the UCC28704. Protection functions include:

- Output Over-Voltage

- Input Under-Voltage

- Primary Over-Current Fault

- CS Pin Open Fault

- CS Pin Short-to-GND Fault

- VS Pin Fault

- External NTC Over-Temperature

- Device Internal Over-Temperature

- Constant Current Under Voltage Output Shutdown (CCUV) for Soft-Short Protection

**Output Over-Voltage:** The output over-voltage function is determined by the voltage feedback on the VS pin. If the voltage sample on VS exceeds 4.67 V, 115% of the nominal regulating level, for three consecutive switching cycles an OV fault is asserted. Once asserted the device stops switching, initiating a UVLO reset and re-start fault cycle. During the fault, the VDD bias current remains at the run current level, discharging the VDD pin to the UVLO turn-off threshold,  $V_{VDD(off)}$ . After that, the device returns to the start state, VDD now charging to  $V_{VDD(on)}$  where switching is initiated. The UVLO sequence repeats as long as the fault condition persists.

**Input Under-Voltage:** The line input run and stop thresholds are determined by current information at the VS pin during the MOSFET on-time. While the VS pin is clamped close to GND during the MOSFET on-time, the current through R<sub>S1</sub>, out of the VS pin, is monitored to determine a sample of the bulk capacitor voltage. A wide separation of run and stop thresholds allows clean start-up and shut-down of the power supply with the line voltage. From the start state, the sensed VS current, I<sub>VSL</sub>, must exceed the run current threshold, I<sub>VSL(run)</sub> (typical 220  $\mu$ A), within the first three cycles after switching starts as VDD reaches V<sub>VDD(on)</sub>. If it does not, then switching stops and the UVLO reset and re-start fault cycle is initiated. Once running, I<sub>VSL</sub> must drop below the stop level, I<sub>VSL(stop)</sub> (typically 80  $\mu$ A), for three consecutive cycles to initiate the fault response.

**Primary Over-Current:** The UCC28704 always operates with cycle-by-cycle primary-peak current control. The normal operating range of the CS pin is 0.75 V to 0.188 V. If the voltage on CS exceeds the 1.5-V over-current level, any time after the internal leading edge blanking time and before the end of the transformer demagnetization, for three consecutive cycles the device shuts down and the UVLO reset and re-start fault cycle begins.

**CS Pin Open:** The CS pin has a 2-µA minimum pull-up that brings the CS pin above the 1.5-V OC fault level if the CS pin is open. This causes the primary over-current fault after three cycles.

**CS Pin Short to GND:** On the first, and only the first cycle at start-up, the device checks to verify that the  $V_{CST(min)}$  threshold is reached at the CS pin within 4 µs of DRV going high. If the CS voltage fails to reach this level then the device terminates the current cycle and immediately enters the UVLO reset and re-start fault sequence.

**VS Pin:** Protection is included in the event of component failures on the VS pin. If the high-side VS divider resistor opens the controller stops switching. VDD collapses to its  $V_{VDD(off)}$  threshold, a start-up attempt follows with a single DRV on-time when VDD reaches  $V_{VDD(on)}$ . The UVLO cycle will repeat. If the low-side VS divider resistor is open then an output over-voltage fault occurs.

**NTC Over-Temperature:** UCC28704 uses the NTC/SU pin to program thermal shutdown threshold with an external NTC thermistor on this pin. The NTC shutdown threshold is 0.95 V with an internal 105- $\mu$ A current source which results in a 9.05-k $\Omega$  thermistor shutdown threshold. If the NTC/SU pin voltage is below 0.95 V at the end of the secondary current demagnetization time for three consecutive cycles switching stops and the UVLO reset and re-start fault sequence is initiated.

**Device Internal OTP:** The internal over-temperature protection threshold is 150°C. If the junction temperature of the device reaches this threshold the device initiates the UVLO reset and re-start fault cycle. If the temperature is still high at the end of the UVLO cycle, the protection cycle repeats.

**Constant Current Under-Voltage:** Output shutdown (CCUV) for soft-short protection. Constant Current Under-Voltage Protection provides detailed description for this fault and fault response.

### Feature Description (continued)

### 7.3.8 Constant Current Under-Voltage Protection

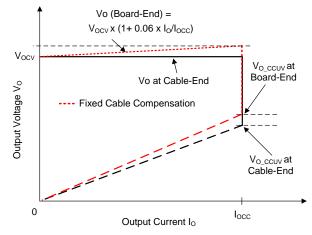

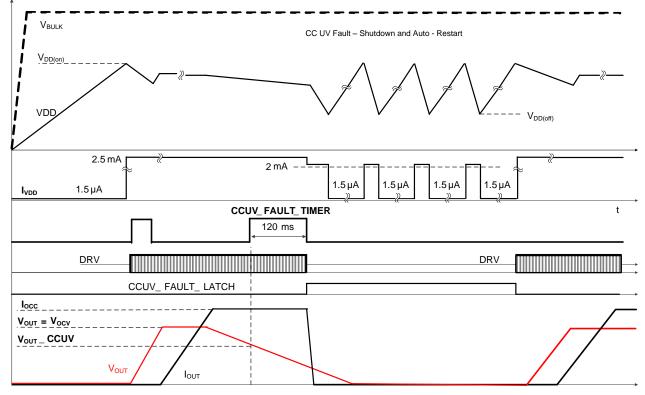

The constant current output under voltage shutdown (CCUV) feature is to provide protection for USB connectors from over-heat or burn-out due to soft-short circuit fault. A partial or soft-short can happen due to the presence of foreign objects at the terminals of the USB upstream facing port, UFP, for example, smartphones with USB Micro-B or USB Type-C connectors. When this happens along with the converter operates in CC mode with enough VDD voltage (VDD >  $V_{VDD(off)}$ ) available from auxiliary winding, the converter can sustain operation at this condition resulting in a potential USB burn-out condition which is named as *soft-short* fault to distinguish from a *hard-short* circuit fault. Traditional over-current protection and short-circuit protection cannot tell a soft-short fault. The UCC28704 provides protection when soft-short circuit fault occurs with the corresponding converter V-I characteristics as shown in Figure 21.

As shown in Figure 22, the CCUV feature of UCC28704 detects the operation of the converter under this condition when the controller is operating in CC mode and when the output voltage drops out of regulation, reaching the CCUV threshold. If the controller detects that the VS pin voltage is below  $V_{CCUV}$  threshold continuously for 120 ms, then it initiates a CCUV fault and sets the CCUV latch. Once the CCUV latch is set, the controller goes through 3 cycles of VDD-UVLO without any PWM operation and clears the latch on the 4th VDD UVLO power-up. If the CCUV condition still exists, then the controller enters into CCUV fault after 120 ms and repeats the UVLO cycles. This 120-ms time delay allows converter normal start up without triggering the CCUV protection. The flyback design should allow output voltage rise above CCUV protection level under normal operating conditions within 120ms or the CCUV fault may be triggered.

Figure 21. Typical Target Output V-I Curves

UCC28704

SLUSCA8A - FEBRUARY 2016 - REVISED FEBRUARY 2016

## Feature Description (continued)

Figure 22. Timing Diagram of CCUV and Output Re-Start

### Feature Description (continued)

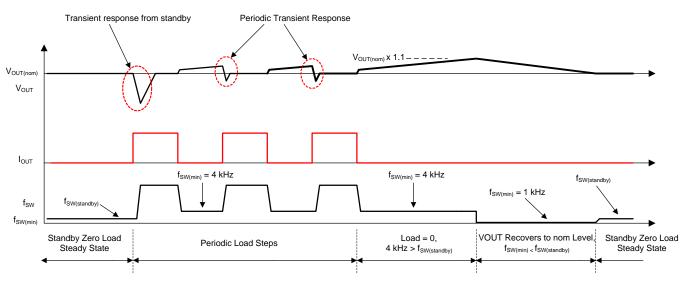

### 7.3.9 Load Transient Response

The UCC28704 can provide excellent transient performance for most load steps. However the response of PSR controller is always limited by the operating frequency of the converter, since the controller only samples or reads the output voltage once every switching cycle. At zero external load, or standby, the operating frequency is set by any preload together with the bias power needed. This frequency,  $f_{SW(standby)}$ , sets a maximum incremental response delay. The preload can always be adjusted, at the expense of standby power, to increase the standby frequency. The actual response delay depends on the relative timing of the load step within the switching cycle. Thus for a given load step,  $I_{OUT(step)}$ , the output deviation can be as large as:

$$\Delta V_{OUT} = \frac{I_{OUT(step)}}{C_{OUT} \times f_{SW(standby)}}$$

(8)

UCC28704

SLUSCA8A - FEBRUARY 2016 - REVISED FEBRUARY 2016

In the case of repeating load transients the situation is aggravated. Whenever the load steps from a modest current level to zero, there is a period of time when there is a slight over-shoot in the output voltage and the control loop saturates and force the converter operating at to its minimum switching frequency,  $f_{SW(min)}$ , or 1 kHz regardless what preload setting is. If the next positive load step occurs during this time the output deviation will be larger, remembering that  $f_{SW(standby)}$  must be >  $f_{SW(min)}$ .

A special transient response algorithm in this controller dynamically adjusts the minimum controlled switching frequency, such that during a mid to high current level condition the loop's minimum switching frequency is raised to  $f_{SW(lim)}$ , typically 4 kHz. This raised minimum switching frequency is maintained following a load step-down change until the output voltage rises momentarily to 10% above its normal regulating level or has stayed above its normal regulating level for 500 ms. During this time the response to a load step-up change benefits from the decreased response delay afforded by the 4-kHz switching frequency. This is illustrated in Figure 23. Application Curves provides test results and further description in regarding to this technique.

### NOTE

In applications where standby power is not critical the minimum operating frequency of the loop can be kept higher than 4 kHz. In these cases controller will continuously maintain a 4-kHz minimum frequency.

Figure 23. Dynamic Load Response

### 7.4 Device Functional Modes

The UCC28704 operates in different modes according to input voltage, VDD voltage, and output load conditions:

- At start-up, when VDD is less than the turn-on threshold, V<sub>VDD(on)</sub>, the device is simply waiting for VDD to reach this threshold while the VDD capacitor is getting charged.

- When VDD exceeds V<sub>VDD(on)</sub>, the device starts switching to deliver power to the converter output. The initial 3 switching cycles control the primary-peak current to I<sub>PP(min)</sub>. This allows sensing any initial input or output faults with minimal power delivery. When confirmed with input voltage above predetermined level and no fault conditions, start up process proceeds and normal power conversion follows. The converter will remain in discontinuous current mode operation during charging of the output capacitor(s), maintaining a constant output current until the output voltage reaches its regulation point.

- CV mode means that the converter keeps the output voltage constant. When the load current is less than

the current limit level, the converter operates in CV mode to keep the output voltage at the regulation level

over the entire load and input line ranges.

- CC mode means that the converter keeps the output current constant. When the output voltage is below the regulation level, the converter operates in CC mode to limit the output current.

- In CC mode, when the output voltage starts to drop below regulation and if it reaches below the CCUV threshold V<sub>CCUV</sub>, sensed at the VS pin, the controller declares a CCUV fault and disables PWM. The controller initiates a shutdown-restart operation. This protection mode helps avoid USB terminals from getting over-heated and thereby preventing a burn-out condition, which is also called soft-short protection. Detailed description is in Constant Current Under-Voltage Protection.

- When operating in CV mode where I<sub>PP</sub> reaches I<sub>PP(max)</sub>, the UCC28704 operates continuously in the *run* state. In this state, the VDD bias current is always at I<sub>RUN</sub> plus the average gate-drive current.

- When operating in CV mode where I<sub>PP</sub> is less than I<sub>PP(max)</sub>, the UCC28704 operates in the *wait* state between switching cycles and in the *run* state during a switching cycle. In the *wait* state, the VDD bias current is reduced to I<sub>WAIT</sub> after demagnetizing time of each switching cycle to improve efficiency at light loads. This helps reduce light-load power losses, particularly for achieving higher efficiency at 10% and 25% load conditions.

- When a dynamic load change occurs in CV mode, the UCC28704 provides an enhanced transient response to reduce load step caused V<sub>OUT</sub> dip in periodic load change operation. Detailed description is in Load Transient Response.

- The device operation can be stopped by the events listed below:

- If VDD drops below the V<sub>VDD(off)</sub> threshold, the device stops switching, its bias current consumption is lowered to I<sub>START</sub> until VDD rises above the V<sub>VDD(on)</sub> threshold. The device then resumes switching.

- If a fault condition is detected, the device stops switching and its bias current consumption becomes I<sub>FAULT</sub>. This current level discharges VDD to V<sub>VDD(off)</sub> where the bias current changes from I<sub>FAULT</sub> to I<sub>START</sub> until VDD rises above the V<sub>VDD(on)</sub> threshold.

- By pulling down NTC/SU pin to below V<sub>NTCTH</sub>, the device responds similar to that of an NTC fault wherein PWM is disabled and converter is shutdown. On releasing the pull-down on NTC, normal operation into CV mode will be restored.

- If a fault condition persists, the operation sequence described above in repeats until the fault condition or the input voltage is removed. Refer to Fault Protection for fault conditions and post-fault operation.

### 8 Applications and Implementation

### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

The UCC28704 device is a PSR controller optimized for isolated-flyback AC-to-DC single-output supply applications, typically in the range from 5 W to 25 W, providing constant-voltage (CV) mode control and constant current (CC) mode control for precise output regulation; and to help meet USB-compliant adaptors and charger requirements as well as help meeting DOE Level VI or CoC V5 Tier 2 efficiency performance. The device uses the information obtained from auxiliary winding sensing (VS) to control the output voltage without requiring optocoupler/TL431 feedback circuitry. Not requiring optocoupler feedback reduces the component count and makes the design more cost effective.

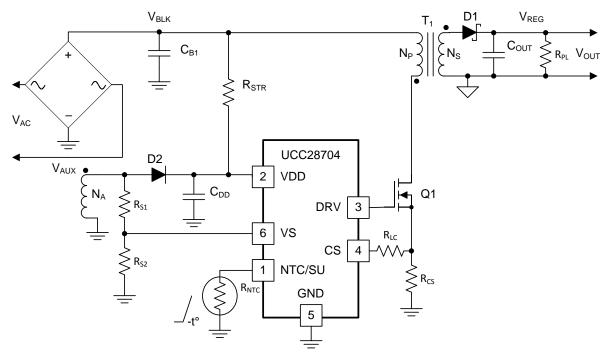

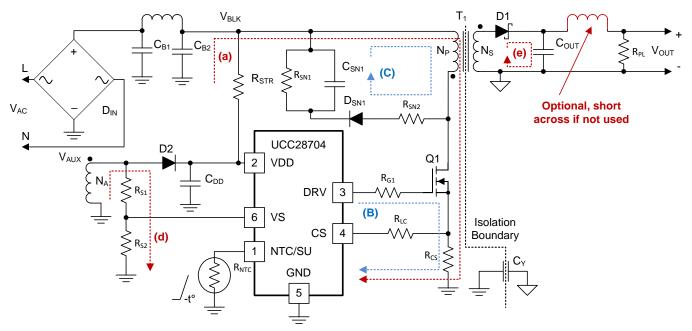

### 8.2 Typical Application

Figure 24 illustrates a typical circuit diagram for AC-to-DC adapter applications. It is a flyback converter with primary-side regulation (PSR) controlled by UCC28704. Such applications widely exist in ac-dc adapters for smartphones, tablet-computers, and e-readers and so forth. The following sub-sections provide critical design formulas.

Figure 24. Typical Application Circuit

### **Typical Application (continued)**

### 8.2.1 Design Requirements

The following table illustrates a typical subset of high-level design requirements for a particular converter of which many of the parameter values are used in the various design equations in this section. Many other necessary design parameters, such as  $f_{SW(MAX)}$  and  $V_{BULK(min)}$  for example, may not be listed in such a table. These values may be selected based on design experience or other considerations, and may be iterated to obtain optimal results.

|                       | PARAMETER                   | TEST CONDITIONS                                                | MIN  | ТҮР     | MAX  | UNIT             |  |  |  |  |

|-----------------------|-----------------------------|----------------------------------------------------------------|------|---------|------|------------------|--|--|--|--|

| INPUT CHARACTERISTICS |                             |                                                                |      |         |      |                  |  |  |  |  |

| V <sub>IN</sub>       | AC-line input voltage       |                                                                | 85   | 115/230 | 265  | V <sub>RMS</sub> |  |  |  |  |

| f <sub>LINE</sub>     | Line frequency              |                                                                | 47   | 50/60   | 63   | Hz               |  |  |  |  |

| P <sub>STBY</sub>     | No-load input power         | $V_{IN} = typ, I_O = 0A$                                       |      | 43      | 50   | mW               |  |  |  |  |

| OUTPUT (              | CHARACTERISTICS (MEASUREME  | NT AT 150-mΩ CABLE-END)                                        |      |         |      |                  |  |  |  |  |

| Vo                    | DC output voltage           | $V_{IN} = typ$ , $I_O = 0$ to $I_{OR}$                         | 4.75 | 5       | 5.25 | V                |  |  |  |  |

| V <sub>RIPPLE</sub>   | Output voltage ripple       | $V_{IN} = typ, I_O = I_{OR}$                                   |      |         | 80   | mV               |  |  |  |  |

| I <sub>OR</sub>       | Output rated current        | V <sub>IN</sub> = min to max                                   |      | 2.0     |      | А                |  |  |  |  |

| locc                  | Output constant current     | $V_{IN} = typ, I_O > I_{OR}$<br>2.7V < V <sub>O</sub> < 5V     | 2.1  | 2.2     | 2.3  | А                |  |  |  |  |

| V <sub>CCUV</sub>     | CC UV shutdown interception | $V_{IN}$ = typ, $I_O = I_{OCC}$                                |      | 2.7     |      | V                |  |  |  |  |

| η <sub>AVG</sub>      | Average efficiency          | V <sub>IN</sub> = typ, average of 25%, 50%, 75%, and 100% Load | 80%  |         |      |                  |  |  |  |  |

| η <sub>10</sub>       | Light-load efficiency       | V <sub>IN</sub> = typ, 10% load                                | 75%  |         |      |                  |  |  |  |  |

| SYSTEMS               | CHARACTERISTICS             |                                                                |      |         |      |                  |  |  |  |  |

| f <sub>sw</sub>       | Switching frequency         |                                                                | 1    |         | 65   | kHz              |  |  |  |  |

| T <sub>ON-Delay</sub> | Power-on delay time         | $V_{IN} = min$<br>$I_{O}= I_{OR}$ (constant resistor load)     |      |         | 1.8  | S                |  |  |  |  |

### Table 1. UCC28704 Design Parameters

#### 8.2.2 Detailed Design Procedure

This procedure outlines the steps to design a constant-voltage, constant-current flyback converter using the UCC28704 controller. Please refer to the Figure 24 for circuit details and section Device Nomenclature for variable definitions used in the applications equations below.

### 8.2.2.1 VDD Capacitance, CDD

The capacitance on VDD needs to supply the device operating current until the output of the converter reaches the target minimum operating voltage. At this time the auxiliary winding can sustain the voltage to the UCC28704. The total output current available to the load and to charge the output capacitors is the constantcurrent regulation target. The equation below assumes the output current of the flyback is available to charge the output capacitance until the minimum output voltage V<sub>OCC</sub> is achieved. The gate-drive current depends on particular MOSFET to be used. If with an estimated 1.0 mA of gate-drive current, C<sub>DD</sub> is determined by Equation 9.

$$C_{DD} = \frac{\left(I_{RUN} + 1.0\text{mA}\right) \times \frac{C_{OUT} \times V_{OCC}}{I_{OCC}}}{\left(V_{DD(\text{on}),\text{min}} - V_{DD(\text{off}),\text{max}}\right)}$$

(9)

### 8.2.2.2 VDD Start-Up Resistance, R<sub>STR</sub>

Once the VDD capacitance is known, the start-up resistance from V<sub>BULK</sub> to achieve the power-on delay time (t<sub>STB</sub>) target can be determined.

$$R_{STR} = \frac{\sqrt{2 \times V_{IN(min)}}}{I_{START} + \frac{V_{DD(on)} \times C_{DD}}{t_{STR}}}$$

### 8.2.2.3 Input Bulk Capacitance and Minimum Bulk Voltage

Determine the minimum voltage on the input capacitance, C<sub>B1</sub> and C<sub>B2</sub> total, in order to determine the maximum Np to Ns turns ratio of the transformer. The input power of the converter based on target full-load efficiency, minimum input rms voltage, and minimum AC input frequency are used to determine the input capacitance requirement.

Maximum input power is determined based on V<sub>OCV</sub>, I<sub>OCC</sub>, and the full-load efficiency target. An initial estimate of 84% can be assumed for the full-load efficiency for a 5-V/2-A design.

$$\mathsf{P}_{\mathsf{IN}} = \frac{\mathsf{V}_{\mathsf{OCV}} \times \mathsf{I}_{\mathsf{OCC}}}{\eta} \tag{11}$$

Equation 12 provides an accurate solution for input capacitance based on a target minimum bulk capacitor voltage. To target a given input capacitance value, iterate the minimum capacitor voltage to achieve the target capacitance.

$$C_{BULK} = \frac{P_{IN} \times \left(0.5 + \frac{1}{\pi} \times \arcsin\left(\frac{V_{BULK(min)}}{\sqrt{2} \times V_{IN(min)}}\right)\right)}{\left(2V_{IN(min)}^2 - V_{BULK(min)}^2\right) \times f_{LINE}}$$

Copyright © 2016, Texas Instruments Incorporated

(10)

(12)

### 8.2.2.4 Transformer Turns Ratio, Inductance, Primary-Peak Current

The maximum primary-to-secondary turns ratio can be determined by the target maximum switching frequency at full load, the minimum input capacitor bulk voltage, and the estimated DCM resonant time.

Initially determine the maximum available total duty cycle of the on time and secondary conduction time based on target switching frequency and DCM resonant time. For DCM resonant time, assume 500 kHz if you do not have an estimate from previous designs. For the transition mode operation limit, the period required from the end of secondary current conduction to the first valley of the V<sub>DS</sub> voltage is  $\frac{1}{2}$  of the DCM resonant period, or 1 µs assuming 500-kHz resonant frequency. D<sub>MAX</sub> can be determined using Equation 13.

$$D_{MAX} = 1 - \left(\frac{t_R}{2} \times f_{MAX}\right) - D_{MAGCC}$$

(13)

Once  $D_{MAX}$  is known, the maximum turns ratio of the primary to secondary can be determined with the equation below.  $D_{MAGCC}$  is defined as the secondary diode conduction duty cycle during constant-current, CC, operation. It is set internally by the UCC28704 at 0.475. The total voltage on the secondary winding needs to be determined; which is the sum of V<sub>OCV</sub>, the secondary rectifier V<sub>F</sub>, and the cable compensation voltage (V<sub>OCBC</sub>). For the 5-V USB charger applications, a turns ratio range of 12 to 15 is typically used for a 10-W design.

$$N_{PS(max)} = \frac{D_{MAX} \times V_{BULK(min)}}{D_{MAGCC} \times (V_{OCV} + V_F + V_{OCBC})}$$

(14)

$N_{PS}$  is determined also with other design factors such as primary MOSFET, secondary rectifier diode, as well as secondary MOSFET if synchronous rectifier is used. Once an optimum turns-ratio is determined from a detailed transformer design, use this ratio for the following parameters.