# **IM6654**

## 4096 Bit CMOS UV EPROM

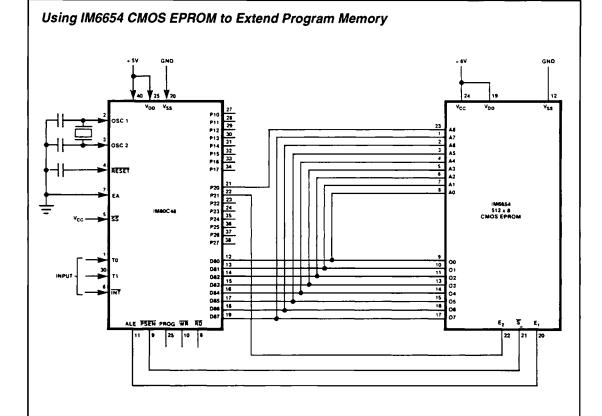

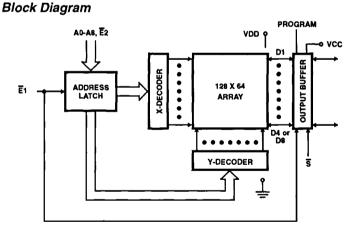

The Harris IM6654 is a fully decoded 4096 bit CMOS electrically programmable ROM (EPROM) fabricated with Harris' advanced CMOS processing technology. In all static states this device exhibits the microwatt power dissipation typical of CMOS. Inputs and three-state outputs are TTL compatible and allow for direct interface with common system bus structures. On-chip address registers and chip select functions simplify system interfacing requirements.

The IM6654 is specifically designed for program development applications where rapid turn-around for program changes is required. The device may be erased by exposing its transparent lid to ultraviolet light, and then reprogrammed.

## Rochester Electronics Manufactured Components

Rochester branded components are manufactured using either die/wafers purchased from the original suppliers or Rochester wafers recreated from the original IP. All re-creations are done with the approval of the Original Component Manufacturer (OCM).

Parts are tested using original factory test programs or Rochester developed test solutions to guarantee product meets or exceeds the OCM data sheet.

## **Quality Overview**

- ISO-9001

- AS9120 certification

- Qualified Manufacturers List (QML) MIL-PRF-35835

- · Class Q Military

- Class V Space Level

- Qualified Suppliers List of Distributors (QSLD)

- Rochester is a critical supplier to DLA and meets all industry and DLA standards.

Rochester Electronics, LLC is committed to supplying products that satisfy customer expectations for quality and are equal to those originally supplied by industry manufacturers.

The original manufacturer's datasheet accompanying this document reflects the performance and specifications of the Rochester manufactured version of this device. Rochester Electronics guarantees the performance of its semiconductor products to the original OCM specifications. 'Typical' values are for reference purposes only. Certain minimum or maximum ratings may be based on product characterization, design, simulation, or sample testing.

## FOR REFERENCE ONLY

# *IM6654*

January 1992

#### 4096 Bit CMOS UV EPROM

| Features                                        |

|-------------------------------------------------|

| Organization512 x 8                             |

| • Low Power                                     |

| High Speed Access Time for IM6654-AI            |

| Single Supply Operation                         |

| UV Erasable                                     |

| Synchronous Operation for Low Power Dissipation |

electrically programmable ROM (EPROM) fabricated with Harris' advanced CMOS processing technology. In all static states this device exhibits the microwatt power dissipation typical of CMOS. Inputs and three-state outputs are TTL compatible and allow for direct interface with common system bus structures. On-chip address registers and chip select functions simplify system interfacing requirements.

The Harris IM6654 is a fully decoded 4096 bit CMOS

The IM6654 is specifically designed for program development applications where rapid turn-around for program changes is required. The device may be erased by exposing its transparent lid to ultra-violet light, and then reprogrammed.

- . Three-State Outputs and Chip Select for Easy System Expansion

#### Ordering Information

| PACKAGE     | TEMPERATURE RANGE | 5V          | 10V        |

|-------------|-------------------|-------------|------------|

| Ceramic DIP | -40°C to +85°C    | IM6654IJG   | IM6654AIJG |

|             |                   | IM6654-1IJG |            |

|             | -55°C to+125°C    | IM6654MJG   | IM6654AMJG |

Description

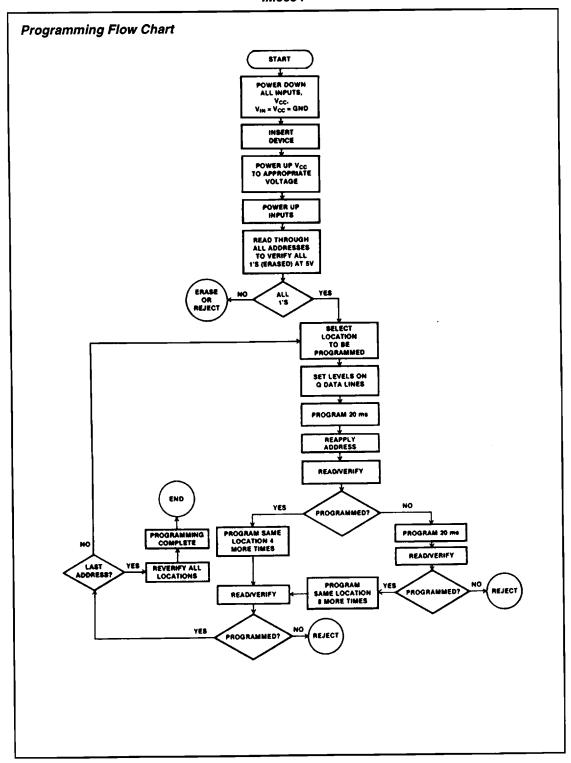

#### **Program Mode Operation**

Initially, all 4096 bits of the EPROM are in the logic one (output high) state. Selective programming of proper bit locations to "0"s is performed electrically.

In the PROGRAM mode for all EPROMs, VCC and VDD are tied together to a +5V operating supply. High logic levels at all of the appropriate chip inputs and outputs must be set at VDD -2V minimum. Low logic levels must be set at VSS +0.8V maximum. Addressing of the desired location in PROGRAM mode is done as in the READ mode. Address and data lines are set at the desired logic levels, and PROGRAM and chip select  $\overline{(S)}$  pins are set high. The address is latched by the downward edge on the strobe line ( $\overline{E}1$ )). During valid DATA IN time, the PROGRAM pin is pulsed from VDD to -40V. This pulse initiates the programming of the device to the levels set on the data outputs. Duty cycle limitations are specified from chip heat dissipation considerations. PULSE RISE AND FALL TIMES MUST NOT BE FASTER THAN 5µs.

Intelligent programmer equipment with successive READ/ PROGRAM/VERIFY sequences is recommended.

#### Programming System Characteristics

During programming the power supply should be capable of limiting peak instantaneous current to 100mA.

- 2. The programming pin is driven from VDD to -40 volts (±2V) by pulses of 20 milliseconds duration. These pulses should be applied in the sequence shown in the flow chart. Pulse rise and fall times of 10 microseconds are recommended. Note that any individual location may be programmed at any time.

- Addresses and data should be presented to the device within the recommended setup/hold time and high/low logic level margins. Both "A" (10V) and non "A" EPROMs are programmed at VCC, VDD of 5V ±5%.

- 4. Programming is to be done at room temperature.

#### Erasing Procedure

The IM6654 is erased by exposure to high intensity short-wave ultraviolet light at a wavelength of 2537Å. The recommended integrated dose (i.e., UV intensity x exposure time) is 10W sec/cm². The lamps should be used without short-wave filters, and the IM6654 to be erased should be placed about one inch away from the lamp tubes. For best results it is recommended that the device remain inactive for 5 minutes after erasure, before reprogramming.

The erasing effect of UV light is cumulative. Care should be taken to protect EPROMs from exposure to direct sunlight or fluorescent lamps radiating UV light in the 2000Å to 4000Å rance

## Specifications IM6654

## DC Characteristics for Programming Operation VCC = VDD = 5V ±5% VSS = 0V, T<sub>A</sub> = +25°C

| SYMBOL | PARAMETER                   | TEST CONDITIONS | MIN     | TYP | MAX | UNITS |

|--------|-----------------------------|-----------------|---------|-----|-----|-------|

| IPROG  | Program Pin Load Current    |                 | -       | 80  | 100 | mA    |

| VPROG  | Programming Pulse Amplitude |                 | -38     | -40 | -42 | V     |

| ICC    | VCC Current                 |                 |         | 0.1 | 5   | mA    |

| IDD    | VDD Current                 |                 |         | 40  | 100 | mA    |

| VIHA   | Address Input High Voltage  |                 | VDD-2.0 | •   | -   | ٧     |

| VILA   | Address Input Low Voltage   |                 | -       |     | 0.8 | V     |

| VIH    | Data Input High Voltage     |                 | VDD-2.0 | -   | -   | V     |

| VIL    | Data Input Low Voltage      | _               | -       | -   | 0.8 | V     |

## AC Characteristics for Programming Operation $VCC = VDD = 5V \pm 5\% VSS = 0V, T_A = +25^{\circ}C$

| SYMBOL  | PARAMETER                | TEST CONDITIONS     | MIN | ТҮР | MAX  | UNITS |

|---------|--------------------------|---------------------|-----|-----|------|-------|

| TPLPH   | Program Pulse Width      | trise = tfall = 5µs | 18  | 20  | 22   | ms    |

|         | Program Pulse Duty Cycle |                     | -   | -   | 75%  |       |

| TDVPL   | Data Setup Time          |                     | 9   | -   | -    | μs    |

| TPHDX   | Data Hold Time           |                     | 9   |     |      | μѕ    |

| TE1HE1L | Strobe Pulse Width       |                     | 150 | -   |      | ns    |

| TAVE1L  | Address Setup Time       |                     | 0   | -   |      | ns    |

| TE1LE1X | Address Hold Time        |                     | 100 |     | -    | ns    |

| TE1LQV  | Access Time              |                     | -   |     | 1000 | ns    |

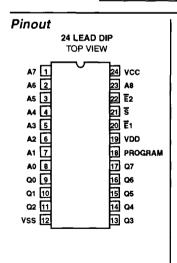

## Pin Description

| PIN         | SYMBOL    | ACTIVE LEVEL | DESCRIPTION                                                |

|-------------|-----------|--------------|------------------------------------------------------------|

| 1-8, 23     | A0-A7, A8 | •            | Address Lines                                              |

| 9-11, 13-17 | Q0-Q7     | •            | Data Out Lines                                             |

| 12          | vss       | -            | Negative Supply                                            |

| 18          | Program   | -            | Programming Pulse Input                                    |

| 19          | VDD       | -            | Chip Positive Supply, Normally Tied to VCC                 |

| 20          | Ē1        | L            | Strobe Line, Latches Both Address Lines and Chip Enable E2 |

| 21          | Š         | L            | Chip Select Line, Must be Low for Valid Data Out           |

| 22          | Ē2        | L            | Chip Enable Line, Latched by Chip Enable E1                |

| 24          | VCC       |              | Output Buffer Positive Supply                              |

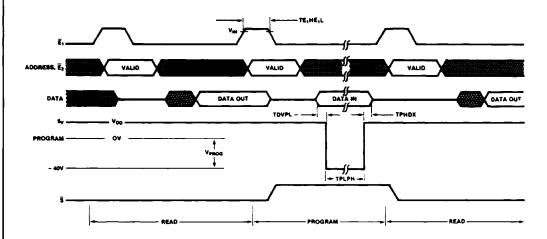

## Read and Program Cycle Timing

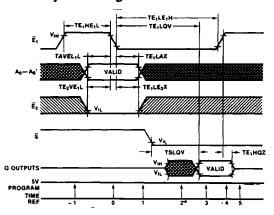

#### Read Mode Operation

In a typical READ operation address lines and chip enable \$\overline{\text{E2}}\$ are latched by the falling edge of chip enable \$\overline{\text{E1}}\$ (T=0). Valid data appears at the outputs one access time (TELQV) later, provided level-sensitive chip select line \$\overline{\text{S}}\$ is low (T=3). Data remains valid until either \$\overline{\text{E1}}\$ or \$\overline{\text{S}}\$ returns to a high level (T=4). Outputs are then forced to a high-Z state.

Address lines and  $\overline{E}2$  must be valid one setup time before (TAVEL), and one hold time after (TELAX), the falling edge of  $\overline{E}1$  starting the read cycle. Before becoming valid, Q output lines become active (T=2). The Q output lines return to a high-Z state one output disable time (TE1HQZ) after any rising edge on  $\overline{E}1$  or  $\overline{S}$ .

The program line remains high throughout the READ cycle.

Chip enable line  $\overline{E}1$  must remain high one minimum positive pulse width (TEHEL) before the next cycle can begin.

#### Read Cycle Timing

#### **FUNCTION TABLE**

|                | INPUTS    |   |   |   | OUTPUTS |                                       |

|----------------|-----------|---|---|---|---------|---------------------------------------|

| TIME REFERENCE | Ē1 Ē2 S A |   |   | A | Q       | NOTES                                 |

| -1             | Н         | х | х | х | z       | Device Inactive                       |

| 0              | 7         | L | х | ٧ | Z       | Cycle Begins; Addresses, E2 Latched   |

| 1              | L         | Х | х | х | Z       | Internal Operations Only              |

| 2              | L         | х | L | Х | A       | Outputs Active Under Control of E1, S |

| 3              | L         | х | L | х | ٧       | Outputs Valid After Access Time       |

| 4              | 5         | х | L | х | ٧       | Read Complete                         |

| 5              | н         | Х | х | Х | z       | Cycle Ends (Same as -1)               |

## Specifications IM6654

#### Absolute Maximum Ratings (IM6654 I, -11, M)

| Supply Voltages                         | Operating Temperature Range (T <sub>A</sub> ) |

|-----------------------------------------|-----------------------------------------------|

| VDD - VSS+8.0V                          | Industrial                                    |

| VCC - VSS+8.0V                          | Military55°C to +125°C                        |

| Input or Output Voltage                 |                                               |

| Storage Temperature Range65°C to +150°C |                                               |

| Lead Temperature (Soldering 10s)+300°C  |                                               |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### **DC Electrical Characteristics** $VCC = VDD = 5V \pm 10\% VSS = 0V$ , $T_A = Operating Temperature Range$

| SYMBOL |                              |                 | IM6654 I  |      |       |

|--------|------------------------------|-----------------|-----------|------|-------|

|        | PARAMETER                    | TEST CONDITIONS | MIN       | MAX  | UNITS |

| VIH    | Logical "1" Input Voltage    | Ē1, Š           | VDD - 2.0 |      | ٧     |

|        |                              | Address Pins    | 2.7       | •    | ٧     |

| VIL    | Logical "0" Input Voltage    | -               |           | 0.8  | ٧     |

| 11     | Input Leakage                | GND ≤ VIN ≤ VDD | -1.0      | 1.0  | μА    |

| VOH    | Logical "1" Output Voltage   | IOH = -0.2mA    | 2.4       | •    | ٧     |

| VOL    | Logical "0" Output Voltage   | IOL = 2.0mA     | -         | 0.45 | ٧     |

| IOLK   | Output Leakage               | GND ≤ VO ≤ VCC  | -1.0      | 1.0  | μΑ    |

| ISTBY  | Standby Supply Current       | VIN = VDD       | -         | 100  | μА    |

| ICC    | Standby Supply Current       | VIN = VDD       |           | 40   | μА    |

| IDD    | Operating Supply Current (1) | f = 1MHz        |           | 6.0  | mA    |

| CI     | Input Capacitance            | Note 1          |           | 7.0  | pF    |

| со     | Output Capacitance           | Note 1          |           | 10.0 | рF    |

NOTE: 1. For design reference only, not 100% tested.

#### AC Electrical Characteristics VCC = VDD = 5V ±10% VSS = 0V, CL = 50pF, T<sub>A</sub> = Operating Temperature Range

|         |                           | IM6654 -11 |     | IM6654 I |     | IM6654 M |     |       |  |

|---------|---------------------------|------------|-----|----------|-----|----------|-----|-------|--|

| SYMBOL  | PARAMETER                 | MIN        | MAX | MIN      | MAX | MIN      | MAX | UNITS |  |

| TE1LQV  | Access Time From E1       | -          | 450 | •        | 550 | -        | 600 | лs    |  |

| TSLQV   | Output Enable Time        | -          | 110 |          | 140 |          | 150 | ns    |  |

| TE1HQZ  | Output Disable Time       | -          | 110 |          | 140 |          | 150 | ns    |  |

| TE1HE1L | E1 Pulse Width (Positive) | 130        |     | 150      | -   | 150      | -   | ns    |  |

| TE1LE1H | E1 Pulse Width (Negative) | 450        | -   | 550      | -   | 600      |     | ns    |  |

| TAVE1L  | Address Setup Time        | 0          | -   | 0        | -   | 0        |     | ns    |  |

| TE1LAX  | Address Hold Time         | 80         | •   | 100      |     | 100      | -   | ns    |  |

| TE2VE1L | Chip Enable Setup Time    | 0          |     | 0        | -   | 0        |     | ns    |  |

| TE1LE2X | Chip Enable Hold Time     | 80         | -   | 100      |     | 100      | -   | ns    |  |

## Specifications IM6654

#### Absolute Maximum Ratings (IM6654AI, AM)

| rature Range (T <sub>A</sub> ) -40°C to +85°C55°C to +125°C |

|-------------------------------------------------------------|

|                                                             |

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

## DC Electrical Characteristics VCC = VDD = 4.5V to 10.5V VSS = 0V, T<sub>A</sub> = Operating Temperature Range

| _      |                              |                   | IM6654     |          |       |

|--------|------------------------------|-------------------|------------|----------|-------|

| SYMBOL | PARAMETER                    | TEST CONDITIONS   | MIN        | MAX      | UNITS |

| VIH    | Logical "1" Input Voltage    | Ē1, S             | VDD - 2.0  | •        | V     |

|        |                              | Address Pins      | VDD - 2.0  | •        | ٧     |

| VIL    | Logical "0" Input Voltage    |                   | -          | 0.8      | >     |

| 11     | Input Leakage                | GND ≤ VIN ≤ VDD   | -1.0       | 1.0      | μА    |

| VOH    | Logical *1* Output Voltage   | IOUT = 0 (Note 1) | VCC - 0.01 | •        | ٧     |

| VOL    | Logical "0" Output Voltage   | IOUT = 0 (Note 1) | •          | VSS+0.01 | ٧     |

| IOLK   | Output Leakage               | VSS ≤ VO ≤ VCC    | -1.0       | 1.0      | μА    |

| ISTBY  | Standby Supply Current       | VIN = VDD         | -          | 100      | μА    |

| ICC    | Standby Supply Current       | VIN = VDD         | -          | 40       | μА    |

| IDD    | Operating Supply Current (1) | f = 1MHz          |            | 12       | mA    |

| CI     | Input Capacitance            | Note 1            | -          | 7.0      | pF    |

| со     | Output Capacitance           | Note 1            |            | 10.0     | pF    |

NOTE: 1. For design reference only, not 100% tested.

## AC Electrical Characteristics VCC = VDD = 5V ±10% VSS = 0V, CL = 50pF, T<sub>A</sub> = Operating Temperature Range

| SYMBOL  |                           | IM66 | 54 AI | IM66 |     |       |

|---------|---------------------------|------|-------|------|-----|-------|

|         | PARAMETER                 | MIN  | МАХ   | MIN  | MAX | UNITS |

| TE1LQV  | Access Time From E1       |      | 300   | •    | 350 | ns    |

| TSLQV   | Output Enable Time        |      | 60    | · ·  | 70  | ns    |

| TE1HQZ  | Output Disable Time       |      | 60    | · ·  | 70  | ns    |

| TE1HE1L | E1 Pulse Width (Positive) | 125  | -     | 125  |     | ns    |

| TE1LE1H | E1 Pulse Width (Negative) | 300  | -     | 350  | -   | ns    |

| TAVE1L  | Address Setup Time        | 0    |       | 0    | -   | ns    |

| TE1LAX  | Address Hold Time         | 60   | -     | 60   |     | ns    |

| TE2VE1L | Chip Enable Setup Time    | 0    | -     | 0    | -   | ns    |

| TE1LE2X | Chip Enable Hold Time     | 60   | -     | 60   | -   | ns    |