##

### Cost-Saving Multichemistry Battery-Charger System

#### General Description

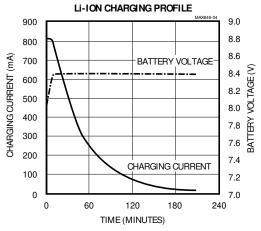

The MAX846A is a cost-saving multichemistry battery-charger system that comes in a space-saving 16-pin QSOP. This integrated system allows different battery chemistries (Li-lon, NiMH or NiCd cells) to be charged using one circuit.

In its simplest application, the MAX846A is a standalone, current-limited float voltage source that charges Li-lon cells. It can also be paired up with a low-cost microcontroller ( $\mu$ C) to build a universal charger capable of charging Li-lon, NiMH, and NiCd cells.

An internal 0.5%-accurate reference allows safe charging of Li-lon cells that require tight voltage accuracy. The voltage- and current-regulation loops used to control a low-cost external PNP transistor (or P-channel MOSFET) are independent of each other, allowing more flexibility in the charging algorithms.

The MAX846A has a built-in 1%, 3.3V, 20mA linear regulator capable of powering the  $\mu$ C and providing a reference for the  $\mu$ C's analog-to-digital converters. An on-board reset notifies the controller upon any unexpected loss of power. The  $\mu$ C can be inexpensive, since its only functions are to monitor the voltage and current and to change the charging algorithms.

#### **Applications**

Li-Ion Battery Packs

**Desktop Cradle Chargers**

Li-Ion/NiMH/NiCd Multichemistry Battery

Chargers

Cellular Phones

**Notebook Computers**

Hand-Held Instruments

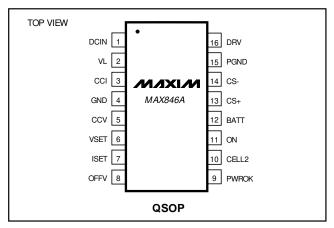

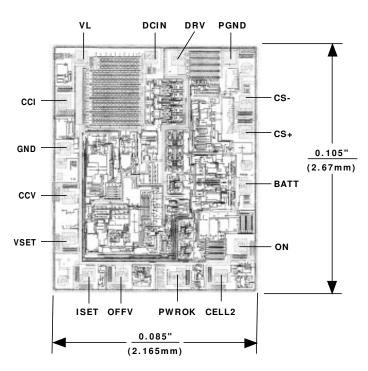

#### Pin Configuration

#### **Features**

- **♦** Multichemistry Charger System (Li-Ion, NiMH, NiCd)

- **♦ Independent Voltage and Current Loops**

- ♦ ±0.5% Internal Reference for Li-Ion Cells

- **♦ Lowers Cost:**

- -Stands Alone or Uses Low-Cost µC

- -Built-In 1% Linear Regulator Powers µC

- -Linear Regulator Provides Reference to μC ADCs

- -Built-In µC Reset

- —Controls Low-Cost External PNP Transistor or P-Channel MOSFET

- **♦** Space-Saving 16-Pin QSOP

- **♦** Charging-Current-Monitor Output

- ♦ <1µA Battery Drain when Off

#### Ordering Information

| PART       | TEMP. RANGE    | PIN-PACKAGE |

|------------|----------------|-------------|

| MAX846AC/D | 0°C to +70°C   | Dice*       |

| MAX846AEEE | -40°C to +85°C | 16 QSOP     |

<sup>\*</sup>Dice are tested at  $T_A = +25$ °C only. Contact factory for details.

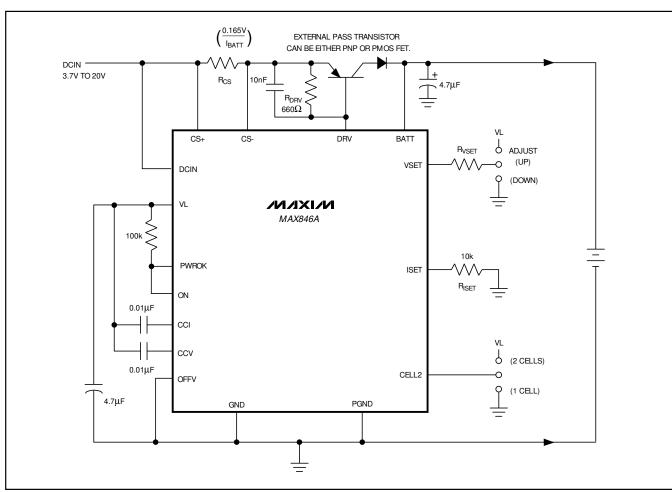

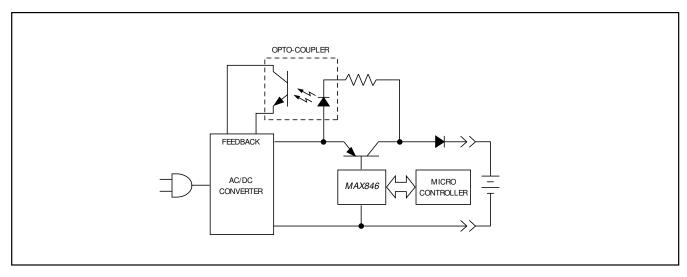

#### Typical Operating Circuit

#### **ABSOLUTE MAXIMUM RATINGS**

| DCIN, DRV, CS+, CS-, BATT to GND   |                 |

|------------------------------------|-----------------|

| VL to GND                          |                 |

| IPWROK                             | 10mA            |

| PWROK, ISET, CCI, CCV, OFFV, VSET, |                 |

| CELL2, ON to GND                   | 0.3V, VL + 0.3V |

| CS+ to CS                          | ±0.3V           |

| VL Short to GND                    | Continuous      |

| I <sub>DRV</sub>                   | 100mA           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| QSOP (derate 8.3mW/°C above +70°C)                    | 667mW          |

| Operating Temperature Range                           |                |

| MAX846AEEE                                            | 40°C to +85°C  |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +160°C |

| Lead Temperature (soldering, 10sec)                   | +300°C         |

| , , , , , , , , , , , , , , , , , , , ,               |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DCIN}=10V,\,ON=VL,\,I_{VL}=I_{VSET}=0mA,\,V_{CS^-}=V_{CS+}=10V,\,V_{BATT}=4.5V,\,V_{OFFV}=V_{CELL2}=0V,\,T_A=0^{\circ}C\,\,to\,+85^{\circ}C,\,unless\,otherwise\,noted.\,Typical\,values\,are\,at\,T_A=+25^{\circ}C.)$

| PARAMETER                          | CONDITIONS                                                                      | MIN   | TYP   | MAX   | UNITS |

|------------------------------------|---------------------------------------------------------------------------------|-------|-------|-------|-------|

| VL REGULATOR                       |                                                                                 |       |       |       |       |

| DCIN Supply Current                | $V_{DCIN} = 20V$ , $I_{DRV} = I_{VL} = 0$ mA                                    |       |       | 5     | mA    |

| Operating Range                    |                                                                                 | 3.7   |       | 20.0  | V     |

| Output Voltage                     | 0mA < I <sub>VL</sub> < 20mA, 3.7V < V <sub>DCIN</sub> < 20V                    | 3.267 | 3.305 | 3.333 | V     |

| Short-Circuit Current Limit        | VL = GND                                                                        |       | 50    |       | mA    |

| PWROK Trip Level                   | Rising VL edge, 2% hysteresis                                                   | 2.9   | 3.0   | 3.1   | V     |

| VL Undervoltage-Lockout Level      |                                                                                 | 2.5   |       | 2.9   | V     |

| REFERENCE                          | ·                                                                               |       |       |       |       |

| Output Voltage                     | Measured at VSET, I <sub>VSET</sub> = 0mA, V <sub>ON</sub> = 0V                 | -0.5% | 1.650 | +0.5% | V     |

| Output Resistance                  |                                                                                 | -2%   | 20    | +2%   | kΩ    |

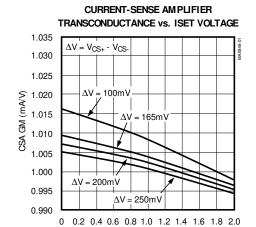

| CURRENT-SENSE AMPLIFIER            |                                                                                 |       |       |       |       |

| Transconductance                   | V <sub>ISET</sub> = 1.7V, V <sub>CS+</sub> - V <sub>CS-</sub> = 165mV           | 0.95  | 1     | 1.05  | mA/V  |

| Output Offset Current              | $V_{CS+} = 4V$                                                                  |       |       | 3     | μΑ    |

| Input Common-Mode Range            | Measured at V <sub>CS</sub> -, V <sub>CS+</sub> - V <sub>CS-</sub> = 165mV      | 2.1   |       | 20.0  | V     |

| Maximum Differential Input Voltage | V <sub>CS</sub> - = V <sub>ISET</sub> = 2.1V,<br>CSA transconductance > 0.9mA/V | 225   |       |       | mV    |

| CS- Lockout Voltage                | When V <sub>CS</sub> is less than this voltage, DRV is disabled.                | 1.9   |       | 2.1   | V     |

| CS+, CS- Input Current             | V <sub>CS+</sub> = 20V, V <sub>CS+</sub> -V <sub>CS-</sub> = 165mV              |       |       | 250   | μΑ    |

| CS+, CS- Off Input Current         | DCIN = VL = ON = GND                                                            |       | 0.01  | 10    | μΑ    |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DCIN}=10V,ON=VL,I_{VL}=I_{VSET}=0mA,V_{CS^-}=V_{CS+}=10V,V_{BATT}=4.5V,V_{OFFV}=V_{CELL2}=0V,T_A=0^{\circ}C~to~+85^{\circ}C,unless~otherwise~noted.$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                    | CONDITIONS                                                                                             | MIN    | TYP   | MAX     | UNITS |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------|--------|-------|---------|-------|--|--|

| VOLTAGE LOOP                 |                                                                                                        |        |       |         |       |  |  |

| Voltage-Loop Set Point       | V <sub>VSET</sub> = 1.650V, V <sub>CELL2</sub> = 0V, I <sub>DRV</sub> = 1mA,<br>V <sub>DRV</sub> = 10V | -0.25% | 4.2   | +0.25%  | V     |  |  |

| voltage-Loop Set Pollit      | V <sub>VSET</sub> = 1.650V, V <sub>CELL2</sub> = VL, I <sub>DRV</sub> = 1mA,<br>V <sub>DRV</sub> = 10V | -0.25% | 8.4   | + 0.25% | V     |  |  |

| VSET Common-Mode Input Range |                                                                                                        | 1.25   |       | 2.0     | V     |  |  |

| CCV Output Impedance         |                                                                                                        |        | 150   |         | kΩ    |  |  |

| Voltage-Loop Load Regulation | 1mA < I <sub>DRV</sub> < 5mA                                                                           |        | 0.05  |         | %     |  |  |

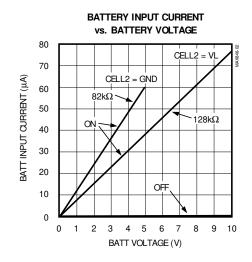

| BATT Input Current           | V <sub>BATT</sub> = 10V, CELL2 = GND or VL                                                             |        |       | 225     | μΑ    |  |  |

| BATT Off Input Current       | VBATT = 10V, ON = GND, CELL2 = GND or VL                                                               |        | 0.01  | 1       | μΑ    |  |  |

| CURRENT LOOP                 | CURRENT LOOP                                                                                           |        |       |         |       |  |  |

| Current-Loop Set Point       | $I_{DRV} = 5mA$ , $V_{DRV} = 10V$                                                                      | 1.634  | 1.650 | 1.666   | V     |  |  |

| CA Voltage Gain              |                                                                                                        |        | 5     |         | V/V   |  |  |

| CCI Output Impedance         |                                                                                                        |        | 50    |         | kΩ    |  |  |

| Overcurrent Trip Level       | When VISET exceeds this voltage, DRV current is disabled.                                              | 1.90   |       | 2.1     | V     |  |  |

| DRIVER                       |                                                                                                        |        |       |         |       |  |  |

| DRV Sink Current             | $V_{DRV} = 3V$                                                                                         | 20     |       |         | mA    |  |  |

| DRV Off Current              | $V_{DRV} = 20V$ , $V_{ON} = 0V$                                                                        |        | 0.1   | 100     | μΑ    |  |  |

| LOGIC INPUTS AND OUTPUTS     |                                                                                                        |        |       |         |       |  |  |

| Input High Level             | CELL2, ON, OFFV                                                                                        | 2.4    |       | VL      | V     |  |  |

| Input Low Level              | CELL2, ON, OFFV                                                                                        | 0      |       | 0.8     | V     |  |  |

| Input Current                | CELL2, ON, OFFV                                                                                        |        | 0.01  | 1       | μΑ    |  |  |

| PWROK Output Low Level       | IPWROK = 1mA, VDCIN = VVL = 2.5V                                                                       |        |       | 0.4     | V     |  |  |

| PWROK Output High Leakage    | V <sub>PWROK</sub> = 3.3V                                                                              |        | 0.01  | 1       | μΑ    |  |  |

#### **ELECTRICAL CHARACTERISTICS (Note 1)**

$(V_{DCIN} = 10V, ON = VL, I_{VL} = I_{VSET} = 0mA, V_{CS^-} = V_{CS+} = 10V, V_{BATT} = 4.5V, V_{OFFV} = V_{CELL2} = 0V, T_A = -40^{\circ}C$  to +85°C, unless otherwise noted.)

| PARAMETER                     | CONDITIONS                                                                                             | MIN    | TYP   | MAX     | UNITS |

|-------------------------------|--------------------------------------------------------------------------------------------------------|--------|-------|---------|-------|

| VL REGULATOR                  |                                                                                                        |        |       |         |       |

| DCIN Supply Current           | V <sub>DCIN</sub> = 20V, I <sub>DRV</sub> = I <sub>VL</sub> = 0mA                                      |        |       | 5       | mA    |

| Output Voltage                | 0mA < I <sub>VL</sub> < 20mA, 3.7V < V <sub>DCIN</sub> < 20V                                           | 3.259  |       | 3.341   | V     |

| PWROK Trip Level              | Rising VL edge, 2% hysteresis                                                                          | 2.9    |       | 3.1     | V     |

| VL Undervoltage-Lockout Level |                                                                                                        | 2.5    |       | 3.0     | V     |

| REFERENCE                     |                                                                                                        |        |       |         |       |

| Output Voltage                | Measured at VSET, I <sub>VSET</sub> = 0mA, V <sub>ON</sub> = 0V                                        | -0.7%  | 1.650 | +0.7%   | V     |

| Output Resistance             |                                                                                                        | -2%    | 20    | +2%     | kΩ    |

| CURRENT-SENSE AMPLIFIER       |                                                                                                        |        |       |         |       |

| Transconductance              | V <sub>ISET</sub> = 1.7V, V <sub>CS+</sub> - V <sub>CS-</sub> = 165mV                                  | 0.93   |       | 1.07    | mA/V  |

| Output Offset Current         | $V_{CS+} = 4V$                                                                                         |        |       | 5       | μΑ    |

| CS+, CS- Off Input Current    | $V_{ON} = 0V$ , $V_{CS+} = V_{CS-} = 10V$                                                              |        |       | 10      | μΑ    |

| VOLTAGE LOOP                  |                                                                                                        |        |       |         |       |

| Voltage Lean Set Daint        | V <sub>V</sub> SET = 1.650V, V <sub>CELL2</sub> = 0V, I <sub>DRV</sub> = 1mA, V <sub>DRV</sub> = 10V   | -0.35% | 4.2   | +0.35%  | V     |

| Voltage-Loop Set Point        | V <sub>VSET</sub> = 1.650V, V <sub>CELL2</sub> = VL, I <sub>DRV</sub> = 1mA,<br>V <sub>DRV</sub> = 10V | -0.35% | 8.4   | + 0.35% | V     |

| BATT Off Input Current        | V <sub>BATT</sub> = 10V, ON = GND, CELL2 = GND or VL                                                   |        |       | 1       | μΑ    |

| CURRENT LOOP                  |                                                                                                        |        |       |         |       |

| Current-Loop Set Point        | $I_{DRV} = 5mA$ , $V_{DRV} = 10V$                                                                      | 1.625  |       | 1.675   | V     |

| Overcurrent Trip Level        | When V <sub>ISET</sub> exceeds this voltage, DRV current is disabled.                                  | 1.86   |       | 2.14    | V     |

| DRIVER                        |                                                                                                        |        |       |         |       |

| DRV Sink Current              | $V_{DRV} = 3V$                                                                                         | 20     |       |         | mA    |

| DRV Off Current               | V <sub>DRV</sub> = 20V, ON = GND                                                                       |        |       | 100     | μΑ    |

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

#### Typical Operating Characteristics

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

ISET VOLTAGE (V)

Pin Description

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | DCIN  | Supply Input from External DC Source. 3.7V ≤ V <sub>DCIN</sub> ≤ 20V.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2   | VL    | 3.3V, 20mA, 1% Linear-Regulator Output. VL powers the system μC and other components. Bypass to GND with a 4.7μF tantalum or ceramic capacitor.                                                                                                                                                                                                                                                                                                                                   |

| 3   | CCI   | Current-Regulation-Loop Compensation Pin. Connect a compensation capacitor (typically 10nF) from CCI to VL.                                                                                                                                                                                                                                                                                                                                                                       |

| 4   | GND   | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 5   | CCV   | Voltage-Regulation-Loop Compensation Pin. Connect a compensation capacitor (typically 10nF) from CCV to VL.                                                                                                                                                                                                                                                                                                                                                                       |

| 6   | VSET  | Float-Voltage Reference-Adjust Input. Leave VSET open for a 4.2V default. See the <i>Applications Information</i> section for adjustment information.                                                                                                                                                                                                                                                                                                                             |

| 7   | ISET  | Current-Set Input/Current-Monitor Output. ISET sets the current-regulation point. Connect a resistor from ISET to GND to monitor the charging current. ISET voltage is regulated at 1.65V by the current-regulation loop. To adjust the current-regulation point, either modify the resistance from ISET to ground or connect a fixed resistor and adjust the voltage on the other side of the resistor (Figure 5). The transconductance of the current-sense amplifier is 1mA/V. |

| 8   | OFFV  | Logic Input that disables the voltage-regulation loop. Set OFFV high for NiCd or NiMH batteries.                                                                                                                                                                                                                                                                                                                                                                                  |

| 9   | PWROK | Open-Drain, Power-Good Output to $\mu$ C. PWROK is low when VL is less than 3V. The reset timeout period can be set externally using an RC circuit (Figure 3).                                                                                                                                                                                                                                                                                                                    |

| 10  | CELL2 | Digital Input. CELL2 programs the number of Li-Ion cells to be charged. A high level equals two cells; a low level equals one cell.                                                                                                                                                                                                                                                                                                                                               |

| 11  | ON    | Charger ON/OFF Input. When low, the driver section is turned off and IBATT <1µA. The VL regulator is always active.                                                                                                                                                                                                                                                                                                                                                               |

| 12  | BATT  | Battery Input. Connect BATT to positive battery terminal.                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 13  | CS+   | Current-Sense Amplifier High-Side Input. Connect CS+ to the sense resistor's power-source side. The sense resistor may be placed on either side of the pass transistor.                                                                                                                                                                                                                                                                                                           |

| 14  | CS-   | Current-Sense Amplifier Low-Side Input. Connect CS- to the sense resistor's battery side.                                                                                                                                                                                                                                                                                                                                                                                         |

| 15  | PGND  | Power Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16  | DRV   | External Pass Transistor (P-channel MOSFET or PNP) Base/Gate Drive Output. DRV sinks current only.                                                                                                                                                                                                                                                                                                                                                                                |

#### Detailed Description

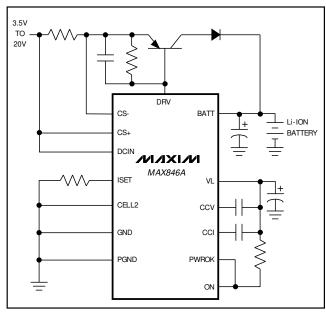

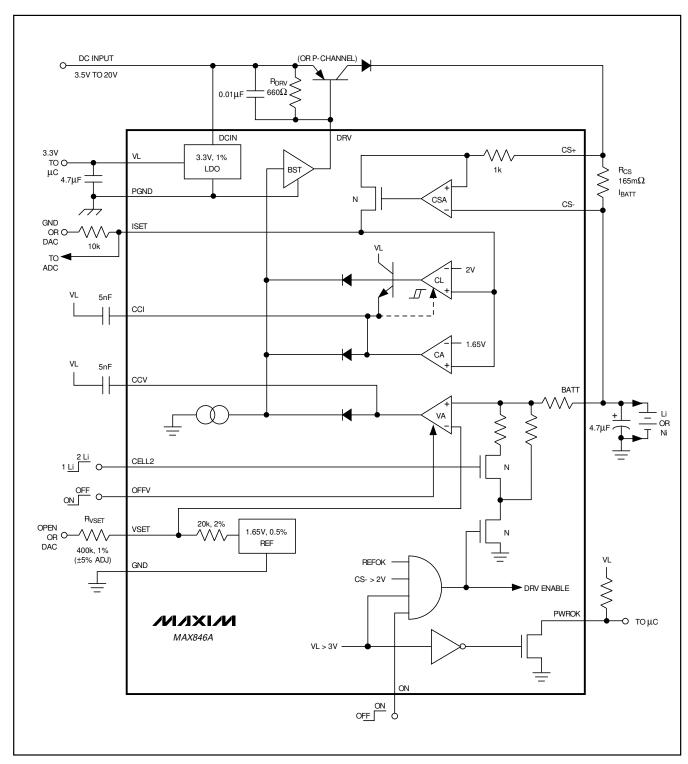

The MAX846A battery-charging controller combines three functional blocks: a 3.3V precision, low-dropout linear regulator (LDO), a precision voltage reference, and a voltage/current regulator (Figure 1).

#### Linear Regulator

The LDO regulator output voltage (VL) is two times the internal reference voltage; therefore, the reference and LDO track. VL delivers up to 20mA to an external load and is short-circuit protected. The power-good output (PWROK) provides microcontroller ( $\mu$ C) reset and charge-current inhibition.

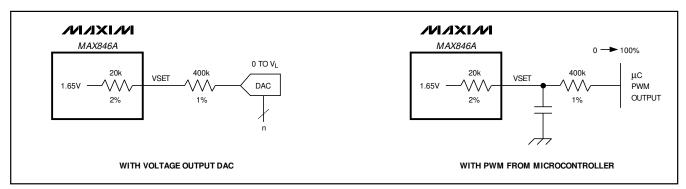

#### Voltage Reference

The precision internal reference provides a voltage to accurately set the float voltage for lithium-ion (Li-lon) battery charging. The reference output connects in series with an internal, 2%-accurate,  $20k\Omega$  resistor. This allows the float voltage to be adjusted using one external 1% resistor (RVSET) to form a voltage divider (Figure 4). The float-voltage accuracy is important for battery life and to ensure full capacity in Li-lon batteries. Table 1 shows the accuracies attainable using the MAX846A.

#### Voltage/Current Regulator

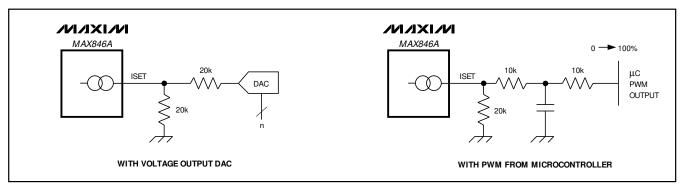

The voltage/current regulator consists of a precision attenuator, voltage loop, current-sense amplifier, and current loop. The attenuator can be pin programmed to set the regulation voltage for one or two Li-lon cells (4.2V and 8.4V, respectively). The current-sense amplifier is configured to sense the battery current on the high side. It is, in essence, a transconductance amplifier converting the voltage across an external sense resistor (R<sub>CS</sub>) to a current, and applying this current to an external load resistor (RISET). Set the charge current by selecting RCs and RISET. The charge current can also be adjusted by varying the voltage at the low side of RISET or by summing/subtracting current from the ISET node (Figure 5). The voltage and current loops are individually compensated using external capacitors at CCV and CCI, respectively. The outputs of these two loops are OR'ed together and drive an open-drain, internal N-channel MOSFET transistor sinking current to ground. An external P-channel MOSFET or PNP transistor pass element completes the loop.

#### Stability

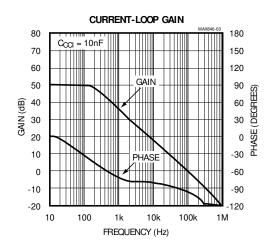

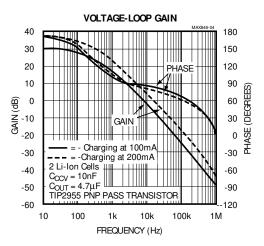

The *Typical Operating Characteristics* show the loop gains for the current loop and voltage loop. The dominant pole for each loop is set by the compensation capacitor connected to each capacitive compensation pin (CCI, CCV). The DC loop gains are about 50dB for the current loop and about 33dB for the voltage loop, for a battery impedance of  $250m\Omega$ .

The CCI output impedance ( $50k\Omega$ ) and the CCI capacitor determine the current-loop dominant pole. In Figure 2, the recommended CCCV is 10nF, which places a dominant pole at 300Hz. There is a high-frequency pole, due to the external PNP, at approximately fT/ß. This pole frequency (on the order of a few hundred kilohertz) will vary with the type of PNP used. Connect a 10nF capacitor between the base and emitter of the

PNP to prevent self-oscillation (due to the high-impedance base drive).

Similarly, the CCV output impedance (150k $\Omega$ ) and the CCV capacitor set the voltage-loop dominant pole. In Figure 2, the compensation capacitance is 10nF, which places a dominant pole at 200Hz.

The battery impedance directly affects the voltage-loop DC and high-frequency gain. At DC, the loop gain is proportional to the battery resistance. At higher frequencies, the AC impedance of the battery and its connections introduces an additional high-frequency zero. A 4.7µF output capacitor in parallel with the battery, mounted close to BATT, minimizes the impact of this impedance. The effect of the battery impedance on DC gain is noticeable in the Voltage-Loop-Gain graph (see Typical Operating Characteristics). The solid line represents voltage-loop gain versus frequency for a fully charged battery, when the battery energy level is high and the ESR is low. The charging current is 100mA. The dashed line shows the loop gain with a 200mA charging current, a lower amount of stored energy in the battery, and a higher battery ESR.

#### \_Applications Information

#### Stand-Alone Li-Ion Charger

Figure 2 shows the stand-alone configuration of the MAX846A. Select the external components and pin configurations as follows:

- Program the number of cells: Connect CELL2 to GND for one-cell operation, or to VL for two-cell operation.

- Program the float voltage: Connect a 1% resistor from VSET to GND to adjust the float voltage down, or to VL to adjust it up. If VSET is unconnected, the float voltage will be 4.2V per cell. Let the desired float voltage per cell be VF, and calculate the resistor value as follows:

Table 1. Float-Voltage Accuracy

| ERROR SOURCE                                                                                                                                                                                                                      | ERROR  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Internal-reference accuracy                                                                                                                                                                                                       | ±0.5%  |

| VSET error due to external divider. Calculated from a 2% internal $20k\Omega$ resistor tolerance and a 1% external R <sub>VSET</sub> resistor tolerance. The total error is 3% x (adjustment). Assume max adjustment range of 5%. | ±0.15% |

| VSET amplifier and divider accuracy                                                                                                                                                                                               | ±0.25% |

| TOTAL                                                                                                                                                                                                                             | ±0.9%  |

Figure 1. Functional Diagram

Figure 2. Stand-Alone Li-Ion Charger

$$R_{VSET} = 20k\Omega \left( \frac{4.2}{1.65} V_X - V_F \over V_F - 4.2} \right)$$

where VX is either GND or VL, and VF is the per-cell float voltage. In the circuit of Figure 1, RVSET is  $400k\Omega.$  RVSET and the internal  $20k\Omega$  resistor form a divider, resulting in an adjustment range of approximately  $\pm 5\%.$

The current-regulation loop attempts to maintain the voltage on ISET at 1.65V. Selecting resistor RISET determines the reflected voltage required at the current-sense amplifier input.

· Calculate Rcs and RiseT as follows:

RCS = VCS / IBATT

RISET (in  $k\Omega$ ) = 1.65V / VCS

where the recommended value for Vcs is 165mV.

Connect ON to PWROK to prevent the charge current from turning on until the voltages have settled.

Minimize power dissipation in the external pass transistor. Power dissipation can be controlled by setting the DCIN input supply as low as possible, or by making VDCIN track the battery voltage.

#### Microprocessor-Controlled Multichemistry Operation

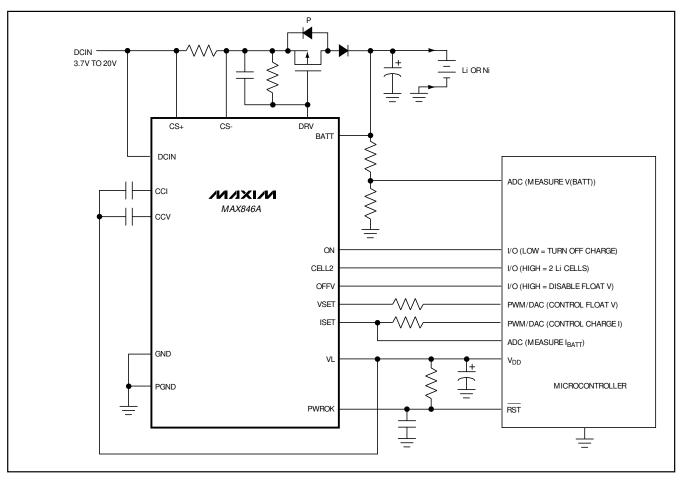

The MAX846A is highly adjustable, allowing for simple interfacing with a low-cost  $\mu C$  to charge Ni-based and Li-lon batteries using one application circuit (Figure 3).

Figure 3. Desktop Multichemistry Charger Concept

Component selection is similar to that of stand-alone operation. By using DACs or  $\mu$ C PWM outputs, the float voltage and charging current can be adjusted by the  $\mu$ C. When a Ni-based battery is being charged, disable the float-voltage regulation using the OFFV input. The  $\mu$ C can also monitor the charge current through the battery by reading the ISET output's voltage using its ADC. Similarly, the battery voltage can be measured using a voltage divider from the battery.

Note that the  $\mu$ C only needs to configure the system for correct voltage and current levels for the battery being charged, and for Ni-based batteries to detect end-of-charge and adjust the current level to trickle. The controller is not burdened with the regulation task.

Float-voltage accuracy is important for battery life and for reaching full capacity for Li-lon batteries. Table 1 shows the accuracy attainable using the MAX846A.

For best float-voltage accuracy, set the DRV current to 1mA ( $R_{DRV}$  = 660 $\Omega$  for a PNP pass transistor).

#### High-Power Multichemistry Offline Charger

The circuit in Figure 6 minimizes power dissipation in the pass transistor by providing optical feedback to the input power source. The offline AC/DC converter maintains 1.2V across the PNP. This allows much higher charging currents than can be used with conventional power sources.

Figure 4. VSET Adjustment Methods

Figure 5. ISET Adjustment Methods

Figure 6. Low-Cost Desktop Multichemistry Charger Concept

#### Chip Topography

SUBSTRATE CONNECTED TO GND TRANSISTOR COUNT: 349

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.