SLLS007D - JULY 1985 - REVISED APRIL 1998

- Meets or Exceeds the Requirements of ANSI Standard EIA/TIA-422-B and ITU Recommendation V.11

- Designed to Operate up to 20 Mbaud

- 3-State TTL Compatible

- Single 5-V Supply Operation

- High Output Impedance in Power-Off Condition

- Complementary Output-Enable Inputs

- Improved Replacement for the AM26LS31

#### D OR N PACKAGE (TOP VIEW) 16 🛮 V<sub>CC</sub> 1Y 🛮 2 15 **1** 4A 1Z**∏**3 14 **1** 4Y G **∏**4 13 **∏** 4Z 2Z 🛮 5 12 🛮 🗔 2Y [ 6 11 3Z 2A **∏** 7 10 3Y 9 **1** 3A GND [18

#### description

The four differential line drivers are designed for data transmission over twisted-pair or parallel-wire transmission lines. They meet the requirements of ANSI Standard EIA/TIA-422-B and ITU Recommendations V.11 and are compatible with 3-state TTL circuits. Advanced low-power Schottky technology provides high speed without the usual power penalties. Standby supply current is typically only 26 mA, while typical propagation delay time is less than 10 ns.

High-impedance inputs maintain low input currents, less than 1  $\mu$ A for a high level and less than 100  $\mu$ A for a low level. Complementary output-enable inputs (G and  $\overline{G}$ ) allow these devices to be enabled at either a high input level or low input level. The SN75ALS192 is capable of data rates in excess of 20 Mbit/s and is designed to operate with the SN75ALS193 quadruple line receiver.

The SN75ALS192 is characterized for operation from 0°C to 70°C.

# FUNCTION TABLE (each driver)

| <u></u> |      |      |         |   |  |  |  |  |

|---------|------|------|---------|---|--|--|--|--|

| INPUT   | ENAI | BLES | OUTPUTS |   |  |  |  |  |

| Α       | G    | G    | Y       | Z |  |  |  |  |

| Н       | Н    | Х    | Н       | L |  |  |  |  |

| L       | Н    | X    | L       | Н |  |  |  |  |

| Н       | Х    | L    | Н       | L |  |  |  |  |

| L       | Х    | L    | L       | Н |  |  |  |  |

| Х       | L    | Н    | Z       | Z |  |  |  |  |

H = high level, L = low level, X = irrelevant,

Z = high impedance (off)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

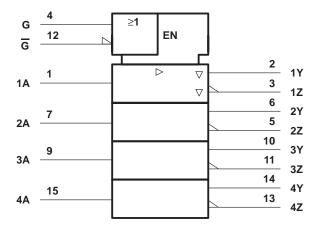

# logic symbol†

<sup>&</sup>lt;sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984 and IEC Publication 617-12.

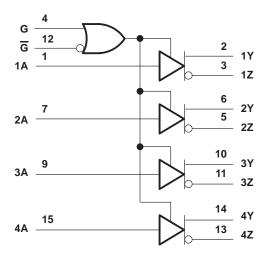

# logic diagram (positive logic)

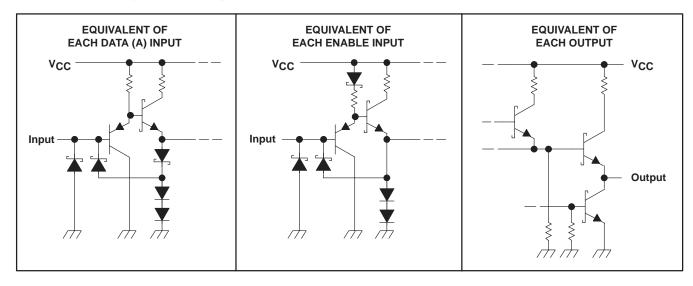

# schematics of inputs and outputs

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage, V <sub>CC</sub> (see Note 1)                 | 7 V                          |

|--------------------------------------------------------------|------------------------------|

| Input voltage, V <sub>I</sub>                                |                              |

| Off-state output voltage                                     | 6 V                          |

| Continuous total dissipation                                 | See Dissipation Rating Table |

| Storage temperature range, T <sub>stg</sub>                  |                              |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds | 260°C                        |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values except differential output voltage, VOD, are with respect to network ground terminal.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_A \le 25^{\circ}C$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 70°C<br>POWER RATING | T <sub>A</sub> = 125°C<br>POWER RATING |  |

|---------|------------------------------------|------------------------------------------------|---------------------------------------|----------------------------------------|--|

| D       | 950 mW                             | 7.6 mW/°C                                      | 608 mW                                | N/A                                    |  |

| N       | 1150 mW                            | 9.2 mW/°C                                      | 736 mW                                | N/A                                    |  |

#### recommended operating conditions

|                                                | MIN  | NOM | MAX  | UNIT |

|------------------------------------------------|------|-----|------|------|

| Supply voltage, V <sub>CC</sub>                | 4.75 | 5   | 5.25 | V    |

| High level input voltage, VIH                  | 2    |     |      | V    |

| Low-level input voltage, V <sub>IL</sub>       |      |     | 0.8  | V    |

| High-level output current, IOH                 |      |     | -20  | mA   |

| Low-level output current, IOL                  |      |     | 20   | mA   |

| Operating free-air temperature, T <sub>A</sub> | 0    |     | 70   | °C   |

SLLS007D - JULY 1985 - REVISED APRIL 1998

# electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER         |                                                     | TEST CONDITIONS†        |                           | MIN                    | TYP‡ | MAX  | UNIT |

|-------------------|-----------------------------------------------------|-------------------------|---------------------------|------------------------|------|------|------|

| VIK               | Input clamp voltage                                 | $V_{CC} = MIN,$         | I <sub>I</sub> = -18 mA   |                        |      | -1.5 | V    |

| Vон               | High-level output voltage                           | V <sub>CC</sub> = MIN,  | $I_{OH} = -20 \text{ mA}$ | 2.5                    |      |      | V    |

| VOL               | Low-level output voltage                            | V <sub>CC</sub> = MIN,  | $I_{OL} = 20 \text{ mA}$  |                        |      | 0.5  | V    |

| Vo                | Output voltage                                      | $V_{CC} = MAX$ ,        | IO = 0                    | 0                      |      | 6    | V    |

| IVOD1I            | Differential output voltage                         | V <sub>CC</sub> = MIN,  | IO = 0                    | 1.5                    |      | 6    | V    |

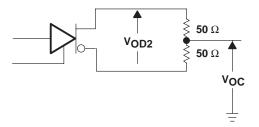

| V <sub>OD2</sub>  | Differential output voltage                         | $R_L = 100 \Omega$ ,    | See Figure 1              | 1/2 V <sub>OD1</sub> o | r 2§ |      | V    |

| Δ V <sub>OD</sub> | Change in magnitude of differential output voltage¶ | R <sub>L</sub> = 100 Ω, | See Figure 1              |                        |      | ±0.2 | V    |

| Voc               | Common-mode output voltage#                         | $R_L = 100 \Omega$ ,    | See Figure 1              |                        |      | ±3   | V    |

| Δ VOC             | Change in magnitude of common-mode output voltage¶  | R <sub>L</sub> = 100 Ω, | See Figure 1              |                        |      | ±0.2 | V    |

|                   | O Output current with power off                     |                         | VO = 6 V                  |                        |      | 100  |      |

| 10                |                                                     |                         | V <sub>O</sub> = -0.25 V  |                        |      | -100 | μΑ   |

| 10=               | IOZ Off-state (high-impedance state) output current |                         | V <sub>O</sub> = 0.5 V    |                        |      | -20  |      |

| 102               |                                                     |                         | V <sub>O</sub> = 2.5 V    |                        |      | 20   | μΑ   |

| lį                | Input current at maximum input voltage              | $V_{CC} = MAX$ ,        | V <sub>I</sub> = 7 V      |                        |      | 100  | μΑ   |

| ΙΗ                | High-level input current                            | $V_{CC} = MAX$ ,        | V <sub>I</sub> = 2.7 V    |                        |      | 20   | μΑ   |

| I∣∟               | Low-level input current                             | $V_{CC} = MAX$ ,        | V <sub>I</sub> = 0.4 V    |                        |      | -200 | μΑ   |

| los               | Short-circuit output current                        | $V_{CC} = MAX$          |                           | -30                    |      | -150 | mA   |

| Icc               | Supply current (all drivers)                        | $V_{CC} = MAX$ ,        | All outputs disabled      |                        | 26   | 45   | mA   |

<sup>†</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions.

# switching characteristics, $V_{CC} = 5 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ (see Figure 2)

|                  | PARAMETER                                        | TEST CONDIT            | MIN                    | TYP | MAX | UNIT |    |

|------------------|--------------------------------------------------|------------------------|------------------------|-----|-----|------|----|

| tPLH             | Propagation delay time, low-to-high-level output | S1 and S2 open,        | C <sub>L</sub> = 30 pF |     | 6   | 13   | ns |

| tPHL             | Propagation delay time, high-to-low-level output | S1 and S2 open,        | C <sub>L</sub> = 30 pF |     | 9   | 14   | ns |

|                  | Output-to-output skew                            | S1 and S2 open,        | C <sub>L</sub> = 30 pF |     | 3   | 6    | ns |

| tPZH             | Output enable time to high level                 | S1 open and S2 closed  |                        |     | 11  | 15   | ns |

| tpZL             | Output enable time to low level                  | S1 closed and S2 open  |                        |     | 16  | 20   | ns |

| <sup>t</sup> PHZ | Output disable time from high level              | S1 open and S2 closed, | C <sub>L</sub> = 10 pF |     | 8   | 15   | ns |

| tPLZ             | Output disable time from low level               | S1 and S2 closed,      | C <sub>L</sub> = 10 pF |     | 18  | 20   | ns |

<sup>&</sup>lt;sup>‡</sup> All typical values are at  $V_{CC} = 5 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ .

<sup>§</sup> The minimum  $V_{OD2}$  with a 100- $\Omega$  load is either 1/2  $V_{OD1}$  or 2 V, whichever is greater.

$<sup>\</sup>P$  |VOD| and |VOC| are the changes in magnitude of VOD and VOC, respectively, that occur when the input is changed from a high level to a low level. # In ANSI Standard EIA/TIA-422-B, VOC, which is the average of the two output voltages with respect to ground, is called output offset voltage,

Not more than one output should be shorted at a time, and duration of the short circuit should not exceed one second.

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Differential and Common-Mode Output Voltages

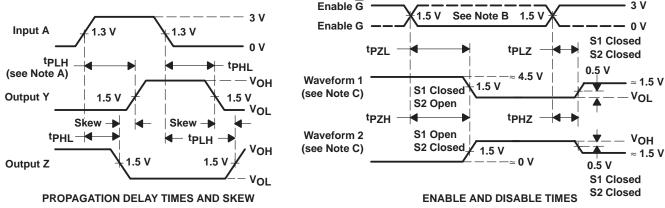

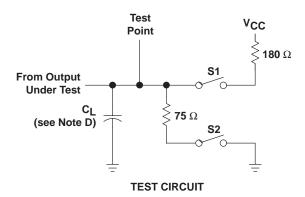

**VOLTAGE WAVEFORMS**

NOTES: A. When measuring propagation delay times and skew, switches S1 and S2 are open.

- B. Each enable is tested separately.

- C. Waveform 1 is for an output with internal conditions such that the output is low except when disabled by the output control. Waveform 2 is for an output with internal conditions such that the output is high except when disabled by the output control.

- D. C<sub>L</sub> includes probe and jig capacitance.

- E. All input pulses are supplied by generators having the following characteristics: PRR  $\leq$  1 MHz,  $Z_O \approx 50~\Omega,\,t_f \leq$  15 ns, and  $t_f \leq$  6 ns.

Figure 2. Test Circuit and Voltage Waveforms

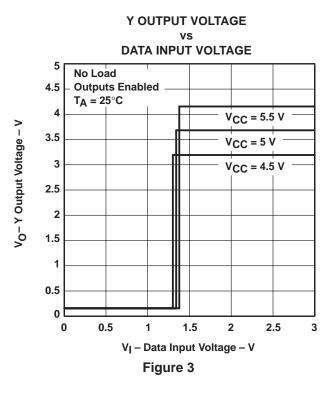

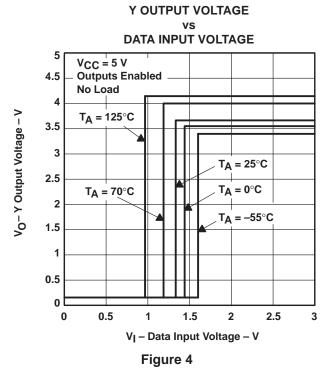

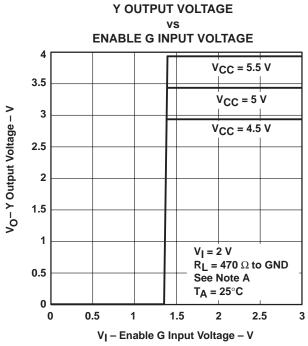

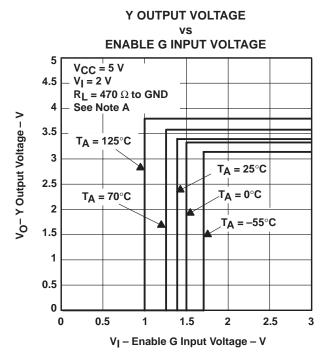

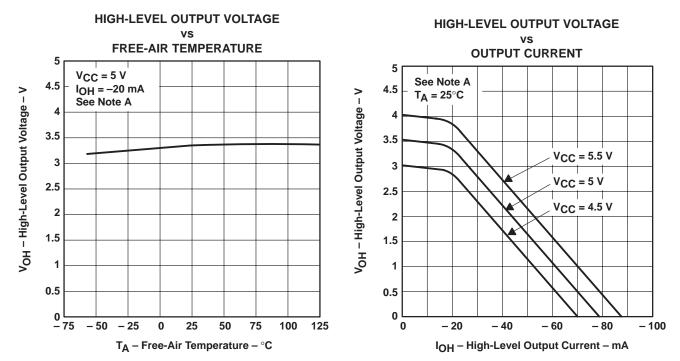

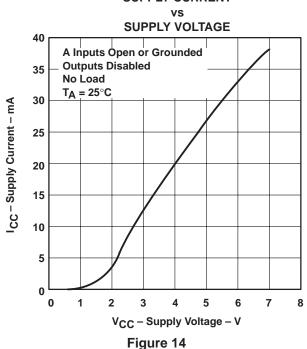

#### TYPICAL CHARACTERISTICS<sup>†</sup>

NOTE A: The A input is connected to  $V_{CC}$  during the testing of the Y outputs and to ground during the testing of the Z outputs.

NOTE A: The A input is connected to V<sub>CC</sub> during the testing of the Y outputs and to ground during the testing of the Z outputs.

Figure 5

Figure 6

<sup>†</sup> Operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

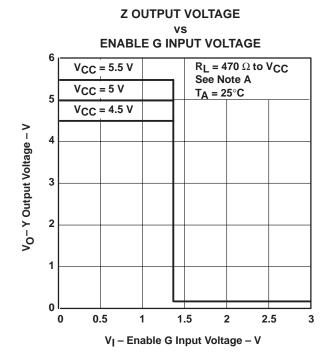

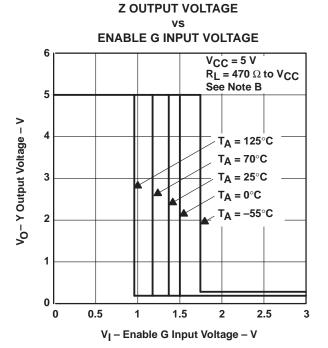

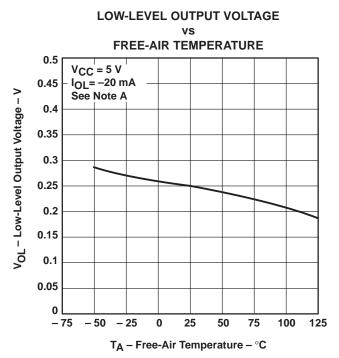

#### TYPICAL CHARACTERISTICS†

NOTE A: The A input is connected to  $V_{CC}$  during the testing of the Y outputs and to ground during the testing of the Z outputs.

NOTE B: The A input is connected to GND during the testing of the Y outputs and to  $V_{CC}$  during the testing of the Z outputs.

Figure 7 Figure 8

† Operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

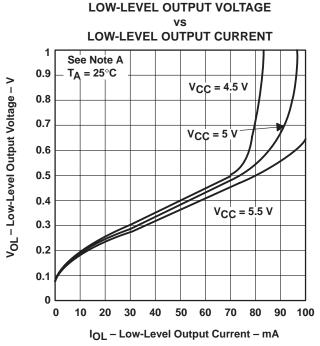

#### TYPICAL CHARACTERISTICS<sup>†</sup>

NOTE A: The A input is connected to V<sub>CC</sub> during the testing of the Y outputs and to ground during the testing of the Z outputs.

NOTE A: The A input is connected to V<sub>CC</sub> during the testing of the Y outputs and to ground during the testing of the Z outputs.

Figure 9 Figure 10

<sup>†</sup>Operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

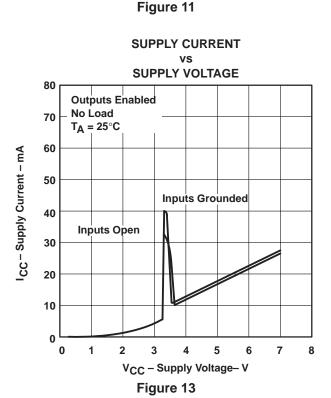

#### TYPICAL CHARACTERISTICS†

NOTE A: The A input is connected to GND during the testing of the Y outputs and to  $V_{\hbox{\footnotesize{CC}}}$  during the testing of the Z outputs.

NOTE A: The A input is connected to GND during the testing of the Y outputs and to VCC during the testing of the Z outputs.

<sup>†</sup> Operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied.

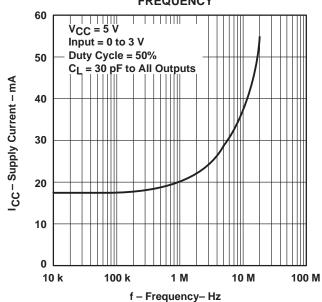

## TYPICAL CHARACTERISTICS

## SUPPLY CURRENT vs FREQUENCY

Figure 15

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated

>> Semiconductor Home > Products > Analog & Mixed-Signal > Interface Products > Transmitters and Receivers >

#### SN75ALS192, QUADRUPLE DIFFERENTIAL LINE DRIVER

**Device Status: Active**

- > Description

- > Features

- > Datasheets

- > Pricing/Samples/Availability

- > Application Notes

- > Related Documents

- > Development Tools

- > Applications

| Parameter Name        | SN75ALS192 |

|-----------------------|------------|

| Drivers Per Package   | 4          |

| Driver tpd (ns)       | 14         |

| Supply Voltage(s) (V) | 5          |

| ICC (max) (mA)        | 45         |

| Footprint             | AM26LS31   |

# **Description**

The four differential line drivers are designed for data transmission over twisted-pair or parallel-wire transmission lines. They meet the requirements of ANSI Standard EIA/TIA-422-B and ITU Recommendations V.11 and are compatible with 3-state TTL circuits. Advanced low-power Schottky technology provides high speed without the usual power penalties. Standby supply current is typically only 26 mA, while typical propagation delay time is less than 10 ns.

High-impedance inputs maintain low input currents, less than 1 uA for a high level and less than 100 uA for a low level. Complementary output-enable inputs (G and G\) allow these devices to be enabled at either a high input level or low input level. The SN75ALS192 is capable of data rates in excess of 20 Mbit/s and is designed to operate with the SN75ALS193 quadruple line receiver.

The SN75ALS192 is characterized for operation from 0°C to 70°C.

H = high level, L = low level, X = irrelevant, Z = high impedance (off)

#### **Features**

- Meets or Exceeds the Requirements of ANSI Standard EIA/TIA-422-B and ITU Recommendation V.11

- Designed to Operate up to 20 Mbaud

- 3-State TTL Compatible

- Single 5-V Supply Operation

- High Output Impedance in Power-Off Condition

- Complementary Output-Enable Inputs

Improved Replacement for the AM26LS31

To view the following documents, <u>Acrobat Reader 3.x</u> is required. To download a document to your hard drive, right-click on the link and choose 'Save'.

## **Datasheets**

Full datasheet in Acrobat PDF: <a href="style="style-type: sels-007d.pdf">sels-007d.pdf</a> (156 KB)

Full datasheet in Zipped PostScript: <a href="style-type: sels-007d.psz">sels-007d.psz</a> (138 KB)

# Pricing/Samples/Availability

| Orderable Device | <u>Package</u> | <u>Pins</u> | Temp (°C) | <u>Status</u> | <u>Price/unit</u><br>USD (100-999) | Pack Qty | Availability / Samples |

|------------------|----------------|-------------|-----------|---------------|------------------------------------|----------|------------------------|

| SN75ALS192D      | <u>D</u>       | 16          | 0 TO 70   | ACTIVE        | 1.70                               | 40       | Check stock or order   |

| SN75ALS192DR     | <u>D</u>       | 16          | 0 TO 70   | ACTIVE        | 1.45                               | 2500     | Check stock or order   |

| SN75ALS192N      | N              | 16          | 0 TO 70   | ACTIVE        | 1.70                               | 25       | Check stock or order   |

| SN75ALS192NS     | <u>NS</u>      | 16          | 0 TO 70   | ACTIVE        |                                    |          | Check stock or order   |

# **Application Reports**

- 422 AND 485 OVERVIEW AND SYSTEM CONFIGURATIONS (SLLA070 Updated: 02/15/2000)

- ANALOG APPLICATIONS JOURNAL, FEBRUARY 2000 (SLYT012A Updated: 03/23/2000)

- ANALOG APPLICATIONS JOURNAL, NOVEMBER 1999 (SLYT010A Updated: 03/23/2000)

- COMPARING BUS SOLUTIONS (SLLA067 Updated: 03/06/2000)

- ELECTROSTATIC DISCHARGE APPLICATION NOTE (SSYA008 Updated: 05/05/1999)

- JITTER ANALYSIS (SLLA075 Updated: 03/31/2000)

- SKEW DEFINITIONS (SLLA060 Updated: 08/13/1999)

- THERMAL CHARACTERISTICS OF LINEAR AND LOGIC PACKAGES USING JEDEC PCB DESIGNS (SZZA017A - Updated: 09/15/1999)

## **Related Documents**

A STATISTICAL SURVEY OF COMMON-MODE NOISE (SLLA057, 131 KB - Updated: 12/23/1999)

Table Data Updated on: 6/2/2000

• Search • Tech Support • Comments • Site Map • TI&ME • Home (c) Copyright 2000 Texas Instruments Incorporated. All rights reserved.

Trademarks, Important Notice!, Privacy Policy